版图对电路的影响—差分放大器

差分放大电路的作用差分放大电路特点

差分放大电路的作用与特点差分放大电路的作用差分放大电路广泛应用于模拟电路、数模混合电路、高速和高精度信号处理以及信号调理等领域。

差分放大电路起到的作用有以下两个方面:1. 差分信号转换为单端信号差分放大电路能够将差分输入信号转化为单端输出信号,以满足不同应用场合的要求。

在电路设计中,常会有多种差分信号或单端信号存在于电路中,因此需要利用差分放大电路将差分信号转换为单端信号。

在传输差分信号的信号线上,使用差分放大电路进行差分信号转换,甚至可以增加传输距离。

2. 放大差分信号幅度在信号调理的过程中,常常需要对输入信号进行放大处理。

差分放大电路作为一种放大器,可以放大不同幅度的差分信号,并输出到下一级电路中。

差分放大电路不仅可以增加信号幅度,而且可以提高信号的抗干扰能力,提高整个系统的稳定性。

差分放大电路的特点差分放大电路不仅能够将差分信号转换为单端信号,还有以下几个特点:1. 抗共模干扰能力强差分放大电路是通过比较两个输入信号的差异来放大信号的。

由于两个输入信号是对称的,并且两个输入信号的共模分量一般在差分放大电路中被抵消,因此差分放大电路对共模信号具有较强的抑制能力。

即使输入信号存在一定的共模干扰,通过差分放大电路处理后,输出信号也能够保持较好的正常工作。

2. 带宽宽、稳定性好差分放大电路的带宽较宽,稳定性较好。

由于差分放大电路中采用了两个互补的信号进行放大,使得差分放大电路具有相对较大的增益带宽乘积(GBP)。

同时,由于差分输入信号在差分放大器内部被抵消,使得差分放大电路具有较好的稳定性。

因此,差分放大电路被广泛应用于高速通信、高精度测量等领域。

3. 集成度高随着集成电路技术的发展,差分放大电路也逐渐实现了微型化和集成化。

差分放大电路已经被应用于单片微处理器、微控制器、数据采集卡、移动通信终端等电子产品中。

差分放大电路的集成度越高,电路复杂度越低,生产成本也越低,同时为电子产品的实现提供了更多可能性。

3.2模拟集成电路设计-差分放大器版图

集成电路设计实习Integrated Circuits Design LabsI t t d Ci it D i L b单元实验三(第二次课)模拟电路单元实验-差分放大器版图设计2007-2008 Institute of Microelectronics Peking University实验内容、实验目的、时间安排z实验内容:z完成差分放大器的版图z完成验证:DRC、LVS、后仿真z目的:z掌握模拟集成电路单元模块的版图设计方法z时间安排:z一次课完成差分放大器的版图与验证Institute of Microelectronics, Peking University集成电路设计实习-单元实验三Page1实验步骤1.完成上节课设计放大器对应的版图对版图进行、检查2.DRC LVS3.创建后仿真电路44.后仿真(进度慢的同学可只选做部分分析)z DC分析:直流功耗等z AC分析:增益、GBW、PMz Tran分析:建立时间、瞬态功耗等Institute of Microelectronics, Peking University集成电路设计实习-单元实验三Page2Display Optionz Layout->Options->Displayz请按左图操作Institute of Microelectronics, Peking University集成电路设计实习-单元实验三Page3由Schematic创建Layoutz Schematic->Tools->DesignSynthesis->Layout XL->弹出窗口->Create New->OK>选择Create New>OKz Virtuoso XL->Design->Gen FromSource->弹出窗口z选择所有Pinz设置Pin的Layerz UpdateInstitute of Microelectronics, Peking University集成电路设计实习-单元实验三Page4对管的共质心画法:相对位置放置z设A管、B管为对管,共8个Multiplier将管的前个p合在一起,置于左上角z A4Multiplierz将A管的后4个Multiplier合在一起,置于右下角z将B管的前4个Multiplier合在一起,置于右上角z将B管的后4个Multiplier合在一起,置于左下角ABABInstitute of Microelectronics, Peking University集成电路设计实习-单元实验三Page5对管的共质心画法:层间互连单元的调用z调用单元z CSMC05MS中的POLY_M1z View为symbolicz设置z Column:Contact列数C l C t tz Row:Contact行数z其余可供调用的层间互连单元z DIFF_M1DIFF M1z M1_M2z M2_M3z Ntapz PtapInstitute of Microelectronics, Peking University集成电路设计实习-单元实验三Page6对管的共质心画法:连线z A管中前4个Multiplier的连线pz挪动B管前4个Multiplier的位置,复制上图中的相关连线(注意:使用上下镜像功能)z按c,鼠标左键拉框,选定一组连线z按F3,选择上下镜像z将复制后的连线放到合适的位置Institute of Microelectronics, Peking University集成电路设计实习-单元实验三Page7对管的共质心画法:连线、隔离z使用ptap将N型MOSFET围起来z固定衬底电压、隔离数字干扰ABABInstitute of Microelectronics, Peking University集成电路设计实习-单元实验三Page8Ntap、ptap的尺寸z尺寸:z Tap lengthz Tap widthz根据需要设置Institute of Microelectronics, Peking University集成电路设计实习-单元实验三Page9显示未完成的连线:查找未完成的连线时使用z Connectivity->Show IncompleteNetsz未完成的连线Listz红框表示该连线被Selectedz放大显示未完成的连线z未完成连线的相关信息Institute of Microelectronics, Peking University集成电路设计实习-单元实验三Page10查找DRC错误标识z Verify->Markers->Find,弹出窗口设置z Zoom To Markersz按Apply显示当前DRC错误标识,按Next显示下一个标识z回到版图窗口,按Shift+z缩小显示目标,查看标识的具体原因Institute of Microelectronics, Peking University集成电路设计实习-单元实验三Page11查找LVS的未匹配处z首先:LVS结束后,查看Output结果z若查看结果很难找出未匹配处,请按如下方法查找1.打开电路的extracted view2.在extracted view中:Verify>LVS>Error Display,弹出窗口2extracted view:Verify->LVS->Error Display3.设置Auto-Zoom,按First、Next可显示LVS失配(佐以shift+z)4.记录失配原因与坐标,回到Layout View查看该坐标处的版图信息4Layout ViewInstitute of Microelectronics, Peking University集成电路设计实习-单元实验三Page12后仿真(第一步):Build Analog1.复制某单元的Layout View到新单元2.执行Extract3.LVS双方均填写extracted4.Run & Build Analog5.Include All & OKInstitute of Microelectronics, Peking University集成电路设计实习-单元实验三Page13后仿真(第二步):Create Symbol1.打开任意一个Schematic View2.Design->Create Cellview->FromCellview,弹出右上窗口3.点击Browse,弹出右下窗口4.选后仿单元的Analog_extracted参考由Schematic生成SymbolInstitute of Microelectronics, Peking University集成电路设计实习-单元实验三Page14后仿真(第三步):仿真设置1.调用analog_extracted生成的symbol,创建仿真电路启动(g g)2.ADE Analog Design Environment3.ADE->Setup-> Environment,弹出窗口4.在Switch View List中添加analog_extracted4Switch View List analog extractedInstitute of Microelectronics, Peking University集成电路设计实习-单元实验三Page15。

差分放大器工作原理详细讲解

差分放大器工作原理详细讲解Differential amplifiers, also known as difference amplifiers, are essential components in analog electronic circuits. They amplify the difference between two input signals while rejecting any common-mode signals present. They play a crucial role in filtering out noise and providing high common-mode rejection ratios. Differential amplifiers are commonly used in a variety of applications such as audio amplifiers, instrumentation amplifiers, and data acquisition systems.差分放大器,也称为差分放大器,是模拟电子电路中的重要组件。

它放大两个输入信号之间的差异,同时抑制任何共模信号。

它在滤除噪声和提供高共模抑制比方面发挥着至关重要的作用。

差分放大器通常用于各种应用,如音频放大器、仪器放大器和数据采集系统。

The differential amplifier works on the principle of amplifying the voltage difference between its two input terminals. When the two input signals are equal, the output voltage is ideally zero, providing common-mode rejection. This rejection of common-mode signals is achieved through the balanced configuration of the amplifier circuit,which amplifies only the difference between the two input voltages. By using matched transistors and resistors, the amplifier can effectively reject any signals that are common to both inputs.差分放大器的工作原理是放大其两个输入端之间的电压差。

第三章 差动放大电路及集成运算放大器 第一节差动放大电路

差动放大电路及集成运算放大器

3.1.1.1 差动放大电路的基本结构 差动放大电路如图3-1所示。

图3-2中可以算出差模输入电阻为: Rid=2(rbe+Rb) 输出电阻为: Rο=2RC

差动放大电路及集成运算放大器

3.1.3 共模输入信号与共模抑制比KCMR

在差动放大器两输入端同时输入一对极性相同、幅度相 同的信号称为共模输入方式。定义共模信号uic为两个输入信 号的算术平均值,即:

uic

ui1

差动放大电路及集成运算放大器

因此,其差模电压放大倍数为:

Aud

uo uid

Rc

Rb rbe

上式说明,该电压放大倍数与单管共射放大电路的电压

放大倍数相等。

这里我们用两套电路的元件实现的电压放大倍数和一套 电路相同。但该电路具有很好的超低频性能和很强的抑制零 点漂移的能力,这个问题下面还要详细讨论。

uo uo1 uo2 2uo1

差动放大电路及集成运算放大器

由图3-2可以计算出VT1、VT2的输出电压分别为:

VT1的输出电压:

uo1

Rcuid

2(Rb rbe )

VT2的输出电压:

uo 2

Rcuid

2(Rb rbe )

则差动放大电路的双端输出电压为:

uo

uo1

uo2

RCuid

Rb rbe

在一些超低频及直流放大电路中,级间耦合必须采用直 接耦合方式。直接耦合电路既能放大交流信号又能放大直流 信号,具有相当好的低频特性,所以又常称为直流放大器。 但由于其内部各级电路的静态工作点相互影响,给电路设计 和调整带来诸多不便。

版图对电路的影响

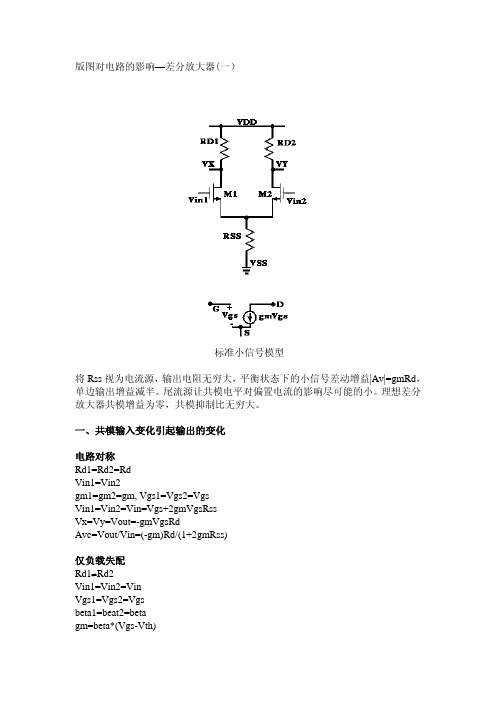

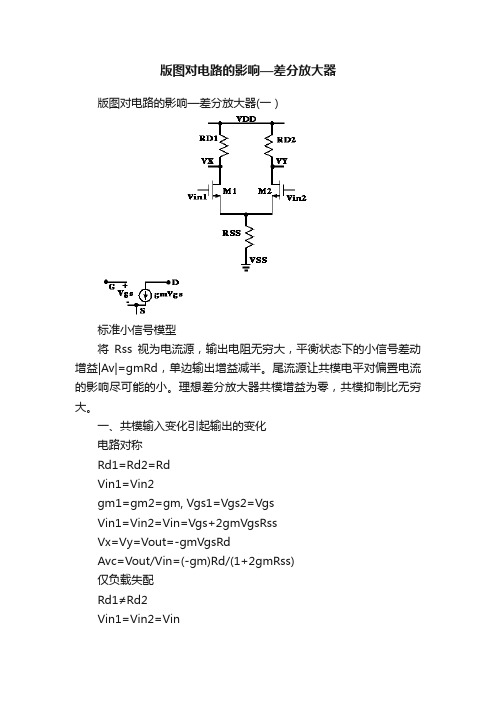

标准小信号模型 将 Rss 视为电流源, 输出电阻无穷大, 平衡状态下的小信号差动增益|Av|=gmRd, 单边输出增益减半。尾流源让共模电平对偏置电流的影响尽可能的小。理想差分 放大器共模增益为零,共模抑制比无穷大。 一、共模输入变化引起输出的变化 电路对称 Rd1=Rd2=Rd Vin1=Vin2 gm1=gm2=gm, Vgs1=Vgs2=Vgs Vin1=Vin2=Vin=Vgs+2gmVgsRss Vx=Vy=Vout=-gmVgsRd Avc=Vout/Vin=(-gm)Rd/(1+2gmRss) 仅负载失配 Rd1≠Rd2 Vin1=Vin2=Vin Vgs1=Vgs2=Vgs beta1=beat2=beta gm=beta*(Vgs-Vth)

2Vin1=2Vgs1(1+gm1Rss+gm2Rss)/(1+2gm2Rss) Avd=(Vx-Vy)/(Vin1-Vin2)=(Vx-Vy)/2Vin1 Avd=(-Rd/2)(gm1+gm2+4gm1gm2Rss)/(1+gm1Rss+gm2Rss)

三、视 Rss 为电流源时, (Vx-Vy)/Vin1|du to vin1=(-Rd1)/[(1/gm1)+(1/gm2)]-Rd2/[(1/gm2)+(1/gm1)] (Vx-Vy)/Vin2|du to vin2=(Rd2)/[(1/gm2)+(1/gm1)]-(-Rd1)/[(1/gm1)+(1/gm2)] Avd=(Vx-Vy)/(Vin1-Vin2)=-(Rd1+Rd2)/[(1/gm1)+(1/gm2)] 如果 Rd1=Rd2=Rd,gm1=gm2=gm,则 Avd=-gmRd 如果 Rd1=Rd2=Rd,gm2=2gm1=gm,则 Avd=(-4/3)gmRd

差分放大器和运算放大器

运算放大器的应用

信号放大

运算放大器可用于信号的线性放大,实现信号的传输 和处理。

模拟计算

利用运算放大器的加法、减法、积分和微分等运算功 能,实现模拟计算。

控制系统

在控制系统如PID控制器中,运算放大器用于信号的 调节和控制。

03 差分放大器和运算放大器 的比较

性能比较

差分放大器

具有高共模抑制比、低噪声、低失真 等优点,适用于信号处理和放大微弱 信号。

差分放大器和运算放大器

目录

• 差分放大器 • 运算放大器 • 差分放大器和运算放大器的比较 • 差分放大器和运算放大器的实际应用案例 • 未来发展趋势和展望

01 差分放大器

差分放大器的定义

差分放大器是一种电子放大器,它能 够放大两个输入信号之间的差值。

它通常由两个对称的放大器组成,每 个放大器分别处理一个输入信号,并 输出放大的信号。

特点

具有极高的开环增益、输入电阻高、输出电阻低等特性。

运算放大器的工作原理

差分输入

01

运算放大器采用差分输入方式,将两个输入端之间的电压差放

大。

反馈机制

02

通过引入负反馈机制,将输出信号反馈到输入端,以控制放大

倍数和输出信号。

输出级

03

输出级通常采用推挽或电压跟随器电路,以提供较大的输出电

流和较低的输出电阻。

差分放大器的工作原理

01

差分放大器通过比较两个输入信号的差值来工作, 将差值转换为输出信号。

02

它通常采用对称电路结构,以减小电路中的误差和 噪声。

03

差分放大器具有高共模抑制比(CMRR)和低噪声 特性,能够有效地放大微弱信号。

差分放大器的应用

第4章 差分放大器

总之,这种电路结构由于差分对管在共模输入时 的工作电流变化引起非线性及输出信号失真等。

基本差分对-电路结构

而基本差分电路结构中通过为差分对提供了固 定的尾电流则很好地解决了原始结构中存在的 上述问题。

为差分对提供 为差分对提供一个电流源 个电流源IS,以使差分对具有固定 以使差分对具有固定 的尾电流,从而产生独立于输入共模信号Vic的电 流ID1+ID2。 在共模输入时差分对管的工作电流ID1=ID2= IS/2,并且保持恒定; 并且保持恒定 同理,其共模输出电平也保持恒定,且其值为 VDD-RIS/2(R为负载等效电阻)。 为负载等效电阻)

因而在实际电路设计中经常采用差分电路以获 得高性能。

基本差分对

基本差分对-电路结构

典型的MOS差分放大器的电路结构 如图所示。

基本差分对-电路结构

图中一般R1=R2=R,在两种差分电路中的负载有多种 形式 既可为无源负载 也可为有源负载 但通常采用 形式,既可为无源负载,也可为有源负载,但通常采用 的是恒流源有源负载。而电流源则采用一个工作于饱和 区的MOS管实现。 管实现 与原始的差分电路相比,不同之处在于原始结构中的差 分对管的源极接地 而上图的差分对管同时接到 个恒 分对管的源极接地,而上图的差分对管同时接到一个恒 流源上。

基本差分对-差分对的差分工作

(1) 差模增益 1) 双端输入双端输出时的差模电压增益 采用“半电路概念”对理想的基本差分对进行小信号分析, 令ΔVi1= =-ΔVi2=ΔVi/2,则 则一个 个MOS管的漏电流增大而 另一个MOS管的电流减小,由于电路是完全对称的,所以 ID1的增加量与ID2的减小量相等,因此总电流保持不变,即 的减小量相等 因此总电流保持不变 即 VQ的电位保持不变,节点Q可被认为是交流地。因此,可由 下图求解。 下图求解

第四章第四节差分放大器

VEE

iC 2 = I CQ 2 − ic

当它们共同流入 REE 时:

静态:ICQ1=ICQ2=ICQ

i EE = 2 I CQ 1 = 2 I CQ 2 = 2 I CQ

静态:IEE=2ICQ1=2ICQ2=2ICQ

从上述推论可知:流过REE 的电流仍为原静态电流IEE , 增量电流∆ic= 0 。 这就是说对差模信号而言,REE 可示为短路,因此,对 差模信号来说,差分放大器可等效为如图所是: 交流通路

VBQ1 − VEE = VBE ( on ) + I E RE

0 − V EE − V BE ( on ) = I E R E

IE =

− V EE − V BEQ RE

RC1 RB1 VBQ1 T1

VCC RC2 Vo2 T2 RE IE VEE RB2 VBQ2

Vo1

在理想情况下,电路两边完全对称: 则有 所以

T1

2、差模性能 、

vid

vid1 vid2

RC1 RC2

RL/2 vod1 vod RL/2 vod2

①、差模输入电阻

T2

定义:从差分放大器两输入端看进去所呈现的视在电阻。 即

vid 2vid1 2vid 2 2rb′eii Ri = = = = = 2rb′e ii ii ii ii

RC1 vo1 T1 vo RC2 vo2 T2

在实际电路中,一般满足 2(1+β)REE >> rb'e 所以

VC 1 = I L R L

VC 1 IL = RL

VC1 VC1 = VCC − ( I C1 + ) RC1 RL RL ′ VC1 = VCC − I C1RL RC + RL

版图对电路的影响—差分放大器

版图对电路的影响—差分放大器版图对电路的影响—差分放大器(一)标准小信号模型将Rss视为电流源,输出电阻无穷大,平衡状态下的小信号差动增益|Av|=gmRd,单边输出增益减半。

尾流源让共模电平对偏置电流的影响尽可能的小。

理想差分放大器共模增益为零,共模抑制比无穷大。

一、共模输入变化引起输出的变化电路对称Rd1=Rd2=RdVin1=Vin2gm1=gm2=gm, Vgs1=Vgs2=VgsVin1=Vin2=Vin=Vgs+2gmVgsRssVx=Vy=Vout=-gmVgsRdAvc=Vout/Vin=(-gm)Rd/(1+2gmRss)仅负载失配Rd1≠Rd2Vin1=Vin2=VinVgs1=Vgs2=Vgsbeta1=beat2=betagm=beta*(Vgs-Vth)gm1=gm2=gmVin=Vgs+2gmVgsRssVx=-gmVgsRd1Vy=-gmVgsRd2Vx-Vy=-gmVgs(Rd1-Rd2)Avc=(Vx-Vy)/Vin=(-gm)(Rd1-Rd2)/(1+2gmRss)仅晶体管失配beta1≠beta2gm1≠gm2Vgs1=Vgs2=VgsRd1=Rd2=RdVin1=Vin2=VinVin=Vgs+(gm1+gm2)VgsRssVx=-gm1VgsRdVy=-gm2VgsRdVx-Vy=-VgsRd(gm1-gm2)Avc=Vx-Vy/Vin=-Rd(gm1-gm2)/[1+(gm1+gm2)Rss]摘录自(1):1、共模扰动频率的增加与尾流源并联的电容会使电流产生很大的变化(即使尾流源输出阻抗很大,在高频时也会变得很严重)2、电路不对称既来自负载电阻,也来自输入晶体管。

通常后者产生的失配要大得多。

由i=q/t, q=cv, f=1/t得到i=cvf,所以尾流部分的寄生电容与输入频率会影响到尾流源,进而影响到整个差动电路的性能。

C=Eox * Area / T ox,很容易看出面积越大电容也越大。

差分放大器版图设计

一.绪论1.1差分放大器的概述差分放大器(Differ entia l amplif ier),是能把两个输入电压的差值加以放大的电路,也称差动放大器。

这是一种零点漂移很小的直接耦合放大器,常用于直流放大。

它可以是平衡(术语“平衡”意味着差分)输入和输出,也可以是单端(非平衡)输入和输出,常用来实现平衡与不平衡电路的相互转换,是各种集成电路的一种基本单元。

由两个参数特性相同的晶体管用直接耦合方式构成的放大器。

若两个输入端上分别输入大小相同且相位相同的信号时,输出为零,从而克服零点漂移。

适于作直流放大器。

差分放大器是一种将两个输入端电压的差以一固定增益放大的电子放大器,有时简称为“差放”。

差分放大器通常被用作功率放大器(简称“功放”)和发射极耦合逻辑电路(ECL, Emitte r Couple d Logic)的输入级。

差分放大器是普通的单端输入放大器的一种推广,只要将差放的一个输入端接地,即可得到单端输入的放大器。

很多系统在差分放大器的一个输入端输入信号,另一个输入端输入反馈信号,从而实现负反馈。

常用于电机或者伺服电机控制,以及信号放大。

在离散电子学中,实现差分放大器的一个常用手段是差动放大,见于多数运算放大器集成电路中的差分电路。

差分放大器可以用晶体三极管(晶体管)或电子管作为它的有源器件。

输出电压u0=u01-u02,是晶体管T1和T2集电极输出电压u01和u02之差。

当T1和T2的输入电压幅度相等但极性相反,即us1=-us2 时,差分放大器的增益Kd(称差模增益)和单管放大器的增益相等,即Kd≈Rc/re,式中Rc=Rc1=Rc2,re是晶体管的射极电阻。

通常re很小,因而Kd较大。

当us1=us2 ,即两输入电压的幅度与极性均相等时,放大器的输出u0应等于零,增益也等于零。

华东师范大学CMOS差分放大器版图设计报告

Project report课程名称:VLSI版图设计作业内容:差分放大器版图设计任课教师:田应洪学生姓名:刘毓达学校院系:华东师范大学电子工程系所在班级:集成电路工程一、设计目标本次版图设计我做的是CMOS差分放大器的设计。

CMOS差分放大器是模拟电路中最基本也是最重要的电路单元之一,掌握其版图对更进一步加深对电路的理解极为重要,更为关键的是,良好的版图能力是一个合格的模拟电路设计者所必须具备的素质。

本次所画差分放大器的原理图如下:二、设计要求设计规则是设计人员与工艺人员之间的接口与“协议”,是版图设计必须无条件的服从的准则,可以极大地避免由于短路、断路造成的电路失效和容差以及寄生效应引起的性能劣化。

设计规则主要包括几何规则、电学规则以及走线规则。

1.工艺本次版图设计使用无锡上华CSMC 0.6um的工艺库。

2.DRC在版图完成后必须要通过DRC规则检查。

只有通过DRC的版图才初步具备实际的生产价值。

DRC文件为工艺库中自带。

以下为部分规则示意:3.I/O端口两个输入端口,两个输出端口,VDD及VSS接口。

如原理图所示。

4.尺寸差分放大器共使用了5个MOS管。

两个PMOS,三个NMOS管。

其中P管尺寸为W/L=80/1,N管尺寸为W/L=64/1。

均使用叉指结构。

P管分成8个W/L为10:1的管。

N管分成16个W/L为4:1的管。

PAD尺寸为:poly层:120*120ummetal1和metal2层:110*110umnwell层:100*100umpad层:96*96umvia层:88*88um三、版图设计首先考虑五个管子的布局。

从上面所给的管子尺寸可以看到,每一个晶体管都是又细又长的一条。

对于实际生产显然不合适,所以经过考虑将每个晶体管做成叉指结构,这样使版图密集紧凑,并且能很好的工作。

对于总体布局,应充分考虑外部pad的连接,避免外部引线过长及交叉。

总体布局图考虑各个器件的匹配。

由于M1和M2的源漏需要与M3和M4的源漏连接,让它们的栅相互靠近,这样就比较容易把输出连接至M3和M4。

差分放大器

差分放大器差分放大器第3、4 章介绍了基本CMOS 放大器的特性。

本章在此基础上讲述单端和差分放大器的概念;说明差分结构在集成电路设计中的重要作用;分析差分放大器的直流传输特性、交流小信号特性、高频特性和共模响应。

最后讨论差分输入-单端输出放大器的特点。

5.1 差分放大器的概念5.1.1 单端和差分放大器第3、4 章讲述了几种基本放大器的结构,它们的共同特点是只有一个输入端和一个输出端,这样的放大器叫做单端输入-单端输出放大器,简称为单端放大器。

单端放大器的性能和它的直流偏置状态密切相关。

以图5.1.1 中的共源放大器为例,分析它的交流小信号增益随直流工作点的变化。

列出下列方程,其中各参数的含义和前面章节中代表的意义相同:21111)(2TH GS ox n V V L W C I ?=μ)(11111TH GS ox n m V V L W C g ?=μ)(11111TH GS D ox n D m in out V V R L W C R g v v ?==μ1o r R ??(5.1.3)(5.1.1) 假设(5.1.2)图5.1.1 单端放大器如图5.1.2,放大器有两个输入端——vin1、vin2;两个输出端——vout1、vout2;输入管M1和M2的源极不是接地电位,而是共同接在电流源I上。

它是对称的双端输入-双端输出放大器,这种对称结构叫做差分结构。

当放大器的两个输入端直流偏置电平相等时,那么根据电路的对称性,两个输出端的直流电平也相等。

在输入端加入大小相等、相位相反的信号——这样的一对信号称为差分信号,则输出端也同样是一对差分信号。

图5.1.2 的放大器叫做差分放大器,因为它的输入、输出都是差分信号,所以更准确的,称之为全差分放大器。

图5.1.2 差分放大器5.1.2 差分电路的优点现在来看看差分放大器是如何解决单端放大器中遇到的交流增益受直流偏置电平影响这一问题的。

它的关键就在于两个输入管下面连接的电流源。

差分放大电路 全篇

Rb

Uoc

Rb

T1

T2

Uic1

Iec1 Rc Uoc1 Uoc2 Rc Iec2

2Ree

2Ree

Uic2

Uoc 0

A Uc(双)

U oc U ic

Uoc1 Uoc2 0 Uic

差放的特点: 输入无差别,输出就不动;输入有差别,输出就变动。

共模抑制比CMRR—衡量差放的一个重要指标。

CMRR A Ud A Uc

差分电路的输入输出方式

单端输入 输入方式

双端输入

单端输出

输出方式

双端输出

Uo

+

差模信号和共模信号 +

Uo Uo

-

差模信号

Ui1

Ui2

一对大小相等,极性 -

+

相反的信号,用Uid1、Uid2

表示, Uid1= - Uid2

共模信号 一对大小相等,极性相同的信号, 用Uic1、Uic2表示,Uic1= Uic2

5. 双端输入/单端输入 指标比较

输出方式

双出

单出

AUD

(Rc

//

1 2

RL )

rbe

(Rc // RL )

2rbe

Rid

2rbe

双出

单出

(Rc

//

1 2

RL )

rbe

(Rc // RL )

2rbe

2rbe

Ro

2 Rc

Rc

2 Rc

Rc

集成运算放大器概述

集成运算放大器结构特点 集成运算放大器组成及各部分作用 集成运算放大器主要参数 理想集成运算放大器及两个工作区域

2. 当V+>V-时,Vo为正向输出饱和电压VOH 当V+<V-时,Vo为负向输出饱和电压VOL 其数值接近运放的正负电源电压

4.4 差分放大器

RL

REE

+ vi1 -

+ vi2 VEE

IEE = iC1 + iC2 = 2ICQ(不变)

+

T1

RL中点视为交流地电位, 即每管负载为RL / 2 。

直流电源短路接地。

注意:关键在于对公共器件的处理。

+ RC RL 2

vid1

-

vod1

-

半电路差模交流通路

2)差模性能指标分析 差模输入电阻

双端输出 Avd Av1

R L rbe

其中 R L RC //( R L / 2 )

其中 R L RC // R L

单端输出 Avd1 Avd2

R L

2 rbe

Avc仅与电路输出方式有关。 v oc 双端输出 Avc 0 v ic RL v oc1 单端输出 Avc1 Avc2 Av1 2R EE v ic

( RC //

rbe RL 2 )

v id v i1 v i2

例:图示电路,已知 =100,vi=20sint(mV),求vo

(1)分析Q点 解:

I EE ( V BE(on) V EE ) / R EE 0.5mA

VCC (12V) RC 10k T1

I CQ1 I CQ2 I EE / 2 0.25 mA

RC T1

VCC RC

因此 Avc1

RL 2R EE

很小。

单端输出电路利用REE的 负反馈作用抑制共模信号。 利用REE抑制共模信号原理:

+ vi1 -

RL

+

-

vo

T2

全差分运算放大器结构框图解析 常见的全差分运算放大器电路分析

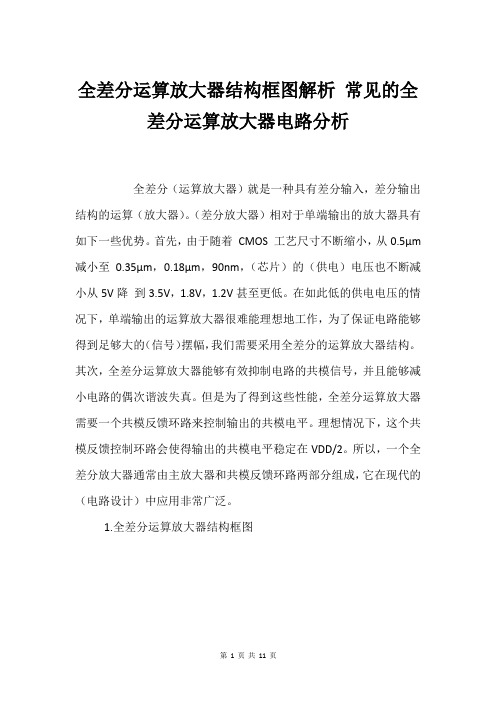

全差分运算放大器结构框图解析常见的全差分运算放大器电路分析全差分(运算放大器)就是一种具有差分输入,差分输出结构的运算(放大器)。

(差分放大器)相对于单端输出的放大器具有如下一些优势。

首先,由于随着CMOS 工艺尺寸不断缩小,从0.5μm 减小至0.35μm,0.18μm,90nm,(芯片)的(供电)电压也不断减小从5V降到3.5V,1.8V,1.2V甚至更低。

在如此低的供电电压的情况下,单端输出的运算放大器很难能理想地工作,为了保证电路能够得到足够大的(信号)摆幅,我们需要采用全差分的运算放大器结构。

其次,全差分运算放大器能够有效抑制电路的共模信号,并且能够减小电路的偶次谐波失真。

但是为了得到这些性能,全差分运算放大器需要一个共模反馈环路来控制输出的共模电平。

理想情况下,这个共模反馈控制环路会使得输出的共模电平稳定在VDD/2。

所以,一个全差分放大器通常由主放大器和共模反馈环路两部分组成,它在现代的(电路设计)中应用非常广泛。

1.全差分运算放大器结构框图共模反馈的基本思想就是由一个共模采样电路取得电路的输出共模信号,然后把共模信号与一个参考信号相比较,将比较后的误差信号放大后再输入主放大器以调节输出共模电压。

对于输入的差分信号来说,共模反馈环路不会对交流信号产生影响,相当于说共模环路对于交流是开路的。

所以,电路的差分增益和相位就由主放大器决定。

但是,对于输入的共模信号,共模反馈环路决定了输出的共模电平,这时,共模环路的增益和相位就会对电路的输出共模电平的精度和稳定性产生影响。

全差分放大器在应用中的一种电路形式,差分输出的信号摆幅vO1-vO2 为单端信号vO1(vO2)摆幅的两倍,所以在输出端可以有较大的输出动态范围,相对于单端输出提高了处理信号的幅度能力。

2. 常见的全差分运算放大器电路(a)是普通的全差分放大器电路,通常作为一个放大器的输入级部分。

图7-3(b)是折叠式全差分运算放大器电路,它的增益会比较大,可以达到60~70dB,但同时会消耗比较大的功耗,因为它有四条支路需要(电流)。

电路中的差分放大器与运算放大器

电路中的差分放大器与运算放大器在现代电子工程中,电路的设计与应用中经常会涉及到差分放大器和运算放大器,它们是电路中非常重要的组成部分。

本文将介绍差分放大器和运算放大器的基本原理以及在电路设计中的应用。

差分放大器是一种特殊的放大电路,其输入端分为正输入端和负输入端。

当两个输入端的电压差为零时,差分放大器的输出电压为零。

差分放大器通过放大输入信号的差分部分,减小噪声干扰以及共模幅度的影响,从而提高信号的质量。

在实际应用中,差分放大器常常被用于测量和控制系统,特别是在高精度、低噪声以及抗干扰能力强的领域。

在电路中,差分放大器可以采用各种形式的放大器电路来实现,比如晶体管放大器、运算放大器等。

其中,运算放大器是一种常用的差分放大器,它的输入电阻非常大、输入电阻相等,输出电阻接近于零,增益稳定且可调节。

运算放大器是一种多功能的放大电路,它可以将输入信号放大到较大的幅度,并且还可以用于数学计算、滤波、比较等功能。

通过调节运放的正负输入端的电位,可以实现对输入信号的放大倍数的调节。

同时,运算放大器还具有很低的输出阻抗,可以提供较大的输出电流。

在电路设计中,差分放大器和运算放大器有着广泛的应用。

在高保密性通信系统中,差分放大器主要被用于信号的差分放大和滤波。

通过输出信号的相位差,可以有效地消除噪声干扰。

在仪器测量与控制系统中,差分放大器被广泛应用于传感器信号的放大和处理。

通过差分测量,可以提高信号的准确性和灵敏度。

运算放大器则广泛应用于模拟电子器件的设计,如滤波器、振荡器、比较器等。

在模拟电路中,运算放大器可以将输入信号进行非线性放大,从而产生更复杂的波形。

同时,运算放大器还常用于数字电子器件的设计,如模数转换器、数模转换器等。

通过运算放大器的调节,可以将模拟信号转换为数字信号,实现数字系统的设计与应用。

然而,差分放大器和运算放大器也存在一些局限性。

首先,差分放大器对于共模电压抑制比要求较高,一旦共模电压超过其抑制比,差分放大器的放大器特性将可能失效。

差分放大器版图设计

一.绪论1.1差分放大器的概述差分放大器(Differential amplifier),是能把两个输入电压的差值加以放大的电路,也称差动放大器。

这是一种零点漂移很小的直接耦合放大器,常用于直流放大。

它可以是平衡(术语“平衡”意味着差分)输入和输出,也可以是单端(非平衡)输入和输出,常用来实现平衡与不平衡电路的相互转换,是各种集成电路的一种基本单元。

由两个参数特性相同的晶体管用直接耦合方式构成的放大器。

若两个输入端上分别输入大小相同且相位相同的信号时,输出为零,从而克服零点漂移。

适于作直流放大器。

差分放大器是一种将两个输入端电压的差以一固定增益放大的电子放大器,有时简称为“差放”。

差分放大器通常被用作功率放大器(简称“功放”)和发射极耦合逻辑电路(ECL, Emitter Coupled Logic) 的输入级。

差分放大器是普通的单端输入放大器的一种推广,只要将差放的一个输入端接地,即可得到单端输入的放大器。

很多系统在差分放大器的一个输入端输入信号,另一个输入端输入反馈信号,从而实现负反馈。

常用于电机或者伺服电机控制,以及信号放大。

在离散电子学中,实现差分放大器的一个常用手段是差动放大,见于多数运算放大器集成电路中的差分电路。

差分放大器可以用晶体三极管(晶体管)或电子管作为它的有源器件。

输出电压u0=u01-u02,是晶体管T1和T2集电极输出电压u01和u02之差。

当T1和T2的输入电压幅度相等但极性相反,即us1=-us2 时,差分放大器的增益Kd(称差模增益)和单管放大器的增益相等,即Kd≈Rc/re,式中Rc=Rc1=Rc2,re是晶体管的射极电阻。

通常re很小,因而Kd较大。

当us1=us2 ,即两输入电压的幅度与极性均相等时,放大器的输出u0应等于零,增益也等于零。

实际放大电路不可能完全对称,因而这时还有一定的增益。

这种增益称为共模增益,记为Kc。

在实际应用中,温度变化和电源电压不稳等因素对放大作用的影响,等效于每个晶体管的输入端产生了一个漂移电压。

差分放大器

差分放大器华侨大学电子工程系IC 工艺及版图设计课程实验(六)模拟电路单元版图布局(2)差分放大器华侨大学厦门专用集成电路系统重点实验室 -2010-IC 工艺及版图设计课程实验七模拟电路单元版图布局-差分放大器一、实验目的1.掌握使用 Cadence Virtuoso XL 版图编辑软件进行模拟 IC 版图布局设计2.掌握两级差分放大器电路版图布局3.通过实验掌握低等精度度匹配(以下简称低度匹配)MOSFET 的布局方法二、实验软件:Cadence IC 5141 Virtuoso Layout XL三、实验要求:实验前请做好预习工作,实验后请做好练习,较熟练地使用Virtuoso 软件对版图进行布局设计,通过实验逐渐掌握低度匹配MOSFET 的布局方法。

IC 工艺及版图设计课程实验六教学任务模拟电路单元版图布局①基准电流源学时 2 专业能力:教学目标 1.熟练掌握版图编辑软件的使用 2.掌握低度匹配 MOSFET 的布局方法 3.掌握两级差分放大器电路的布局教学内容重点难点 1. 低度匹配 MOSFET 布局 2. 两级差分放大器版图布局低度匹配 MOSFET 版图布局低度匹配MOSFET 版图布局华侨大学电子工程系(The Department of Electronic Engineering Huaqiao University)1 华侨大学厦门专用集成电路系统重点实验室第一部分实验演示部分集成电路版图设计是一门技术,它需要设计者具有电路系统原理与工艺制造方面的基础知识。

但是它更需要设计者的创造性、空间想象力和耐性,需要设计者长期工作的经验和知识的积累。

然而集成电路版图设计不仅仅是一门技术,还是一门艺术。

设计出一套符合设计规则的“正确”版图也许并不困难,但是要设计出最大程度体现高性能、低功耗、低成本、性能可靠的芯片版图却不是一朝一夕就能学会的事情。

在设计 CMOS 芯片时,主要的目标是优化芯片尺寸和提高密集度。

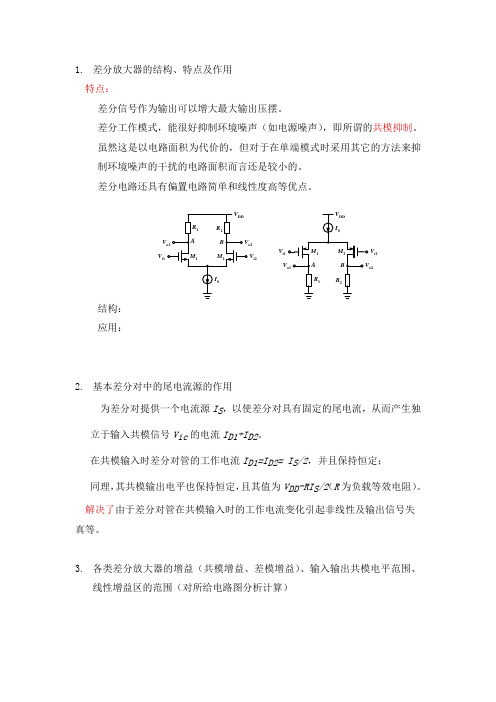

差分放大器的结构、特点及作用

1. 差分放大器的结构、特点及作用 特点:差分信号作为输出可以增大最大输出压摆。

差分工作模式,能很好抑制环境噪声(如电源噪声),即所谓的共模抑制。

虽然这是以电路面积为代价的,但对于在单端模式时采用其它的方法来抑制环境噪声的干扰的电路面积而言还是较小的。

差分电路还具有偏置电路简单和线性度高等优点。

结构: 应用:2. 基本差分对中的尾电流源的作用为差分对提供一个电流源I S ,以使差分对具有固定的尾电流,从而产生独立于输入共模信号V ic 的电流I D1+I D2。

在共模输入时差分对管的工作电流I D1=I D2= I S /2,并且保持恒定; 同理,其共模输出电平也保持恒定,且其值为V DD -RI S /2(R 为负载等效电阻)。

解决了由于差分对管在共模输入时的工作电流变化引起非线性及输出信号失真等。

3. 各类差分放大器的增益(共模增益、差模增益)、输入输出共模电平范围、线性增益区的范围(对所给电路图分析计算)V i1V i2V i1V i2双端输入双端输出时的差模电压增益 双端输入单端输出差模电压增益在理想情况下,由于电路的完全对称性,则当输入共模信号时,由于引起差分对管的每边的输出电压的变化量相等,双端输出的电压为0,故电压增益为0。

理想情况下,单端输出共模小信号增益也为0。

4. 各类差分放大器的失调分析(失调的表示方式、原因,减小失调的方法) P83减小由于输入差分对管不对称所引起的输入失调电压a 、减小输入差分对管MOS 管的阈值电压差,一种有效的方法就是采用离子注入工艺,使输入差分对管的阈值电压一致性较好。

b 、减小失调误差的另一种方法是减小由于差分对管的几何尺寸的不对称引入的误差,这可以增大差分对管的尺寸,从而减小ΔW/W 与ΔL/L 的值(但这会造成输入差分对管具有大的寄生电容)来实现,并且通过提高光刻精度以减小ΔW/W 与ΔL/L 的误差值。

5. 差分放大器共模抑制能力的表示方式共模抑制比CMRR 表示差分放大器的共模抑制能力,CMRR 定义为放大器的差模信号电压增益与共模信号电压增益之比。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

版图对电路的影响—差分放大器(一)

标准小信号模型

将Rss视为电流源,输出电阻无穷大,平衡状态下的小信号差动增益|Av|=gmRd,单边输出增益减半。

尾流源让共模电平对偏置电流的影响尽可能的小。

理想差分放大器共模增益为零,共模抑制比无穷大。

一、共模输入变化引起输出的变化

电路对称

Rd1=Rd2=Rd

Vin1=Vin2

gm1=gm2=gm, Vgs1=Vgs2=Vgs

Vin1=Vin2=Vin=Vgs+2gmVgsRss

Vx=Vy=Vout=-gmVgsRd

Avc=Vout/Vin=(-gm)Rd/(1+2gmRss)

仅负载失配

Rd1≠Rd2

Vin1=Vin2=Vin

Vgs1=Vgs2=Vgs

beta1=beat2=beta

gm=beta*(Vgs-Vth)

gm1=gm2=gm

Vin=Vgs+2gmVgsRss

Vx=-gmVgsRd1

Vy=-gmVgsRd2

Vx-Vy=-gmVgs(Rd1-Rd2)

Avc=(Vx-Vy)/Vin=(-gm)(Rd1-Rd2)/(1+2gmRss)

仅晶体管失配

beta1≠beta2

gm1≠gm2

Vgs1=Vgs2=Vgs

Rd1=Rd2=Rd

Vin1=Vin2=Vin

Vin=Vgs+(gm1+gm2)VgsRss

Vx=-gm1VgsRd

Vy=-gm2VgsRd

Vx-Vy=-VgsRd(gm1-gm2)

Avc=Vx-Vy/Vin=-Rd(gm1-gm2)/[1+(gm1+gm2)Rss]

摘录自(1):

1、共模扰动频率的增加与尾流源并联的电容会使电流产生很大的变化(即使

尾流源输出阻抗很大,在高频时也会变得很严重)

2、电路不对称既来自负载电阻,也来自输入晶体管。

通常后者产生的失配要

大得多。

由i=q/t, q=cv, f=1/t得到i=cvf,所以尾流部分的寄生电容与输入频率会影响到尾流源,进而影响到整个差动电路的性能。

C=Eox * Area / Tox,很容易看出面积越大电容也越大。

以W/L = 100 / 1的晶体管为例,画成finger =1时,diff_area_f1=100 * (1.5*2 + 1) = 400, all _area_f1=400 + (0.5*4*2) = 404;当finger =2 时,diff_area_f2 = 50 * (1.5*3 +1*2) = 325, all_area_f2=325 + (0.5*6.5*2) = 331.5。

每次减小重合部分的面积。

设MOS宽度为W,重合部分宽度为ds,channel长度为g,gate出diff为cap,finger 数目为n,有(W/n+2*cap)(n*ds+ds+n*g)>=(W+2*cap)(2*ds+g),得出当n>=W*ds/[2*cap*(g+ds)]时,finger=n的整体面积大于finger=1的面积。

如果ds=x * cap, g=y *cap则

n = [W/(2*cap)] *[x / (x+y)],finger=n

如果y=z*x,其中z=g/d,则

n=W/[2*(1+z)*cap],将(1+z)*cap作为一个整体k,则

n=(W/2)*(1/k),k=(1+g/ds)*cap

上式可知k越小,n越大,也就是k越小画成多个finger的形式越合算。

更直观讲就是栅宽度过大于源漏极的宽度,或者栅超出有源区很大值时,画成finger态就不太经济了。

以图例的值计算结果n=60,当然拆分来画,还是要是电路的性能作为最终的依据。

这里建议取n为偶数根source端在两边,drain端在中间,注意(以图为例)水平宽度与垂直高度相对比例。

尾流源器件目的是提供稳定的电流,其实可以是镜像电流源的一部分,所以画法已经在上次讨论过了。

不过考虑与另一晶体管相距较远,应以metal 作为连线。

晶体管失配会造成很大的影响,为保持晶体管的匹配通常的做法有,中心对称和质心对称(交叉对称)法,这些可以运用在制程偏差很大的项目中。

在先进的工艺里,这方面的所占的比重在逐步下降,甚至可以忽略,在种情况下的匹配就是将晶体管尽量靠近,比如共用。

二、差模输入变化引起输出的变化

电路对称:

Rd1=Rd2=Rd

Vgs1=Vgs2=Vgs

gm1=gm2=gm

Vx=-Vy

Vx-Vy=2Vx

Vx=-gmVgsRd

Vin1=-Vin2

Vin1-Vin2=2Vin1

Vin1=Vgs+2gmVgsRss

Avd=(Vx-Vy)/(Vin1-Vin2)=Vx/Vin1=(-gm)Rd/(1+2gmRss)

仅负载失配

Rd1≠Rd2

Vgs1=Vgs2=Vgs

gm1=gm2=gm

Vx=-gmVgsRd1

Vy=gmVgsRd2

Vx-Vy=-gmVgs(Rd1+Rd2)

Vin1=-Vin2

Vin1-Vin2=2Vin1

Vin1=Vgs+2gmVgsRss

Avd=(Vx-Vy)/2Vin=(-gm)[(Rd1+Rd2)/2]/(1+2gmRss)

仅晶体管失配

beta1≠beta2

gm1≠gm2

Vgs1≠Vgs2

Vin1=-Vin2

Vin1-Vin2=2Vin1

Vin1-Vgs1=Vin2-Vgs2

2Vin1=Vgs1-Vgs2

Vin1=Vgs1+(gm1Vgs1+gm2Vgs2)Rss

Vin2=Vgs2+(gm1Vgs1+gm2Vgs2)Rss

Vin1=-Vin2

Vgs2=-Vgs1(1+2gm1Rss)/(1+2gm2Rss)

Vx=-gm1Vgs1Rd

Vy=-gm2Vgs2Rd

Vx-Vy=-Vgs1Rd(gm1+gm2+4gm1gm2Rss)/(1+2gm2Rss)

2Vin1=2Vgs1(1+gm1Rss+gm2Rss)/(1+2gm2Rss)

Avd=(Vx-Vy)/(Vin1-Vin2)=(Vx-Vy)/2Vin1

Avd=(-Rd/2)(gm1+gm2+4gm1gm2Rss)/(1+gm1Rss+gm2Rss)

三、视Rss为电流源时,

(Vx-Vy)/Vin1|du to vin1=(-Rd1)/[(1/gm1)+(1/gm2)]-Rd2/[(1/gm2)+(1/gm1)]

(Vx-Vy)/Vin2|du to vin2=(Rd2)/[(1/gm2)+(1/gm1)]-(-Rd1)/[(1/gm1)+(1/gm2)]

Avd=(Vx-Vy)/(Vin1-Vin2)=-(Rd1+Rd2)/[(1/gm1)+(1/gm2)]

如果Rd1=Rd2=Rd,gm1=gm2=gm,则Avd=-gmRd

如果Rd1=Rd2=Rd,gm2=2gm1=gm,则Avd=(-4/3)gmRd

这些资料还没有整理完,因为拖得太久就先贴出来与大家共同探讨。

本篇中,着重讨论了共模和少部分差模情况,在后续的内容中,会从相关问题为出发点来进行整理,比如,增益减小、摆幅下降、输出频率下降、相位位移、噪音干扰等,这些都是我们应该知道的,问题出现了我们要做些什么?

[参考文献]

1、《模拟CMOS集成电路设计》--- Razavi

2、《CMOS模拟集成电路设计》—Allen。