cyclone3的配置方式

在对cyclone3配置时遇到的问题及配置的相关内容

在对cyclone3配置时遇到的问题及配置的相关内容Cyclone III 器件的 AS 配置引脚与其他FPGA不同,其他FPGA 的 DA TA、DCLK、CSn、ASDO等引脚都是专用的,Cyclone III会使用另外的一些IO作为 EPCS 连接脚?有点晕!对cyclone3配置时,程序就是写不进去!目前来说问题出在一、核电压没有加上(vccint=1.2v)。

二、PLL的供电电压也没有加上(vcca=2.5v)。

三、配置引脚所用的BANK对应的电压也没有加上(vccio=3.3v)。

于是我注定写不进程序啊!!!DATASHEET中发现,这三个引脚一个不能少,这样子才能配置成功!另外的一些收获也记录一下吧。

一、有若干种配置模式,比如FAST AS,STANDARD AS等等,这个由MSEL【3:0】来设定。

二、VCCA is the analog power to the phase-locked loop (PLL).三、When using a JTAG configuration scheme or a serial configuration device in an AS configuration scheme, you must connect a 25ou series resistor at the near end of the TDO and TDI pin or the serial configuration device for the DATA[0]pin.四、After POR, the Cyclone III device family releases nSTATUS, pull-up resistor and enters which is pulled high by an external 10-k configuration mode.When nCONFIG goes high, the device exits reset and releases the open-drainnSTATUS pin, which pull-up resistor. After Ωis then pulled high by an external 10-k nSTATUS is released, the device is ready to receive configuration data and the configuration stage begins.五、ConfigurationConfiguration data is latched into the Cyclone III device family at each DCLK cycle.However, the width of the data bus and the configuration time taken for each schemeare different. After the device receives all the configuration data, the device releasesthe open-drain pull-up ΩCONF_DONE pin, which is pulled high by an external 10-kresistor. A low-to-high transition on the CONF_DONE pin indicates that configurationis complete and initialization of the device can begin. The CONF_DONE pin must havepull-up resistor for the device to initialize.Ωan external 10-kYou can begin reconfiguration by pulling the nCONFIG pin low. The nCONFIG pinmust be low for at least 500 ns. When nCONFIG is pulled low, theCyclone III devicefamily is reset. The Cyclone III device family also pulls nSTATUS and CONF_DONE lowand all I/O pins are tri-stated. When nCONFIG returns to a logic-high level andnSTATUS is released by the Cyclone III device family, reconfiguration begins.六、User ModeAn optional INIT_DONE pin is available that signals the end of initialization and thestart of user mode with a low-to-high transition. The Enable INIT_DONE Outputoption is available in the Quartus II software from the General tab of the Device andPin Options dialog box. If you use the INIT_DONE pin, it is high due to an external10-k pull-up resistor when nCONFIG is low and during the beginning ofconfiguration. After the option bit to enable INIT_DONE is programmed into thedevice (during the first frame of configuration data), the INIT_DONE pin goes low.When initialization is complete, the INIT_DONE pin is released and pulled high. Thislow-to-high transition signals that the device has entered user mode. In user mode,the user I/O pins function as assigned in your design and no longer have weakpull-up resistors.七、整个过程应该是program>>configuration>>initialiaition.进入user mode。

Altera Cyclone III系列FPGA开发板简介

ETL-002 Altera Cyclone III系列FPGA开发板简介概述ETL-002 FPGA开发板是以Altera公司的最新系列Cyclone III中的3C10为主芯片,并提供了极为丰富的芯片外围接口资源以及下载线,数据线以及资料光盘等。

除了这些硬件外,我们还提供了十多个接口实验,并公开了电路原理图和实验的Verilog源代码,以便于大家对照学习,并可以在该开发板上进行二次开发。

单板描述主芯片EP3C10提供了10320个逻辑单元(LE),46块SRAM(每块9K bits), 23个18*18的乘法器。

开发板自带USB供电电路:您只需将USB线插上您的USB端口,无需外接+5V直流电源,开发板即可工作。

开发板同时支持AS模式下载和JTAG模式下载。

程序固化既可通过JTAG口也可直接对板上的FLASH进行编程。

丰富的外围接口可满足常用的外设的人机交互,我们还将剩下未用的40个用户I/O引脚全部引出,使得您可以通过这些信号对本开发板进行电路扩展。

这些接口主要包括:PS2鼠标接口:可以将PS2鼠标的任何移动的信息反应在数码管上PS2键盘接口:可以将PS2键盘上的任意按键以16进制的信息反应在数码管上VGA显示器接口:可以将FPGA产生的信息反映在VGA显示器上。

开发板自带了动态彩条显示的功能双串口接口:可以与任何的串口设备相接。

开发板自带的演示程序是将PC上的超级终端中输入的任何信息返回PC 4位数码管:可以实时显示任何的数字信息。

开发板自带的演示程序实时地显示分钟和秒钟的信息。

4位LED灯:用于指示状态。

开发板自带了跑马灯实验。

4位按键开关:可用于复位等作用。

4位拨码开关:可用于电路的选择作用教学实验除了开发板的丰富的硬件资源外,我们还提供了数十个学习实验。

通过这些实验,您可以学习FPGA芯片,Quartus II软件和设计仿真和下载等FPGA的设计流程,然后将试验中程序执行的信息通过数码管,LED 灯,串口等板上的硬件直观的显示出来。

Cyborg v3震动手柄

赛钛客Cyborg V 3振动手柄特点

赛钛客的Cyborg V 3手柄是目前国内唯一支持PS3\PS2\PC三平台并支持第一称射击游戏的 手柄 更加舒适的PS外形的手柄。 独有的专利技术可更换方向键的手柄,满足不同使用习惯。 全球唯一带线性的L2和R2键PC手柄。 全球唯一带有FPS游戏切换功能的手柄,可使手柄功能翻倍。 全球唯一可改小摇杆移动速度的手柄。对于赛车游戏细腻控制方向,精准的射击有极 大的帮助。 全球唯一含带鼠标功能,可支持第一称射击类游戏。 支持强大的SST软件功能,可实现将一连串的动作设置在一个键上来实现一键大招等。 超级耐用及灵活的方向键。 高细腻精准的防滑双摇杆。 全球唯一支持任何PC、PS3、PS2游戏的手柄。

• • • • • • • • • •

系统支持及售后

接口类型:USB,支持即插即用、PS3\PS2接口 适用操作系统:

推荐游戏软件:FIFA足球、实况足球 NhomakorabeaNBA篮球、极品飞车、 刺客信条、网游地下城与勇士、光线飞车、路尼亚战记等 所有可在电脑、PS3、PS2游戏机上使用的游戏。 售后服务:一年质保

赛钛客Cyborg V 3振动手柄---参数

官方零售价: 官方零售价:349元 元 • • • • • • • • • • •

手柄参数

支持PS3及PS2、PC三平台 独有可更换方向键功能 预置FPS按键 ,直接支持第一人称射 击游戏。 独有精准模式设置 ,更有利于射击 游戏。 2个快速开火侧翼扳机 2个带线性的模拟扳机 2个摇杆下压按键(L3\R3) 2个高精度模拟摇杆 4功能按键 2个菜单控制按键(back\start) PS HOME按钮

Cyclone III资料

Cyclone III原型开发调试转载:/ilove314/1819329/Message.aspx 最近设计的Cyclone III原型板是特权同学第一次接触Cyclone III的器件。

原理图、PCB绘制、管脚分配上都碰到了一些问题,这些问题或多或少都是由于个人对新器件不熟悉、设计的时候有一些粗心大意造成的。

主要针对板级的硬件设计,这里凌乱的罗列一下,做一点总结,今后要多吸取教训,低级的失误要尽量避免。

1. 首先要提一个没有解决的问题,EP3C5E144/EP3C10E144/ EP3C16E144/ EP3C 25E144(是管脚完全兼容的不同资源的器件,Altera在这一点上是非常值得称道的)器件的PIIN11和PIN12存在不可同时使用的问题,这个问题出现在架构了一个NIOS2系统里集成了EPCS控制器的时候,在Cyclone II中是不需要分配这个EPCS控制器的管脚的(内部自动映射),而Cyclone III则需要手动分配(事先需要到Setting里动动手脚)。

EPCS的DCLK需要分配到PIN12上,工程中分配了一个SDRAM的D0脚给PIN11,编译到Fitting阶段就Error了。

在handbook里海找没什么成效,求助于搜索引擎,最终看到有人遇到相同的问题,但是给出的却是不是办法的解决办法:不用PIN11或者不用PI N12。

这个问题上特权同学也很是无可奈何,估计是Cyclone III器件的这两个脚做了一些信号耦合之类的检查,也不知道是否在工具选项里做一些设置可以取消此类检查。

也很期待有相同遭遇的朋友现身说法,告诉特权如何解决问题。

2. 再说两个很低级的错误,错的很傻,没有什么技术含量,只能给自己敲个警钟:干活的时候脑子一定要清醒。

两个错误分别和BOM表和网络标号有关。

先说和BOM表有关的,这个错误源于原理图上两个三端稳压器-1.2和-2.5的标示刚好反过来了,因为管脚定义和封装都一样所以也没留意,好在最后只影响BOM表的标示,但这也导致了第一块样板焊接的时候出现了1.2V和2.5V互换位置的惨剧,结果可想而知,EP3C10E144C7就这样挂了,非常的心疼。

将两层板进行到底,搞起CycloneIII

将两层板进行到底,搞起CycloneIII我以前DIY过两个FPGA的板子,都是Altera Cyclone II的。

几年前就买了的几片Cyclone III EP3C10一直没动,除了还没有DIY 项目必须要用到它外,还有个原因是Cyclone III系列需要3组电压供给,在两层板上走线不太好弄。

我也看到过别人在用两层PCB做的Cyclone III的设计,能跑起来说明也不是不可行。

今年已经DIY过两个带SDRAM的MCU板子,都是两层PCB。

这次我继续挑战一下,在两层板上把EP3C10加SDRAM搞起来,打算玩一玩NIOS II. 经过长时间的Layout斟酌,上个月总算把这个PCB 做出来了。

和我的前两个FPGA实验板不同的是,我这次设计成了核心板的形式,只保留FPGA+SDRAM以及必要的外围元件,把扩展GPIO接口和应用相关的接口件都挪到扩展板上去。

核心板和扩展板使用2.0 pitch的双排针/座来连接。

做出来是这个效果(简单做了几个2.54排针,以及JTAG座扩展卡):比如只需要用USB Blaster进行JTAG下载的时候,是这样用的(示意一下,另外还需要连3.3V电源)板子的背面:有2.5V和1.2V的LDO, 都是小封装的。

SDRAM还没有焊,待我把NIOS玩起来了再焊它调试。

扩展的排插是2.0 pitch,一方面是减小体积,另一方面是这种双排母比常见2.54的排母接触好。

正面:晶振也用3225的,比7050的省地方。

我手头恰好没有3225了,就焊了个2520更小尺寸的。

右边白色的插座是1.25 pitch 的连接器,可接6pin排线,用于少量I/O的扩展,连其它板子。

原理图:还是用我DIY一贯的EagleCyclone III 需要至少3组电压:1.2V的VCCINT, 2.5V的VCCA,以及平常3.0/3.3V的VCCIO. SDRAM只用到3.3V.Layout费了番心思。

cyclone3引脚整理

FLASH_nC E, nCSO

I/O, Output(A S, AP Note 13

DATA1, ASDO

PLL[1..4 ]_CLKOUT p Note 3

I/O, Output

Clock, Input

来自于 PLL [1..4]. 的可选 positive 正端外部 时钟输出 。该引脚 如果被用 作PLL输 出,能被 指定为单 端或差分 I/O标准 。

专用全局 时钟输入 引脚,用 于差分全 局时钟输 入或用户 输入引脚 的 negative 负端输入 。不支持 编程弱上 拉电阻。 不使用时 连接到 GND,注9.

MSEL[0.. 3]

Input

配置输入 引脚,用 来设置 Cyclone III 设备 配置方案 。一些较 小的设备 或包装选 项不支持 AP注 13flash 编程,不 使用 MSEL3引 脚。

这些引脚 内部连接 5-KΩ resistor to GND。 当未被使 用时,连 接至GND, 不悬空。 Device Family Handbook :配置, 设计安全 性, Cyclone III Devices 远程系统 升级。如 果使用 JTAG 配 置,连到 GND.

nCE 应 该接到 模式,则 GND

CONF_DON E

Bidirect ional (opendrain)

专用配置 状态引 脚,随着 状态输 出,在配 置前和配 置期间, CONF_DON E pin drives low 当状态输 入,所有 数据被接 收后, CONF_DON E变为高 。然后设 备初始 化,进入 用户使用 模式。该 引脚不可 做I/O引 脚,引脚 应被拉 高,通过 上拉电阻 被释放。 10-KΩ.

Cyclone III FPGA Starter Kit User Guide

101 Innovation DriveSan Jose, CA 95134Cyclone III FPGA Starter KitUser GuideDocument Version: 1.2Document Date: July 2010P25-36228-03© 2010 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Reg. U.S. Pat. & Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trademarks and service marks are the property of their respective holders as described at /common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of devicespecifications before relying on any published information and before placing orders for products or services.Part Number UG-01018-1.2ContentsChapter 1. Getting StartedIntroduction............................................................................................................................................1–1 Before You Begin...................................................................................................................................1–2 Further Information..............................................................................................................................1–2 Software Installation.............................................................................................................................1–2 Installing the Cyclone III FPGA Starter Kit..................................................................................1–2 Installing the Quartus II Web Edition Software..........................................................................1–4 Chapter 2. Development Board and Control Panel SetupDevelopment Board Setup...................................................................................................................2–1 Requirements....................................................................................................................................2–2 Powering Up the Development Board..........................................................................................2–2 Installing the USB-Blaster Driver........................................................................................................2–2 Control Panel Setup...............................................................................................................................2–3 Configuring the FPGA Using the Quartus II Programmer.............................................................2–3 Chapter 3. Using the Control PanelOverview.................................................................................................................................................3–1 Control Panel Start................................................................................................................................3–1 LEDs and Buttons..................................................................................................................................3–2 Illuminating LEDs............................................................................................................................3–2 Buttons Indicators............................................................................................................................3–3 DDR SDRAM/SSRAM/On-Chip Controller...............................................................................................................3–3 Read/Write Data..............................................................................................................................3–4 Read from a File................................................................................................................................3–5 Write to a File...................................................................................................................................3–5 Flash Memory Programmer.................................................................................................................3–5 Flash Memory Tab...........................................................................................................................3–6 CFI Query..........................................................................................................................................3–6 Read/Write Data..............................................................................................................................3–7ContentsChapter 4. Measuring Power on the Cyclone III Starter BoardIntroduction............................................................................................................................................4–1 Measuring Power...................................................................................................................................4–2 Changing the Example Design.......................................................................................................4–3 Appendix A. Programming the Configuration Flash DeviceOverview................................................................................................................................................A–1 Creating a Flash-Programmable POF File........................................................................................A–1 Programming the Flash Device..........................................................................................................A–5 Additional InformationRevision –i How to Contact –ii Typographic –ii1.Getting StartedIntroduction Welcome to the Altera® Cyclone®III FPGA Starter Kit, which includes afull-featured field-programmable gate array (FPGA) development board,hardware and software development tools, documentation, andaccessories needed to begin FPGA development.The development board includes an Altera Cyclone III FPGA and comespreconfigured with a hardware reference design stored in flash memory.You can use the development board as a platform to prototype a varietyof FPGA designs.The starter kit provides an integrated control environment that includesa software controller in a control panel application, a USB commandcontroller, a multi-port SRAM/DDR SDRAM/flash memory controller,and example designs specified in Verilog code. You can use this design asa starting point for test designs.This user guide addresses the following topics:■How to set up, power up, and verify correct operation of thedevelopment board.■How to install the Cyclone III FPGA Starter Kit.■How to install the Altera® Quartus II Web Edition software.■How to set up and use the control panel, a graphical user interface(GUI), to manipulate components on the board, implementapplications.■How to configure the Cyclone III FPGA.■How to set up and run example designs.f For complete details on the development board, refer to theCyclone III FPGA Starter Board Reference Manual.Before You BeginBefore You Begin Before proceeding, check the contents of the kit:■Cyclone III FPGA Starter Development Board ■12-V DC power supply■USB cablef For the most up-to-date information on this product, visit the Alterawebsite at /products/devkits/altera/kit-cyc3-starter.html.FurtherInformationFor other related information, refer to the following websites:Software Installation This section describes the following procedures:■“Installing the Cyclone III FPGA Starter Kit”■“Installing the Quartus II Web Edition Software” on page1–4 Installing the Cyclone III FPGA Starter KitThe license-free Cyclone III FPGA Starter Kit installer includes all the documentation and design examples for the kit.To install the Cyclone III FPGA Starter Kit, follow these steps:1.Download the Cyclone III FPGA Starter Kit installer from theCyclone III FPGA Starter Kit page of the Altera website.Alternatively, you can request a development kit DVD from theDevelopment Kits, Daughter Cards & Programming Hardware page of the Altera website.For More Information About Refer ToAdditional daughter cardsavailable for purchase/products/devkits/kit-daughter_boards.jspCyclone III handbook /literature/lit-cyc3.jspCyclone III reference designs /products/devkits/altera/kit-cyc3-starter.htmleStore if you want topurchase devices/buy/devices/buy-devices.htmlCyclone III Orcad symbols /support/software/download/pcb/pcbpcb_index.htmlNios® II 32-bit embeddedprocessor solutions/technology/embedded/emb-index.htmlGetting Started 2.Follow the on-screen instructions to complete the installationprocess.The installation program creates the Cyclone III FPGA Starter Kit directory structure shown in Figure1–1.Figure1–1.Cyclone III FPGA Starter Kit Default Installed Directory StructureTable1–1 lists the file directory names and a description of their contents.Table1–1.Installed Directory ContentsDirectory Name Description of Contentsboard_design_files Contains schematic, layout, assembly, and bill of materialboard design files. Use these files as a starting point for anew prototype board design.demos Contains demonstration projects that may or may notcontain up-to-date source code.documents Contains the development kit documentation.examples Contains the example design files for the Cyclone III FPGAStarter Kitfactory_recovery Contains programming files for returning board to factorydefault condition.Software InstallationInstalling the Quartus II Web Edition SoftwareThe Quartus II Web Edition software provides the necessary tools fordeveloping hardware and software for Altera FPGAs. Included in theQuartus II Web Edition software are the Quartus II software, the Nios IIEDS, and the MegaCore® IP Library. The Quartus II software (includingSOPC Builder) and the Nios II EDS are the primary FPGA developmenttools for creating the reference designs in this kit.To install the Quartus II Web Edition software, follow these steps:1.Download the Quartus II Web Edition software from the Quartus IIWeb Edition Software page of the Altera website. Alternatively, youcan request a DVD from the Altera IP and Software DVD RequestForm page of the Altera website.2.Follow the on-screen instructions to complete the installationprocess.f If you have difficulty installing the Quartus II software,refer to Quartus II Installation & Licensing for Windows andLinux Workstations.The Quartus II Web Edition software includes the following items:■Quartus II software—The Quartus II software, including the SOPCBuilder system development tool, provides a comprehensiveenvironment for system-on-a-programmable-chip (SOPC) design.The Quartus II software integrates into nearly any designenvironment and provides interfaces to industry-standard EDAtools.f To compare the Quartus II subscription and web editions,refer to Altera Quartus II Software—Subscription Edition vs.Web Edition. The kit also works with the subscriptionedition.■MegaCore IP Library—A library that contains Altera IP MegaCorefunctions. You can evaluate MegaCore functions with the OpenCorePlus feature to perform the following tasks:●Simulate behavior of a MegaCore function in your system●Verify functionality of your design, and quickly and easilyevaluate its size and speed●Generate time-limited device programming files for designs thatinclude MegaCore functions●Program a device and verify your design in hardwareGetting Started 1The OpenCore Plus hardware evaluation feature is anevaluation tool for prototyping only. You must purchase alicense to use a MegaCore function in production.f For more information about OpenCore Plus, refer toAN320: OpenCore Plus Evaluation of Megafunctions.■Nios® II Embedded Design Suite (EDS)—A full-featured tool set that allows you to develop embedded software for the Nios II processor which you can include in your Altera FPGA designs.Licensing ConsiderationsThe Quartus II Web Edition software is license-free and supports Cyclone III devices without any additional licensing requirement. This kit also works with the Quartus II Subscription Edition software, after you obtain the proper license file. To purchase a subscription, contact your Altera sales representative.Software Installation2.Development Board andControl Panel Setup DevelopmentBoard SetupThe development board is preloaded with an example design todemonstrate the Cyclone®III device and board features. At power-up,the preloaded design also enables you to quickly confirm that the boardis operating correctly.Figure2–1 shows the Cyclone III development board layout andcomponents.Figure2–1.Cyclone III Development Board Layout and Components1-Mbyte SSRAM (U5)DC PowerInput (J2)Power Switch (SW1)16-MbyteParallelFlash (U6)ConnectorFlash LEDUSBUART (U8)JT AG Header (J4)32-MbyteDDR SDRAM (U4)Reconfigureand ResetPush Buttons50-MHzSystem ClockUser LEDsUser Push Button SwitchesHSMCConnector (J1)Cyclone III Device (U1)Configuration Done LEDSense Resistor for FPGACore Power Measurement (JP6)Sense Resistorfor Shared I/OAltera Corporation 2–1Installing the USB-Blaster DriverRequirementsBefore you proceed, ensure that the follwing items are installed:■Altera® Quartus®II software on the host computer■Cyclone III FPGA Starter Kit■USB-Blaster™ driver software on the host computer. TheCyclone III FPGA starter development board includes an integratedUSB-Blaster circuitry for FPGA programming.Powering Up the Development BoardTo power-up the development board, follow these steps:1.Ensure that the ON/OFF switch (SW1) is in the OFF position (up).2.Connect the USB-Blaster cable from the host computer to theUSB-Blaster port on the development board.3.Connect the 12-V DC adapter to the development board and to apower source.w Only use the supplied 12-V power supply. Power regulationcircuitry on the board could be damaged by supplies greaterthan 12V.4.Press the power switch (SW1).5.Confirm that all four user LEDs are ON.Installing the USB-Blaster Driver The Cyclone III FPGA development board includes an integratedUSB-Blaster circuitry for FPGA programming. However, for the host computer and board to communicate, you must install the USB-Blaster driver on the host computer.Installation instructions for the USB-Blaster driver are available on the Altera website at /support/software/drivers/dri-index.html. On the “Altera Programming Cable Driver Information” page of the Altera website, locate the table entry for your configuration and click the link to access the instructions.2–2Altera CorporationDevelopment Board and Control Panel SetupControl Panel Setup Setting up the control panel involves the following:■Configuring the FPGA■Starting the control panel1Power up the board and ensure that is is operational.For more information about using the control panel, refer to the “Using the Control Panel” chapter.Configuring the FPGA Using the Quartus II Programmer You can use the Quartus II Programmer to configure the FPGA with a specific .sof. Before configuring the FPGA, ensure that the Quartus II Programmer and the USB-Blaster driver are installed on the host computer, the USB cable is connected to the development board, power to the board is on, and no other applications that use the JTAG chain are running.To configure the Cyclone III FPGA, follow these steps:1.Start the Quartus II Programmer.2.Click Add File and select the path to the desired .sof.3.Turn on the Program/Configure option for the added file.4.Click Start to configure the selected file to the FPGA. Configurationis complete when the progress bar reaches 100%.Altera Corporation 2–3Configuring the FPGA Using the Quartus II Programmer2–4Altera Corporationing the Control PanelOverview The control panel consists of the following:■The graphical user interface (GUI) application on the host computer■The standard Nios II hardware design running on the board'sCyclone III FPGA deviceAfter installing the Cyclone III FPGA Starter Kit, you can locate thecontrol panel for the hardware and software in the<kit path>\demos\control_panel directory.The design downloaded to the Cyclone III device implements acommand controller that processes board commands sent over theUSB-Blaster from the control panel. To perform the appropriate actions,the command controller communicates with the controller of the targetedboard I/O device.You can perform the following actions with the control panel:■Light up LEDs■Detect push button presses■Read from and write to the DDR SDRAM, SRAM, flash memory, andon-chip RAMThe following sections describe how to perform the above actions withthe control panel already open on the host computer. If not already open,launch the control panel as described in “Control Panel Start”.Control Panel Start The Cyclone III development board is shipped with an example design stored in the flash memory which configures the Cyclone III FPGA upon power-up with the standard Nios II design.1For an older version of the Cyclone III development board shipped with the Cyclone III FPGA Starter Kit v7.1.0, v7.2.0, or8.0.0 application, you must manually configure thecycloneIII_3c25_start_niosII_standard.sof into the FPGAbefore launching the control panel application.Altera Corporation 3–13–2Altera Corporation LEDs and ButtonsYou can locate the source for the example design in the <kitpath>\examples\cycloneIII_3c25_starter_board_standard directory. 1To launch the control panel user interface, run thecontrol_panel.exe program found in the <kitpath >\demos\control_panel directory (Figure 3–1).Figure 3–1.Control Panel WindowLEDs andButtons Illuminating LEDs To illuminate an LED, follow these steps:1.The LED & Buttons tab should be visible when the application runs.If it is not visible, click the LED & Buttons tab (Figure 3–2).2.Click on LEDs to individually turn on the LEDs.Using the Control PanelButtons Indicators1.Press the push-button switches on the board. Notice that buttons onthe GUI change accordingly.Figure3–2.Control Panel Window for LEDs and ButtonsDDR SDRAM/ SSRAM/On-Chip Controller You can perform the following types of memory read/write operations with the control panel:■Read from and write to the DDR SDRAM, SSRAM, or on-chip device ■Write entire contents of a file, to the DDR SDRAM, SSRAM, or on-chip device■Read contents of the DDR SDRAM, SSRAM, or on-chip device, to afileAltera Corporation 3–33–4Altera Corporation DDR SDRAM/ SSRAM/On-Chip ControllerThe following sections describe how to access the DDR SDRAM. You can use the same procedure to access the SSRAM.Read/Write DataTo read from and write to the DDR SDRAM, follow these steps:1.Click the DDR SDRAM tab (Figure 3–3). The Address columnindicates the hex address of the DDR SDRAM. The values inside the 0-3, 4-7, 8-B , and C-F columns are the DDR SDRAM contents in hex words format.Figure 3–3.Control Panel DDR SDRAM Tab2.To write a 32-bit word to the DDR SDRAM, click the desiredlocation, enter the desired value in hex format, and press Enter.Using the Control PanelRead from a FileTo read the contents of a file and load it to the DDR SDRAM, follow these steps:1.Click Load File.2.Browse to sample.txt located in the control_panel directory andclick Open. This step instantiates the DDR SDRAM controller and loads the text contents into the DDR SDRAM. Notice that the Data to Ascii-text column shows the DDR SDRAM contents in Asciivalue.Write to a FileTo write the contents of the DDR SDRAM to a file, follow these steps:1.Click Save File.2.Enter the start and end addresses of the DDR SDRAM.3.Choose a file name and click Save. This instantiates the controller toread the DDR SDRAM contents from the start address to the endaddress, and write the contents to a file.Flash Memory Programmer You can perform the following operations to read from and write to the board’s flash memory with the control panel:■Perform a CFI query of flash memory■Erase select blocks of flash memory■Write 32-bit hex word to flash memory■Write a binary file to flash memory■Load the contents of the flash memory into a filec Do not exit from the control panel while erasing the flashmemory.Altera Corporation 3–5Flash Memory ProgrammerFlash Memory TabTo use the flash memory functions, click the Flash Memory tab(Figure3–4).Figure3–4.Control Panel Flash Memory TabCFI QueryThe common flash interface (CFI) flash memory devices conform to basicflash commands. The most basic command is Query which switches thedevice into a ROM table mode so that features of the flash device aredetermined by reading values from the table.To perform a CFI query using the host application, click CFI Query.Notice that the memory table displays contents that correlate with thetable contents as described in the device datasheet.To put the flash device back in user mode, press Reset on the controlpanel.3–6Altera CorporationAltera Corporation 3–7Using the Control PanelRead/Write DataTo read from and write to the flash memory, follow these steps:Figure 3–5.Control Panel Flash Memory Tab1.Click Erase Block to perform a block erase of the flash memory. The Address column indicates the hex address of the flash memory. The values inside the 0-3, 4-7, 8-B , and C-F columns are the flash memory contents in hex words format.2.To write a 32-bit word to the flash memory, click the desired location, enter the desired value in hex format, and press Enter.Flash Memory Programmer3–8Altera Corporation4.Measuring Power on theCyclone III Starter BoardIntroduction One of the main features of the Cyclone®III device is its low powerconsumption. You can measure the power of the 3C25 device on theCyclone III starter board under various conditions with an exampledesign provided with the kit.The power example design allows you to control the amount of logicutilized in the FPGA, the clock frequency, the number of I/Os being used,and measure the effect on the power to the Cyclone III device. Because theCyclone III starter board has only four buttons and four LEDs, interactionwith the board is minimal as defined below.Table4–1 describes the functionality of the four input buttons that controlthe power example design.Tables4–2 and 4–3 describe how the LEDs indicate the example design’scurrent power state.Table4–1.Four Input Button FunctionalityButton FPGA Pin Type Description1F1Reset Resets the demo to the beginning, nodei_nrst.2F2Toggle Advances the example design to the next higherfrequency, node i_nfreq_next.3A10Toggle Advances the example design to the next higherresource utilization, node_i_nperc_next.4B10Press and Hold Enables the outputs to toggle, nodei_noutput_ena.Table4–2.LEDs Power State (Frequency)DisplaysLEDsStateClock Frequency(MHz)MSB LSBFrequency LED2 LED10000133106711100Altera Corporation 4–14–2Altera CorporationMeasuring PowerThe design used for power measurement is a replicated set of randomly filled ROMs that feed a multiplier block and a shift register that is fed by a signal that changes every clock cycle. Tables 4–2 and 4–3 show the power state which represent the percent of the full design used. As compiled, this full design uses:■Logic elements: 22,493/24,624 (91%)■Combinational functions: 1,961/24,624 (8%) ■Dedicated logic registers: 21,133/24,624 (86%) ■Total registers: 21,133 ■Total pins: 73/216 (34%)■Total memory bits: 524,288/608,256 (86%)■Embedded Multiplier 9-bit elements: 128/132 (97 %)■Total PLLs: 1/4 (25%)Measuring PowerThe example design is located in<kit install >\examples\cycloneIII_3c25_start_power_demo . Configure the FPGA with the .sof found in the directory. 1The input clock (i_clk PIN_B9) is the 50-MHz oscillator on the board, which generates the input clock for the reference design through a PLLfFor more information on configuring the FPGA, refer to “Configuring the FPGA Using the Quartus II Programmer” on page 2–3.Current sense resistors (0.010 ± 1%) are installed at locations JP6 (FPGA core power) and JP3 (FPGA I/O power + other device I/O power). With a digital multimeter set to mV measurement range, the resistor at location JP6 measures the core power. The resistor at location JP3 measures the I/O power. To measure the current being used in various configurations, use the following steps:Table 4–3.LEDs Power State (Resources)DisplaysLEDsState% of Design UsedMSBLSBResourcesLED4LED30025%0150%1075%11100%Measuring Power on the Cyclone III Starter Board1To obtain the power (P) in milliwatts, measure <MeasuredVoltage> (the voltage across the sense resistors at JP6 or JP3) inmV and calculate the nominal power using the equation:P = 100 x <Measured Voltage> x <Supply Voltage>where <Supply Voltage> is 1.2 V for JP6 and 2.5 V for JP3.You can use the four input buttons to advance through the various powerstate as outlined in Table4–2. Notice how current increases as frequencyand resource usage increase.You can also measure the I/O power consumed by measuring the voltageacross sense-resistor JP3 when Button 4 is pressed and held. Because this2.5-V power rail is shared with other devices, there is a nominal 100mWthat must be subtracted from the calculated I/O power to obtain theFPGA I/O power.The number of I/O pins used is controlled by the resource state (shownin Tables4–2 and 4–3). For each increment in resources, 16 additional I/Opins are added (refer to Table4–4).Table4–4.I/O Pin & Resource StateLED4/LED3Number of I/O Pins0016013210481164Similarly, the toggle-frequency of these I/O pins is set by the overalldesign frequency (refer to Table4–1).Changing the Example DesignThe source code for the Cyclone III power example design is alsoprovided so you can use it as a starting point for your own measurements.You can adjust the number of outputs by changing parameterNUM_OUTPUTS_PER_STAMP. The default is 16, which for four resourcepercentage steps equates to 16 x 4 = 64.The appropriate pins to be used as outputs are pre-assigned to the HSMCconnector (J1). If you would like to look at more than the 76 I/Os availableon J1, you need to make the appropriate pin assignments.Altera Corporation 4–3。

CycloneFPGA配置模式及应用

摘要:本文主要通过介绍Cyclone 系列FPGA 器件的配置方案,主要阐述了低成本专用配置芯片的主动串行(AS )配置方案以及基于微处理器的被动串行(PS )配置方案的配置过程。

介绍了如何结合工程设计选择配置方案,改变现在的任意选择配置方案的现象。

提出一种实时解压数据减少贮存要求和配置时间的配置方案,这些方案在工程项目中具有很高的实际应用价值。

关键词:Cyclone FPGA 配置模式主动串行被动串行0引言FPGA 是英文Field -Programmable Gate Array 的缩写,即现场可编程门阵列,它是在PAL 、GAL 、CPLD 等可编程器件的基础上进一步发展的产物。

FPGA 技术广泛应用于通讯、视频、信息处理等特定领域。

FPGA 主要生产厂商有Altera 、Xilinx 、Actel 和Lattice ,对比不同的FPGA 编程技术特点,综合各个厂家不同系列器件的技术优势、逻辑资源、器件功耗、芯片速度、供货、价格和系统要求等诸多因素考虑,在很多项目设计中采用Altera 公司基于SRAM 架构Cyclone 系列器件。

Cyclone 器件与其他FPGA 器件一样是基于门阵列方式为用户提供可编程资源的,其内部逻辑结构的形成是由配置数据决定的。

这些配置数据可通过多种模式加载到FPGA 内部的SRAM 中,由于SRAM 的易失性,每次上电时,都必须对FPGA 进行重新配置。

1Cyclone FPGA 配置模式Cyclone 系列FPGA 器件配置方案主要有三种,包括使用低成本配置芯片的主动串行(AS )配置、被动串行(PS )配置以及基于JTAG 配置,实际应用时可以使用其中的一种方案配置Cyclone 系列FPGA 器件,来实现用户编程所要实现的功能。

Cyclone 系列FPGA 器件是用SRAM 单元配置数据的。

由于SRAM 掉电后容易丢失数据,配置数据必须即时地下载到上电的Cyclone 器件中。

Cyclone III中LVDS的设计

Cyclone III中LVDS的设计一,概述LVDS低压差分信号,最早由美国国家半导体公司提出的一种高速串行信号传输电平,由于它传输速度快,功耗低,抗干扰能力强,传输距离远,易于匹配等优点,迅速得到诸多芯片制造厂商和应用商的青睐,并通过TIA/EIA的确认,成为该组织的标准(ANSI/TIA/EIA-644 standard)。

LVDS信号被广泛应用于计算机、通信以及消费电子领域,并被以PCI-Express为代表的第三代I/O标准中采用。

LVDS信号的电压摆幅只有350MV,为电流驱动的差分信号方式工作,最长的传输距离可以达到10米以上。

为了确保信号在传输线当中传播时,不受反射信号的影响,LVDS信号要求传输线阻抗受控,其中单线阻抗为50ohms,差分阻抗100ohms。

在实际应用当中,利用一些高速电路仿真分析工具,通过合理的设置层叠厚度和介质参数,调整走线的线宽和线间距,计算出单线和差分阻抗结果,来达到阻抗控制的目的。

LVDS的工作原理是其中发送端是一个为3.5mA的电流源,产生的3.5mA的电流通过差分线的其中一路到接收端。

由于接收端对于直流表现为高阻,电流通过接收端的100欧姆的匹配电阻产生350mV的电压,同时电流经过差分线的另一条流回发送端。

当发送端进行状态变化时它通过改变流经100欧姆电阻的电流的方向产生有效的'0'和'1'态。

二,硬件设计为了达到阻抗控制的要求,PCB的设计采用常见的4层板,基本叠层结构如下图:板子的总体厚度约为1.6mm,L1,L4为信号层,L2,L3分别为地线层和电源层,半固化片采用2116,根据CTS的计算,选取差分线线宽6mil,间距8mil,信号层铺铜厚度为0.5OZ(完成后约为高度48um),可以达到差分阻抗约100欧姆。

在CIII芯片中,有多组可以输出LVDS信号的IO,但有几点需要注意。

在芯片的right bank,left bank上,也就是1,2,5,6 bank,设计了“dedicated output buffer”,这些IO不要添加其他器件既可以输出LVDS信号,也就是说不需要做任何电阻网络匹配的工作了。

Cyclone_III配置

Cyclone_III配置Cyclone III 的配置全文翻译自Altera公司Cyclone III的器件手册。

所有表格与图标标号与手册原文一致,以便于查对。

出于个人需要,仅翻译了AS与JTAG配置两部分,且仅都配置一片FPGA芯片。

可以通过压缩数据的方法以节约存储空间,并节省程序load时间(page 220);9通过Remote System Upgrade方式可以减少新产品面市的时间(page 221);9AS Configuration(Serial Configuration Devices)表10-6显示的是对各种配置电平来说,MSELx管脚的接法单一器件配置四个接口管脚包含了串口时钟(DCLK),串行数据输出(DATA),AS 数据输入(ASDI),以及低电平有效的片选信号(nCS)。

注:1)上拉一个电阻,连接到该管脚所在的bank的VCCIO;2)Cyclone III器件通过DATA[1]-to-ASDI路径控制配置芯片;3)nCEO管脚浮空,或者当没有连接到另一个器件的nCE管脚时,可以当作通用IO使用;4)MSEL管脚的设置,用于选择不同的电平标准和不同的POR时间;参考表10-6,选择接法;5)这些是复用管脚。

FLASH_nCE管脚在AS配置电路图中当作nCSO功能使用,DATA[1]管脚当作ASDO功能使用;6)这些串接的电阻尽可能靠近配置芯片当连接一个配置芯片到Cyclone III器件时,DATA[0]管脚必须串一个电阻,并应接近配置芯片。

配置器件和Cyclone III芯片间连线的长度应符合表10-8所推荐的值。

当选择AS配置方式的时候,BAMK 1的IO电压必须是3.3,3.0或2.5。

上电以后,CIII器件有一个POR时间的延迟,在此期间,nSTATUS和CONF_DONE 会一直为低,所有的IO也都是三态输出。

芯片配置的三个阶段分别是复位,配置和初始化。

CycloneⅢ系列FPGA器件的硬件设计

需要 的资 源做 一个估算 。 () 2RAM资源 为4 4 0 9 i,rm块 的大 l ~7 1Kbt a

小都 是9 i。 Kbt

( ) 2 ~3 6 1 位 的乘 法器 ,每 个 3具有 3 9 个 1 位 8 8 l 位 的乘法 器 也 可 以分 成 两个 9 9 的 乘 8 1位 8 位 位

芯 片配 置 ,电源部 分 的 处理 ,C K引脚 、多功 能 L 引脚 以及虚 拟 引脚 的复 用 ,器件 的安 全 加密 等 方 面进行 了论述 ,给 出了实 际的设计 方法及 步骤 。

比较 困难 。一 般认为 使用 8% 右是 比较合 适 的。 0左

() y ln I L 是5 2 0 1C co e II E K到 0 K。针对对 设计

同的器件 可 以直接替 换 使用 。 当然都得 是 C co e y ln

也可 以采用 智 能主机 ,如 微处 理器 来模 拟J TAG时

序 进行 配置 。 为 了方便 调 试 可 以采 用 AS TAG的配置 方 +J

II I的器 件 。这 样 的好 处在 于 ,初 期设 计 时 可 以用 大 规模 的器 件 ,设 计 成 功 后 ,根 据 实 际 的 资源 使 用情 况 ,更 换更 经济 的器 件来 量产 。 3 )器件 的速度 、功耗 及 l支 持器件 速度 O

CycloneIII使用注意事项V1.0

© 2008 Cytech Technology Ltd – Confidential

Notice6:在使用增量编译时的告警

在使用增量编译的时候,如果在子工程中分配了管脚,在导出.QXP网表 文件以及在定层导入网表的时候,QUARTUS会出现如下的警告,会造成 用户的误解,导出网表时的警告:

Warning: Complex I/O atoms found during Design Partition Export Warning: Node GZ_DATA[0] is a non-trivial IO atom Warning: Node GZ_DATA[1] is a non-trivial IO atom Warning: Node GZ_DATA[2] is a non-trivial IO atom Warning: Node GZ_DATA[3] is a non-trivial IO atom Warning: Node GZ_DATA[4] is a non-trivial IO atom Warning: Node GZ_DATA[5] is a non-trivial IO atom Warning: Node GZ_DATA[6] is a non-trivial IO atom Warning: Node GZ_DATA[7] is a non-trivial IO atom Warning: Node flash_d[0] is a non-trivial IO atom Warning: Node flash_d[1] is a non-trivial IO atom Warning: Node flash_d[2] is a non-trivial IO atom Warning: Node flash_d[3] is a non-trivial IO atom Warning: Node flash_d[4] is a non-trivial IO atom Warning: Node flash_d[5] is a non-trivial IO atom Warning: Node flash_d[6] is a non-trivial IO atom Warning: Node flash_d[7] is a non-trivial IO atom

cyclone3的配置方式

cyclone3的配置方式cyclone3的配置方式cyclone3器件使用SRAM单元保存配置信息。

因为SRAM掉电易失的特性,fpga芯片上电的时候必须重新配置。

根据期间密度和封装选择,它有如下5中配置方案(红色部分为常用配置方案,并不是所有FPGA芯片都能使用所有配置方案,具体可查看cyclone3的器件手册):1. Active serial (AS)主动串行配置2. Active parallel (AP)主动并行配置3. Passive serial (PS)被动串行配置4. Fast passive parallel (FPP)快速被动并行配置5. Joint Test Action Group (JTAG)AS和AP配置方案需要外部FLASH存储器存储配置信息。

其它3种配置方案需要外部的控制器或者下载电缆。

主动配置方案以及JTAG方案常用于单芯片系统设计。

下面重点介绍AS,AP和JTAG。

以AS配置为例介绍。

Cyclone3器件的配置芯片通常选择EPCS64,EPCS16以及EPCS4或者flash.这些芯片能够提供廉价,方便(引脚少)的解决方案。

因为FPGA芯片容量的限制,它对配置信息的大小也有所限制。

EP3C80系列器件可提供21MBITS的配置信息流容量。

MSEL【3:0】为FPGA器件的输入,用于确定配置方式。

AS模式下,它连接1101.AP模式下,它连接1011.注意要直接接 VCCA or GND,更不能悬空,避免无效配置。

查看手册可得到其它配置值。

在JTAG模式下,忽略MSEL配置,JTAG模式有优先权。

AS模式支持配置信息压缩,AP模式不支持。

压缩信息可以节约空间以及配置时间。

在Device & Pin Options――Configuration中可以选择压缩与否。

选择好器件后,参考下图连接。

POR――上电复位.复位时间由MSEL【3:0】决定。

复位结束后开始发送配置控制信号。

烈风马丁3山地车配置表

烈风马丁3山地车配置表

【原创版】

目录

一、烈风马丁 3 山地车的概述

二、烈风马丁 3 山地车的配置特点

三、烈风马丁 3 山地车的性能表现

四、烈风马丁 3 山地车的价格与购买建议

正文

一、烈风马丁 3 山地车的概述

烈风马丁 3 山地车是一款适合新手入门的山地车,其性价比非常高,成为了许多车友的首选。

这款山地车由凯路仕公司设计、生产和销售,致力于为户外运动单车以及配套的单车运动装备提供最专业、最具性价比的产品。

二、烈风马丁 3 山地车的配置特点

1.车架:烈风马丁 3 山地车的车架采用了优质的铝合金材料,具有重量轻、强度高的特点,使得整车在保证强度的同时还能保持轻便。

2.前叉:前叉采用了带有锁死功能的山地车前叉,可以在需要时锁死前叉,使骑行更加稳定。

3.变速器:烈风马丁 3 山地车配备了禧玛诺变速器,具有稳定的性能和流畅的换挡体验。

4.刹车系统:刹车系统采用了液压碟刹,制动力强,反应迅速,为骑行安全提供了保障。

5.轮组:轮组采用了双层铝合金车圈,搭配耐磨的轮胎,为骑行提供了良好的支撑。

三、烈风马丁 3 山地车的性能表现

烈风马丁 3 山地车在性能方面表现优秀,其轻量化的设计使得骑行更加轻松,同时具备较高的强度。

变速器的性能稳定,换挡流畅,为骑行提供了舒适的体验。

刹车系统反应迅速,制动力强,为骑行安全提供了保障。

四、烈风马丁 3 山地车的价格与购买建议

烈风马丁 3 山地车的价格在 2000 元左右,性价比非常高。

对于新手入门的山地车爱好者来说,这款山地车是一个不错的选择。

在购买时,可以根据个人需求和预算选择合适的配置和颜色。

CYCLONE III EPCS使用方法

一、只使用FPGA硬件资源,不使用NIOS的时候

需要将nCEO引脚设为用户引脚,注意:一般编译器是默认它为程序下载的引脚的

将nCEO设为用户IO,其它的保留原样

二、使用NIOS的时候

由于CD0板子上没有设计FLASH。

所以在使用NIOS的时候,需要把程序存在EPCS器件中。

CYCLONE III器件跟其它器件的EPCS使用方法不同。

将DEVICE AND PIN OPTIONS页全部置为USER IO

在SOPC中添加epcs_flash_controller

在FPGA工程的顶层模块中添加EPCS控值器的接口

在NIOS的FLASH PROGRAMMER中做如下设置

将FPGA的SOF文件用QUARTUS的通过JTAG下载到FPGA后,

在NIOS的FLASH PROGRAMMER中点这时,NIOS的FLASH

PROGRAMMER会把.SOF文件和NIOS生成的.ELF文件合在一起,生成另一个配置文件下载到板子上的EPCS芯片中

重新上电,FPGA就以正常运行NIOS+FPGA的程序了

注意:在使用NIOS的时候FPGA的PIN_22因为太靠近PIN_23:DCLK(FPGA提供给EPCS 芯片的时钟)而不能再使用(使用时QUARTUS编译器会报错)。

PIN_22对应了CD0板子上的GPIO1[13],

所以在有NIOS的工程中都没有使用这一个引脚,对应的有NIOS的FPGA顶层也写成了如下:

跳过了…[12]这个引脚。

altera cyclone系列器件命名规则

altera cyclone系列器件命名规则Altera Cyclone系列器件是一种可编程逻辑器件,由Intel公司生产和销售。

这些器件以其高度集成、低功耗和成本效益而闻名。

Cyclone系列器件具有广泛的适用领域,包括消费电子、嵌入式系统、通信设备、工业自动化和汽车等。

Cyclone系列器件的命名规则遵循一定的规律和标准,下面是关于Cyclone系列器件命名规则的一些参考内容。

1. 器件型号:Cyclone系列器件的型号通常由几个字母和数字组合而成。

字母部分通常表示器件系列和特定特征,数字部分表示器件规格和性能等级。

例如,Cyclone III系列器件的型号通常以"EP3C"开头,Cyclone IV系列器件以"EP4C"开头。

2. 系列标识:Cyclone系列器件通常分为不同的系列,每个系列具有不同的特点和功能。

系列标识通常在器件型号的开头部分出现,用于区分不同系列。

例如,Cyclone III系列的器件型号通常以"EP3C"开头,Cyclone IV系列的器件型号以"EP4C"开头。

3. 功能特征:Cyclone系列器件的型号通常包含有关器件功能和特征的信息。

这些信息可以体现在型号的字母部分中。

例如,字母"D"通常表示器件带有内置的DDR2或DDR3控制器,字母"G"表示器件带有Gigabit以太网MAC,字母"F"表示器件带有配置存储器。

4. 性能等级:Cyclone系列器件的型号通常包含有关器件性能和等级的信息。

这些信息可以体现在型号的数字部分中。

例如,较高的数字通常表示更高的性能和功能等级。

例如,Cyclone III系列的器件型号中,数字3表示该器件属于Cyclone III系列的第三个性能等级。

5. 封装类型:Cyclone系列器件通常提供不同的封装类型以满足不同应用需求。

cyclone配置手册

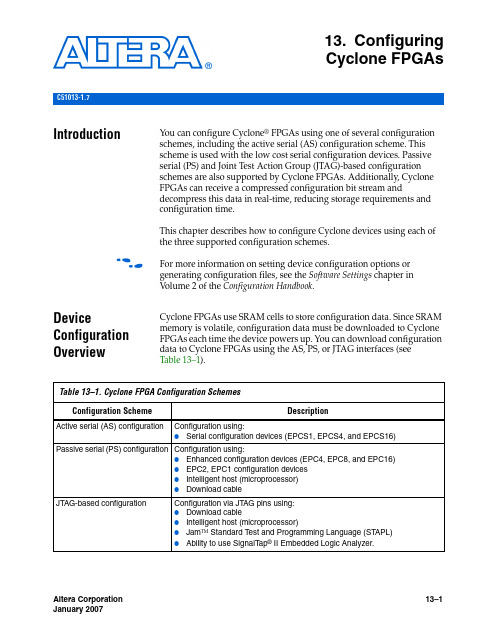

Altera Corporation13–1January 200713.ConfiguringCyclone FPGAsIntroduction You can configure Cyclone ® FPGAs using one of several configurationschemes, including the active serial (AS) configuration scheme. This scheme is used with the low cost serial configuration devices. Passive serial (PS) and Joint Test Action Group (JTAG)-based configuration schemes are also supported by Cyclone FPGAs. Additionally, Cyclone FPGAs can receive a compressed configuration bit stream and decompress this data in real-time, reducing storage requirements and configuration time.This chapter describes how to configure Cyclone devices using each of the three supported configuration schemes.f For more information on setting device configuration options orgenerating configuration files, see the Software Settings chapter in Volume 2 of the Configuration Handbook .Device Configuration OverviewCyclone FPGAs use SRAM cells to store configuration data. Since SRAM memory is volatile, configuration data must be downloaded to Cyclone FPGAs each time the device powers up. You can download configuration data to Cyclone FPGAs using the AS, PS, or JTAG interfaces (see Table 13–1). Table 13–1.Cyclone FPGA Configuration SchemesConfiguration SchemeDescription Active serial (AS) configuration Configuration using:●Serial configuration devices (EPCS1, EPCS4, and EPCS16)Passive serial (PS) configuration Configuration using:●Enhanced configuration devices (EPC4, EPC8, and EPC16)●EPC2, EPC1 configuration devices●Intelligent host (microprocessor)●Download cableJTAG-based configuration Configuration via JT AG pins using:●Download cable●Intelligent host (microprocessor)●Jam TM Standard T est and Programming Language (ST APL)●Ability to use SignalT ap ®II Embedded Logic Analyzer.C51013-1.713–2Altera Corporation Cyclone Device Handbook, Volume 1January 2007Device Configuration OverviewYou can select a Cyclone FPGA configuration scheme by driving itsMSEL1 and MSEL0 pins either high (1) or low (0), as shown in Table 13–2. If your application only requires a single configuration mode, the MSEL pins can be connected to V CC (the I/O bank’s V CCIO voltage where the MSEL pin resides) or to ground. If your application requires more than one configuration mode, the MSEL pins can be switched after the FPGA has been configured successfully. Toggling these pins during user mode does not affect the device operation. However, the MSEL pins must be valid before initiating reconfiguration.After configuration, Cyclone FPGAs will initialize registers and I/O pins, then enter user mode and function as per the user design. Figure 13–1 shows an AS configuration waveform.Figure 13–1.AS Configuration Waveform Table 13–2.Selecting Cyclone Configuration SchemesMSEL1MSEL0Configuration Scheme 00AS 01PS 01JTAG-based (1)Note to Table 13–2:(1)JTAG-based configuration takes precedence over other schemes, which meansthat MSELpin settings are ignored.Altera Corporation13–3January 2007Cyclone Device Handbook, Volume 1Configuring Cyclone FPGAsYou can configure Cyclone FPGAs using the 3.3-, 2.5-, 1.8-, or 1.5-V LVTTL I/O standard on configuration and JTAG input pins. These devices do not feature a VCCSEL pin; therefore, you should connect the VCCIO pins of the I/O banks containing configuration or JTAG pins according to the I/O standard specifications.Table 13–3 summarizes the approximate uncompressed configuration file size for each Cyclone FPGA. To calculate the amount of storage space required for multi-device configurations, add the file size of each device together.You should only use the numbers in Table 13–3 to estimate the configuration file size before design compilation. Different file formats, such as .hex or .ttf files, have different file sizes. For any specific version of the Quartus ®II software, any design targeted for the same device has the same uncompressed configuration file size. If compression is used, the file size can vary after each compilation.DataCompressionCyclone FPGAs are the first FPGAs to support decompression of configuration data. This feature allows you to store compressed configuration data in configuration devices or other memory, and transmit this compressed bit stream to Cyclone FPGAs. During configuration, the Cyclone FPGA decompresses the bit stream in real time and programs its SRAM cells.Cyclone FPGAs support compression in the AS and PS configuration schemes. Compression is not supported for JTAG-based configuration. 1Preliminary data indicates that compression reduces configuration bit stream size by 35 to 60%.Table 13–3.Cyclone Raw Binary File (.rbf) Sizes Device Data Size (Bits)Data Size (Bytes)EP1C3627,37678,422EP1C4924,512115,564EP1C61,167,216145,902EP1C122,323,240290,405EP1C203,559,608435,000Data CompressionWhen you enable compression, the Quartus II software generatesconfiguration files with compressed configuration data. Thiscompression reduces the storage requirements in the configurationdevice or flash, and decreases the time needed to transmit the bit streamto the Cyclone FPGA.There are two methods to enable compression for Cyclone bitstreams:before design compilation (in the Compiler Settings menu) and afterdesign compilation (in the Convert Programming Files window).To enable compression in the project's compiler settings, select Deviceunder the Assignments menu to bring up the settings window. Afterselecting your Cyclone device open the Device & Pin Options window,and in the General settings tab enable the check box for Generatecompressed bitstreams (as shown in Figure13–2).13–4Altera Corporation Cyclone Device Handbook, Volume 1January 2007Configuring Cyclone FPGAsFigure13–2.Enabling Compression for Cyclone Bitstreams in CompilerSettingsAltera Corporation 13–5 January 2007Cyclone Device Handbook, Volume 113–6Altera Corporation Cyclone Device Handbook, Volume 1January 2007Data CompressionCompression can also be enabled when creating programming files from the Convert Programming Files window. See Figure 13–3.1.Click Convert Programming Files (File menu). 2.Select the programming file type (POF, SRAM HEXOUT, RBF, orTTF).3.For POF output files, select a configuration device.4.Select Add File and add a Cyclone SOF file(s).5.Select the name of the file you added to the SOF Data area and click on Properties .6.Check the Compression checkbox.Figure 13–3.Enabling Compression for Cyclone Bitstreams in ConvertProgramming FilesConfiguring Cyclone FPGAsWhen multiple Cyclone devices are cascaded, the compression featurecan be selectively enabled for each device in the chain. Figure13–4depicts a chain of two Cyclone FPGAs. The first Cyclone FPGA has thecompression feature enabled and therefore receives a compressed bitstream from the configuration device. The second Cyclone FPGA has thecompression feature disabled and receives uncompressed data.Figure13–pressed & Uncompressed Configuration Data in the SameProgramming File Note(1)Note to Figure13–4:(1)The first device in the chain should be set up in AS configuration mode(MSEL[1..0]="00"). The remaining devices in the chain must be set up in PSconfiguration mode (MSEL[1..0]="01").You can generate programming files for this setup from the ConvertProgramming Files window (File menu) in the Quartus II software.The decompression feature supported by Cyclone FPGAs is separatefrom the decompression feature in enhanced configuration devices(EPC16, EPC8, and EPC4 devices). The data compression feature in theenhanced configuration devices allows them to store compressed dataand decompress the bit stream before transmitting to the target devices.When using Cyclone FPGAs with enhanced configuration devices, Alterarecommends using compression on one of the devices, not both(preferably the Cyclone FPGA since transmitting compressed datareduces configuration time).Altera Corporation 13–7 January 2007Cyclone Device Handbook, Volume 113–8Altera Corporation Cyclone Device Handbook, Volume 1January 2007Configuration SchemesConfigurationSchemes This section describes the various configuration schemes you can use to configure Cyclone FPGAs. Descriptions include an overview of theprotocol, pin connections, and timing information. The schemes discussed are:■AS configuration (serial configuration devices)■PS configuration ■JTAG-based configurationActive Serial Configuration (Serial Configuration Devices)In the AS configuration scheme, Cyclone FPGAs are configured using the new serial configuration devices. These configuration devices are low cost devices with non-volatile memory that feature a simple four-pin interface and a small form factor. These features make serialconfiguration devices an ideal solution for configuring the low-cost Cyclone FPGAs.f For more information on programming serial configuration devices, seethe Cyclone Literature web page and the Serial Configuration Devices (EPCS1, EPCS4, EPCS16 & EPCS64) Data Sheet .Serial configuration devices provide a serial interface to accessconfiguration data. During device configuration, Cyclone FPGAs read configuration data via the serial interface, decompress data if necessary, and configure their SRAM cells. This scheme is referred to as an AS configuration scheme because the FPGA controls the configurationinterface. This scheme is in contrast to the PS configuration scheme where the configuration device controls the interface.Serial configuration devices have a four-pin interface: serial clock input (DCLK ), serial data output (DATA ), AS data input (ASDI ), and an active-low chip select (nCS ). This four-pin interface connects to Cyclone FPGA pins as shown in Figure 13–5.Configuring Cyclone FPGAsFigure13–5.AS Configuration of a Single Cyclone FPGANotes to Figure13–5:(1)Connect the pull-up resistors to a 3.3-V supply.(2)Cyclone FPGAs use the ASDO to ASDI path to control the configuration device.Connecting the MSEL[1..0] pins to 00 selects the AS configurationscheme. The Cyclone chip enable signal, nCE, must also be connected toground or driven low for successful configuration.During system power up, both the Cyclone FPGA and serialconfiguration device enter a power-on reset (POR) period. As soon as theCyclone FPGA enters POR, it drives nSTATUS low to indicate it is busyand drives CONF_DONE low to indicate that it has not been configured.After POR, which typically lasts 100 ms, the Cyclone FPGA releasesnSTATUS and enters configuration mode when this signal is pulled highby the external 10-kΩ resistor. Once the FPGA successfully exits POR, alluser I/O pins are tri-stated. Cyclone devices have weak pull-up resistorson the user I/O pins which are on before and during configuration.f The value of the weak pull-up resistors on the I/O pins that are onbefore and during configuration can be found in Chapter4, DC &Switching Characteristics.The serial clock (DCLK) generated by the Cyclone FPGA controls theentire configuration cycle (see Figure13–1 on page13–2) and this clocksignal provides the timing for the serial interface. Cyclone FPGAs use an Altera Corporation 13–9 January 2007Cyclone Device Handbook, Volume 113–10Altera Corporation Cyclone Device Handbook, Volume 1January 2007Configuration Schemesinternal oscillator to generate DCLK . After configuration, this internal oscillator is turned off. Table 13–4 shows the active serial DCLK output frequencies.The serial configuration device latches input/control signals on the rising edge of DCLK and drives out configuration data on the falling edge.Cyclone FPGAs drive out control signals on the falling edge of DCLK and latch configuration data on the falling edge of DCLK .In configuration mode, the Cyclone FPGA enables the serialconfiguration device by driving its nCSO output pin low that is connected to the chip select (nCS ) pin of the configuration device. The Cyclone FPGA’s serial clock (DCLK ) and serial data output (ASDO ) pins sendoperation commands and read-address signals to the serial configuration device. The configuration device provides data on its serial data output (DATA ) pin that is connected to the DATA0 input on Cyclone FPGAs.After the Cyclone FPGA receives all configuration bits, it releases the open-drain CONF_DONE pin allowing the external 10-k Ω resistor to pull this signal to a high level. Initialization begins only after the CONF_DONE line reaches a high level. The CONF_DONE pin must have an external 10-k Ω pull-up resistor in order for the device to initialize.You can select the clock used for initialization by using the User Supplied Start-Up Clock option in the Quartus II software. The Quartus IIsoftware uses the 10-MHz (typical) internal oscillator (separate from the AS internal oscillator) by default to initialize the Cyclone FPGA. After initialization, the internal oscillator is turned off. When you enable the User Supplied Start-Up Clock option, the software uses the CLKUSR pin as the initialization clock. Supplying a clock on the CLKUSR pin does not affect the configuration process. After all configuration data is accepted and the CONF_DONE signal goes high, Cyclone devices require 136 clock cycles to initialize properly.An optional INIT_DONE pin is available. This pin signals the end ofinitialization and the start of user mode with a low-to-high transition. The Enable INIT_DONE output option is available in the Quartus IIsoftware. If the INIT_DONE pin is used, it is high due to an external 10-k Ω pull-up resistor when nCONFIG is low and during the beginning ofconfiguration. Once the option bit to enable INIT_DONE is programmed into the device (during the first frame of configuration data), the Table 13–4.Active Serial DCLK Output FrequencyMinimum Typical Maximum Units14 17 20 M H zINIT_DONE pin goes low. When initialization is complete, theINIT_DONE pin is released and pulled high. This low-to-high transition signals that the FPGA has entered user mode. In user mode, the user I/O pins do not have weak pull-ups and functions as assigned in your design. If an error occurs during configuration, the Cyclone FPGA asserts the nSTATUS signal low indicating a data frame error, and the CONF_DONE signal stays low. With the Auto-Restart Configuration on Frame Error option enabled in the Quartus II software, the Cyclone FPGA resets the configuration device by pulsing nCSO, releases nSTATUS after a reset time-out period (about 30 μs), and retries configuration. If this option is turned off, the system must monitor nSTATUS for errors and then pulse nCONFIG low for at least 40 μs to restart configuration. After successful configuration, the CONF_DONE signal is tri-stated by the target device and then pulled high by the pull-up resistor.All AS configuration pins, DATA0, DCLK, nCSO, and ASDO, have weak internal pull-up resistors. These pull-up resistors are always active. When the Cyclone FPGA is in user mode, you can initiate reconfiguration by pulling the nCONFIG pin low. The nCONFIG pin should be low for at least 40 μs. When nCONFIG is pulled low, the FPGA also pulls nSTATUS and CONF_DONE low and all I/O pins are tri-stated. Once nCONFIG returns to a logic high level and nSTATUS is released by the Cyclone FPGA, reconfiguration begins.Co n fig ur i n g M u ltiple Device s (Ca s cadi n g)You can configure multiple Cyclone FPGAs using a single serial configuration device. You can cascade multiple Cyclone FPGAs using the chip-enable (nCE) and chip-enable-out (nCEO) pins. The first device in the chain must have its nCE pin connected to ground. You must connect its nCEO pin to the nCE pin of the next device in the chain. When the first device captures all of its configuration data from the bit stream, it drives the nCEO pin low enabling the next device in the chain. You must leave the nCEO pin of the last device unconnected. The nCONFIG, nSTATUS, CONF_DONE, DCLK, and DATA0 pins of each device in the chain are connected (see Figure13–6).This first Cyclone FPGA in the chain is the configuration master and controls configuration of the entire chain. You must connect its MSEL pins to select the AS configuration scheme. The remaining Cyclone FPGAs are configuration slaves and you must connect their MSEL pins to select the PS configuration scheme. Figure13–6 shows the pin connections for this setup.Figure13–6.Configuring Multiple Devices Using a Serial Configuration Device (AS)Note to Figure13–6:(1)Connect the pull-up resistors to a 3.3-V supply.As shown in Figure13–6, the nSTATUS and CONF_DONE pins on all targetFPGAs are connected together with external pull-up resistors. These pinsare open-drain bidirectional pins on the FPGAs. When the first deviceasserts nCEO (after receiving all of its configuration data), it releases itsCONF_DONE pin. But the subsequent devices in the chain keep this sharedCONF_DONE line low until they have received their configuration data.When all target FPGAs in the chain have received their configuration dataand have released CONF_DONE, the pull-up resistor drives a high level onthis line and all devices simultaneously enter initialization mode. If anerror occurs at any point during configuration, the nSTATUS line isdriven low by the failing FPGA. If you enable the Auto RestartConfiguration on Frame Error option, reconfiguration of the entire chainbegins after a reset time-out period (a maximum of 40 μs). If the option isturned off, the external system must monitor nSTATUS for errors andthen pulse nCONFIG low to restart configuration. The external system canpulse nCONFIG if it is under system control rather than tied to V CC.1While you can cascade Cyclone FPGAs, serial configurationdevices cannot be cascaded or chained together.If the configuration bit stream size exceeds the capacity of a serial configuration device, you must select a larger configuration deviceand/or enable the compression feature. While configuring multiple devices, the size of the bit stream is the sum of the individual devices’ configuration bit streams.Co n fig ur i n g M u ltiple Device s with the Same DataCertain applications require the configuration of multiple Cyclone devices with the same design through a configuration bit stream or SOF file. This can actually be done by two methods and they are shown below. For both methods, the serial configuration devices cannot be cascaded or chained together.Method 1For method 1, the serial configuration device stores two copies of the SOF file. The first copy configures the master Cyclone device, and the second copy configures all the remaining slave devices concurrently. The setup is similar to Figure13–7 where the master is setup in AS mode (MSEL=00) and the slave devices are setup in PS mode (MSEL01).To configure four identical Cyclone devices with the same SOF file, you could setup the chain similar to the example shown in Figure13–6, except connect the three slave devices for concurrent configuration. The nCEO pin from the master device drives the nCE input pins on all three slave devices, and the DATA and DCLK pins connect in parallel to all four devices. During the first configuration cycle, the master device reads its configuration data from the serial configuration device while holding nCEO high. After completing its configuration cycle, the master drives nCE low and transmits the second copy of the configuration data to all three slave devices, configuring them simultaneously. The advantage of using the setup in Figure13–7 is you can have a different SOF file for the Cyclone master device. However, all the Cyclone slave devices must be configured with the same SOF file.Figure13–7.Configuring Multiple Devices with the Same Design Using a Serial Configuration DeviceNote to Figure13–7:(1)The pull-up resistor should be connected to the same supply voltage as the configuration device.Method 2Method 2 configures multiple Cyclone devices with the same SOFs bystoring only one copy of the SOF in the serial configuration device. Thissaves memory space in the serial configuration device for general-purpose use and may reduce costs. This method is shown in Figure13–8where the master device is set up in AS mode (MSLE=00), and the slavedevices are set up in PS mode (MSEL=01). You could set up one or moreslave devices in the chain and all the slave devices are set up in the sameway as the design shown in Figure13–8.Figure13–8.Configuring Multiple Devices with the Same Design Using a Serial Configuration DeviceIn this setup, all the Cyclone devices in the chain are connected forconcurrent configuration. This reduces the active serial configurationtime because all the Cyclone devices are configured in only oneconfiguration cycle. To achieve this, the nCE input pins on all the Cyclonedevices are connected to ground and the nCEO output pins on all theCyclone devices are left unconnected. The DATA and DCLK pins connectin parallel to all the Cyclone devices.It is recommended to add a buffer before the DATA and DCLK output fromthe master Cyclone to avoid signal strength and signal integrity issues.The buffer should not significantly change the DATA-to-DCLKrelationships or delay them with respect to other ASMI signals, which areASDI and nCS signals. Also, the buffer should only drive the slaveCyclone devices, so that the timing between the master Cyclone deviceand serial configuration device is unaffected.This setup can support both compressed and uncompressed SOFs.Therefore, if the configuration bit stream size exceeds the capacity of aserial configuration device, you can enable the compression feature onthe SOF used or you can select a larger serial configuration device.E s timati n g Active Se r ial Co n fig ur atio n TimeActive serial configuration time is dominated by the time it takes totransfer data from the serial configuration device to the Cyclone FPGA.This serial interface is clocked by the Cyclone DCLK output (generatedfrom an internal oscillator). As listed in Table13–4, the DCLK minimumfrequency is 14 MHz (71 ns). Therefore, the maximum configuration timeestimate for an EP1C3 device (0.628 MBits of uncompressed data) is:(0.628 MBits × 71 ns) = 47 ms.The typical configuration time is 33 ms.Enabling compression reduces the amount of configuration data that istransmitted to the Cyclone device, reducing configuration time. Onaverage, compression reduces configuration time by 50%.P r og r ammi n g Se r ial Co n fig ur atio n Device sSerial configuration devices are non-volatile, flash-memory-baseddevices. You can program these devices in-system using theByteBlaster TM II download cable. Alternatively, you can program themusing the Altera Programming Unit (APU) or supported third-partyprogrammers.You can perform in-system programming of serial configuration devicesvia the AS programming interface. During in-system programming, thedownload cable disables FPGA access to the AS interface by driving thenCE pin high. Cyclone FPGAs are also held in reset by a low level onnCONFIG. After programming is complete, the download cable releasesnCE and nCONFIG, allowing the pull-down and pull-up resistor to driveGND and VCC, respectively. Figure13–9 shows the download cableconnections to the serial configuration device.f For more information on the ByteBlaster II cable, see the ByteBlaster IIDownload Cable Data Sheet.The serial configuration devices can be programmed in-system by anexternal microprocessor using SRunner. SRunner is a software driverdeveloped for embedded serial configuration device programming thatcan be customized to fit in different embedded systems. The SRunner canread a Raw Programming Data file (.rpd) and write to the serialconfiguration devices. The programming time is comparable to theQuartus II software programming time.f For more information about SRunner, see the “SRunner: An EmbeddedSolution for Serial Configuration Device Programming” white paper and thesource code on the Altera web site ().Figure13–9.In-System Programming of Serial Configuration DevicesNotes to Figure13–9:(1)Connect these pull-up resistors to 3.3-V supply.(2)The nCEO pin is left unconnected.(3)Power up the ByteBlaster II cable’s V CC with a 3.3-V supply.You can program serial configuration devices by using the Quartus IIsoftware with the APU and the appropriate configuration deviceprogramming adapter. All serial configuration devices are offered in aneight-pin small outline integrated circuit (SOIC) package and can beprogrammed using the PLMSEPC-8 adapter.In production environments, serial configuration devices can beprogrammed using multiple methods. Altera programming hardware(APU) or other third-party programming hardware can be used toprogram blank serial configuration devices before they are mounted ontoPCBs. Alternatively, you can use an on-board microprocessor to programthe serial configuration device in-system using C-based software driversprovided by Altera.f For more information on programming serial configuration devices, seethe Cyclone Literature web page and the Serial Configuration Devices(EPCS1, EPCS4, EPCS16 & EPCS64) Data Sheet.f Device configuration options and how to create configuration files arediscussed further in the Software Settings chapter in Volume II of theConfiguration Handbook.Passive Serial ConfigurationCyclone FPGAs also feature the PS configuration scheme supported byall Altera FPGAs. In the PS scheme, an external host (configurationdevice, embedded processor, or host PC) controls configuration.Configuration data is clocked into the target Cyclone FPGAs via theDATA0 pin at each rising edge of DCLK. The configuration waveforms forthis scheme are shown in Figure13–10.Figure13–10.PS Configuration Cycle WaveformNotes to Figure13–10:(1)During initial power up and configuration, CONF_DONE is low. After configuration, CONF_DONE goes high toindicate successful configuration. If the device is reconfigured, CONF_DONE goes low after nCONFIG is driven low.(2)User I/O pins are tri-stated during configuration. Cyclone FPGAs also have a weak pull-up resistor on I/O pinsduring configuration. After initialization, the user I/O pins perform the function assigned in the user’s design. (3)When used, the optional INIT_DONE signal is high when nCONFIG is low before configuration and during the first136 clock cycles of configuration.(4)In user mode, DCLK should be driven high or low when using the PS configuration scheme. When using the ASconfiguration scheme, DCLK is a Cyclone output pin and should not be driven externally.(5)In user mode, DATA0 should be driven high or low.PS Co n fig ur atio n U s i n g Co n fig ur atio n DeviceIn the PS configuration device scheme, nCONFIG is usually tied to V CC(when using EPC16, EPC8, EPC4, or EPC2 devices, you can connectnCONFIG to nINIT_CONF). Upon device power-up, the target CycloneFPGA senses the low-to-high transition on nCONFIG and initiatesconfiguration. The target device then drives the open-drain CONF_DONEpin low, which in-turn drives the configuration device’s nCS pin low.When exiting POR, both the target and configuration device release theopen-drain nSTATUS pin (typically Cyclone POR lasts 100 ms).Before configuration begins, the configuration device goes through aPOR delay of up to 100 ms (maximum) to allow the power supply tostabilize. You must power the Cyclone FPGA before or during the PORtime of the enhanced configuration device. During POR, theconfiguration device drives its OE pin low. This low signal delaysconfiguration because the OE pin is connected to the target device’snSTATUS pin. When the target and configuration devices complete POR,they both release the nSTATUS to OE line, which is then pulled high by apull-up resistor.。

利用高级Cyclone_III_FPGA_PLL,提高灵活性,增加集成度

利用高级Cyclone III FPGA PLL,提高灵活性,增加集成度-技术白皮书来源:EDACN摘要:在使用FPGA时,经常忽略了它的一个优点——能够集成时钟解决方案。

这种集成能力不但降低了系统成本,而且最新的65-nm Altera®Cyclone®III FPGA支持高级时钟管理和锁相环(PLL)技术,因此,还极大地提高了设计灵活性。

设计人员利用Cyclone III时钟管理功能,管理整个FPGA和电路板的时钟系统。

而且,由于Cyclone III PLL集成在FPGA中,可以利用Altera 的Quartus®II设计环境,轻松进行设置和配置。

关键词:FPGA,Cyclone III FPGA PLL,集成度引言在使用FPGA时,经常忽略了它的一个优点——能够集成时钟解决方案。

这种集成能力不但降低了系统成本,而且最新的65-nm Altera®Cyclone®III FPGA支持高级时钟管理和锁相环(PLL)技术,因此,还极大地提高了设计灵活性。

设计人员利用Cyclone III时钟管理功能,管理整个FPGA 和电路板的时钟系统。

而且,由于Cyclone III PLL集成在FPGA中,可以利用Altera的Quartus®II 设计环境,轻松进行设置和配置。

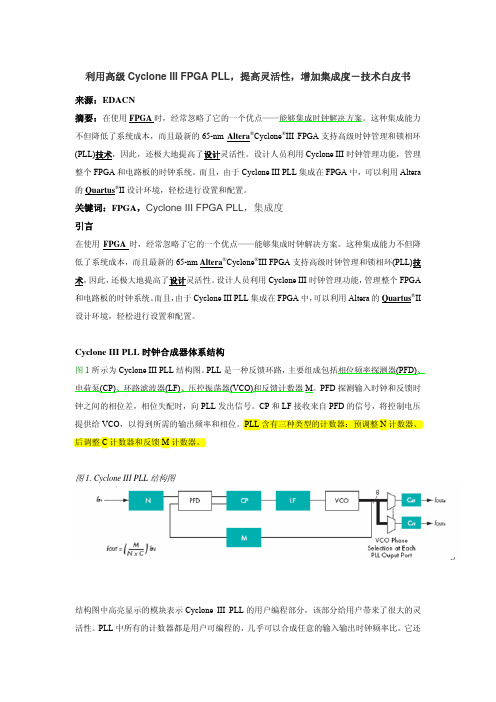

Cyclone III PLL时钟合成器体系结构图1所示为Cyclone III PLL结构图。

PLL是一种反馈环路,主要组成包括相位频率探测器(PFD)、电荷泵(CP)、环路滤波器(LF)、压控振荡器(VCO)和反馈计数器M。

PFD探测输入时钟和反馈时钟之间的相位差,相位失配时,向PLL发出信号。

CP和LF接收来自PFD的信号,将控制电压提供给VCO,以得到所需的输出频率和相位。

PLL含有三种类型的计数器:预调整N计数器、后调整C计数器和反馈M计数器。

图1. Cyclone III PLL结构图结构图中高亮显示的模块表示Cyclone III PLL的用户编程部分,该部分给用户带来了很大的灵活性。

CycloneIII设计向导

CycloneIII设计向导CycloneIII设计向导第一篇:芯片选型1.考虑器件的资源,包括LE,ram资源,硬件乘法器,PLL,全局时钟网络等。

总体来说,对于FPGA设计,资源一定要留有余量,否则最后的时序收敛会比较困难。

我认为使用80%左右是比较合适的。

对于资源使用量在95%以上的设计,除了时序收敛,可能还会遇到一些你想不到的问题。

A. LE是5K到120K。

要对设计需要的资源做一个估算,120K,对于大部分的应用,应该是一个很大的数字了。

B.ram资源为400K-3888Kbit.注意ram块的大小都是9Kbit,有些模块,比如fifo,实际上用不到9K的资源。

但不管你用多少,都得占用一个ram(有些情况下占用0.5个ram)。

所以ram 的数量是否足够也得考虑。

C.乘法器的数量23-288个。

注意是18*18bit的乘法器。

实际使用时,要看应用需要的乘法器精度是多少。

D.PLL的数量为2-4个。

每个PLL可以输出5个时钟,一般的设计够用了。

如果设计中的时钟很多,就得仔细考虑了。

E.全局时钟网络为10-20个。

一般够用,如果设计中有很多时钟或者很多扇出(fan-out)很大的信号,比如复位信号,也得仔细考虑。

2.考虑引脚,封装和迁移A.引脚数量。

设计前,就要考虑需要多少普通IO(LVTTL),这个应该是比较好计算的。

电平有几种,因为一个bank只能1个IO电平。

需要多少LVDS管脚,一些小封装器件的LVDS管脚很少。

B.封装。

封装影响到引脚数量。

还影响到焊接的难度。

EQFP和PQFP当然好焊接也好拆卸,如果是BGA的,一般需要找专人焊接(需要专门的工具),价格也贵。

布线难度:用BGA,还得出注意ball pitch(焊接球的间距)。

1.0mm的当然比0.8mm的好布线。

F780比F484的外圈引脚数量多,当然也好布线一些。

体积:也就是芯片的大小了,比如用于移动和手持应用,就得考虑大小了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

cyclone3的配置方式

cyclone3器件使用SRAM单元保存配置信息。

因为SRAM掉电易失的特性,fpga芯片上电的时候必须重新配置。

根据期间密度和封装选择,它有如下5中配置方案(红色部分为常用配置方案,并不是所有FPGA芯片都能使用所有配置方案,具体可查看cyclone3的器件手册):

1.Active serial (AS)主动串行配置

2.Active parallel (AP)主动并行配置

3.Passive serial (PS)被动串行配置

4.Fast passive parallel (FPP)快速被动并行配置

5.Joint Test Action Group (JTAG)

AS和AP配置方案需要外部FLASH存储器存储配置信息。

其它3种配置方案需要外部的控制器或者下载电缆。

主动配置方案以及JTAG方案常用于单芯片系统设计。

下面重点介绍AS,AP和JTAG。

以AS配置为例介绍。

Cyclone3器件的配置芯片通常选择EPCS64,EPCS16以及EPCS4或者flash.这些芯片能够提供廉价,方便(引脚少)的解决方案。

因为FPGA芯片容量的限制,它对配置信息的大小也有所限制。

EP3C80系列器件可提供21MBITS的配置信息流容量。

MSEL【3:0】为FPGA器件的输入,用于确定配置方式。

AS模式下,它连接1101.AP模式下,它连接1011.注意要直接接 VCCA or GND,

更不能悬空,避免无效配置。

查看手册可得到其它配置值。

在JTAG 模式下,忽略MSEL配置,JTAG模式有优先权。

AS模式支持配置信息压缩,AP模式不支持。

压缩信息可以节约空间以及配置时间。

在 Device & Pin Options——Configuration中可以选择压缩与否。

选择好器件后,参考下图连接。

POR——上电复位.复位时间由MSEL【3:0】决定。

复位结束后开始发送配置控制信号。

DCLK信号由fpga内部晶振产生。

Cyclone3系列器件使用40Mhz时钟晶振。

在此时钟上升沿,输入控制信号,下降沿输出配置信息。

配置时间由配置信息流的大小和时钟频率决定。

配置过程大概如下:复位

——配置——初始化。

复位过程中,nconfig以及nstatus被拉低。

复位结束后,nstatus被外部的10k电阻拉高,进入配置阶段。

配置完成后,释放config_done引脚。

自此开始初始化。

JTAG确定了边界扫测试描的规范。

此种配置方式下,配置信息直接由quartus软件产生,经由下载电缆下载。

它需要配置4个信号: TDI, TDO, TMS, and TCK.

其中标示(2)部分,表示可按其他配置方式设置。