线路板多层板叠层计算公式

PADS内电层分割与铺铜

PADS电层分割与铺铜一、约定软件:PADS LAYOUT 9.3(PADS2007也可以参考通用步骤)二、一般步骤多层板的分割一般步骤为:定义叠层→设置层的属性(正、负片)→分配网络→分割→铺铜。

首次定义多层板的叠层结构。

四层板堆叠一般为:SIG1/GND/POWER/SIG2;六层板堆叠为:① SIG1/GND/SIG2/SIG3/POWER/SIG4;② SIG1/GND1/POWER/SIG2/GND2/SIG3;在PADS当中板层定义如下图所示:其次,为电源层分配电源网络。

上图中强调一下“Plane Type”的问题。

首先从工艺角度讲,电层实物为薄薄的铜箔。

在制造流程上有“正片”和“负片”之分。

在PADS LAYOUT中,电层属性配置当中,CAM PLANE为负片属性,其他两层为正片属性。

以下部分是摘自PADS help文件:· No Plane — Prevents planes from being added to the layer. The No Plane layer is available for routing. If you select No Plane, you can only create Copper and Copper Pour areas on the layer.· CAM Plane — Sets the entire layer to be solid copper and connected to only one net. The CAM Plane layer is a negative image, and the copper does not appear in the design as it normally does for all other copper objects. You can not manipulate the shape/ou tline of the copper on this layer since it is generated automatically and covers t he entire layer. This is an outmoded layer type. You can not route traces on a CAM Plane layer. Copper Pours and Plane areas can not be created on CAM Plane layers.· Split/Mixed Plane — Enables one or more planes on the layer, and enables routing on the layer. Rout es can be placed within or without plane areas. Plane areas avoid traces within th eir outline by a clearance area defined in the design rules. Copper Pours can not be placed on Split/Mixed layers. Plane areas are created on Split/Mixed plane laye rs and are similar to but more feature-packed than Copper Pours.简单的讲,NO PLANE自由度更大一些,除了“Plane Area”以及相关的操作命令不能用以外,我们可以在NO PLANE层进行布线、铺铜、铺铜切割、2D图形边框的绘制等常用操作。

PCB线路板常用阻抗设计及叠层结构

PCB线路板常用阻抗设计及叠层结构PCB线路板(Printed Circuit Board)是现代电子设备中常用的一种基础组件,用于支持和连接电子元件,实现电路功能。

在PCB设计过程中,阻抗是一个重要的设计参数,特别是在高频信号传输和高速数字信号传输中。

1.电源和地线:电源和地线通常被设计成具有低阻抗的结构,以确保稳定的电源供应和良好的信号接地。

在PCB布局中,电源和地线一般会采用较宽的铜箔,以降低电阻和电感。

2.信号线:对于高速数字信号和高频信号的传输,常常需要控制信号线的阻抗。

阻抗匹配可以提高信号传输的带宽和抗干扰能力。

常见的阻抗设计包括单端阻抗和差分阻抗。

单端线路一般采用50欧姆的阻抗,而差分线路一般采用90欧姆的阻抗。

3.地平面:在高速数字信号传输中,地平面既可以作为信号的返回路径,同时也可以帮助抑制信号的辐射和干扰。

为了保持地平面的阻抗一致性,通常会在地平面上布满大面积的铜箔,以降低电阻和电感。

5.间距和宽度:阻抗的大小与线路的宽度和间距密切相关。

调整线路的宽度和间距可以实现对阻抗的精确控制。

在设计过程中,可以使用专业的PCB设计工具进行阻抗仿真和优化,以满足设计需求。

对于PCB线路板的叠层结构,常见的设计包括以下几种:1. 单面板(Single Layer PCB):单面板是最简单的PCB结构,只有一层导电层,通常用于简单的电路或低成本的产品中。

2. 双面板(Double Layer PCB):双面板具有两层导电层,信号可以在两层之间进行传输。

双面板可以实现更复杂的电路布局和更高的密度,通常用于中等复杂度的产品。

3. 多层板(Multilayer PCB):多层板由内外多个导电层组成,其中通过绝缘层来隔离。

多层板可以实现更高的集成度和更复杂的布局,用于高速数字信号传输和复杂电路的设计。

4. 刚性-柔性板(Rigid-Flex PCB):刚性-柔性板结合了刚性电路板和柔性电路板的优势。

一到八层电路板的叠层设计方式

一到八层电路板的叠层设计方式电路板的叠层安排是对PCB的整个系统设计的基础。

叠层设计如有缺陷,将最终影响到整机的EMC性能。

总的来说叠层设计主要要遵从两个规矩:1. 每个走线层都必须有一个邻近的参考层(电源或地层);2. 邻近的主电源层和地层要保持最小间距,以提供较大的耦合电容;下面列出从单层板到八层板的叠层:一、单面板和双面板的叠层对于两层板来说,由于板层数量少,已经不存在叠层的问题。

控制EMI辐射主要从布线和布局来考虑;单层板和双层板的电磁兼容问题越来越突出。

造成这种现象的主要原因就是因是信号回路面积过大,不仅产生了较强的电磁辐射,而且使电路对外界干扰敏感。

要改善线路的电磁兼容性,最简单的方法是减小关键信号的回路面积。

关键信号:从电磁兼容的角度考虑,关键信号主要指产生较强辐射的信号和对外界敏感的信号。

能够产生较强辐射的信号一般是周期性信号,如时钟或地址的低位信号。

对干扰敏感的信号是指那些电平较低的模拟信号。

单、双层板通常使用在低于10KHz的低频模拟设计中:1 在同一层的电源走线以辐射状走线,并最小化线的长度总和;2 走电源、地线时,相互靠近;在关键信号线边上布一条地线,这条地线应尽量靠近信号线。

这样就形成了较小的回路面积,减小差模辐射对外界干扰的敏感度。

当信号线的旁边加一条地线后,就形成了一个面积最小的回路,信号电流肯定会取道这个回路,而不是其它地线路径。

3 如果是双层线路板,可以在线路板的另一面,紧靠近信号线的下面,沿着信号线布一条地线,一线尽量宽些。

这样形成的回路面积等于pcb线路板的厚度乘以信号线的长度。

二、四层板的叠层推荐叠层方式:2.1 SIG-GND(PWR)-PWR (GND)-SIG;2.2 GND-SIG(PWR)-SIG(PWR)-GND;对于以上两种叠层设计,潜在的问题是对于传统的1.6mm(62mil)板厚。

层间距将会变得很大,不仅不利于控制阻抗,层间耦合及屏蔽;特别是电源地层之间间距很大,降低了板电容,不利于滤除噪声。

[最新]pcb板计算公式

![[最新]pcb板计算公式](https://img.taocdn.com/s3/m/81352c2530126edb6f1aff00bed5b9f3f90f7205.png)

PCB板计算公式(1平方米=10000CM,1平方米=1000000MM)

PCB板公式:长*宽*单价/拼板

双面板(FR4 0.6-1.2MM)450/平方米

四层板(FR4 0.8-1.2MM)850/平方米

六层板(FR4 1.6MM)1350/平方米

单面板(FR4 0.6-1.2MM)300/平方米

珍珠棉公式:长*厚*多少钱一平方*税率

纸箱公式:(长+宽+2)*(宽+高+1)*单价*2除1000

平卡:(长+0.5")*(宽+0.5")*单价/1000

啤盒"(长+宽+1")*(宽+高+1")*2*单价/1000

PE袋计算公式(MM/25.4,CM*2.54,1CM=2.54)长*宽*厚度*密度(2.62)*单价/1000

体积换算重量的公式

长(MM)*宽(MM)*厚度(MM)*比重/10的6次方*1000就等于多少G了

模具成本分析=材料費+彈簧費+螺絲費+邊釘費+熱處理費+小導柱費+大導柱費+標準件費+加工費

五金摸具报价公式:

单冲模报价(HK)=<下模板V*7.9*Price*3+线割,五金,模座>

连续模报价(HK)=<下模板V*7.9*Price*4+线割,五金,模座>

SUS弹片模报价=<下模板V*7.9*Price*4+线割,五金,模座>

会计类销售额计算公式:税额=含税额收入/(1+税率或征收率)

税额计算公式:税额=含税总收入-销售额不含税单价计算公式:不含税单价=销售数/数量。

多层PCB堆叠描述

多层PCB堆叠描述叠层结构采用0.3 1/1+1080*2+0.2 1/1+ 1080*2+0.3 1/1(0.265/0.22/0.265)详细描述:该板为6层板,采用3块2层板叠压而成,0.3 1/1,表示第一个双层板的介质厚度加上第一层铜箔厚度为0.3mm,1/1表示第一个双层板铜箔厚度为1盎司;1080×2,表示半固化板(软胶)厚度为0.12mm,1080为0.06mm;0.2 1/1,表示第二个双层板的介质厚度加上两层铜箔厚度为0.2mm,1/1表示第二个双层板铜箔厚度为1盎司;1080×2,表示半固化板(软胶)厚度为0.12mm,1080为0.06mm;0.3 1/1,表示第三个双层板的介质厚度加上两层铜箔厚度为0.3mm,1/1表示第二个双层板铜箔厚度为1盎司;结合目前PCB板加工厂家的工艺能力,在用polar公司阻抗计算器CITS25计算PCB板上迹线特性阻抗时,对影响PCB板迹线控制阻抗的几个相关参数分述如下:1、铜层厚度铜层厚度代表了PCB迹线的高度T。

内层铜箔通常情况下用到1OZ(厚度为35微米),也有在电源层要流过大电流时用到2OZ(厚度为70微米)。

外层铜箔常用1/2OZ(18微米),但由于经过板镀和图形电镀最终成品外层铜厚将达到48微米(实际计算时用该值),设计成其他铜厚将较难控制铜厚厚度公差。

若外层使用1OZ铜箔,则最终铜厚将达到65微米。

2、 PCB板迹线的上下线宽由于侧蚀的影响,PCB迹线的截面为一梯形,上下线宽差距以1mil来计算,其中下线宽=要求线宽,而上线宽=要求线宽-1mil。

3、阻焊层阻焊层厚度按10um为准(选择盖阻焊模式),但有机印后将会有所增厚,但其变化将基本不会带来阻抗值的变化。

4、介质厚度常用板材(芯板):(mm OZ/OZ *表示其数值为不包括铜箔厚度的芯板厚度)0.13* 1/1 0.21* 1/1 0.25* 1/1 0.36* 1/10.51* 1/1 0.71* 1/1 0.80* 1/11.0 1/1 1.2 1/1 1.6 0.5/0.5 1.6 1/1 1.6 2/22.0 1/1 2.0 2/2 2.4 1/13.0 1/1 3.2 1/1芯板在计算控制阻抗时的实际厚度:芯板规格0.13 0.21 0.25 0.36 0.51 0.71 0.80厚度(mm)0.13 0.21 0.25 0.36 0.51 0.71 0.80厚度(mil)5.12 8.27 9.84 14.17 20.08 27.95 31.50芯板规格1.0 1.2 1.62.0 2.4 2.5厚度(mm)0.99 1.15 1.55 1.95 2.35 2.45厚度(mil)38.98 45.28 61.02 76.77 92.52 96.46常用半固化片:(mm/mil)7628: 0.175/6.92116: 0.11/4.31080: 0.066/2.6实际计算厚度时注意半固化片随着两面线路结构不同而有所不同:(mil)HOZ 半固化片规格Copper/Gnd Gnd/Gnd Copper/Signal Gnd/SignalSignal/Signal1080 2.8 2.6 2.5 2.4 2.22116 4.6 4.4 4.2 4.0 3.87628 7.3 7.0 6.8 6.7 6.61OZ 半固化片规格Copper/Gnd Gnd/Gnd Copper/Signal Gnd/SignalSignal/SignalCopper/Gnd1080 2.8 2.6 2.5 2.4 2.22116 4.5 4.3 4.1 3.9 3.77682 7.1 6.8 6.6 6.56.4其中GND层包括铜面积占80%以上的线路层。

PADS内电层分割与铺铜

PADS内电层分割与铺铜一、约定软件:PADS LAYOUT 9.3(PADS2007也可以参考通用步骤)二、一般步骤多层板的分割一般步骤为:定义叠层→设置层的属性(正、负片)→分配网络→分割→铺铜。

首次定义多层板的叠层结构。

四层板堆叠一般为:SIG1/GND/POWER/SIG2;六层板堆叠为:① SIG1/GND/SIG2/SIG3/POWER/SIG4;② SIG1/GND1/POWER/SIG2/GND2/SIG3;在PADS当中板层定义如下图所示:其次,为电源层分配电源网络。

上图中强调一下“Plane Type”的问题。

首先从工艺角度讲,内电层实物为薄薄的铜箔。

在制造流程上有“正片”和“负片”之分。

在PADS LAYOUT中,内电层属性配置当中,CAM PLANE为负片属性,其他两层为正片属性。

以下部分是摘自PADS help文件:· No Plane — Prevents planes from being added to the layer. The No Plane layer is available for rou ting. If you select No Plane, you can only create Copper and Copper Pour areas on the l ayer.· CAM Plane — Sets the entire layer to be solid copper and connected to only one net. The CAM Plan e layer is a negative image, and the copper does not appear in the design as it normally does for all other copper objects. You can not manipulate the shape/outline of the copper on this layer since it is generated automatically and covers the entire layer. This is an ou tmoded layer type. You can not route traces on a CAM Plane layer. Copper Pours and Pl ane areas can not be created on CAM Plane layers.· Split/Mixed Plane — Enables one or more planes on the layer, and enables routing on the layer. Routes ca n be placed within or without plane areas. Plane areas avoid traces within their outline b y a clearance area defined in the design rules. Copper Pours can not be placed on Split/ Mixed layers. Plane areas are created on Split/Mixed plane layers and are similar to but more feature-packed than Copper Pours.简单的讲,NO PLANE自由度更大一些,除了“Plane Area”以及相关的操作命令不能用以外,我们可以在NO PLANE层进行布线、铺铜、铺铜切割、2D图形边框的绘制等常用操作。

pcb单价计算公式

pcb单价计算公式

PCB(Printed Circuit Board,印刷电路板)的单价计算公式通常涉及多个因素,包括以下几个主要方面:

1. PCB板的尺寸:通常以平方英寸(sq.in.)或平方毫米(sq.mm)为单位。

较大的尺寸会增加制作成本。

2. 层数:指印刷电路板的层数,例如单面板、双面板、多层板等。

层数越多,制作难度和成本也会相应提高。

3. 板厚:通常以毫米为单位。

较厚的板厚可能需要更多材料和制作工艺,从而增加成本。

4. 线宽/线距:指印刷电路板上导线的宽度和间距,通常以毫米为单位。

较小的线宽和线距通常需要更高的制作精度,因此成本也会相应增加。

5. 数量:指需要制作的PCB板的数量。

通常来说,批量生产的单价要比小批量制作的单价低。

6. 表面处理:指PCB板表面的处理方式,例如沉金、喷镀锡等。

不同的表面处理方式对成本有一定影响。

综合考虑以上因素,一般的PCB单价计算公式可以简化为:

单价 = (基础价格 + 面积价格 + 层数价格 + 线宽/线距价格+ 表面处理价格) * 数量

其中,基础价格是根据供应商提供的基本制作成本计算得出的,面积价格、层数价格、线宽/线距价格和表面处理价格则是根据PCB 板的具体要求和供应商的报价来确定的。

需要注意的是,由于不同的供应商和不同的项目要求可能会有差异,以上公式只是一种常见的计算方法,实际的PCB单价还需与具体情况结合进行评估和报价。

一到八层电路板的叠层设计方式

一到八层电路板的叠层设计方式一到八层电路板的叠层设计方式电路板的叠层安排是对PCB的整个系统设计的基础。

叠层设计如有缺陷,将最终影响到整机的EMC性能。

总的来说叠层设计主要要遵从两个规矩:1. 每个走线层都必须有一个邻近的参考层(电源或地层);2. 邻近的主电源层和地层要保持最小间距,以提供较大的耦合电容;下面列出从单层板到八层板的叠层:一、单面板和双面板的叠层对于两层板来说,由于板层数量少,已经不存在叠层的问题。

控制EMI辐射主要从布线和布局来考虑;单层板和双层板的电磁兼容问题越来越突出。

造成这种现象的主要原因就是因是信号回路面积过大,不仅产生了较强的电磁辐射,而且使电路对外界干扰敏感。

要改善线路的电磁兼容性,最简单的方法是减小关键信号的回路面积。

关键信号:从电磁兼容的角度考虑,关键信号主要指产生较强辐射的信号和对外界敏感的信号。

能够产生较强辐射的信号一般是周期性信号,如时钟或地址的低位信号。

对干扰敏感的信号是指那些电平较低的模拟信号。

单、双层板通常使用在低于10KHz的低频模拟设计中:1 在同一层的电源走线以辐射状走线,并最小化线的长度总和;2 走电源、地线时,相互靠近;在关键信号线边上布一条地线,这条地线应尽量靠近信号线。

这样就形成了较小的回路面积,减小差模辐射对外界干扰的敏感度。

当信号线的旁边加一条地线后,就形成了一个面积最小的回路,信号电流肯定会取道这个回路,而不是其它地线路径。

3 如果是双层线路板,可以在线路板的另一面,紧靠近信号线的下面,沿着信号线布一条地线,一线尽量宽些。

这样形成的回路面积等于pcb线路板的厚度乘以信号线的长度。

二、四层板的叠层推荐叠层方式:2.1 SIG-GND(PWR)-PWR (GND)-SIG;2.2 GND-SIG(PWR)-SIG(PWR)-GND;对于以上两种叠层设计,潜在的问题是对于传统的1.6mm (62mil)板厚。

层间距将会变得很大,不仅不利于控制阻抗,层间耦合及屏蔽;特别是电源地层之间间距很大,降低了板电容,不利于滤除噪声。

PADS内电层分割与铺铜

欢迎共阅PADS内电层分割与铺铜一、约定软件:PADS?LAYOUT?9.3(PADS2007也可以参考通用步骤)二、一般步骤多层板的分割一般步骤为:定义叠层→设置层的属性(正、负片)→分配网络→分割→铺铜。

首次定义多层板的叠层结构。

四层板堆叠一般为:SIG1/GND/POWER/SIG2;六层板堆叠为:①?SIG1/GND/SIG2/SIG3/POWER/SIG4;?????????????????? ??②?SIG1/GND1/POWER/SIG2/GND2/SIG3;在PADS当中板层定义如下图所示:其次,为电源层分配电源网络。

上图中强调一下“Plane?Type”的问题。

首先从工艺角度讲,内电层实物为薄薄的铜箔。

在制造流程上有“正片”和“负片”之分。

在PADS?LAYOUT中,内电层属性配置当中,CAM?PLANE为负片属性,其他两层为正片属性。

以下部分是摘自PADS?help文件:·?No?Plane—?Prevents?planes?from?being?added?to?the?layer.?The?No?Plane?layer?is ?available?for?routing.?If?you?select?No?Plane,?you?can?only?create?Copper ?and?Copper?Pour?areas?on?the?layer.·?CAM?Plane—?Sets?the?entire?layer?to?be?solid?copper?and?connected?to?only?one?net .?The?CAM?Plane?layer?is?a?negative?image,?and?the?copper?does?not?ap pear?in?the?design?as?it?normally?does?for?all?other?copper?objects.?You?c an?not?manipulate?the?shape/outline?of?the?copper?on?this?layer?since?it?is ?generated?automatically?and?covers?the?entire?layer.?This?is?an?outmoded ?layer?type.?You?can?not?route?traces?on?a?CAM?Plane?layer.?Copper?Pou rs?and?Plane?areas?can?not?be?created?on?CAM?Plane?layers.·?Split/Mixed?Plane—?Enables?one?or?more?planes?on?the?layer,?and?enables?routing?on?the? layer.?Routes?can?be?placed?within?or?without?plane?areas.?Plane?areas?av oid?traces?within?their?outline?by?a?clearance?area?defined?in?the?design?ru les.?Copper?Pours?can?not?be?placed?on?Split/Mixed?layers.?Plane?areas?a re?created?on?Split/Mixed?plane?layers?and?are?similar?to?but?more?feature-packed?than?Copper?Pours.简单的讲,NO?PLANE自由度更大一些,除了“Plane?Area”以及相关的操作命令不能用以外,我们可以在NO?PLANE层进行布线、铺铜、铺铜切割、2D图形边框的绘制等常用操作。

pcb l计算公式

pcb l计算公式(最新版)目录1.PCB 概述2.PCB 布局设计3.PCB 计算公式4.常用 PCB 计算公式详解5.总结正文一、PCB 概述PCB(印刷电路板)是一种用于实现电子设备中电路互联的基板,由导电层、绝缘层和金属化孔等组成。

PCB 在现代电子设备中具有举足轻重的地位,其设计与制造水平直接影响到电子设备的性能和可靠性。

二、PCB 布局设计PCB 布局设计是指将电路原理图中的各个元件、连线、电源、地线等在 PCB 上合理地布置和连接,以实现电路功能的过程。

优秀的 PCB 布局设计可以减小信号干扰、提高产品稳定性、降低生产成本。

三、PCB 计算公式在 PCB 布局设计过程中,涉及到一系列的计算公式,这些公式可以帮助工程师更精确地完成设计。

常用的 PCB 计算公式包括线宽、间距、焊盘尺寸、过孔尺寸等。

四、常用 PCB 计算公式详解1.线宽计算公式线宽(Width)是指印刷电路板上导线或信号线的宽度。

合适的线宽可以减小信号干扰,提高信号传输质量。

常用的线宽计算公式为:线宽(mm)= (电流 I / 电流密度 J)×线阻抗 Z2.间距计算公式间距(Clearance)是指 PCB 上导线或信号线之间的最小距离。

合适的间距可以减小信号干扰,提高信号传输质量。

常用的间距计算公式为:间距(mm)= (信号频率 f ×信号传输速度 V)/ (传输线效应参数α×电磁波速 C)3.焊盘尺寸计算公式焊盘(Pad)是 PCB 上用于焊接元器件的圆形导电区域。

合适的焊盘尺寸可以保证焊接质量,减小焊接不良率。

常用的焊盘尺寸计算公式为:焊盘直径(mm)= (焊盘孔径 D + 焊盘边缘到焊盘孔径D的1/4)× 0.84.过孔尺寸计算公式过孔(Via)是 PCB 上用于连接不同层之间的导电通道。

合适的过孔尺寸可以保证信号传输质量,减小信号干扰。

常用的过孔尺寸计算公式为:过孔直径(mm)= (过孔孔径 D + 过孔边缘到过孔孔径D的1/4)× 0.8五、总结PCB 计算公式在 PCB 布局设计过程中起到了举足轻重的作用,它们可以帮助工程师更精确地完成设计,提高产品性能和可靠性。

叠层结构理论厚度计算公式

106(72%) 1080(63%) 1080(68%) 2116(50%) 2116(54%) 2116(56%) 7628(43%) 7628(45%) 7628(50%)

0.05 0.065 0.075 0.105 0.115 0.125 0.175 0.19 0.215 基材厚度 0.262 2.621 2 2

0 0 0 0 0.23 0 0.35 0 0

备注: 备注:

如左表中在蓝色单元格里 如左表中在蓝色单元格里 的张数、PP型号张数 的张数、PP型号张数 单元格里填上 填上内层板单张厚度 单元格里填上内层板单张厚度 度就会自动计算出结果10 2.621 3.237

压合理论厚度: 压合理论厚度:

蓝色单元格里填上对应铜箔型号 蓝色单元格里填上对应铜箔型号 填上对应 型号张数、内层板张数; 型号张数、内层板张数;在黄色 内层板单张厚度。 内层板单张厚度。压合理论厚 自动计算出结果。 自动计算出结果。

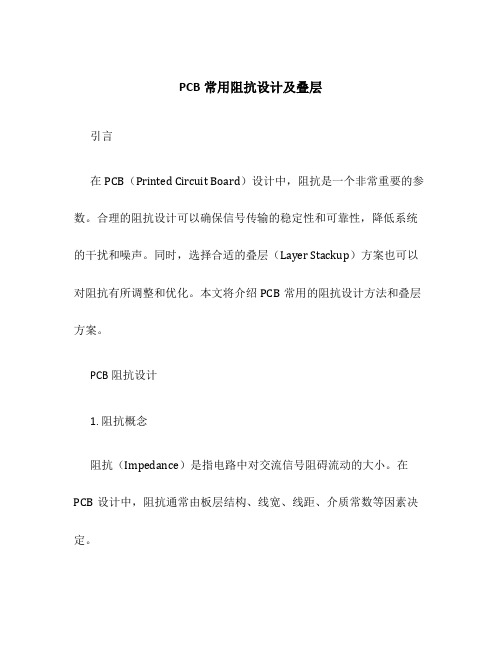

PCB常用阻抗设计及叠层

PCB常用阻抗设计及叠层引言在PCB(Printed Circuit Board)设计中,阻抗是一个非常重要的参数。

合理的阻抗设计可以确保信号传输的稳定性和可靠性,降低系统的干扰和噪声。

同时,选择合适的叠层(Layer Stackup)方案也可以对阻抗有所调整和优化。

本文将介绍PCB常用的阻抗设计方法和叠层方案。

PCB阻抗设计1. 阻抗概念阻抗(Impedance)是指电路中对交流信号阻碍流动的大小。

在PCB设计中,阻抗通常由板层结构、线宽、线距、介质常数等因素决定。

2. 阻抗计算通常,可以使用PCB设计软件或在线计算工具来计算PCB线路的阻抗。

这些工具提供了预设好的阻抗公式和参数,通过输入线路几何尺寸和介质参数即可得到阻抗值。

3. 阻抗控制在PCB设计中,常用的阻抗控制方法有以下几种:A. 线宽/线距控制通过调整线宽和线距可以改变PCB线路的阻抗。

通常,增加线宽和减小线距可以降低阻抗值,反之亦然。

B. 铜箔厚度控制铜箔厚度也是影响PCB线路阻抗的一个重要因素。

增加铜箔厚度可以降低阻抗值,但也会增加制造成本。

C. 介质常数控制PCB板层中的介质常数(Permittivity)也会对线路的阻抗产生影响。

通常,较高的介质常数会导致较低的阻抗值。

D. 叠层设计通过合理设计PCB板层的叠层结构,可以实现对阻抗的控制和优化。

不同的叠层方案可以改变电磁场分布,从而影响阻抗。

4. 阻抗匹配与调试在PCB设计中,除了阻抗的计算和控制,还需要进行阻抗匹配与调试。

通常,在信号源和负载之间不匹配的阻抗会导致信号的反射和损耗。

通过在信号路径中添加阻抗匹配电路,可以有效降低信号的反射损耗。

1. 叠层概念PCB的叠层(Layer Stackup)是指PCB板层的堆叠顺序和结构。

叠层设计直接影响到PCB的信号传输特性、阻抗控制和EMI (Electromagnetic Interference)性能。

2. 叠层结构优化合理的叠层结构可以实现对PCB阻抗的优化和控制。

电路板叠层的设计原则及设计方式

电路板叠层的设计原则及设计方式电路板的叠层安排是对PCB的整个系统设计的基础。

叠层设计如有缺陷,将最终影响到整机的EMC性能。

总的来说叠层设计主要要遵从两个规矩:1、每个走线层都必须有一个邻近的参考层(电源或地层);2、邻近的主电源层和地层要保持最小间距,以提供较大的耦合电容;下面列出从两层板到十层板的叠层:2.1 单面板和双面板的叠层;对于两层板来说,由于板层数量少,已经不存在叠层的问题。

控制EMI辐射主要从布线和布局来考虑;单层板和双层板的电磁兼容问题越来越突出。

造成这种现象的主要原因就是因是信号回路面积过大,不仅产生了较强的电磁辐射,而且使电路对外界干扰敏感。

要改善线路的电磁兼容性,最简单的方法是减小关键信号的回路面积。

关键信号:从电磁兼容的角度考虑,关键信号主要指产生较强辐射的信号和对外界敏感的信号。

能够产生较强辐射的信号一般是周期性信号,如时钟或地址的低位信号。

对干扰敏感的信号是指那些电平较低的模拟信号。

单、双层板通常使用在低于10KHz的低频模拟设计中:在同一层的电源走线以辐射状走线,并最小化线的长度总和;走电源、地线时,相互靠近;在关键信号线边上布一条地线,这条地线应尽量靠近信号线。

这样就形成了较小的回路面积,减小差模辐射对外界干扰的敏感度。

当信号线的旁边加一条地线后,就形成了一个面积最小的回路,信号电流肯定会取道这个回路,而不是其它地线路径。

如果是双层线路板,可以在线路板的另一面,紧靠近信号线的下面,沿着信号线布一条地线,一线尽量宽些。

这样形成的回路面积等于线路板的厚度乘以信号线的长度。

2.2 四层板的叠层;推荐叠层方式:2.2.1 SIG-GND(PWR)-PWR (GND)-SIG;2.2.2 GND-SIG(PWR)-SIG(PWR)-GND;对于以上两种叠层设计,潜在的问题是对于传统的1.6mm(62mil)板厚。

层间距将会变得很大,不仅不利于控制阻抗,层间耦合及屏蔽;特别是电源地层之间间距很大,降低了板电容,不利于滤除噪声。

PCB多层板叠层要求

2.5 中间两块0.8的双面,中间两张7628,两面各一张7628与一张1080

3 中间两块0.8的双面,中间间隙两张7628,两面各两张7628和两张1080

1 中间三块0.15的双面,每间隙两张1080,共八张1080

1.5-1.6 中间三块0.3的双面,中间两间隙各两张1080,两边各一张7628

十层 1.5-1.6 中间四块0.15的双面,每间隙一张7628

2 中间四块0.3的双面,中间三间隙各两张1080,两边两间各一张7628,共两张7628六张1080

1.5-1.6 中间五块0.15的双面,每间隙两张1080,共12张1080

十二层

2 中间五块0.15的双面,中间四间隙各一张7628,两边各一张7628和一张1080,共六张7628两张1080

中间五块0.3的双面,最中间的两个间隙各一张7628和一张1080,其余的四个间隙各两张1080,共十六张1080两 3 张7628

十四层 1.5-1.6 六块0.1的双面,每间隙两张1080,共14张1080

2 六块0.15的双面,最中间的三间隙各一张7628,两边四个间隙各两张1080,共三张7628八张1080

层数 厚度 叠层要求

0.3 中间一块0.1的双面,每面各一张1080

0.6 中间一块0.2的双面,每面各一张7628

0.8 中间一块0.3的双面,每面各一张7628与一张1080

1 中间一块0.6的双面,每面各一张7628

四层

1.2 中间一块0.8的双面,每面各一张7628

1.5-1.6 中间一块0.8的双面,每面各两张7628

1.8 中间三块0.3的双面,中间两间隙各一张7628与一张1080,两面各一张7628

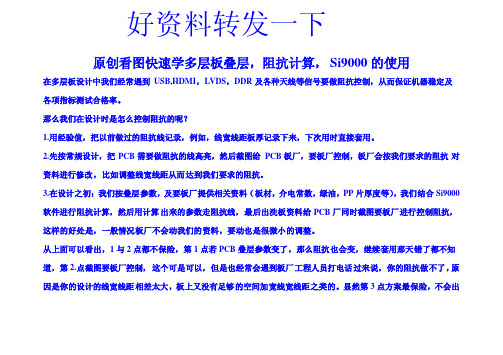

原创看图快速学多层板叠层阻抗计算

好资料丆转发一下

原创看图快速学多层板叠层,阻抗计算,Si9000的使用

在多层板设计中我们经常遇到USB,HDMI,LVDS,DDR及各种天线等信号要做阻抗控制,从而保证机器稳定及各项指标测试合格率。

那么我们在设计时是怎么控制阻抗的呢?

1.用经验值,把以前做过的阻抗线记录,例如,线宽线距板厚记录下来,下次用时直接套用。

2.先按常规设计,把PCB需要做阻抗的线高亮,然后截图给PCB板厂,要板厂控制,板厂会按我们要求的阻抗对资料进行修改,比如调整线宽线距从而达到我们要求的阻抗。

3.在设计之初:我们按叠层参数,及要板厂提供相关资料(板材,介电常数,绿油,PP片厚度等),我们结合Si9000软件进行阻抗计算,然后用计算出来的参数走阻抗线,最后出洗板资料给PCB厂同时截图要板厂进行控制阻抗,这样的好处是,一般情况板厂不会动我们的资料,要动也是很微小的调整。

从上面可以看出,1与2点都不保险,第1点若PCB叠层参数变了,那么阻抗也会变,继续套用那天错了都不知道,第2.点截图要板厂控制,这个可是可以,但是也经常会遇到板厂工程人员打电话过来说,你的阻抗做不了,原因是你的设计的线宽线距相差太大,板上又没有足够的空间加宽线宽线距之类的。

显然第3点方案最保险,不会出

现板厂不能控制阻抗的现象发生。

好了,现在我们开始学习如Si9000的使用,培训内容如下:

1.公司常用叠层模板说明

2.Shortcut to Si9000阻抗计算软件界面讲解。

3.常用阻抗计算模版说明。

4.阻抗计算正推反推教程

5.实列一讲解(单端阻抗包地计算)

6.实例二讲解(差分对阻抗包地讲算)。