verilog实现串并并串转换的代码和仿真结果

VerilogHDL实验报告

VerilogHDL实验报告实验一Modelsim仿真软件的使用一、实验目的(1)熟悉Modelsim 软件(2)掌握Modelsim 软件的编译、仿真方法(3)熟练运用Modelsim 软件进行HDL 程序设计开发二、实验内容1、实验要求用Verilog HDL 程序实现一个异或门,Modelism仿真,观察效果。

2、步骤1、建立工程2、添加文件到工程3、编译文件4、查看编译后的设计单元5、将信号加入波形窗口6、运行仿真3、方法moduleyihuo (a,b,c);inputa,b;output c;assign c=a^b;endmodule测试程序:module t_yihuo;reg a,b; wire c;initial begin a=0; forever #20 a=~a; end initial begin b=0; forever #30 b=~b; endyihuou1(a,b,c);endmodule二、实验结果波形图:三、分析和心得通过这次的实验,我基本熟悉Modelsim软件,掌握了Modelsim软件的编译、仿真方法。

同时在编写程序的过程中,加深了我对课上所讲的HDL的语法的认识。

实验二简单组合电路设计一、实验目的(1)掌握基于Modelsim的数字电路设计方法(2)熟练掌握HDL 程序的不同实现方法二、实验内容1、实验要求设计一个三人表决器(高电平表示通过),实验内容如下:(1)三个人,一个主裁判,两个副裁判;(2)规则:只要主裁判同意,输出结果为通过;否则,按少数服从多数原则决定是否通过。

使用 Verilog HDL 程序实现上述实验内容,并使用modelsim 仿真。

2、方法module test(a,b,c,s);inputa,b,c;output s;assign s=c|(b&a);endmodulemodulet_test;rega,b,c;wire s;initialbegina=0;forever#10 a=~a;endinitialbeginb=0;forever #20 b=~b;endinitialbeginc=0;forever#40 c=~c;endtest u1(a,b,c,s);endmodule三、实验结果四、分析和心得通过本次实验,我掌握基于Modelsim的简单数字电路设计方法,且尝试了用不同方法实现功能,三人表决器可以通过testbench测试程序实现,也可以利用always模块实现,可见程序的设计思想是很重要的。

并串串并转换设计

并串/串并转换电路设计一、实验目的:用verilog语言设计一个8:1的并串转换电路、设计一个1:8的串并转换电路。

二、实验原理:实现8位的并行数据转换为串行的数据:并行转串行,只要把每个输入按从高到低的顺序输出即可。

即每个时钟脉冲输出一个数据。

实现8位的串行数据转换为并行的数据:8位串行数据转换为并行数据,需要一个模为8的计数器,当计到8个时钟脉冲时,把之前的8个数据全部输出,然后从新接收。

三、实验内容:用verilog实现8位的并行数据转换为串行的数据:module bingchuan(out,in,rst,clk);output out;reg out;input [7:0] in;input rst,clk;integer i=0;always@(posedge clk)beginif(rst)out<=0;elsebeginif(i==8)beginout<=0;endelseout<=in[i];i<=i+1;endendendmodulemodule textbingchuan;reg [7:0] in;reg rst,clk;wire out;bingchuan bc(out,in,rst,clk);initial clk=1;always #5 clk=~clk;initialbeginrst=1;#100 rst=0;in=8'b11101110;endendmodule仿真后的波形:用verilog实现8位的串行数据转换为并行的数据:module chuanbing(out,in,rst,clk);output [7:0] out;reg [7:0] out;input in,rst,clk;reg[7:0] temout;reg[2:0] cd;always@(posedge clk)beginif(rst)cd=3'b111;elsebegintemout[cd]<=in;cd<=cd-1'b1;if(cd==3'b111)beginout<=temout;endelseout<=8'bz;endendendmodulemodule textchuanbing;reg rst,clk,in;wire [7:0] out; chuanbing ch(out,in,rst,clk); initial clk =0;always#5 clk=~clk;initialbeginrst=1;#10 rst =0;in=1;#10 in=0;#10 in=1;#10 in=1;#10 in=0;#10 in=1;#10 in=0;#10 in=1;#10 in=1;#10 in=1;#10 in=0;#10 in=1;endendmodule仿真后的波形:。

Quartus-Ⅱ8.1入门教程(一个Verilog程序的编译和功能仿真)

Quartus-Ⅱ8.1入门教程(一个Verilog程序的编译和功能仿真)Quartus Ⅱ8.1入门教程(一个Verilog 程序的编译和功能仿真)Quartus Ⅱ 是Altera 公司推出的专业EDA 工具,支持原理图输入、硬件描述语言的输入等多种输入方式。

硬件描述语言的输入方式是利用类似高级程序的设计方法来设计出数字系统。

接下来我们对这种智能的EDA 工具进行初步的学习。

使大家以后的数字系统设计更加容易上手。

快捷工具●快捷工具栏:提供设置(setting),编译(compile)等快捷方式,方便用户使用,用户也可以在菜单栏的下拉菜单找到相应的选项。

●菜单栏:软件所有功能的控制选项都可以在其下拉菜单中找到。

●信息栏:编译或者综合整个过程的详细信息显示窗口,包括编译通过信息和报错信息。

注意以下命名要一致。

第二步:新建工程(file>new Project Wizard)所建工程的1 工程名称:2第三步:添加文件(file>new> VHDL file),新建完成之后要先保存。

第四步:编写程序以实现一个与门和或门为例,Verilog描述源文件如下:module test(a,b,out1,out2);input a,b;Output out1,out2;assign out1=a&b; assign out2=a | b; endmodule然后保存源文件;第五步:检查语法(点击工具栏的这个按钮(start Analysis & synthesis ))点击确定完成语法检查第六步:(锁定引脚,点击工具栏的(pin planner ))(注:如果不下载到开发板上进行测试,引脚可以不用分配)双击location 为您的输入输出配置引脚。

第七步:整体编译(工具栏的按钮(startComplilation))各个端口顶层某块的第八步:功能仿真(直接利用quratus 进行功能仿真)1 将仿真类型设置为功能仿真(Assignments>setting>Simulator Settings>下拉>Function )2 建立一个波形文件:(new>Vector Waveform File )然后导入引脚(双击Name 下面空白区域>Node Finder>list>点击):接下来设置激励信号(单击>选择>Timing>Multiplied by1)设置b 信号源的时候类同设置a 信号源,最后一步改为然后要先生成仿真需要的网表(工具栏processing>Generate Functional Simulation Netlist )设置输入接下来开始仿真(仿真前要将波形文件保存,点击工具栏开始仿真):观察波形,刚好符合我们的逻辑。

verilog有限状态机实验报告范文(附源代码)

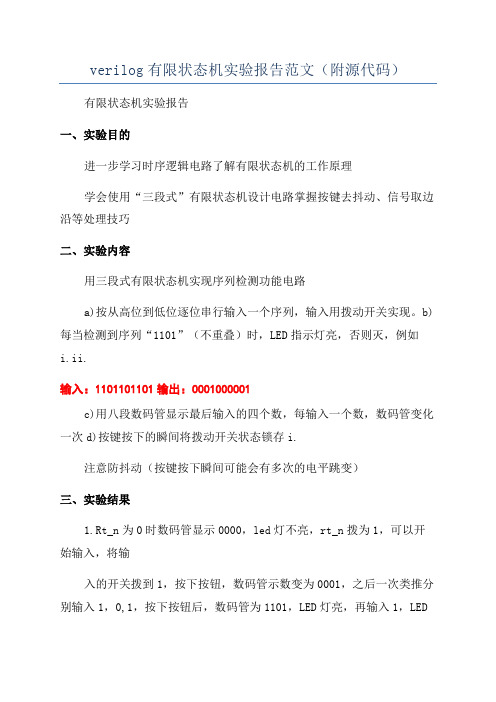

verilog有限状态机实验报告范文(附源代码)有限状态机实验报告一、实验目的进一步学习时序逻辑电路了解有限状态机的工作原理学会使用“三段式”有限状态机设计电路掌握按键去抖动、信号取边沿等处理技巧二、实验内容用三段式有限状态机实现序列检测功能电路a)按从高位到低位逐位串行输入一个序列,输入用拨动开关实现。

b)每当检测到序列“1101”(不重叠)时,LED指示灯亮,否则灭,例如i.ii.输入:1101101101输出:0001000001c)用八段数码管显示最后输入的四个数,每输入一个数,数码管变化一次d)按键按下的瞬间将拨动开关状态锁存i.注意防抖动(按键按下瞬间可能会有多次的电平跳变)三、实验结果1.Rt_n为0时数码管显示0000,led灯不亮,rt_n拨为1,可以开始输入,将输入的开关拨到1,按下按钮,数码管示数变为0001,之后一次类推分别输入1,0,1,按下按钮后,数码管为1101,LED灯亮,再输入1,LED灯灭,之后再输入0,1(即共输入1101101使1101重叠,第二次LED灯不亮),之后单独输入1101,LED灯亮2.仿真图像刚启动时使用rt_n一段时间后其中Y代表输出,即控制led灯的信号,el表示数码管的选择信号,eg表示数码管信号四、实验分析1、实验基本结构其中状态机部分使用三段式结构:2、整体结构为:建立一下模块:Anti_dither.v输入按键信号和时钟信号,输出去除抖动的按键信号生成的脉冲信号op这一模块实现思路是利用按钮按下时会持续10m以上而上下抖动时接触时间不超过10m来给向下接触的时间计时,达到上限时间才产生输出。

Num.v输入op和序列输入信号A,时钟信号clk和复位信号,复位信号将num置零,否则若收到脉冲信号则将num左移一位并将输入存进最后一位。

输出的num即为即将在数码管上显示的值Scan.v输入时钟信号,对其降频以产生1m一次的扫描信号。

Trigger.v这一模块即为状态机模块,按三段式书写。

FPGA乒乓操作及串并转换设计篇

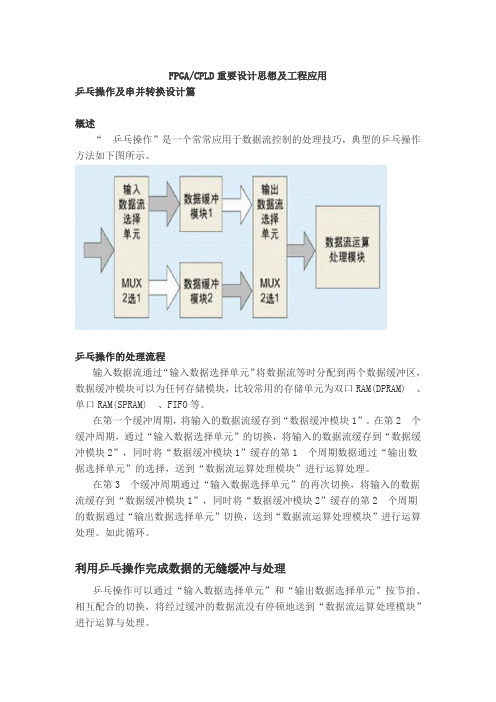

FPGA/CPLD重要设计思想及工程应用乒乓操作及串并转换设计篇概述“乒乓操作”是一个常常应用于数据流控制的处理技巧,典型的乒乓操作方法如下图所示。

乒乓操作的处理流程输入数据流通过“输入数据选择单元”将数据流等时分配到两个数据缓冲区,数据缓冲模块可以为任何存储模块,比较常用的存储单元为双口RAM(DPRAM) 、单口RAM(SPRAM) 、FIFO等。

在第一个缓冲周期,将输入的数据流缓存到“数据缓冲模块1”。

在第2 个缓冲周期,通过“输入数据选择单元”的切换,将输入的数据流缓存到“数据缓冲模块2”,同时将“数据缓冲模块1”缓存的第1 个周期数据通过“输出数据选择单元”的选择,送到“数据流运算处理模块”进行运算处理。

在第3 个缓冲周期通过“输入数据选择单元”的再次切换,将输入的数据流缓存到“数据缓冲模块1”,同时将“数据缓冲模块2”缓存的第2 个周期的数据通过“输出数据选择单元”切换,送到“数据流运算处理模块”进行运算处理。

如此循环。

利用乒乓操作完成数据的无缝缓冲与处理乒乓操作可以通过“输入数据选择单元”和“输出数据选择单元”按节拍、相互配合的切换,将经过缓冲的数据流没有停顿地送到“数据流运算处理模块”进行运算与处理。

把乒乓操作模块当做一个整体,站在这个模块的两端看数据,输入数据流和输出数据流都是连续不断的,没有任何停顿,因此非常适合对数据流进行流水线式处理。

所以乒乓操作常常应用于流水线设计中,完成数据的无缝缓冲与处理。

串并转换串并转换是FPGA 设计的一个重要技巧,它是高速数据流处理的常用手段,串并转换的实现方法多种多样,根据数据的排序和数量的要求,可以选用寄存器、双口RAM(DPRAM) 、单口RAM(SPRAM) 、FIFO 等实现。

若想数据的缓冲区开得很大,可以通过DPRAM 实现了数据流的串并转换,对于数量比较小的设计可以采用寄存器完成串并转换。

如无特殊需求,系统中应该用同步时序设计完成串并之间的转换。

组合-时序逻辑电路Verilog-Testbench代码_带仿真代码和波形_

1组合逻辑电路--基本门电路1.1基本门电路1.1.1结构化描述方式代码如下View Code1 module logics2 (3 input iA,4 input iB,5 output oAnd,6 output oOr,7 output oNot8 );910 and and_inst(oAnd,iA,iB);11 or or_inst(oOr,iA,iB);12 not not_inst(oNot,iA);1314 endmodule最底层的是门级原语and or not RTL级视图testbench如下View Code1 `timescale 1 ns/ 1 ns2 module logics_tb();34 reg ia;5 reg ib;67 wire oAnd;8 wire oOr;9 wire oNot;1011 initial12 begin13 ia=0;14 #40 ia=1;15 #40 ia=0;16 #40 ia=1;17 #40 ia=0;18 end1920 initial21 begin22 ib=0;23 #40 ib=0;24 #40 ib=1;25 #40 ib=1;26 #40 ib=0;27 end2829 logics logics_inst30 (31 .iA(ia),32 .iB(ib),33 .oAnd(oAnd),34 .oOr(oOr),35 .oNot(oNot)36 );3738 endmoduleRTL级仿真图形如下GATE级仿真图如下可见RTL级仿真是理想的,GATE级仿真考虑了延迟和信号开始的不确定。

1.1.2采用流描述方法代码如下View Code1 module logics2 (3 input iA,4 input iB,5 output oAnd,6 output oOr,7 output oNot8 );910 assign oAnd=iA&iB;11 assign oOr=iA|iB;12 assign oNot=~iA;1314 endmoduleRTL级视图,仿真图形同上。

串并转换电路

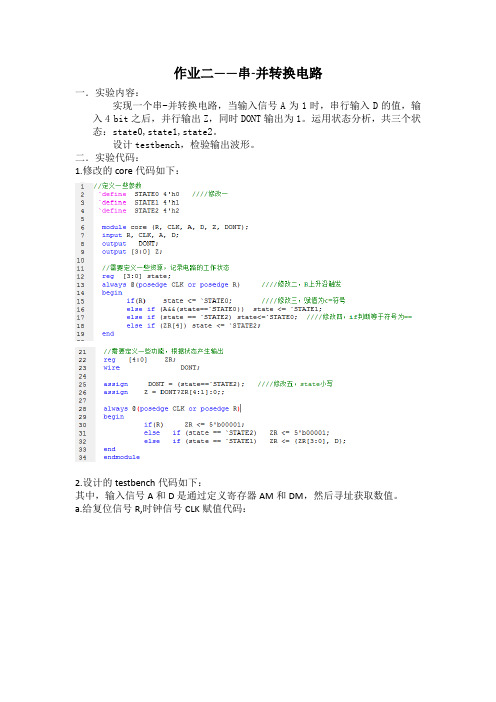

作业二——串-并转换电路

一.实验内容:

实现一个串-并转换电路,当输入信号A为1时,串行输入D的值,输入4 bit之后,并行输出Z,同时DONT输出为1。

运用状态分析,共三个状态:state0,state1,state2。

设计testbench,检验输出波形。

二.实验代码:

1.修改的core代码如下:

2.设计的testbench代码如下:

其中,输入信号A和D是通过定义寄存器AM和DM,然后寻址获取数值。

a.给复位信号R,时钟信号CLK赋值代码:

b.给输入信号A和D赋值代码:

三.仿真波形

1.总的波形

分析:从这幅图中可以看出,当R=1时,所有的信号复位成0,状态为0,之后当A=1给出ready信号之后,开始串行读数,四个时钟周期后,将数值并行输出到Z,同时DONT变为1,回归状态0。

之后再次等待ready信号A=1,如此循环,实现串-并转换。

波形正确。

2.第一个并行输出放大波形:

分析:从这幅图中可以看出,当时钟上升沿读取到A=1,说明准备好读入D 的数值了,D分别为:1,0,1,1,四个时钟之后,Z并行输出1011,同时DONT输出为1,之后回归到状态0,重新开始准备读数。

3.第二个并行输出波形:

分析:这幅图中,当Z输出1011之后,下一个时钟上升沿,虽然D为1,A 也为1,但是由于此时刚读入状态为0,因此还没有开始读数,而是在下一个时钟沿时开始串行读入D,一次读入D为:0,0,1,1,所以最后输出不是1001,而是0011。

verilog之四位全加器的编译及仿真(用开源免费的软件——iverilog+GTKWave)

verilog之四位全加器的编译及仿真(⽤开源免费的软件——iverilog+GTKWave)四位全加器的verilog的代码⽐⽐皆是,这⾥上⼀个⽐较简单的:/*4位全加器全加器需要有输⼊输出,需要有下级向上进位的输⼊,需要有向上⼀位进位的输出。

⼤家看⼀下,这个模块已经包含全部的输⼊输出信息。

⼤家都知道,N位加法器得出来的出来的和最多是N+1位因此可以清晰从下⾯代码中看到相关信息。

然后assign⽤的是阻塞赋值。

相加即满⾜相关的需求。

*/module adder4(cout,sum,ina,inb,cin);output[3:0] sum;output cout;input[3:0] ina,inb;input cin;assign {cout,sum}=ina+inb+cin;endmodule在写testbeach⽂件之前,先普及⼀点testbeach的知识:⼀般来讲,在数据类型声明时,和被测模块的输⼊端⼝相连的信号定义为reg类型,这样便于在initial语句和always语句块中对其进⾏赋值;和被测模块输出端⼝相连的信号定义为wire类型,便于进⾏检测。

Testbench模块最重要的的任务就是利⽤各种合法的语句,产⽣适当的时序和数据,以完成测试,并达到覆盖率要求。

那么testbeach⽂件如下:/*File Name : test_adder4.vDescription : The testbench of the adder_4.vWritten By : LiMingData : 2011/04/18 20:13modefied : 在仿真的时候,把延时从10ns改为5ns: cout显⽰为2位*///test_adder4 (top-level module)`timescale 1ns/1nsmodule test_adder4;//Declare variableswire[3:0] sum;wire cout;reg[3:0] ina,inb;reg cin;//Instantiate the module adder4adder4 adder4_1(cout,sum,ina,inb,cin);//Stimulate the inputs, Finish the stimulation at 90 time unitsinitialbegin#0 ina = 4'b0001; inb = 4'b1010; cin = 1'b0;#5 ina = 4'b0010; inb = 4'b1010; cin = 1'b1;#5 ina = 4'b0010; inb = 4'b1110; cin = 1'b0;#5 ina = 4'b0011; inb = 4'b1100; cin = 1'b1;#5 ina = 4'b0111; inb = 4'b1001; cin = 1'b0;#5 ina = 4'b0001; inb = 4'b1100; cin = 1'b1;#5 ina = 4'b0011; inb = 4'b1100; cin = 1'b0;#5 ina = 4'b0111; inb = 4'b1111; cin = 1'b1;#5 $finish;endinitial$monitor("At time %t, ina(%b) + inb(%b) + cin(%b) = sum(%b)(%2d),cout(%b)",$time, ina, inb, cin, sum, sum, cout);initialbegin$dumpfile("test.vcd");$dumpvars(0,test_adder4);endendmodule由于是在windows的cmd下进⾏命令⾏的运⾏,所以有时候每次输⼊⼀个命令显得很费时间,所以我这⾥⼜写了⼀个(批处理⽂件)bat⽂件:go.batECHO OFFECHO *********************************ECHO * Batch fileECHO *********************************ECHO *ECHO ONiverilog -o test adder4.v test_adder4.vvvp -n test -lxt2cp test.vcd test.lxtgtkwave test.lxt(说明⼀下,我在windows下安装了gnuwin的软件,即能在windows下⽤gnu的⼀些⼩的实⽤的⼯具!)哈哈,这⾥就可以⼀键运⾏了,上⾯的⼀些命令的解释可以到我的“wndows下如何⽤Iverilog+GTKWave进⾏verilog的编译和查看仿真波形”的博⽂⾥去看看吧。

fpga串并转换代码

fpga串并转换代码摘要:1.FPGA 简介2.串并转换的概念3.FPGA 实现串并转换的方法4.串并转换代码实例5.总结正文:一、FPGA 简介FPGA(现场可编程门阵列)是一种集成电路,用户可以通过编程配置其内部的逻辑门和连线,从而实现特定的功能。

FPGA 具有高度的灵活性和可重构性,广泛应用于数字信号处理、通信、图像处理等领域。

二、串并转换的概念串并转换,顾名思义,是指将串行数据转换为并行数据,或者将并行数据转换为串行数据。

这种转换在数据传输和处理过程中具有重要意义,可以有效地提高数据传输的效率和降低硬件复杂度。

三、FPGA 实现串并转换的方法在FPGA 中实现串并转换,通常采用以下两种方法:1.使用查找表(LUT):通过编程配置查找表,将输入的串行数据转换为对应的并行数据。

2.使用串行到并行转换器(S/P 转换器):这是一种硬件电路,通过移位寄存器和逻辑门实现串行数据到并行数据的转换。

四、串并转换代码实例下面以查找表方法为例,给出一个简单的FPGA 串并转换代码实例。

假设输入串行数据为3 位,需要转换为8 位并行数据。

首先,我们需要配置一个3 位到8 位的查找表。

在Verilog 中,可以这样编写:```verilogmodule s_to_p_conv(input wire clk, input wire rst_n, input wire [2:0] s_in, output reg [7:0] p_out){reg [7:0] lut [7:0];integer i;always @(posedge clk or negedge rst_n)beginif (!rst_n)for (i = 0; i < 8; i = i + 1)lut[i] <= 8"b0;elsefor (i = 0; i < 8; i = i + 1)lut[i] <= s_in[i];endassign p_out = lut[s_in[2:0]];endmodule```在上述代码中,我们定义了一个名为s_to_p_conv 的模块,输入信号包括时钟信号clk、复位信号rst_n、输入串行数据s_in,输出并行数据p_out。

交换网络32路复用模块设计verilog

电子科技大学ASIC课程设计报告二学号:201222240937 姓名:周恒课题题目:交换网络32路复用模块设计2013年5月题目要求Develop, verify (before and after synthesis), and synthesize a Verilog module that encapsulates the functionality shown in Fig.2, where the outputs of the A/D converters are inputs to a module that interleaves the sample bytes, with separate sub-modules for the control unit, the mux, the demux, the parallel to serial converter, and the serial to parallel converter. Define additional interface signals as needed to complete the design. Model the multiplexer so that its outputs will be registered. Carefully document your work.图1-2 一个简单的交换控制系统组成本次设计的主要内容为交换网络复用与解复用模块,在下文做出详细设计,包括设计规格书、设计框图、仿真波形和设计结论。

一、设计框图整个系统由5个模块组成,其顶层模块如下图所示:1.控制模块:用于对整个系统的控制,包括复用控制,串并转换控制,并串转换控制和解复用控制。

2.复用模块:对32路输入数据进行复用,依次输入系统。

3.并串转换模块:将8bit的并行数据转换为串行数据。

4.串并转换模块:将对应的串行数据转换为并行数据。

使用FPGA实现并-串转换电路

使用FPGA实现并/串转换电路

并串转换电路在通信接口中具有广泛的应用,可编程逻辑阵列由于具备灵活、可重构等特点非常适应于并串转换硬件电路的实现。

为了解决硬件电路结构中资源与性能的矛盾,分析比较了移位寄存器、计数器与组合逻辑条件判定三种不同的并串转换硬件电路结构,并通过设计仿真对其进行了功能验证和性能评估。

实验结果表明采用移位寄存器的实现方法具有最优的速度性能,采用计数器的实现方法具有最优的性价比,采用组合逻辑条件判定的实现方法具有最少的寄存器资源消耗,可根据实际应用需求合理选择并串转换硬件电路实现方式。

0 引言

并串转换电路作为一种重要的数字信号传输途径,在SPI、I2C、UART

等接口协议及高速SERDES、PCIE等通信接口上具有广泛的应用。

在近年来的集成电路发展中,针对并串转换电路的设计主要有三种途径,分别是采用集成电路定制的设计方式、基于可编程逻辑阵列(Field Programmable Gate Array,FPGA)的设计方式以及采用软件的设计方式。

基于集成电路定制的并串转换电路设计方式由于流片成本高昂,通常仅应用在一些对传输速率要求非常高的场合,如1.25 Gbps的并串转换集成电路、2.5 Gbps的PCIE并串转换电路、1.25 GHz的差分收发芯片以及4G高速并串转换电路等。

而采用。

4位串入并出的移位寄存器verilog代码

移位寄存器是数字电路中常用的一种寄存器,它能够对寄存器中的数据进行左移或右移操作。

在Verilog代码中,实现一个4位串入并出的移位寄存器可以帮助我们更好地理解其工作原理和应用场景。

我们来了解一下移位寄存器的基本原理。

移位寄存器是一种特殊的寄存器,它能够在时钟信号的控制下对其中的数据进行左移或右移操作。

在Verilog代码中,我们可以使用多个触发器来实现移位寄存器的功能,其中每个触发器都能够对数据进行一位的移位操作。

接下来,我们将按照从简到繁的方式来探讨如何使用Verilog代码实现一个4位串入并出的移位寄存器。

我们需要定义一个4位的寄存器,并将其与时钟信号和数据输入信号进行连接。

在每个时钟周期的上升沿,我们可以通过控制信号来实现左移或右移操作,从而实现移位寄存器的功能。

在Verilog代码中,我们可以使用for循环来简化代码的编写,同时也可以使用条件语句来实现左移或右移操作。

在实现移位寄存器的过程中,我们需要考虑到时序逻辑的设计,以确保移位操作能够正确地在每个时钟周期中进行。

我们还需要考虑移位寄存器的应用场景。

移位寄存器在数字信号处理、通信系统和图像处理等领域都有着广泛的应用,它能够对数据进行快速的处理和传输,从而满足不同应用场景的需求。

总结回顾:通过对Verilog代码实现4位串入并出的移位寄存器的探讨,我们深入地了解了移位寄存器的工作原理和应用场景。

在编写代码的过程中,我们需要考虑到时序逻辑的设计,并通过for循环和条件语句来简化代码的编写。

移位寄存器在数字信号处理、通信系统和图像处理等领域都有着广泛的应用,它能够对数据进行快速的处理和传输,满足不同应用场景的需求。

个人观点:我认为Verilog代码实现移位寄存器是一项非常有趣和实用的工作,它能够帮助我们更好地理解数字电路的原理,并在实际应用中发挥重要作用。

通过深入学习和实践,我们能够开发出更加高效和稳定的移位寄存器,从而推动数字电路技术的发展。

verilog--实现数据的串并转换

verilog--实现数据的串并转换并⾏转串⾏--⽤这个测试⽤例是最简单易懂的,这个测试⽤例需要使⽤使能信号端。

当然还可以⽤计数器就稍微⿇烦⼀点。

module parallel(clk, rst_n, en, din, dout);input clk;input rst_n;input en;input [7:0]din;output dout;reg dout;reg [6:0]dout_1;always@(posedge clk )beginif(!rst_n)begin{dout_1,dout} <=8'b0; //通过拼接符,可减少触发器端⼝数endelse beginif(en) begin{dout_1,dout} <= din;endelse begin{dout_1,dout} <= {1'b0,dout_1};endendendendmoduletb:`timescale 1ns/1psmodule parallel_tb;reg clk;reg rst_n;reg en;reg [7:0]din;wire dout;parallel u1(.clk(clk),.rst_n(rst_n),.en(en),.din(din),.dout(dout));initial beginclk=1'b1;rst_n=1'b0;en=1'b0;#8;rst_n=1'b1;#2;en=1'b1;#10;en=1'b0;#70;en=1'b1;#10;en=1'b0;endalways #5 clk=~clk;initial begin#10;din=8'b0110_1100;#80;din=8'b11110000;#150;$stop();endendmodule串⾏转并⾏--每四位进⾏⼀次输出,并含有标志位,串转并:4bit⼀输出。

基于Verilog的数模转换器的设计(5)

基于Verilog的数模转换器的设计电子信息工程专业陈琪[摘要]数/模转换(D/A)电路,是数字系统中常用的电路之一,其主要作用是把数字信号转换成模拟信号,通常是利用专用的数/模转换(D/A)芯片来实现的。

本文的设计为一种8位高速数模转换器,设计方案确定了输入方式为并行输入,输出为电流互补输出,以实现高速的要求,然后在分析了转换电路的性能参数以后,采用主从一分段式的电流舵结构来实现高速数模转换,电流源应用电流分裂技术,其中开关采用全差分电流开关。

在完成硬件结构的基础上,采用verilog-AMS语言对本设计进行了模拟仿真。

[关键词]数模转换电路;并行串出;模拟仿真;可编程逻辑器件Design of the DAC based on VerilogElectronic Information Engineering Specialty CHEN Qi Abstract: D / A converter (D / A) circuit is a circuit commonly used in digital systems, one of its main function is to convert the analog signal digital signal, usually uses a dedicated D / A converter (D / A) chip to achieve of. This article was designed to be a 8-bit high speed DAC design to determine the input for the parallel input and output for the current complementary output, in order to achieve high-speed requirements, and then analyzes the circuit's performance parameters after conversion, with master-slave a sub-type structure to achieve high-speed current-steering digital-analog conversion, Current source application current splitting technique, which uses a fully differential current switch switches. In the completion of the structure based on the use Verilog-AMS language of this design was simulated..Key words:Digital-analog converter circuit; parallel string out; simulation; field programmable gate array目录1 引言 (1)1.1本课题研究的主要内容 (1)1.2国内外研究现状 (1)2 数/模转换电路的结构和功能 (2)2.1数/模转换电路的组成 (2)2.2D/A转换器的结构 (3)3 系统硬件的设计 (4)3.1总体结构设计 (4)3.2单元电路设计 (5)3.2.1 电路网络组态设计 (5)3.2.2 电流开关设计 (7)3.2.3 电流源偏置设计 (8)3.38位D/A转换器 (9)3.3.1 引脚及其功能 (9)3.3.2 DA0832的工作方式 (11)3.3.3 DA0832的功能应用 (11)4 基于VRILOG的行为模型描述 (12)4.1V ERILOG-AMS语言概述 (12)4.2V ERILOG-AMS的行为模型结构 (13)4.3V ERILOG-AMS程序的仿真 (14)5 模拟仿真结果 (15)5.1静态参数模拟 (15)5.2建立时间模拟 (17)结束语 (19)参考文献 (20)致谢 (21)1 引言数/模转换(D/A)电路,是数字系统中常用的电路之一,其主要作用是把数字信号转换成模拟信号,通常是利用专用的数/模转换(D/A)芯片来实现的。

verilog实验

实验二:组合逻辑电路设计一、实验目的:学习组合逻辑电路,学习译码器的功能与定义,学习Verilog语言。

二、实验内容:编写3-8译码器的Verilog 代码并仿真,编译下载验证。

三、实验环境PC 机(Pentium100 以上)、Altera Quartus II 6.0 CPLD/FPGA 集成开发环境、AR1000核心板、SOPC-MBoard板、ByteBlaster II 下载电缆。

四、实验原理译码是编码的逆过程,它的功能是将特定含义的二进制码进行辨别,并转换成控制信号,具有译码功能的逻辑电路成为译码器。

译码器可分为两种类型,一种是将一系列代码转换成与之一一对应得有效信号。

这种译码器可以称为唯一地址译码器,它常用于计算机中对存储器单元地址的译码,即将每一个地址代码换成一个有效信号,从而选中对应的单元。

另一种是将一种代码转换成另一种代码,所以也称为代码变换器。

五、实验过程1.代码2.编译成功3.波形simulation4.仿真波形图实验三:时序逻辑电路设计(一)一、实验目的:学习时序逻辑电路,学习计数器的原理,学习Verilog。

二、实验内容:编写一个带预置输入,清零输入,可加/可减计数器的Verilog 代码并仿真。

三、实验环境PC 机(Pentium100 以上)、Altera Quartus II 6.0 CPLD/FPGA 集成开发环境。

四、实验原理计数器是数字系统中用的较多的基本逻辑器件。

它不仅能记录输入时钟脉冲的个数,还可以实现分频、定时等功能。

计数器的种类很多。

按脉冲方式可以分为同步计数器和异步计数器;按进制可以分为二进制计数器和非二进制计数器;按计数过程数字的增减,可分为加计数器、减计数器和可逆计数器。

本实验就是设计一个4位二进制加减法计数器,该计数器可以通过一个控制信号决定计数器时加计数还是减计数,另外,该寄存器还有一个清零输入,低电平有效。

还有一个load装载数据的信号输入,用于预置数据;还有一个C的输出,用于计数器的级联。

Verilog代码(计数器、交通灯、串并转换)

1、通用二进制计数器设计一个二进制计数器(默认为8位计数器),具有加/减计数功能、异步复位、预制数功能。

代码如下:`define WIDTH 8module BinaryCounter(counter,clk,up_down,load,reset,din);output reg [`WIDTH-1:0] counter;input clk;input up_down; //1为加计数,0为减计数input reset;input load; //预置数,1有效,din输出到counterinput [`WIDTH-1:0] din;always@(posedge clk or posedge reset)beginif(reset)counter<=0;else if(load)counter<=din;else if(up_down==1)counter<=counter+1;else if(up_down==0)begincounter<=counter-1;if(counter<1) counter<=0;endendendmodule测试程序如下:`define WIDTH 8module BinaryCounter_tb;reg clk,up_down,reset,load;reg [`WIDTH-1:0] din;wire [`WIDTH-1:0] counter;integer i;initialbeginclk=0;reset=1;#5 reset=0;#3000 $stop;endalways #5 clk=~clk;/*always@(posedge clk)beginup_down={$random}%2;load={$random}%2;din={$random}%256;end*/initialbegin#5;for(i=0;i<256;i=i+3)begindin=i;#10;endendinitialbeginup_down=1;load=1;#20 load=0;#30 load=1;#30 load=0;endalways #200 up_down=~up_down;BinaryCounter bcounter(.counter(counter),.clk(clk),.up_down(up_down),.load(load),.reset(reset),.din(din));endmodule波形图如下:图1 二进制计数器波形图图2 二进制计数器波形图从图像可看出,20s-50s为加计数,50s-80s时load=1,执行置数功能,80s-200s 时up_down=1,为加计数,200s-280s时up_down=0,为减计数。

软件无线电实验报告

软件无线电实验报告基于 FPGA 的直接序列扩频发射机的设计姓名:学号:联系电话:班级:指导老师:完成时间:2010-07-03目录摘要 (2)正文一、项目名称 (2)二、项目描述 (2)三、实验要求 (3)四、实验设备与仿真环境 (4)五、总体设计与系统框图 (4)六、各模块设计与仿真1)时钟模块 (5)2)待发射模块设计 (7)3)卷积模块设计................... . (10)4)扩频模块设计....................... .......... . .. (13)5)极性变换与内插模块设计................... . (15)6)基带滤波模块设计............................ .. (16)七、系统联调仿真........ ................ .... (17)八、MATLAB仿真 (18)九、实验总结与体会 (20)【摘要】扩展频谱通信系统(Spread Spectrum Communication System)是指将待传输信息的频谱用某个特定的扩频函数扩展后成为宽频带信号,送入信道中传输,接收端再利用相应手段将其解扩,从而获取传输信息的通信系统。

扩频信号是不可预测的伪随机的宽带信号;它的带宽远大于欲传输信息(数据)带宽;具有类似于噪声的随机特性等。

直接序列扩频(DSSS)是扩频通信方式中的一种,实现简单,应用广泛。

【正文】一、项目名称本文以Altera公司的FPGA为硬件平台,以MAX-PLUSII为设计工具,实现直接基于FPGA的直接序列扩频发射机的设计序列扩频(DSSS)发射机,顶层采用图形设计方式,各模块是基于Verilog HDL设计的。

本设计中待发射信息是以循环读ROM的方式读取,信道编码采用(2,1,7)卷积码,扩频模块采用扩频长度255的kasami码,极性变换模块为3bit二、项目描述量化模式,内插模块为每两比特间插入7bit,输出滤波为16阶的FIR滤波器。

使用VerilogHDL进行数字逻辑设计、综合、仿真的步骤及工具软件使用简要说明[指南]

![使用VerilogHDL进行数字逻辑设计、综合、仿真的步骤及工具软件使用简要说明[指南]](https://img.taocdn.com/s3/m/236b285dce84b9d528ea81c758f5f61fb73628db.png)

使用V erilog HDL进行数字逻辑设计、综合、仿真的步骤及工具软件使用简要说明综合工具使用synplify pro 7.0仿真工具使用modelsim 5.5e (几个菜单排列与5.6有不同,文中有介绍)布局布线工具及时序仿真模型生成使用maxplusII 10.0一.写在开干之前1.涉及到的文件a.源程序(*.v)用户编写的用于描述所需电路的module (可能有多个文件,多个module相互调用)如果用于综合,则源程序内用于描述的V erilog语言必须是可综合风格的。

否则将只能做功能仿真(前仿真),而不能做综合后的仿真和时序仿真(后仿真)。

b.综合后的V erilog HDL 模型(网表) (*.vm)用综合工具synplify对a 进行综合后生成的电路的V erilog HDL 描述。

由synplify自动生成(必须在Implementation Option —Implementation results选项中选中write mapped verilog netlist后才会生成vm文件)。

此文件用于作综合后的仿真c.布局布线后生成的时序仿真模型(网表) (*.vo)文件使用maxplusII对设计进行布局布线之后,生成的带有布局布线及具体器件延迟特性等参数的电路模型的V erilog HDL描述。

要让maxplusII生成vo文件,必须在maxplusII的compile interface中选中verilog netlist writer。

此文件用于作时序仿真(后仿真)d.测试文件(*.v或*.tf)用户编写的V erilog HDL源程序。

用于测试源程序(a,b,c)中所描述电路。

在测试文件中调用被测试的module,生成被测点路所需的输入信号。

所用V erilog HDL语句不需要是可以综合的,只需语法正确。

如果被测试的模型为a,则对应的仿真为前仿真(功能仿真)如果被测试的模型为b, 则对应的仿真为综合后仿真如果被测试的模型为c, 则对应的仿真为后仿真2.强烈建议a.在写用于综合的源程序时,一个源程序文件里只写一个moduleb.源程序文件名与其内所描述的module名相同(如module myadder 文件名myadder.v)c.为了方便管理文件,为每一个设计都单独创建一个目录,目录内创建source, test子目录分别用于存放源程序(用于综合的)和测试文件。

fpga串并转换代码

FPGA串并转换代码1. 任务概述FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,可以通过编程来实现各种数字逻辑电路。

串并转换是一种常见的数字电路转换方式,用于将串行数据转换为并行数据或将并行数据转换为串行数据。

本任务旨在编写FPGA串并转换的代码,实现数据的转换和传输。

2. 串并转换原理串并转换是指将串行数据转换为并行数据或将并行数据转换为串行数据的过程。

在串并转换中,串行数据一次只传输一位,而并行数据一次可以传输多位。

2.1 串到并转换串到并转换的原理如下:1.将串行数据的每一位按照顺序存储在FPGA的寄存器中。

2.在时钟信号的控制下,将每个寄存器的值同时输出,形成并行数据。

2.2 并到串转换并到串转换的原理如下:1.将并行数据的每一位同时存储在FPGA的寄存器中。

2.在时钟信号的控制下,按照顺序将每个寄存器的值输出,形成串行数据。

3. FPGA串并转换代码实现FPGA串并转换代码的实现主要包括以下几个步骤:1.设计FPGA的输入和输出接口。

2.编写串到并转换的代码。

3.编写并到串转换的代码。

4.进行仿真和调试。

3.1 设计FPGA的输入和输出接口在FPGA中,我们需要设计合适的输入和输出接口来连接外部的串行或并行数据。

可以使用FPGA开发板上的GPIO(General Purpose Input/Output)接口来实现。

3.2 编写串到并转换的代码串到并转换的代码可以使用Verilog或VHDL等硬件描述语言编写。

以下是一个简单的串到并转换的Verilog代码示例:module serial_to_parallel(input wire clk,input wire reset,input wire serial_data,output wire [7:0] parallel_data);reg [7:0] shift_reg;always @(posedge clk or posedge reset) beginif (reset)shift_reg <= 8'b00000000;elseshift_reg <= {shift_reg[6:0], serial_data};endassign parallel_data = shift_reg;endmodule3.3 编写并到串转换的代码并到串转换的代码与串到并转换的代码类似,只是操作的方向相反。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

begin

r <= 4'h0;//如果复位信号rst_n为低电平输出0000

end

else if(load)//如果load信号为高电平,可以输入信号

begin

r <= pi;//把输入值r数组

end

else//如果load为低电平则完成输出功能

begin

r <= {r, 1'bx};//移位寄存器的实现,如果r输出到so,则给r已经输//出了的位置为x

if(r[3]||~r[3])//判断r寄存器是否已经全部清空为x

begin

so = r[3];

if(r[2]||~r[2])//在r2没有输出之前biaozhi为0

biaozhi=1'b0;

else//当r3刚刚跳变的瞬间,biaozhi变为1

biaozhi=1'b1;

end

else

begin

so=1'bx;//没有信号输入时so置为不定态

load <= 1'b1;

pi <= 4'b1100;

#20;

load <= 1'b0;

pi <= 4'hxxxx;

#90

load<=1'b1;

pi<=4'hxxxx;

reg [3:0] pi;

wire [3:0] po;

wire so;

reg flag;

//reg biaozhi;

initial begin

flag=1'b1;

#400;

flag=1'b0;

end

initial begin

en = 1'b0;

si = 1'b0;

#10;

// 4'b1010输入si为1010该信号为合法输入

源代码

测试代码

3

2.3.1程序代码及测试代码已标注本人完成部分,且赋较详细注释

源代码:

module spps (

clk,

rst_n,

en,

si,

po,

flag,

load,

pi,

so,

biaozhi

);

input clk;

input rst_n;

input en;

input si;

input load;

input flag;

input [3:0] pi;

output reg so;

output reg [3:0] po;

output reg biaozhi;

reg [3:0] r;

always@(posedge clk )

if(flag)

begin

if(~rst_n)

begin

r <= 8'h0;

end

else

begin

r = {r, si};

if(si||~si)

begin

po = (en) ? r :4'h0;

biaozhi=(en)?1'b1:1'b0;

end

else

begin

po=4'hxxxx;

biaozhi=1'b0;

end

end

end

else

begin/*以下部分由本人完成*/

另外,在本程序中,采用了x来表示功能实现失败,即如果输入的串行数据少于四个,则在输出的四位数为x态。在并转串中,在最后一位串行输出实现时,biaozhi为1,否则为0,表示尚未完成输出。

具体实现中,如果有输入,即si||~si,则在en(使能位)为1时让所存在触发器中的输入变量输出。但是如果si输入的值少于四个,则输出四个x态。由于测试代码中en在最后一个周期赋值为1,所以之前的输入并不能同步输出,而是锁存起来了。这样就实现了少于四位输出x状态的功能。具体实现如下

1

1.1

串并转换电路是串行通信系统中重要的组成部分。在

从图中可以看出,并串转换的原理是:先将四位数据暂存于一个四位寄存器器中,然后左移输出到一位输出端口,这里通过一个“移位”指令就可以了。

从图中可以看出,串并转换的原理是:新输入的位值成为原来数据的最低位,将原来数据的最高位舍去,这里可以通过一个简单的“连接符”就能做到。

si = 1'b1;

#20;

si = 1'b0;

#20;

si = 1'b1;

#பைடு நூலகம்0;

en = 1'b1;//将en信号此时赋为1,此时输出po

si = 1'b0;

#20;

en = 1'b0;

si = 1'bx;

end

initial begin

load = 1'b0;

pi = 4'hxxxx;

#400;

2

2.1

在本程序中要实现两个功能,即串行到并行和并行到串行的分别转换。在一个模块中,需要使用一个标志位flag,flag为1时,实现串行到并行的转换,flag为0时,实现串行到并行的转换。需要把flag当做module的一个输入端口,并在测试代码中表现出来。

2.2

本程序中采用biaozhi作为标志,若变量biaozhi为1,则代表转换成功,为零代表转换失败。设计标志位的原因是本程序中,在串行输入时,当输入位数少于4,则无法实现串转并的功能。

题目:串并互换电路的设计

系(部):***

专业班:***

姓名:***

学号:***

指导教师:***

完成比例:**

2011年12月

摘

本文主要讲述用verilog实现串并互换电路,在同步时钟的控制下,四位的并行数据和串行数据相互转换,通过一位的控制信号来控制该电路为串并或并串转换,最后由串并有效位来表示串并互换成功。

关键词:串转并并转串移位寄存器

Abstract

This paper deals with verilog realize string and swap circuit, in synchronous clock under the control of four parallel data and serial data transformation, through a control signals to control the circuit for the series and or and string of conversion, finally by string and effective to say a string and swap success.Key Words:Parallel turns to serialserial turns to parallelShift register

biaozhi=0;//标志重新归零

end

end

end

endmodule/*以上部分有本人完成*/

测试代码1:

`timescale 1ns/1ns

`include "e:/spps(4)/spps.v"

module spps_tb;

reg clk;

reg rst_n;

reg en;

reg si;

reg load;