基于AD7606 的可扩展多通道同步采样数据采集系统的布局考虑

基于AD7606的多通道数据采集系统设计

基于AD7606的多通道数据采集系统设计

陶海军;张一鸣;曾志辉

【期刊名称】《工矿自动化》

【年(卷),期】2013(039)012

【摘要】针对DSP芯片TMS320F2812自带的AD转换模块不能满足同步采集电流和电压参数要求的问题,设计了一种基于AD7606的多通道数据采集系统.详细介绍了系统中电压/电流输入电路、输入滤波电路、AD7606与TMS320F2812接口电路、AD转换程序的设计.测试结果表明,与TMS320F2812自带的AD转换模块进行AD转换的结果相比,采用AD7606进行AD转换的结果精度高、误差小,适合高精度AD转换电路.

【总页数】4页(P110-113)

【作者】陶海军;张一鸣;曾志辉

【作者单位】北京工业大学电子信息与控制工程学院,北京 100124;河南理工大学电气工程与自动化学院,河南焦作454003;北京工业大学电子信息与控制工程学院,北京 100124;北京工业大学电子信息与控制工程学院,北京 100124;河南理工大学电气工程与自动化学院,河南焦作454003

【正文语种】中文

【中图分类】TD67

【相关文献】

1.基于AD7606的同步多通道语音采集系统设计 [J], 王森

2.基于AD7606的智能电网数据采集系统设计 [J], 王水鱼;王伟

3.基于AD7606的树莓派多通道数据采集系统设计 [J], 刘喜梅;吕文韬

4.基于FPGA的多通道数据采集系统设计应用 [J], 王旭东;陈涛;郑磊

5.基于FPGA的多通道数据采集系统设计应用 [J], 王旭东;陈涛;郑磊

因版权原因,仅展示原文概要,查看原文内容请购买。

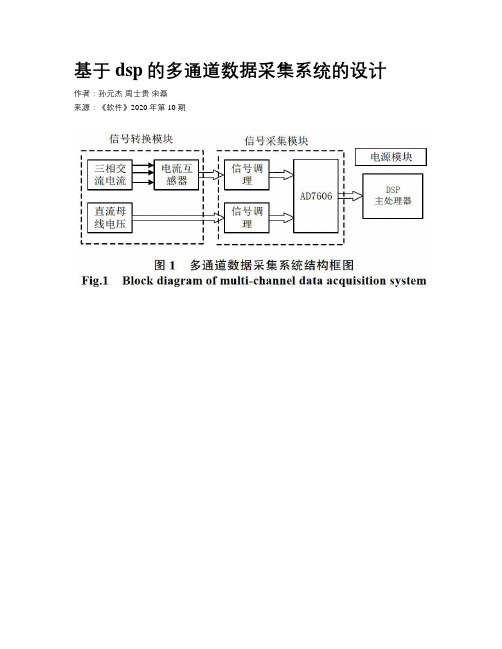

基于dsp的多通道数据采集系统的设计

基于dsp的多通道数据采集系统的设计作者:孙元杰周士贵宋磊来源:《软件》2020年第10期摘要:针对DSP内部AD采样电路精度低等问题,设计了一种以AD7606高精度实时的模数转换器,进行采集交流信号,并介绍分析了AD7606得硬件电路和软件设计。

最后通过实验对比了DSP TMS320F28335内部AD和AD7606这两种模数转换得精度,相对于DSP TMS320F28335内部AD,AD7606具有采样精度更高,误差小,能够高速采样,适用于永磁同步电机的数据得采集转换。

关键词: AD7606;硬件电路;高速采样中图分类号: TP274.2 文献标识码: A DOI:10.3969/j.issn.1003-6970.2020.10.026本文著录格式:孙元杰,周士贵,宋磊. 基于DSP的多通道数据采集系统的设计[J]. 软件,2020,41(10):105108【Abstract】: Aiming at the low accuracy of the internal AD sampling circuit of the DSP, a high-precision real-time digital-to-analog converter based on the AD7606 is designed, and the hardware circuit and software design of the AD7606 are introduced and analyzed. Finally, the two AD-analog conversion precisions in the DSP TMS320F28335 and AD7606 are compared throughexperiments. Compared with the DSP TMS320F28335 AD, the AD7606 has higher sampling accuracy, less error, and high real-time performance. Acquisition conversion.【Key words】: AD7606; Hardware circuit; High-speed sampling0 引言隨着永磁同步电机的广泛应用,各种控制算法控制理论的不断在永磁同步电机的控制中应用。

基于AD7606的同步多通道语音采集系统设计

基于AD7606的同步多通道语音采集系统设计

王森

【期刊名称】《电子质量》

【年(卷),期】2018(0)3

【摘要】语音是用于信息交流的重要媒介,清晰的提取语音信号是准确信息传递的前提,面对日益复杂的声场环境,麦克风阵列系统以优异的性能逐渐替代单麦克风系统.为了更好地应用麦克风阵列实现语音定位与增强,设计了一款包含低噪声前置放大器、信号调理电路和高速多路同步采集ADC的麦克风阵列系统.经过试验,该系统能够清晰准确地实现多路语音信号采集.

【总页数】3页(P31-33)

【作者】王森

【作者单位】山东科技大学电气与自动化工程学院,山东青岛266590

【正文语种】中文

【中图分类】TP274+.2

【相关文献】

1.基于AD7606的多通道数据采集系统设计 [J], 陶海军;张一鸣;曾志辉

2.基于AD7606的SVG数据同步采集系统设计 [J], 黄华钦;刘桂英;周路平;曾林俊;胡宸

3.基于FPGA的多通道同步实时高速数据采集系统设计 [J], 易志强;韩宾;江虹;张秋云

4.基于GD32F407及CL1606的多通道同步采集系统设计 [J], 罗瑞;徐涛;卢少微;

马克明

5.基于AD7606的树莓派多通道数据采集系统设计 [J], 刘喜梅;吕文韬

因版权原因,仅展示原文概要,查看原文内容请购买。

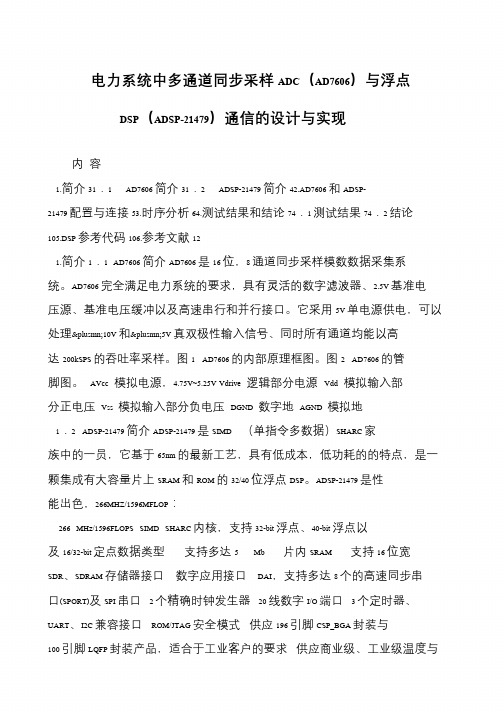

电力系统中多通道同步采样ADC(AD7606)与浮点DSP(ADSP-21479)通信的设计与实现

电力系统中多通道同步采样ADC(AD7606)与浮点DSP(ADSP-21479)通信的设计与实现内容1.简介31.1 AD7606 简介31.2 ADSP-21479 简介42.AD7606 和ADSP- 21479 配置与连接53.时序分析64.测试结果和结论74.1 测试结果74.2 结论105.DSP 参考代码106.参考文献121.简介1.1 AD7606 简介AD7606 是16 位,8 通道同步采样模数数据采集系统。

AD7606 完全满足电力系统的要求,具有灵活的数字滤波器、2.5V 基准电压源、基准电压缓冲以及高速串行和并行接口。

它采用5V 单电源供电,可以处理±10V 和±5V 真双极性输入信号、同时所有通道均能以高达200kSPS 的吞吐率采样。

图1 AD7606 的内部原理框图。

图2 AD7606 的管脚图。

AVcc 模拟电源,4.75V~5.25V Vdrive 逻辑部分电源Vdd 模拟输入部分正电压Vss 模拟输入部分负电压DGND 数字地AGND 模拟地1.2 ADSP-21479 简介ADSP-21479 是SIMD (单指令多数据)SHARC 家族中的一员,它基于65nm 的最新工艺,具有低成本,低功耗的的特点,是一颗集成有大容量片上SRAM 和ROM 的32/40 位浮点DSP。

ADSP-21479 是性能出色,266MHZ/1596MFLOP:266 MHz/1596FLOPS SIMD SHARC 内核,支持32-bit 浮点、40-bit 浮点以及16/32-bit 定点数据类型支持多达5 Mb 片内SRAM 支持16 位宽SDR、SDRAM 存储器接口数字应用接口DAI,支持多达8 个的高速同步串口(SPORT)及SPI 串口 2 个精确时钟发生器20 线数字I/O 端口 3 个定时器、UART、I2C 兼容接口ROM/JTAG 安全模式供应196 引脚CSP_BGA 封装与100 引脚LQFP 封装产品,适合于工业客户的要求供应商业级、工业级温度与。

基于AD7606的高精度数据采集系统的实现

基于AD7606的高精度数据采集系统的实现

肖李欢;黄元峰;代文泽;张兴

【期刊名称】《电脑知识与技术》

【年(卷),期】2017(013)020

【摘要】该文针对单片机内部AD采样模块的分辨率较低以及不能同步采样不同信号的问题,提出了基于AD7606的高精度的16位八通道数据采集系统.重点分析该采样系统的硬件电路的原理,并介绍了AD采样的软件设计的时序图与流程图,根据性能测试数,相对于常见的一些12位AD采样模块,采用AD7606的AD采样的误差小、精度高,适用于精度要求较高的场合.

【总页数】3页(P210-211,214)

【作者】肖李欢;黄元峰;代文泽;张兴

【作者单位】武汉工程大学电气信息学院,湖北武汉430205;武汉工程大学电气信息学院,湖北武汉430205;武汉工程大学电气信息学院,湖北武汉430205;武汉工程大学电气信息学院,湖北武汉430205

【正文语种】中文

【中图分类】TP311

【相关文献】

1.基于FPGA实现的AD1674高精度快速数据采集系统 [J], 徐大诏

2.基于AD7175-2的高精度数据采集系统设计与实现 [J], 严小明;谭建宇;谢明

3.基于高精度定位的通用型GIS数据采集系统的设计与实现 [J], 吴斌晖

4.基于MSP430F149的高精度压力数据采集系统的设计和实现 [J], 刘洪刚; 陈永奇; 张连凯

5.基于高精度定位的通用型GIS数据采集系统的设计与实现 [J], 吴斌晖

因版权原因,仅展示原文概要,查看原文内容请购买。

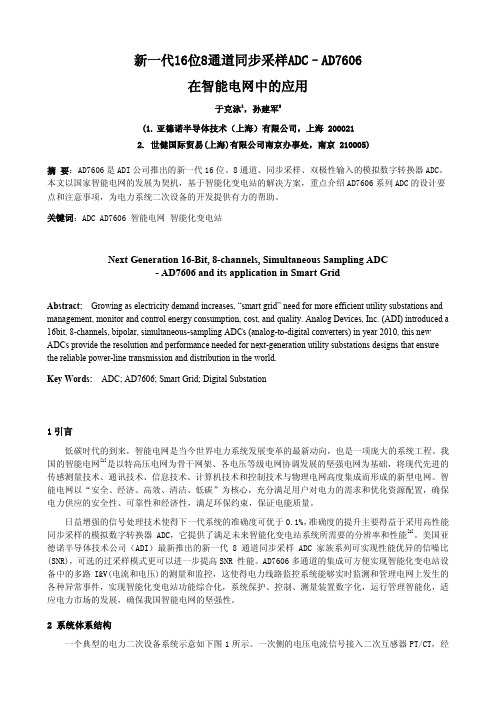

ADC–AD7606

新一代16位8通道同步采样ADC–AD7606在智能电网中的应用于克泳1,孙建军2(1.亚德诺半导体技术(上海)有限公司,上海 2000212. 世健国际贸易(上海)有限公司南京办事处,南京 210005)摘要:AD7606是ADI公司推出的新一代16位、8通道、同步采样、双极性输入的模拟数字转换器ADC。

本文以国家智能电网的发展为契机,基于智能化变电站的解决方案,重点介绍AD7606系列ADC的设计要点和注意事项,为电力系统二次设备的开发提供有力的帮助。

关键词:ADC AD7606 智能电网智能化变电站Next Generation 16-Bit, 8-channels, Simultaneous Sampling ADC- AD7606 and its application in Smart GridAbstract:Growing as electricity demand increases, “smart grid” need for more efficient utility substations and management, monitor and control energy consumption, cost, and quality. Analog Devices, Inc. (ADI) introduced a 16bit, 8-channels, bipolar, simultaneous-sampling ADCs (analog-to-digital converters) in year 2010, this new ADCs provide the resolution and performance needed for next-generation utility substations designs that ensure the reliable power-line transmission and distribution in the world.Key Words: ADC; AD7606; Smart Grid; Digital Substation1引言低碳时代的到来,智能电网是当今世界电力系统发展变革的最新动向,也是一项庞大的系统工程。

基于AD7606的智能电网数据采集系统设计

基于AD7606的智能电网数据采集系统设计王水鱼;王伟【摘要】In view of the requirement of the measurement and monitoring of multi-channel current and voltage in the intelligent substation equipment, a multi-channel data acquisition system based on AD7606 is designed.This paper introduces the working characteristics and the setting of common working mode of the 16 bit,8 channel ADC chip AD7606 in detail.Based on this, the software code for the control and signal transmission of analog / digital converter with Field Programmable Gate Array(FPGA) as the core controller is designed.The system can realize data transmission between serial bus and PC, which is suitable for the collection of power system parameters in smart grid.%鉴于智能化变电站设备中的多路电流和电压的测量和监控需求,设计了一种基于AD7606的多通道数据采集系统.详细介绍了16位、8通道模数转换芯片AD7606的工作特性及常用工作方式设置,以此为基础设计了以现场可编程门阵列(Field-Programmable Gate Array,FPGA)为核心控制器的模/数转换的控制和信号传输的软件代码.该系统可通过串口总线与PC之间实现数据交换,适用于智能电网中电力系统参数的采集.【期刊名称】《微型机与应用》【年(卷),期】2016(035)022【总页数】3页(P8-10)【关键词】数据采集;多通道;AD7606;FPGA【作者】王水鱼;王伟【作者单位】西安理工大学,陕西西安 710048;西安理工大学,陕西西安 710048【正文语种】中文【中图分类】TM93当今世界电力系统发展和变革日新月异,进入21世纪,智能电网成为最新动向,并逐步成为一项庞大的系统工程。

基于AD7606-6的STATCOM信号采集模块设计

基于AD7606-6的STATCOM信号采集模块设计陈华;杨升振;苏之山;罗世杰;梁永【摘要】STATCOM作为新一代无功功率补偿装置,具有实时快速准确的补偿特性,其特性的发挥前提是需要快速精确同步的采集三相电压电流.为此,设计了以AD7606-6为核心的前端采集电路.在介绍STATCOM的基本结构和工作原理的基础上,阐述了AD7606-6的特性、引脚功能、并行数据输出时序逻辑.最后,设计了信号调理的AD7606-6与TMS320F2812接口电路,给出了软件设计部分.实验测试表明,该采集模块达到了STATCOM对电量参数采集的要求.【期刊名称】《电子科技》【年(卷),期】2013(026)003【总页数】5页(P35-38,41)【关键词】AD7606-6;STATCOM;电量信号采集;TMS320F2812【作者】陈华;杨升振;苏之山;罗世杰;梁永【作者单位】桂林电子科技大学机电工程学院,广西桂林541004【正文语种】中文【中图分类】TN911;TM930.2在电网适当地点合理添加无功功率补偿设备对电网进行无功功率补偿是提高电能质量的方法之一。

STATCOM作为一种新型无功功率补偿设备,已成为柔性交流输电系统(FACTS)的一个重要组成部分,是未来无功功率补偿设备的发展方向。

和其他无功补偿设备如SVC相比,具有响应速度快;不会引起谐振短路;无功功率可以在感性和容性之间连续调节;利用PWM调制技术实现精准的电压调控;可同时对谐波和无功进行补偿[1]。

要实现STATCOM实时快速准确的补偿特性,必须建立在对电网无功功率、有功功率、谐波等电量参数的实时快速准确测量基础上。

基于瞬时无功功率理论的无功功率检测算法,进行的多是瞬时值运算,响应速度快,适用于变化快、冲击大的无功功率和电压闪变的补偿。

但瞬时无功功率理论的应用要求同步采样电网某时刻的三相电压电流,针对此情况,文中设计了由AD7606-6模数转换芯片与TMS320F2812组成的数据采集模块。

AD7606在电力系统参数采集中的应用与设计

AD7606在电力系统参数采集中的应用与设计【摘要】介绍了基于TI公司TMS320F2812和16位A/D芯片AD7606在电力系统参数采集系统中二者的接口设计,并详细介绍了A/D转换的控制和实现过程的软件程序实现。

该系统可通过串口总线或以太网与PC机之间实现数据交换,同时也可以在本地对数据进行处理,能适用于电力系统参数的采集。

【关键词】DSP;AD7606;TMS320F2812;A/D转换1.引言电力系统不仅对电流、电压、功率、频率等参数采集的实时性和精确性要求较高,而且对采集的主要技术指标,如采样速率、分辨率、输入电压范围、控制方式以及抗干扰能力等方面也提出了越来越高的要求[1]。

电力系统参数的采集对系统的稳定运行有着至关重要的作用。

因此如何快速、准确地采集各种参数就显得十分的重要[2]。

本文介绍了采用高速定点DSP芯片TMS320F2812DSP和高速A/D转换芯片AD7606的方案在电力参数采集系统中的应用。

重点介绍二者的接口设计、转换的控制和采集过程的软件实现。

2.芯片及其特点2.1 A/D转换芯片AD7606AD7606为16位同步采样模数数据转换芯片,每个芯片有8个采集通道。

AD7606能完全满足电力系统对采样的要求。

它具有灵活的数字滤波器、2.5V基准电压源以及高速并行接口。

它采用5V单电源供电,不再需要正负双电源并支持真正的双极性信号输入。

所有的通道均能以高达200kSPS的速率进行采样,同时输入端箝位保护电路可以承受最高达±16.5V的电压[3]。

相比其它的采样芯片,AD7606有以下几个显著地优点:(1)系统中包含的电流/电压互感器的数量会有多个,对ADC总通道数的需求往往超过12个。

以往的A/D采样芯片一般为6通道,需要采用3片才能满足要求。

而AD7606是8通道采样芯片,两个AD7606完全能满足系统的需要。

(2)简化了前端设计,不再需要外部驱动和滤波电路[4]。

基于AD7606的高性能电力线监测、继电保护系统设计指南

基于AD7606的高性能电力线监测、继电保护系统设计指南随着全球电网持续的发展,电力线监测、继电保护产品在不断地更新换代并改变着设计模式。

作为全球领先的高性能信号处理解决方案供应商,ADI公司 (/zh/pr0513 )推出的系列高性能ADC一直引领该领域的技术发展路线:第一代电力继电保护产品均采用模拟开关,采用单通道16位ADC(如AD976 (/zh/pr0513/ad976)、AD574)进行设计;后来出现了使用16位的AD7656 (/zh/pr0513/ad7656)和14位的AD7865 (/zh/pr0513/ad7865)配合模拟开关的第二代继电保护产品,AD7656和AD7865在当前很多电力继电保护产品中仍有非常成功的应用案例;随着技术的更新和产品工艺的改进,尤其是其±10V双极多通道同步输入等技术特点,使AD7656成为上一代电力继电保护的主流选择,目前该产品仍在大量的电力监测及保护设备中发挥重要作用。

随着电网智能化管理发展趋势,电力线监测及保护产品设计面临越来越多的挑战,多通道电流与电压监控系统的设计人员需要应对诸如双电源、有限的模拟输入范围、低模拟输入阻抗、以及采用昂贵的分立器件所造成的高成本等一系列复杂的设计挑战。

作为电力二次设备制造商的关键方案提供商,ADI公司深刻理解全球电力设备企业的技术需求,在AD7656成功应用的经验基础之上,再次成功推出16位8通道同步采样AD7606 (/zh/pr0513/ad7606)系列,帮助客户更好地应对智能电网时代开发二次设备所面临的技术挑战。

图1:ADI公司高性能ADC产品发展路线图。

AD7606简化电力线监测系统设计AD7606系列器件采用单5V供电,并支持真正的±10V和±5V双极性信号输入,每通道的采样率能达到200ksps。

单芯片内集成多个通道可支持变电站自动化设备中三相电流、电压和零线的测量。

16位8通道DAS AD7606

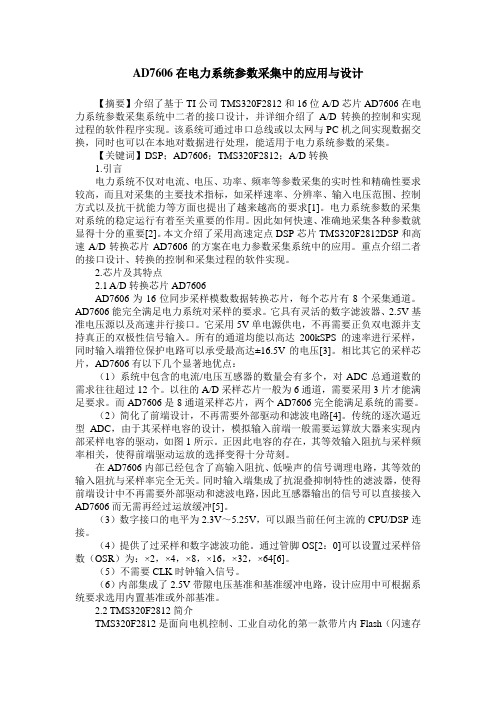

图 4. 底层去耦,显示了四个 AVCC 引脚和 VDRIVE 引脚的去耦电容 放大

16 通道系统的通道间匹配 在高通道数系统中,良好的通道间和器件间性能匹配可以大大简化校准程序。AD7606 器件、模拟输入通 道和去耦电容的对称布局有助于多个器件之间的性能匹配。使用公共系统基准电压将能进一步增强系统的 匹配性能。图 5 显示所有输入接地时,用于测量板上 16 个通道之间性能匹配的电路配置。还有最多 7 个 码的分布直方图,各通道直方图的中心为码 0,如图 6 所示。

使用实心接地层。这些对称布局原则适用于含有两个以上 AD7606 器件的系统。AD7606 器件可以沿南北 方向放置,基准电压位于器件的中间,基准电压走线则沿南北方向布设,类似于图 2。 良好的去耦也很重要,以便降低 AD7606 的电源阻抗,及其电源尖峰幅度。去耦电容应靠近(理想情况是 紧靠)这些引脚及其对应接地引脚放置。 REFIN/REFOUT 引脚和 REFCAPA、REFCAPB 引脚的去耦电容是攸关性能的重要电容,应尽可能靠近相 应的 AD7606 引脚。可能的话,应将这些电容放在电路板上与 AD7606 器件相同的一侧。图 3 显示 AD7606 电路板顶层的建议去耦配置。所示的四个陶瓷电容是 REFIN/REFOUT 引脚、REGCAP 引脚、REFCAPA 引脚和 REFCAPB 引脚的去耦电容。这些电容沿南北方向放置,以便尽可能靠近相应的引脚。

回到顶部

常见变化ቤተ መጻሕፍቲ ባይዱ

AD7606 是一款 8 通道 DAS,还可以使用 AD7606-6(6 通道 DAS)和 AD7606-4(4 通道 DAS)。AD7607 是 AD7606 的 14 位版本。其它基准电压源可以利用基准电压源选型和评估工具进行选择。

电力系统中多通道同步采样AD7606与浮点DSP通信的设计与实现

电力系统中多通道同步采样AD7606与浮点DSP通信的设计与实现电力系统中多通道同步采样AD7606与浮点DSP通信的设计与实现电力系统中多通道同步采样ADC(AD7606)与浮点DSP(ADSP-21479)通信的设计与实现内容1. 简介31.1 AD7606简介31.2 ADSP-21479简介42. AD7606和ADSP-21479配置与连接53. 时序分析64. 测试结果和结论74.1测试结果74.2结论105. DSP参考代码106. 参考文献121简介1.1AD7606简介AD7606是16位,8通道同步采样模数数据采集系统。

AD7606完全满足电力系统的要求,具有灵活的数字滤波器、2.5V基准电压源、基准电压缓冲以及高速串行和并行接口。

它采用5V单电源供电,可以处理±10V和±5V真双极性输入信号、同时所有通道均能以高达200kSPS 的吞吐率采样。

图1 AD7606的内部原理框图。

图2 AD7606的管脚图。

A Vcc 模拟电源,4.75V~5.25VVdrive 逻辑部分电源Vdd 模拟输入部分正电压Vss 模拟输入部分负电压DGND 数字地AGND 模拟地1.2ADSP-21479简介ADSP-21479是SIMD (单指令多数据)SHARC家族中的一员,它基于65nm的最新工艺,具有低成本,低功耗的的特点,是一颗集成有大容量片上SRAM和ROM的32/40位浮点DSP。

ADSP-21479是性能出色,266MHZ/1596MFLOP:266 MH z/1596FLOPS SIMD SHARC内核,支持32-bit浮点、40-bit浮点以及16/32-bit 定点数据类型支持多达5 Mb 片内SRAM支持16位宽SDR、SDRAM存储器接口数字应用接口DAI,支持多达8个的高速同步串口(SPORT)及SPI 串口2个精确时钟发生器20线数字I/O端口3个定时器、UART、I2C兼容接口ROM/JTAG安全模式供应196引脚CSP_BGA封装与100引脚LQFP封装产品,适合于工业客户的要求? 供应商业级、工业级温度与汽车级温度等级产品图3 ADSP-21479的内部原理框图。

基于AD7656的多路并行同步音频数据采集系统设计与实现

基于AD7656的多路并行同步音频数据采集系统设计与实现李石亮;杨俊安;叶春逢

【期刊名称】《现代电子技术》

【年(卷),期】2008(31)10

【摘要】针对音频BSS(盲源分离)瞬时模型的多信源多传感器问题,提出一种严格的多路并行同步数据采集的ADC方案.首先介绍ADC AD7656的性能特点,提出并实现一种并行同步多路音频数据采集的系统方案.着重介绍AD7656周围电路的设计和控制逻辑的实现,解决多路采集时序及数据分离的难题;设计完成PCI采集系统的数据接口和驱动程序;采用CPLD作控制核心,简化设计,且方便应用的扩展;最后,给出测试结果.该系统已实际应用于相关课题的研究.

【总页数】5页(P167-170,173)

【作者】李石亮;杨俊安;叶春逢

【作者单位】电子工程学院,安徽,合肥,230037;电子工程学院,安徽,合肥,230037;电子工程学院,安徽,合肥,230037

【正文语种】中文

【中图分类】TP335+.1

【相关文献】

1.基于计算机并行口的多路数据采集系统设计 [J], 刘春荣

2.一种基于FPGA+ADS130E08多路同步数据采集系统设计 [J], 张文俊;汪相坤;成印沙;王洪亮;李绪勇

3.基于计算机并行口的多路数据采集系统设计 [J], 吴文秀;赵启兰;武修明

4.基于计算机并行口的多路数据采集系统设计 [J], 林凯旋;史树新;白国庆

5.基于FPGA技术的多路并行实时数据采集系统 [J], 陈武福;胡修林;陈钧;张兵山因版权原因,仅展示原文概要,查看原文内容请购买。

基于AD7656和ADSP 21369的多路信号采集系统

基于AD7656和ADSP 21369的多路信号采集系统摘要:利用AD7656和ADI高性能数字信号处理器ADSP 21369实现了同步6通道的多路信号采集。

简要介绍了AD7656的性能特点,着重研究该系统的硬件接口方案、软件设计流程以及系统整体性能估算测试。

该系统可以广泛用于模拟信号采集领域。

关键词: ADC;AD7656;ADSP 21369;信号采集随着数字信号处理技术的飞速发展,利用数字系统处理模拟信号的技术已经被运用到测绘?控制等众多领域。

将模拟转换成数字量输出接口的A/D转换器正在向低功耗?高速度?高分辨率的方向发展。

同时,对于信号采集系统的要求也变得更高?更多样。

本文介绍利用高效灵活的数模转换芯片AD7656与高性能数字信号处理器ADSP 21369实现的多路信号采集系统。

1 系统芯片简介本采集系统采用AD7656为前端ADC,利用ADSP 21369实现数据的接收处理。

AD7656是ADI公司的一款高性能ADC,它具有6个独立ADC通道,采用iCMOS处理技术,可以实现6通道16bit逐次逼近(SAR)采样,每个通道最高可达250kS/s的吞吐速率。

具有低功耗宽输入带宽的特点,50kHz输入频率下SNR为86.5dB。

片上有2.5V基准电压源和基准缓冲器,支持并行?串行以及菊花链接口模式,支持软硬件配置方式。

ADSP 21369是ADI SHARC系列处理器的第三代产品,具有出色的处理性能。

数字音频接口(DAI)和数字外设接口(DPI)都可以通过用户自定义访问系统外设。

这些自定义访问接口,运用灵活,配置也十分简便。

本系统就是通过DAI访问数据接收的SPORT0口,通过DPI配置产生启动信号的FLAG 信号。

具体应用将在后面的章节里详细介绍。

2 系统设计整个数据采集系统由AD7656实现对模拟信号的采集转换,利用ADSP 21369接收采集到的数据,恢复波形。

下面对整个系统设计及原理进行介绍。

十六通道高精度同步数据采集系统设计

第34卷第1期2020年1月兰州文理学院学报(自然科学版)J o u r n a l o fL a n z h o uU n i v e r s i t y ofA r t s a n dS c i e n c e (N a t u r a l S c i e n c e s )V o l .34N o .1J a n .2020收稿日期:2019G09G25基金项目:安徽省教育厅自然科学研究重点项目(K J 2019A 0980);安徽省质量工程项目(2016c k j h 232);2018年度校级精品资源共享课程项目 F P G A 应用技术 ;安徽省教育厅自然科学研究重点项目(K J 2018A 0699)作者简介:杨会伟(1982G),男,河南南阳人,副教授,硕士,研究方向:嵌入式仪器仪表和数字信号处理.E Gm a i l:150496837@q q.c o m ㊀㊀文章编号:2095G6991(2020)01G0062G05十六通道高精度同步数据采集系统设计杨会伟,马书香,周先飞(芜湖职业技术学院信息工程学院,安徽芜湖241000)摘要:为了对探测对象进行多个探测点同步探测,实时精确反应探测对象某时刻的真实情况,提出了一种16通道高精度同步数据采集系统,系统利用可编程F P G A 作为控制单元,统一控制两片A D 7606的C O N S T A B ㊁C S N 使能以及RD 读操作,通过2个并行的任务执行将两片A D 7606的8通道数据同步采集到两个F I F O 阵列中,最后通过两个F I F O 的乒乓操作将数据交替转换成U S B 格式数据传送到P C 机,利用上位机软件进行存储和显示.实验结果表明:系统能够实现16通道数据的同步采集和显示,采样速率为200K S P S ,可采样电压量程为-10~+10V.关键词:高精度;同步;数据采集;时序控制中图分类号:T P 391㊀㊀㊀文献标志码:A0㊀引言信息化㊁现代化的快速发展使数据采集作用越来越重要,数据采集的采样率㊁采样精度㊁实时性㊁丰富性越来越高.多通道高精度同步数据采集系统可完成多个探测单元数据的同步采集,同步获得丰富的数据信息,提高数据分析的准确性,实时精确反映探测对象某时刻的真实情况,广泛应用于地质勘探㊁环境监测㊁电力控制系统等领域[1G3].当前基于不同控制器的数据采集系统方案也很多,比如嵌入式微处理器㊁嵌入式微控制器㊁虚拟仪器等,每种处理器都有各自的优缺点,都能够构建完整的数据采集系统,但对于大多数单核处理器来说,处理器在某一时刻只能处理一个任务,且受到主频的限制,在实现多通道数据采集时通常无法实现高精度同步.F P G A 在时序控制上优势明显,能够实现多任务并行执行,外部引脚资源丰富,且内部有大量的I P 核资源,可扩展性强,在实现多通道高精度同步采集时能够充分体现出优势.利用F P G A 和多片A D 7606构建一个16位精度多通道可扩展同步数据采集系统具有一定的应用价值[4G7].1㊀高精度多通道同步数据采集系统方案㊀㊀高精度多通道同步数据采集系统总体结构如图1所示.整个系统包括:F P G A 控制器作为系统主控单元,A D 7606前端信号采集转换单元㊁F T 2232_U S B 接口数据传输模块㊁上位机数据处理和存储软件组成.前端利用两片A D 7606在F P G A 的控制下实现16位精度㊁16通道模拟信号的同步A D转换,在下次数据采集之前,通过F P G A 内部的A D 7606控制程序模块分别将转换后的数据采集到内部两个16∗8F I F O 中进行数据缓存;再通过F P G A 内部的F I F O 乒乓访问控制模块程序将F I F O 数据交替采集到F T 2232_U S B 控制模块,实现F I F O 数据接口到U S B 数据接口的转换,最后通过F T 2232_U S B 接口将数据传输到上位机,通过上位机软件对采集数据进行存储和处理.2㊀高精度多通道同步数据采集系统设计2.1㊀硬件电路设计系统采用两片A D 7606与F P G A 进行连接,图1㊀高精度多通道同步数据采集系统框图系统主要引脚电路设计包括:①每片A D7606都采用正常工作方式,将它们的#S T B Y引脚连在一起,接上拉电阻到V C C;②O S2~O S0引脚用来控制A D7606内部数字一阶s i n c滤波器的过采样倍率,为了达到系统的采样速率,将O S2~ O S0设置为000,-10~+10V量程的S N R为90d B,3d B带宽22k H z,采样速率可达200k H z.③将F P G A的一个G P I O口与A D7606的R A N G E引脚相连,通过F P G A控制该引脚的高/低电平来设置每片A D7606外部采样输入模拟电压量程;将P A R#/S E R/B Y T E引脚接地输入低电平,使得每片A D7606采用平行接口;④为了实现双A D7606构成的16通道数据高精度同步采样,分别将每片A D7606的C O N V S T A和C O N V S T B连在一起,实现多通道同时采集;⑤将每片A D7606的16位平行数据输出(D B0~ D B15)分别与F P G A引脚相连,实现数据的同步输出;⑥两片A D7606的采样使能信号#C S和读数据触发信号R D/C L K由F P G A统一控制,实现两片A D7606真正的同步采样.⑦用一个外部基准电压源A D S421驱动2片A D7606器件的R E F I N/R E F O U T引脚,提供基准电压为2 5V.另外,每片A D7606的R E F I N/R E F O U T引脚连接100n F陶瓷去耦电容[8G9].如图2所示.2.2㊀系统数字逻辑控制时序设计F PG A作为高精度多通道同步数据采集系统的控制核心,主要实现的功能包括:A D7606驱动控制模块㊁双F I F O数据缓存㊁F T2232_U S B转换控制模块.2.2.1㊀C O N V S T A B转换时序㊀首先上电后提供上升沿复位信号R E S E T进行复位,初始化设图2㊀硬件连接图置A D7606的工作模式:设置O S0~O S2=3ᶄb000,R A N G E=1,关闭过采样,设置每片A D7606最高采样频率支持200K,-10~+10V 量程;设置2片A D7606的P A R#/S E R/B Y T E (P I N6)㊁D B15(P I N33)为0,选择16位并行接口模式.为了实现2片A D7606所有16通道同步采样,将2片A D7606的C O N V S T A和C O N V S T B 连在一起,统一进行控制,施加一个转换开始信号;数据的读取包括转换之后读取和转换期间读取两种,为了实现更快的吞吐率,两片A D7606都采用转换期间读取数据.A D7606所有通道同步采样控制时序如图3所示.其中,t1为C O N V S T A B高电平到B U S Y高电平的时间间隔,最大值为40n s;t2为C O N VGS T A B的低电平脉冲,最短时间为25n s;t3为C O N V S T A B的高电平脉冲,最短为25n s;t C Y C L E 为吞吐率的倒数,并行模式转换期间读取时间; t C O N V为转换时间,介于3.45μs与4.15μs之间,典型应用值为4μs;t4为复位信号R S T低电平到C O N V S T A B高电平之间的最短延迟时间,最小36第1期杨会伟等:十六通道高精度同步数据采集系统设计图3㊀C O N V S T A B转换时序图值为25n s;t5是C S N下降沿与B U S Y下降沿之间的时间设置,没有特殊要求;t R E S E T为复位信号高电平脉冲宽度,最短复位时间为50n s[10].根据时序图,利用V e r i l o g语言设计A D7606的C O N V S T A B转换时序,首先在系统上电后利用外部的复位按钮产生复位信号,该复位信号输出后经过处理产生一个约50n s的高电平脉冲复位信号,发送至A D7606复位引脚进行复位操作.在复位信号的高电平有效时,初始化产生C O NGS T A B的分频计数器为0,A D7606采用200K S P S的采样频率,C O N S T A B的周期为1s/200K=5μs,已知外部时钟为50MH z,分频计数器大小为50∗106/1/0.000005=500.复位结束后,利用复位信号的下降沿作为起点,以50MH z时钟上升沿为触发条件,开始对C O N S T A B分频计数器进行计数,计数范围为0~500,参照时序图和数据手册,设定计数器前10个计数状态下C O N S T A B为低电平,其余11~500计数状态下C O N S T A B为高电平.在C O N S T A B由低电平转换到高电平后,A D7606产生输出高电平B U S Y 信号并开始转换,大约4μs后转换结束,B U S Y 信号由高电平跳变为低电平,B U S Y信号的下降沿表明当前转换数据已经锁存到输出数据寄存器中,B U S Y低电平稳定后就可以读取本次转换数据.为了便于实现并保证当前读取数据为最新转换数据,两片A D7606都采用转换后读取数据的方式,在B U S Y信号高电平期间,产生一定时间的低电平采样使能信号C S N,开始读取上次数据,在B U S Y下降沿到来前,任何在B U S Y高电平状态数据的读取必须都要完成,所以在设计时, C S N上升沿比B U S Y信号上升沿提前一段时间[10].2.2.2㊀并行数据读取控制㊀在设计好C O N VGS T A B转换时序和采样使能信号C S N后,启动多通道并行数据读取,将上次转换数据读取至相应的F I F O中.两片A D7606并行多通道数据读取时序如图4所示.其中,t6为采样使能信号C S N有效到读使图4㊀并行数据读取时序能信号R D的有效时间间隔,没有特殊要求,可根据C S N下降延为基准产生R D有效低电平;t7为读使能信号R D读取一个通道数据周期中低电平脉冲宽度,最低为21n s;t8为读使能信号R D读取一个通道数据周期中高电平脉冲宽度,最短时间为15n s;t9为R D下降沿后的数据访问时间,最大值为21n s;t10为C S N到R D保持时间,没有特殊要求,保证在一个C S N的低电平时间内有8个周期的R D信号,以读取V1~V88个通道的数据,两片A D7606共用同一个C S N和R D,以实46㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀兰州文理学院学报(自然科学版)㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀第34卷现16通道同步采样.根据时序图,利用V e r i l o g语言设计两片A D7606的16通道数据的读取功能.首先,建立16个深度为128㊁宽度为16的F I F O数组阵列,分别用于存放16通道采样数据,为每个F I F O指定读写地址.在复位信号高电平有效时,清空各个F I F O,F I F O满状态标志位设置为空状态,建立两个并行的过程块,分别用于完成两片A D7606各个通道的数据采集.针对每个数据采集过程,利用状态机控制实现8个通道数据采样到F I F O数组中,执行流程为:(1)进入空闲状态,在空闲状态下等待B U S Y信号高电平到来,当获得B U S Y信号为高电平时,进入A D转换,B U S Y等信号一直保持高电平.(2)当检测到B U S Y信号恢复低电平后,说明A D转换完成,数据已经锁存到输出寄存器中,开始进入A D76068个通道数据顺序读取状态,在B U S Y信号下降沿的触发下设置C S N 为低电平,该低电平一直保持到8个通道数据读取结束为止.在C S N低电平期间,参照图4中t7和t8,设计产生8个R D周期性脉冲信号.A D7606的8个R D脉冲信号从通道1到通道8顺序读取数据,并将数据依次存入到相应的F I F O数组中,在读取期间同时检测B U S Y状态,在B U S Y下一个上升沿到来之前完成8通道数据读取工作.在第8个通道数据读完后,设置F I F O满状态标志为满状态,以提示可以将F I F O 数据取出传送至其他模块,另一片A D7606的数据读取是按照同样设计同步进行的,最终完成16通道数据的同步采样.将16个通道数据全部采集到F I F O数组后,通过判断F I F O标志为满状态,开始将16个F I F O数组数据依次传送至F T2232_U S B模块,通过U S B接口传送至上位机进行显示和保存.3㊀上位机数据采集与测试利用F T2232_U S B模块的F I F O转U S B功能,实现将16个通道16位宽度F I F O数据依次转换成U S B串口数据并传输至上位机,U S B串口数据通信格式为:帧头+多通道数据;2个字节为1个数据,低字节在前,16通道数据的帧头定义为0x5a10.F T2232H为F T D I公司的2通道高速U S B 2.0芯片,F T D I提供了F T2232H开发所需的所有驱动和多种语言上位机示例,无需编写U S B底层驱动,F T官方已提供了D L L,用户只需调用A P I即可.安装F T2232H驱动程序,在V B.n e t 开发环境中利用V B语言调用F T提供的D L L,进行U S B接口数据采集和显示,采集结果如图5所示.测试结果表明:当动态改变外部通道采样电压,16个通道采样数据会立刻改变,该系统能够完成16通道数据的实时同步采集.图5㊀数据采集界面4㊀结束语本文提出了一种16通道高精度同步数据采集系统,系统分辨率16位㊁16通道,采样率可达200K S P S;可采样电压量程为-10~+10V.该系统利用可编程器件F P G A作为主控制器,便于56第1期杨会伟等:十六通道高精度同步数据采集系统设计系统功能灵活升级和优化,采用多任务并行执行和V e r i l o g并行硬件语言编程,可提高多通道同步采样精度,利用两个F I F O阵列的乒乓操作便于实现16通道数据转换为U S B上位机数据采集,提高系统采集效率.参考文献:[1]阳继军.基于G P S授时的地震采集系统同步系统设计[J].石油仪器,2009,23(1):82G85.[2]邱桂芬.高速多通道数据采集系统的时钟同步设计[J].舰船电子对抗,2013,36(1):93G96.[3]刘小林,范育兵,罗春晖.基于F P G A的多通道数据采集系统设计[J].北京:电子技术应用,2009(7):42G44.[4]徐加彦.基于F P G A的高速多通道A D采样系统的设计与实现[J].自动化与仪表,2014(9):49G52.[5]纪大伟,徐抒岩,胡君.基于F P G A的多通道高速数据采集系统[J].仪表技术与传感器,2011,12:31G32.[6]甘建伟,秦付军,王鹏.基于F P G A的高速多通道数据采集系统设计[J].电子技术应用,2013,39(4):87G88.[7]杨炜新.基于F P G A的多通道数据采集系统设计[D].太原:中北大学,2014.[8]秦爽.多通道同步数据采集系统设计与实现[D].成都:电子科技大学,2009.[9]刘洋.基于N i o s I I的多路基阵信号数据采集与传输技术研究[D].哈尔滨:哈尔滨工程大学,2013.[10]刘曲波.基于I E C61850的电子式互感器数字接口的设计[D].武汉:华中科技大学,2007.[责任编辑:李岚]D e s i g no f16GC h a n n e lH i g hGp r e c i s i o nS y n c h r o n i z e dD a t aA c q u i s i t i o nS y s t e mY A N G H u iGw e i,MAS h uGx i a n g,Z H O U X i a nGf e i(S c h o o l o f I n f o r m a t i o nE n g i n e e r i n g,W u h u I n s t i t u t e o fT e c h n o l o g y,W u h u241002,A n h u i,C h i n a)A b s t r a c t:I n o r d e r t o s y n c h r o n o u s l y d e t e c tm u l t i p l e d e t e c t i o n p o i n t s a n d a c c u r a t e l y r e f l e c t t h e r e a l s i t uGa t i o no f t h e d e t e c t i o n o b j e c t a t a c e r t a i n t i m e,a16Gc h a n n e l h i g hGp r e c i s i o n s y n c h r o n o u s d a t a a c q u i s i t i o n s y s t e mi s p r o p o s e d.T h e s y s t e mf i r s t l y a p p l i e s p r o g r a mm a b l eF P G Aa s t h e c o n t r o l u n i t t o p r o v i d e a u n i f i e dC O N S T A B,C S N e n a b l e m e n ta n d RGr e a d i n g c o n t r o l s e q u e n c ef o rt h et w o p i e c e so fF P G A, t h e n t w o t a s k s a r e e x e c u t e d i n p a r a l l e l t o c o m p l e t e t h e16Gp a s s c o m p o s e d o f t w o p i e c e s o fA D7606a n d c h a n n e l d a t aa r ec o l l e c t e ds y n c h r o n o u s l y i n t ot w oc o r r e s p o n d i n g F I F Oa r r a y s,f i n a l l y,t h ed a t aa r e c o n v e r t e d i n t oU S Bd a t ab y t a b l e t e n n i s o p e r a t i o no f F I F Oa n d t r a n s m i t t e d t oP C f o r s t o r a g e a n dd i sGp l a y.T h e e x p e r i m e n t a l r e s u l t s s h o wt h a t t h e s y s t e mc a n a c h i e v e16Gc h a n n e l d a t a s y n c h r o n o u s a c q u i s iGt i o na n dd i s p l a y,t h es a m p l i n g r a t e i s200K S M P S,a n dt h er a n g eo f s a m p l i n g v o l t a g e i s-10~+10V.K e y w o r d s:h i g hGp r e c i s i o n;s y n c h r o n i z a t i o n;d a t a a c q u i s i t i o n;t i m i n g c o n t r o l66㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀兰州文理学院学报(自然科学版)㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀㊀第34卷。

基于STM32及AD7606的16通道同步数据采集系统设计

基于STM32及AD7606的16通道同步数据采集系统设计摘要: 介绍了基于STM32及AD7606的同步数据采集系统的软硬件设计。

主控芯片采用基于ARM Cortex-M4内核的STM32F407IGT6,实现对AD 采集数据的实时计算并通过以太网络进行数据传输。

A7606为16位、8通道同步采样模数数据采集系统[],利用两片AD7606,可以实现对16路通道的实时同步采样。

经过测试,该系统可以实现较高精度的实时数据采集。

0 引言[此处找书介绍STM32],该芯片主频可达168MHz,具有丰富的片内外设,并且与前代相比增加了浮点运算单元(Floating Point Unit,FPU),使其可以满足数据采集系统中的 [介绍AD7606]1 系统总体方案设计整个系统由传感器模块、信号调理模块、数据采集模块、处理器STM32、及通信模块及上位机系统组成。

系统整体结构框图如图1所示。

本系统是为液态金属电池性能测试设计,需要测量电池的充放电电压、电流以及交流加热系统的电压、电流,并以此计算出整个液态金属电池储能系统的效率。

因此两片AD7606的16个通道分为两组,每组8个通道,这两组分别测量4路直流、交流的电压和电流信号。

AD7606通过并行接口与STM32连接,STM32读取AD 采样数据后进行计算,并将数据通过网络芯片DP83848通过UDP 协议发送给上位机。

上位机负责显示各通道采集信息、绘制波形以及保存数据等。

STM32F407IGT6霍尔直流传感器上位机软件DP83848直流信号交流信号交流互感器调理电路调理电路AD7606AD7606图1 系统整体结构框图2 系统硬件设计2.1 模拟信号采集电路设计 模拟信号的采集包含直流电压、电流,交流电压、电流四部分。

直流信号的采集分别使用霍尔电压传感器HNV025A 和霍尔电流传感器HNC100B ,两种传感器的电路原理图类似,仅以霍尔电压传感器电路原理图为例说明,如图2-1所示。

基于DAS的可扩展多通道同步采样数据采集系统的布局考虑

基于DAS的可扩展多通道同步采样数据采集系统的布局考虑Claire Croke

【期刊名称】《今日电子》

【年(卷),期】2010(000)010

【摘要】@@ 电路描述rnAD7606是一款集成式8通道数据采集系统,片内集成输入放大器、过压保护电路、二阶模拟抗混叠滤波器、模拟多路复用器、16位200kS/s SAR ADC和一个数字滤波器.如图1所示电路包括两个AD7606器件,可以配置为使用2.5V内部基准电压源或2.5V外部基准电压源ADR421.

【总页数】3页(P43-45)

【作者】Claire Croke

【作者单位】ADI公司

【正文语种】中文

【相关文献】

1.基于DSP的多通道高速可扩展数据采集系统 [J], 郑辉;陈俊峰;姚建斌

2.基于FPGA的可扩展多通道数据采集系统设计 [J], 姚殿奎;李希垒

3.多通道同步采样数据采集系统研究 [J], 山昆;刘建业;赵伟;祝燕华

4.基于MAX125的多通道同步采样数据采集系统 [J], 涂水林

5.多通道同步采样数据采集系统的设计 [J], 史延龄;邹来智;李洪津

因版权原因,仅展示原文概要,查看原文内容请购买。

ARM与AD7656-1的多通道数据采集系统设计

ARM与AD7656-1的多通道数据采集系统设计

徐园;靳根;王希涛;陈法国;刘倍

【期刊名称】《核电子学与探测技术》

【年(卷),期】2012(032)008

【摘要】针对γ辐射监测系统,应用ARM微处理器控制多通道AD芯片,实现对4路输入信号的高速数据采集.详细介绍了LPC2300系列ARM与高速模数转换芯片AD7656 -1基于SPI串行通信的应用方案,给出了二者之间的硬件连接图以及

μC/OS -Ⅱ实时操作系统下的软件实现方法,为ARM嵌入式系统在高速数据采集方面的应用提供了一个解决方案.

【总页数】4页(P914-917)

【作者】徐园;靳根;王希涛;陈法国;刘倍

【作者单位】中国辐射防护研究院,山西太原 030006;中国辐射防护研究院,山西太原 030006;中国辐射防护研究院,山西太原 030006;中国辐射防护研究院,山西太原030006;中国辐射防护研究院,山西太原 030006

【正文语种】中文

【中图分类】TP274+2

【相关文献】

1.基于ARM+CPLD的多通道数据采集系统研究 [J], 钟知原;吴学杰;隋皓;薛闯

2.基于ARM的多通道数据采集系统 [J], 杨博;张加宏;李敏;顾芳

3.AD7656-1菊花链的多通道数据采集接口设计 [J], 温小旭;林知明;辛柒荣

4.基于ARM的分布式多通道数据采集仪 [J], 陆建荣;单梁;汪静;李军;孙翌晨

5.基于ARM微处理器的多通道数据采集系统 [J], 李振宇;迟岩;蔡惠茵

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电路笔记CN-0148连接/参考器件8通道DAS ,内置16位、双极性、同步采样ADCAD7606利用ADI 公司产品进行电路设计Rev.0“Circuits from the Lab” from Analog Devices have been designed and built by Analog Devices engineers. Standard engineering practices have been employed in the design and construction of each circuit, and their function and performance have been tested and verified in a lab environment at room temperature. However, you are solely responsible for testing the circuit and determining its suitability and applicability for your use and application. Accordingly, in no event shall Analog Devices be liable for direct, indirect, special, incidental, consequential or One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781.329.4700 Fax: 781.461.3113 ©2010 Analog Devices, Inc. All rights reserved. AD7606-66通道DAS ,内置16位、双极性、同步采样ADC放心运用这些配套产品迅速完成设计。

欲获得更多信息和/或技术支持,请拨打4006-100-006或访问AD7606-44通道DAS ,内置16位、双极性、同步采样ADC/zh/circuits 。

ADR421精密、低噪声XFET ®基准电压源基于16位8通道DAS AD7606的可扩展多通道同步采样数据采集系统(DAS)的布局考虑电路描述电路功能与优势AD7606是一款集成式8通道数据采集系统,片内集成输入放大器、过压保护电路、二阶模拟抗混叠滤波器、模拟多路复用器、16位200 kSPS SAR ADC 和一个数字滤波器。

在电力线路测量和保护系统中,需要对多相输配电网络的大量电流和电压通道进行同步采样。

这些应用中,通道数量从6个到64个以上不等。

AD7606 8通道数据采集系统(DAS)集成16位双极性同步采样SAR ADC 和片内过压保护功能,可大大简化信号调理电路,并减少器件数量、电路板面积和测量保护板的成本。

高集成度使得每个AD7606只需9个低值陶瓷去耦电容就能工作。

图1所示电路包括两个AD7606器件,可以配置为使用2.5 V 内部基准电压源或2.5 V 外部基准电压源ADR421。

如果REF SELECT 引脚接逻辑高电平,则选择内部基准电压源。

如果REF SELECT 引脚接逻辑低电平,则选择外部基准电压源。

在测量和保护系统中,为了保持多相电力线网络的电流和电压通道之间的相位信息,必须具备同步采样能力。

AD7606具有宽动态范围,是捕获欠压/欠流和过压/过流状况的理想器件。

输入电压范围可以通过引脚编程设置为±5 V 或±10 V 。

此电路笔记详细介绍针对采用多个AD7606器件应用而推荐的印刷电路板(PCB)布局。

该布局在通道间匹配和器件间匹配方面进行了优化,有助于简化高通道数系统的校准程序。

当通道间匹配非常重要时,此电路可以使用2.5 V 内部基准电压源AD7606;而对于要求出色绝对精度的高通道数应用,此电路可以使用外部精密基准电压源ADR421,它具有高精度(B 级:最大值±1 mV )、低漂移(B 级:最大值3 ppm/°C )、低噪声(典型值1.75 μV p-p ,0.1 Hz 至10 Hz )等特性。

低噪声及出色的稳定性和精度特性使得ADR421非常适合高精度转换应用。

这两个器件相结合,能够实现业界前所未有的集成度、通道密度和精度。

电源要求如下:AV CC = 5 V ,V DRIVE = 2.3 V 至5 V (取决于外部逻辑接口要求)。

本电路笔记描述一个评估板的布局和性能,其中内置两个AD7606,构成一个16通道数据采集系统。

欲浏览完整的16通道DAS PC 板文档,请访问:/CN0148_PCB_Documentation 。

为实现良好的通道间匹配和器件间匹配,模拟输入通道和器件去耦的对称布局非常重要。

所示数据支持利用图1所示16通道ADC 实现的匹配性能。

16通道DAS 的双路AD7606板布局在内置多个AD7606器件的系统中,为确保器件之间的性能匹配良好,这些器件必须采用对称布局。

图2显示采用两个AD7606器件的布局。

CN-0148 电路笔记图1.采用两个AD7606 8通道DAS的16通道、16位数据采集系统(原理示意图,未显示所有连接。

对于通道间和器件间匹配测试,器件之间的具体连接参见正文)电路笔记CN-0148AV 电压平面沿两个器件的右侧布设,V REFIN/REFOUT 引脚和REFCAPA 、REFCAPB 引脚的去耦电容是攸关性能的重要电容,应尽可能靠近相应的AD7606引脚。

可能的话,应将这些电容放在电路板上与AD7606器件相同的一侧。

CC DRIVE 电源走线沿两个AD7606器件的左侧布设。

基准电压芯片ADR421位于两个AD7606器件之间,基准电压走线向上布设到U2的引脚42,向下布设到U1的引脚42。

使用实心接地层。

这些对称布局原则适用于含有两个以上AD7606器件的系统。

AD7606器件可以沿南北方向放置,基准电压位于器件的中间,基准电压走线则沿南北方向布设,类似于图3显示AD7606电路板顶层的建议去耦配置。

所示的四个陶瓷电容是REFIN/REFOUT 引脚、REGCAP 引脚、REFCAPA 引脚和REFCAPB 引脚的去耦电容。

这些电容沿南北方向放置,以便尽可能靠近相应的引脚。

图2。

良好的去耦也很重要,以便降低AD7606的电源阻抗,及其电源尖峰幅度。

去耦电容应靠近(理想情况是紧靠)这些引脚及其对应接地引脚放置。

图3.顶层去耦,显示了两个REFCAP A 引脚、REFIN/REFOUT 引脚和REFCAP A/B 引脚的去耦电容图4.底层去耦,显示了四个AVCC 引脚和VDRIVE 引脚的去耦电容图2.采用两个AD7606的16通道DAS 的PCB 布局CN-0148电路笔记AD7606内部基准电压源用作系统基准电压源图4显示底层去耦配置,它用于四个AVCC 引脚和VDRIVE 引脚的去耦。

使用多个过孔将引脚与其相应的去耦电容相连。

AD7606器件周围去耦电容的对称布局有利于器件间的性能匹配。

多个过孔用来将电容焊盘和引脚焊盘接地及接到电压平面和基准电压走线。

AD7606内置一个2.5 V 基准电压源,经过内部放大,它可以为AD7606 ADC 提供约4.5 V 的缓冲基准电压。

在通道间和器件间匹配性能至关重要的高通道数应用中,可以用一个AD7606的内部基准电压源为另一个AD7606器件提供基准电压。

在此配置中,U1配置为在内部基准电压下工作,如图7所示。

16通道系统的通道间匹配AD7606 U2器件可配置为在外部基准电压源模式下工作。

U1 REFIN/RFOUT 引脚提供的2.5 V 基准电压路由至U2的REFIN/REFOUT 引脚。

一个10 μF 去耦电容位于AD7606器件的REFIN/REFOUT 引脚。

在AD7606 U1和U2上,REFCAPA 和REFCAPB 引脚短接在一起,并通过一个10 μF 陶瓷电容去耦至GND 。

在高通道数系统中,良好的通道间和器件间性能匹配可以大大简化校准程序。

AD7606器件、模拟输入通道和去耦电容的对称布局有助于多个器件之间的性能匹配。

使用公共系统基准电压将能进一步增强系统的匹配性能。

图5显示所有输入接地时,用于测量板上16个通道之间性能匹配的电路配置。

还有最多7个码的分布直方图,各通道直方图的中心为码0,如图6所示。

两个AD7606器件均以200 kSPS 的采样速率工作,一个7.5 V 直流信号施加于U1的V1和V2,如图7所示。

码的直方图如图8所示。

在同一器件的通道之间,平均输出码相差1.2个码。

板上的所有16个通道以200 kSPS 速率进行转换。

图5.用于测试16通道系统通道间匹配的电路示意图,该系统采用两个AD7606和外部基准电压源ADR421,所有输入接地图7.用于测试一个AD7606通道间匹配的电路示意图,使用U1内部基准电压源图6.图5所示电路的直方图,显示了使用外部基准电压源ADR421的16通道系统的通道间匹配性能图8.图7所示电路的直方图电路笔记CN-01487.5 V 信号施加于U1的V1和U2的V1,板上的所有16个通道以200 kSPS 速率工作,如实际理想码的值会因温度而不同,具体取决于系统基准电压源的温度系数特性。

在绝对精度非常重要的应用中,或者在希望避免通过复杂的温度校准程序实现绝对精度和通道匹配的应用中,应当使用ADR421等小容差、低漂移2.5 V 基准电压源作为AD7606器件的系统基准电压源。

图9的配置电路示意图所示。

码的直方图如图10所示。

在不同器件的V1通道之间,平均输出码相差1.4个码。

图117.5 V 直流电压施加于U1的输入(V1和V2),如的电路所示,并使用外部基准电压源。

U1的两个通道的码直方图如图12所示。

两个通道的码直方图平均值相差0.9 LSB 。

图9.用于测试两个AD7606之间器件间匹配的电路示意图,U1内部基准电压源用作系统基准电压源图11.用于测试一个AD7607通道间匹配的电路示意图,使用外部基准电压源图10.图9所示电路的直方图将一个AD7606的内部基准电压源用作系统基准电压源时,以上直方图显示,一个AD7606器件的通道之间以及多个器件的通道之间都具有非常好的匹配性能。

绝对精度图12.图11所示电路的直方图除了通道间匹配和器件间匹配外,如果ADC 转换结果的绝对精度也非常重要,则应使用外部小容差、低漂移基准电压源作为系统基准电压源。

在该电路中,ADR421 2.5 V 基准电压源用作系统基准电压源。