基于DE1-SoC的模块化数字系统实验箱的研制

数字电视实验装置研制与学生科研能力培养

数字电视实验装置研制与学生科研能力培养介绍自行研制的数字电视实验装置,并结合电子与通信专业课程,建立一套旨在培养学生科研和创新能力的体系。

分析学生参与科研活动和提高科研能力的关系。

标签:数字电视传输流(TS)科研能力创新能力教育部在《关于进一步加强高等学校本科教学工作的若干意见》中指出,“积极推动研究性教学,提高大学生的创新能力。

”以培养学生全新的创造性思维,结合电子与通信本科专业的培养目标,笔者结合数字电视实验室的实验教学经验和科研资源,研制了基于NDK的数字电视传输流(TS)网络采集系统,并挑选学生参与整个系统的研制工作。

(一)实验装置介绍本实验装置包括硬件及软件两部分。

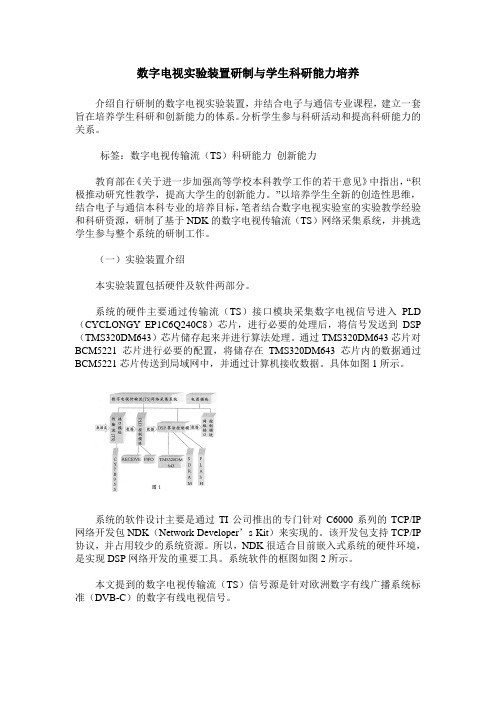

系统的硬件主要通过传输流(TS)接口模块采集数字电视信号进入PLD (CYCLONGY EP1C6Q240C8)芯片,进行必要的处理后,将信号发送到DSP (TMS320DM643)芯片储存起来并进行算法处理。

通过TMS320DM643芯片对BCM5221芯片进行必要的配置,将储存在TMS320DM643芯片内的数据通过BCM5221芯片传送到局域网中,并通过计算机接收数据。

具体如图1所示。

系统的软件设计主要是通过TI公司推出的专门针对C6000系列的TCP/IP 网络开发包NDK(Network Developer’s Kit)来实现的。

该开发包支持TCP/IP 协议,并占用较少的系统资源。

所以,NDK很适合目前嵌入式系统的硬件环境,是实现DSP网络开发的重要工具。

系统软件的框图如图2所示。

本文提到的数字电视传输流(TS)信号源是针对欧洲数字有线广播系统标准(DVB-C)的数字有线电视信号。

(二)围绕专业课程建立科研课题基于NDK的数字电视传输流(TS)网络采集系统的科研课题是针对电子与通信专业课程培养体系确定的。

为了培养学生的实际应用能力和创新能力,达到“学习数字电视专业课程”的实验教学目的,我们在装置的研制开发过程中涉及到了电子与通信专业的大部分课程知识,其中,传输流接口模块主要由教师完成。

基于 SoC的现代电子系统设计课程创新研究

( De p a r t me n t o f Au t o ma t i o n ,Ts i n g h u a Un i v e r s i t y, Be i j i n g 1 0 0 0 8 4,Ch i n a )

关 键 词 :S o C;电子 系 统 设 计 ; 课 程 中 图分 类号 : G 6 4 2 . 0 文 献 标 志 码 :A 文 章 编 号 :1 0 0 2 — 4 9 5 6 ( 2 0 1 4 ) 1 — 0 1 6 6 — 0 3

Re s e a r c h o n i n n o v a t i o n o f Mo d e r n E l e c t r o n i c S y s t e m D e s i g n c o u r s e b a s e d o n S o C

Vo 1 . 3 1 No . 1 J a l 1 . 2 0 1 4

基于 S o C的现 代 电子系统设计课程创新研究

叶 朝 辉 ,周 永 明 ,林 博 ,张 燕

( 清 华 大学 自动 化 系 ,北 京 1 0 0 0 8 4 )

摘

要: 随着 S o C( S y s t e m o n C h i p ) 应用越来越广泛 , 现 代 电子 系 统 大 多 以 S o C 为基 础 进 行 设 计 。 首 先 调 研

目前 的 S o C电子系统设计课程 , 在 此 基础 上 介 绍 了 内 容 上 和 教 学 模 式 上 具 有 一 定 创 新 的 现 代 电 子 系 统 设 计 相关课程 , 并 详 细 介 绍 了课 程 的教 学 指 导思 想 、 教 学 内容 和 教 学 模 式 及 课 程 开 设 的 效 果 。

开放型模块式结构单片机实验箱设计

2 0 2 15 系统 的 + .v电源采用 半导 体集成 稳压芯 片 L 1— - X A 2两个 引脚外接 1 M与 1. 9 M双路 晶振 ,采用 内部 时 33 M1 33 17 T L 1M 设计 ,M1 1 L 17为一个 低压差 电压 调节器系列 , 有可调 电压版本 钟 方 式 ,通 过 选 择 跳 线 进 行 选 择 ,2 晶 振 为 常 用 晶 振 , 1 52 0 和 5个 固定 电压版本 , 并且具有电流限制和热保 护功能 , 出电 1 . 9 M晶振能够 为串 口通信提供准确 的时钟信号。由于不外 输 O E /p 内外 程序存储 器选择控制端 ) 为高电平 , 流 可达 80 A, 0 m 线性 调整率 为 02 负载调 整率为 0 %, 以 扩 R M,A V p引脚 ( . %, . 足 4

开放型模 块 式 结构 单 片机 实验箱 设计

魏 文 涛

( 州学院机 电工程 系 德

摘

一

德州

2 32 ) 5 03

要 当前单片机实验教学设 备存在实验 内容简单 、 序固定 的弊端 , 程 学生 自主操作 的空间很小 , 与工程实际相差甚远 。针对这 问题提出改进设计方案 , 从工程开发 的角度设计各功能模块 , 于开放式设计理念 , 功能模块 与母板采 用可拆 卸式的连接 , 基 各 方

实践性强的特点 , 在教学 的过程 中需 要理论与实验相结合 , 为保 功能模块供电 ,功能模块通过铜柱 与母板进行 可拆卸式的连接 。 证实验教学的效果 , 实验 的内容及方法要从实 际应用 出发 , 既要 模块 与处理器之间及模块与模块之 问采用 杜邦 线连接 ,从而方 完成理论教学的验证作用 ,又要培养学生的实际应用能力和工 便组成各实验的硬 件电路 。实验箱模块分布图见图 1 所示 。 程创新意识 。 1 在 目前的单片机教学 中 ,各高校大都 以 5 单 片机为基础 , 1 采用一种 “ 理论 +验证 性实验” 的教学模式 , 实验箱一般 采用封 闭式设计 , 学生 只需调入程序就可以完成验证性 的实验 , 与工程 实际相差较大 , 不能满足学生的学习兴趣 , 不利于学生实践技能 的培养 以及工程应用能力的训 练。针对 当前单片机实验教学存 在 的缺陷 , 本设计从实 际工程开发的角度出发 , 采用模块式结构 对 5 单 片机实验箱进行 了优化设计 , 1 方便学生进行实训式 的单 片机学习 , 使学生掌握工程实际 中单片机的开发流程 , 并可 以引

单片机综合实验箱的研制

本 实验箱 提供2 实验平 台:单片机实验平 台和 个 E A实验平 台。通过单片机实验平 台完成单片机原理 D

与应 用 课程 中的基 础 性 实验 。通 过 E A实验 平 台, D 利用

性、综合性实验, 而传统的单 片机实验箱 功能单一, 无 法给学生提供一个充分开放 自由的实验环境, 不能满足 实验教学的需要。 开发单片机 综合实验箱, 基于3 个基本要求 :第一, 要满足实验教学大纲所开实验 的要求;第二, 具有多功 能, 可完成设计性、综合设计性实验 ;第三, 便携式, 为

Zh n io g , a a d n a g Zhh n Zh i Xi o o g

1 Xu h u i si t f r h tcu a c n lg , z o , 21 1 , i a . z o t u eo a c i t r l e h o o y Xu h u 2 1 6 Ch n n t e t 2 Xu a o lg , i au i e st f n i g& t c o o y Xu h u 2 1 0 , i a . h i l e Ch n n v r i o mi n c e y e h lg , z o n 2 0 8 Ch n

,

Absr c:De c b sd v lp e u p eofne mod l i ge c i c o o u e x e me td vc , e c b s h a i d s n d sg ta t s r e e eo m ntp r os w i essn l hp mi c mp tre p r n e ie d sr e eb sc e i , e in r i i t g pln, tu t a e tr s I to u e ef ncin o ba i o ue t ed vc . a sr curlfau e , n r d c dt u to f scm d lsOf h e ie h Ke r : i l hp mir o p tr o p e e svee pe me tl x EDA ; a e t ywo ds sng ec i coc m u e;c m r h n i x r i na ; bo p tn

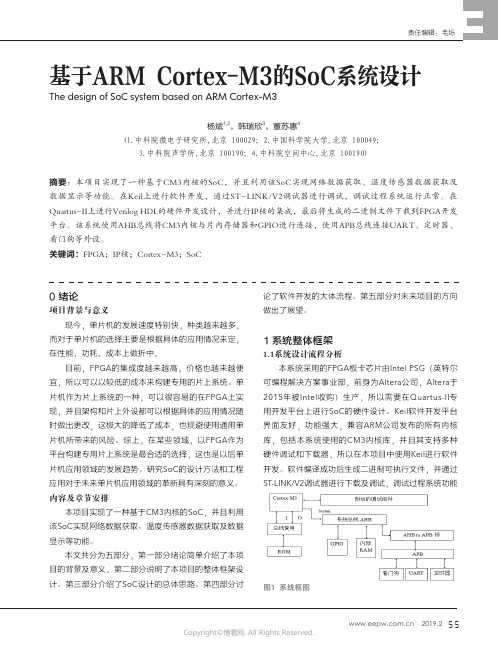

基于ARM_Cortex-M3的SoC系统设计_

核发出中断请求信号,包含最多240个中断请求,以及1个不可屏蔽中断。

NVIC是与CPU紧密耦合的,它还包含了若干个系统控制寄存器。

2.2.3 总线系统总线系统用于将Cortex-M3内部的各个功能部件连接在一起。

总线系统包括:①内部总线系统;②处理器核内部的数据通道;③AHB Lite接口单元。

2.2.4 调试子系统作为Cortex-M3处理器重要的一部分,调试子系统提供下面的功能。

①管理调试控制、程序断点、以及数据监控点。

②当产生调试事件时,它将处理器核设置为停止状态。

此时,可以在该点分析处理器的状态,如寄存器值和标志。

2.3 异常处理与中断向量表设计Cortex-M3在内核水平上搭载了一个异常响应系统,支持为数众多的系统异常和外部中断。

向量中断控制器(NVIC)以存储器映射的方式来访问,除了包含控制寄存器和中断处理的控制逻辑之外,NVIC还包含了MPU的控制寄存器、SysTick定时器以及调试控制。

2.4 地址译码器和多路复用器设计本系统基于AHB-Lite所构建的Cortex-M3 SoC系统设计包含了地址译码器和多路复用器。

在系统中,来自不同从设备的响应信号,包括:HRDATA、HREADY和HRESP连接到多路复用器的输入,根据地址译码器所生成的选择信号,多路复用器将选择的从设备响应信号送给主设备。

其中HRDATA[31:0]是来自多路复用器到主设备的读数据,由多路复用器指向主设备;HREADY是来自多路复用器到主设备的准备信号,由多路复用器指向主设备和从设备,当该位为高时,该信号表示到主设备和先前完成传输的所用从设备。

2.5 APB子系统该APB子系统的顶层是AHB-Lite总线接口,可以与内核的AHB总线进行连接。

子系统内部包括的外设有定时器、UART、双输入定时器、看门狗电路、AHB到APB的桥接器、异步中断信号等。

表2为APB系统IRQ分配表。

表2 APB系统IRQ分配IRQ Device0UART 0 receive interrupt1UART 0 transmit interrupt2UART 1 receive interrupt3UART 1 transmit interrupt4UART2 receive interrupt5UART 2 transmit interrupt8Timer 09Timer 110Dual-input timer11Not used12UART 0 overflow interrupt13UART1 overflow interrupt14UART 2 overflow interrupt15Not used in APB subway16-31Not used in APB subway a: Reserved for GPIO in AHBb: Reserved for DMA2.6 时钟和复位电路设计本系统片上SoC系统主要包含HCLK、PCLK、PCLKG等三个时钟,HCLK时钟主要用于内核的工作时钟以及驱动片内高性能总线上挂载的外设。

基于国产芯片的E1接口重构技术研究与实现

基于国产芯片的E1接口重构技术研究与实现孙伟;李鉴;杨玉发【摘要】Domestic chips are usually used in key components for access board of access router, such as FPGA and CPU, control data and business data are in distributed collaborative process, and the modular design makes the change of card interface module and the loading of different programs realize equipment static reconfiguration. The adoption of two pieces of FPGA could make up the inadequacy of domestic chip performance, and makes easy the isolation of different access board data processing modules. The overall design of access board, the problems to be solved, the hardware and software strategies are described. The channels of between the CPU, FPGA and interface module are configured. Experiment indicates that this E1 board could fairly implement data receiving and dispatch process.%接入路由器中接入板的FPGA和CPU等关键元器件采用国产化芯片,控制数据和业务数据分布式协同处理,同时对板卡进行模块化设计,使得更改接口模块和加载不同程序实现设备的静态重构。

eda-sopc实验箱简介

第一章实验箱简介EDA/SOPC实验箱是集EDA和SOPC开发为一体的综合性实验箱,它不仅可以独立完成几乎所有的EDA设计,也可以完成大多数的SOPC开发。

采用Altera公司的Cyclone系列的30万门FPGA为核心,整个系统采用模块化设计,各个模块之间可以自由组合,使得该实验箱的灵活性大大提高。

同时实验箱还提供了丰富的接口模块,供人机交互,从而大大增加了实验开发者开发的乐趣,满足了普通高等院校、科研人员等的需求。

开发工程师可以使用VHDL语言、Verilog HDL语言、原理图输入等多种方式,利用Altera公司提供的Quartus II及NiosII软件进行编译,下载,并通过EDA/SOPC实验箱进行结果验证。

实验箱提供多种人机交互方式,如键盘阵列、按键、拨挡开关输入;七段码管、大屏幕图形点阵LCD显示;串口通信;VGA接口、PS2接口、USB接口、Ethernet接口等,利用Altera公司提供的一些IP资源和Nios 32位处理器,用户可以在该实验箱上完成不同的SOPC设计。

EDA/SOPC实验箱提供的资源有:●Altera公司的EP1C6Q240C8,30万门级FPGA,另外可选配更高资源的FPGA●FPGA配置芯片采用可在线变成的EPCS4,通过JTAG口和AS口即可完成设计的固化●1个数字时钟源,提供48MHz、12MHz、1MHz、100KHz、10KHz、1KHz、100Hz、10Hz、2Hz和1Hz等多个时钟●1个模拟信号源,提供频率和幅度可调的正弦波、三角波和方波●1个串行接口,用于完成与计算机的通信●1个VGA接口●1个PS2接口,可以接键盘或鼠标●1个USB接口,利用PDIUSBD12芯片实现USB协议转换●1个Ethernet接口,利用RTL8019芯片实现TCP/IP协议转换●基于SPI接口的音频CODEC模块●1个输入、输出探测模块,供数字信号的观察●16个LED显示●8个拨挡开关输入●8个按键输入●1个4X4键盘阵列●8个七段码管显示●1个扬声器模块●1个交通灯模块●1个直流电机模块●1个高速AD和1个高速DA●240×128大屏幕图形点阵LED显示●存储器模块提供256K×32bit(8Mbyte)的SRAM和8M×8Bit的FLASH ROM实验箱基本布局如下图1-1所示:图1-1 EDA/SOPC 试验箱系统布局下面就部分模块做简要介绍。

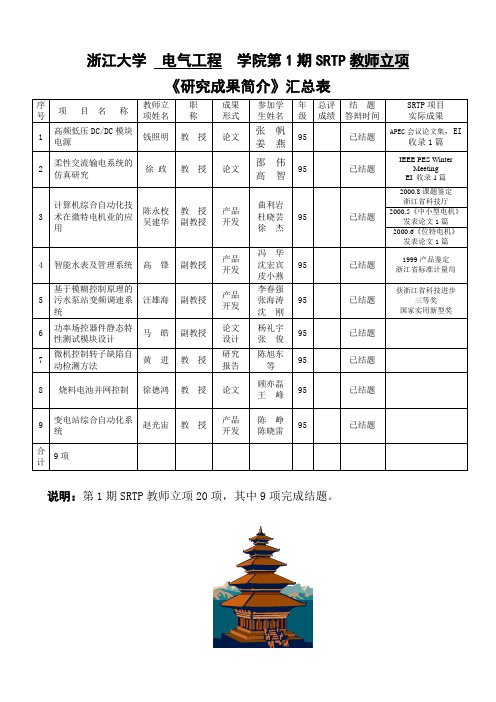

浙江大学电气工程学院第1期SRTP教师立项

方鸽飞

副教授

研究报告

李一泉

施松阳

胡晓辉

97级

良

(88)

2001.6

6

发电厂整定计算可视化程序的网络设计

王慧芳王康元赵舫

副教授

软件开发

陈林

陈宏山

98级

良

(88)

2002.1

7

输电线路三维地理信息系统的实现

邱家驹

教授

研究报告

徐奇锋应开怀

97级

中

(80)

2001.6

8

多组输出电源的精确控制研究

王正仕

讲师

成绩

结题

答辩时间

SRTP项目

实际成果

1

计算机管理信息系统

黄进

教授

论文

鉴定

陈敦

96级

优

(95)

2000.11

课题鉴定

2级刊物文章

发表2篇

2

可视化10kV配电网网损软件开发

徐瑞德

许诺

副教授

论文

鉴定

王敏

97级

优

(90)

2000.11

2000.11课题鉴定

浙江省电力局

2001.6

《电力系统及其自动化》发表论文1篇

3

电气工程管理学院科研管理信息系统

赵光宙

张国宏

教授

产品

开发

林群

裘君

97级

优

(96)

2000.11

浙江大学大学生科技成果获二等奖

4

智能型无功控制器

吴为麟

副教授

产品

开发

陈晓东

朱鹏军

梅雪

林颖

陈云

97级

基于通用实验平台的积木式加宝塔式电子系统综合实验箱设计

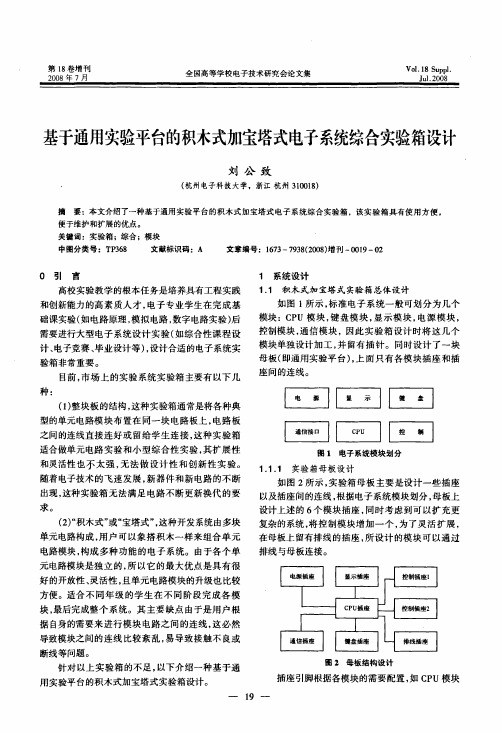

第18卷增刊2008年7月全国高等学校电子技术研究会论文集V01.18s uppl.J ul.2008基于通用实验平台的积木式加宝塔式电子系统综合实验箱设计刘公致(杭州电子科技大学,浙江杭州310018)摘要:本文介绍了一种基于通用实验平台的积木式加宝塔式电子系统综合实验箱,该实验箱具有使用方便,便于维护和扩展的优点。

关键词:实验箱;综合;模块中图分类号:T P368文献标识码:A文章编号:1673—7938(2008)增刊一0019—020引言高校实验教学的根本任务是培养具有工程实践和创新能力的高素质人才,电子专业学生在完成基础课实验(如电路原理,模拟电路,数字电路实验)后需要进行大型电子系统设计实验(如综合性课程设计、电子竞赛、毕业设计等),设计合适的电子系统实验箱非常重要。

目前,市场上的实验系统实验箱主要有以下几种:(1)整块板的结构,这种实验箱通常是将各种典型的单元电路模块布置在同一块电路板上,电路板之间的连线直接连好或留给学生连接,这种实验箱适合做单元电路实验和小型综合性实验,其扩展性和灵活性也不太强,无法做设计性和创新性实验。

随着电子技术的飞速发展,新器件和新电路的不断出现,这种实验箱无法满足电路不断更新换代的要求。

(2)“积木式”或“宝塔式”,这种开发系统由多块单元电路构成,用户可以象搭积木一样来组合单元电路模块,构成多种功能的电子系统。

由于各个单元电路模块是独立的,所以它的最大优点是具有很好的开放性、灵活性,且单元电路模块的升级也比较方便。

适合不同年级的学生在不同阶段完成各模块,最后完成整个系统。

其主要缺点由于是用户根据自身的需要来进行模块电路之间的连线,这必然导致模块之间的连线比较紊乱,易导致接触不良或断线等问题。

针对以上实验箱的不足,以下介绍一种基于通用实验平台的积木式加宝塔式实验箱设计。

1系统设计1.1积木式加宝塔式实验箱总体设计如图1所示,标准电子系统一般可划分为几个模块:cPu模块,键盘模块,显示模块,电源模块,控制模块,通信模块,因此实验箱设计时将这几个模块单独设计加工,并留有插针。

基于FPGA的SOC技术毕业设计

摘要随着半导体工艺技术的迅猛发展,可编程逻辑器件的集成度越来越高,FPGA中的逻辑资源也日益丰富,已达到百万门量级,这使得使用FPGA实现片上系统成为可能。

基于FPGA的片上系统设计方案具有开发周期短、设计成本低、软硬件在系统可编程、系统设计灵活、可裁减、可扩充、可升级等优点,正在成为电子系统设计的研究热点。

随着设计与制造技术的发展,集成电路设计从晶体管的集成发展到逻辑门的集成,现在又发展到IP的集成,即SOC设计技术。

SOC可以有效地降低电子信息系统产品的开发成本,缩短开发周期,提高产品的竞争力,是未来工业界将采用的最主要的产品开发方式。

FPGA将现代的VLSI逻辑集成的优点和可编程器件设计灵活,制作及上市快速的长处相结合,使设计者在FPGA开发系统软件的支持下,现场直接根据系统要求定义和修改其逻辑功能。

使一个包含数千个逻辑门的数字系统设计实现,采用FPGA技术,即可几天内完成。

本设计实现一种基于FPGA的SOPC解决方案,实现了系统的灵活性架构,以及参数化配置,便于系统的集成与设计修改,具有良好的可继承性与可移植性。

关键词:系统级芯片(片上系统);现场可编程门阵列;NiosⅡAbstractWith the rapid development of semiconductor technology,logic resources in FPGA have reached millions orders of magnitude,which make system-on-chip (SOC) based on FPGA has become possible. The design of SOC based on FPGA has many advantages,such as a short development cycle,low-cost,software and hardware in-system programmable,system design flexibility and can be trimmed,sealable,upgradeable,etc,Because of these,it has became a hot spot of research of electrical system design.With the design and manufacturing technology, integrated circuit design from transistors to integrated development of integrated logic gates, and now developed to the IP integration, that SOC design technology. SOC can effectively reduce the electronic information system product development costs, shorten development cycles, improve product's competitiveness, is the next most important industry will use methods of product development. FPAG the modern logic of integration of the advantages of VLSI and programmable device design flexibility, faster production and market strengths combined to enable FPGA designers to develop system software support, on-site directly from system requirements definition and change its logic function. Make a logic gate that contains thousands of digital system design and implementation, using FPGA technology can be completed within a few days.The Design and Implementation of FPGA-based SOPC solutions to achieve the flexibility of the system structure and parameters of configuration, ease of system integration and design changes, has a good inheritable and portability.Key words:SOC;FPGA;Nios Ⅱ目录摘要 (I)Abstract (II)1 绪论 (1)1.1 课题背景 (1)1.2目的及意义 (1)1.3国内外研究现状 (1)1.4论文章节安排 (2)2基于FPGA的SOC技术 (3)2.1 FPGA简介 (3)2.2 SOC概述 (7)2.3 SOPC概述 (8)2.4软核与硬核 (11)3 系统硬件设计 (14)3.1 QuartusⅡ简介 (14)3.2 SOPC Builder工具简介 (14)3.3嵌入式软核Nios II处理器 (15)3.4 Nios II CPU的搭建 (16)4 Nios ⅡIDE的软件设计 (22)4.1 新建软件工程 (22)4.2主程序设计 (23)4.3 UART串口 (24)4.4 LED控制 (26)结论 (29)致谢 (30)参考文献 (31)附录1:英文文献 (32)附录2:中文文献 (38)附录3:程序代码 (43)1 绪论1.1 课题背景EDA(Electronic Design Automation)技术是近几年迅速发展起来的计算机软件,硬件和微电子交叉的现代电子学科,涉及计算机操作系统、计算数学、电路理论和微电子学等领域,其内容广泛,综合性强。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于DE1-SoC的模块化数字系统实验箱的研制

黄霞;张冰洋

【期刊名称】《电子制作》

【年(卷),期】2023(31)1

【摘要】本文设计并研制了一套数字系统实验箱。

该实验箱以FPGA开发板DE1-SoC为基础,采用核心板加外设接口的模式进行设计,不仅能实现传统的硬件逻辑设计,还能完成Verilog硬件描述语言的FPGA设计,实现数字系统设计的实验,基本满足实验教学需求。

【总页数】4页(P86-88)

【作者】黄霞;张冰洋

【作者单位】中南民族大学实验教学与工程训练中心

【正文语种】中文

【中图分类】TP3

【相关文献】

1.基于虚拟仪器技术的模块化测控技术实验系统研制

2.信息学院“模块化综合电子系统设计实验箱”被评为全国高等学校电子技术研究会实验教学成果一等奖

3.基于FPGA的模块化联网实验箱系统的设计与实现

4.基于FPGA的模块化联网实验箱系统的设计与实现

5.数字电路和EDA实验箱的研制及数字电路实验教学改革

因版权原因,仅展示原文概要,查看原文内容请购买。