微电子器件与IC设计 (1)

微电子器件与IC设计基础第2版课后答案

课后习题答案1.1 为什么经典物理无法准确描述电子的状态?在量子力学中又是用什么方法来描述的? 解:在经典物理中,粒子和波是被区分的。

然而,电子和光子是微观粒子,具有波粒二象性。

因此,经典物理无法准确描述电子的状态。

在量子力学中,粒子具有波粒二象性,其能量和动量是通过这样一个常数来与物质波的频率ω和波矢k 建立联系的,即 k n c h p h E ====υωυ 上述等式的左边描述的是粒子的能量和动量,右边描述的则是粒子波动性的频率ω和波矢k 。

1.2 量子力学中用什么来描述波函数的时空变化规律?解:波函数ψ是空间和时间的复函数。

与经典物理不同的是,它描述的不是实在的物理量的波动,而是粒子在空间的概率分布,是一种几率波。

如果用()t r ,ψ表示粒子的德布洛意波的振幅,以()()()t r t r t r ,,,2ψψψ*=表示波的强度,那么,t 时刻在r 附近的小体积元z y x ∆∆∆中检测到粒子的概率正比于()z y x t r ∆∆∆2,ψ。

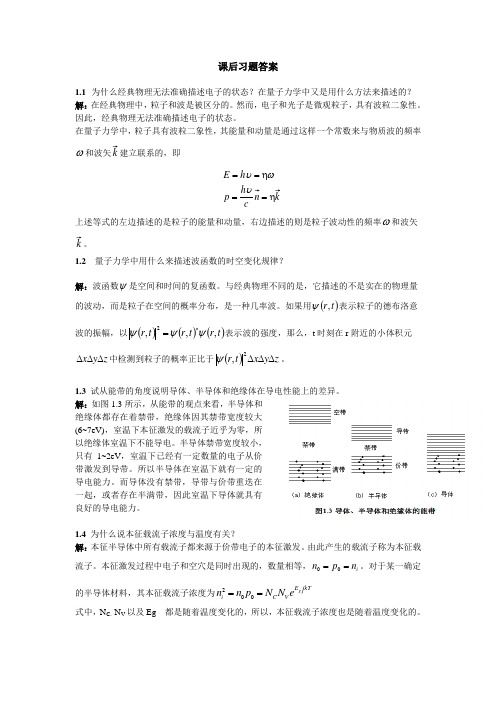

1.3 试从能带的角度说明导体、半导体和绝缘体在导电性能上的差异。

解:如图1.3所示,从能带的观点来看,半导体和绝缘体都存在着禁带,绝缘体因其禁带宽度较大(6~7eV),室温下本征激发的载流子近乎为零,所以绝缘体室温下不能导电。

半导体禁带宽度较小,只有1~2eV ,室温下已经有一定数量的电子从价带激发到导带。

所以半导体在室温下就有一定的导电能力。

而导体没有禁带,导带与价带重迭在一起,或者存在半满带,因此室温下导体就具有良好的导电能力。

1.4 为什么说本征载流子浓度与温度有关?解:本征半导体中所有载流子都来源于价带电子的本征激发。

由此产生的载流子称为本征载流子。

本征激发过程中电子和空穴是同时出现的,数量相等,i n p n ==00。

对于某一确定的半导体材料,其本征载流子浓度为kT E V C i g e N N p n n ==002式中,N C ,N V 以及Eg 都是随着温度变化的,所以,本征载流子浓度也是随着温度变化的。

IC设计总结文档

1.1 微电子技术概述1.1.1 集成电路的发展回顾全球集成电路发展的路程,基本上可以总结为六个阶段:第一阶段:1962年制造出包含12个晶体管的小规模集成电路(SSI,Small-Scale Integration)。

第二阶段:1966年发展到集成度为100~1000个晶体管的中规模集成电路(MSI,Medium-Scale Integration)。

第三阶段:1967~1973年,研制出1000~100000个晶体管的大规模集成电路(LSI,Large-Scale Integration)。

第四阶段:1977年研制出在30平方毫米的硅晶片上集成15万个晶体管的超大规模集成电路(VLSI,Very Large-Scale Integration)。

这是电子技术的第4次重大突破,从此真正迈入了微电子时代。

第五阶段:1993年随着集成了1000万个晶体管的16MB FLASH和256MB DRAM的研制成功,进入了特大规模集成电路(ULSI,Ultra Large-Scale Integration)时代。

第六阶段:1994年由于集成1亿个元件的1GB DRAM的研制成功,进入巨大规模集成电路(GSI,Giga Scale Integration)时代。

1.1.2 集成电路产业分工微电子技术的迅速发展得益于集成电路产业内部的细致分工。

目前,集成电路产业链主要包括设计、制造、封装和测试,如图所示。

在这历史过程中,世界IC产业为适应技术的发展和市场的需求,其产业结构经历了3次重大变革。

1、以生产为导向的初级阶段20世纪60年代的集成电路产业就是半导体产业,IC设计只是附属产品。

70年代出现独立的IC厂家设计IC产品。

2、Foundry与Fabless设计公司的崛起20世纪80年代,工艺设备生产能力已经相当强大,但是费用十分昂贵,IC厂家自己的设计不足以供其饱和运行,因此开始承接对外加工,继而由部分到全部对外加工,形成了Foundry加工和Fabless设计的分工。

第三章--双极型晶体管

c

b e

PNP

c b

e

NPN

3.1 晶体管的基本结构及杂质分布

3.1.2 BJT的杂质分布 1.锗合金管-均匀基区晶体管 特点: 三个区杂质均匀分布 2结为突变结

2.硅平面管-缓变基区晶体管 特点: E、B区杂质非均匀分布 2结为缓变结

3.1 晶体管的基本结构及杂质分布

“背靠背”的2个二极管有放大作用吗?

I ne IE

I ne Ine I pe

1 1 I pe

I ne

I pe Ine

,则 0

2、基区输运系数β*

0

I nc I ne

Ine Irb I ne

1

I rb I ne

I rb I ne

,则

0

3、集电区倍增因子 *

Ic 1

I nc

3.2.3、晶体管电流放大系数

e 1 e qVbe kT

x LpE

3.3 晶体管的直流电流增益

一、少数载流子分布

(3)、集电区少数载 流子分布

pC(x)

0

x

pC

x pC0 pC0

e 1 e qVbc kT

x LpC

3.3 晶体管的直流电流增益

二、电流密度分布函数

jnB

3.3 晶体管的直流电流增益

任务:导出α 0、β 0的定量关系式

0 0 0

0

0 10

0

1 1 I pe

I ne

0

1

I rb I ne

3.3.1 均匀基区晶体管的电流增益 均匀基区晶体管直流电流增益推导思路

ic设计必备知识点

ic设计必备知识点在现代科技发展迅猛的背景下,集成电路(IC)设计在电子领域中扮演着重要的角色。

为了更好地理解和应用IC设计,有一些必备的知识点是不可或缺的。

本文将介绍IC设计的核心概念、设计流程以及常用的设计工具和技术。

一、IC设计的核心概念1. MOSFET:金属氧化物半导体场效应管(MOSFET)是IC设计中最基本的构建块之一。

它是一种三端器件,由金属栅、绝缘层和半导体构成。

MOSFET的工作原理涉及栅极电压和源极-漏极电压之间的关系。

2. CMOS:互补金属氧化物半导体(CMOS)是一种常用的逻辑电路设计风格。

它由两个互补的MOSFET(pMOS和nMOS)组成,能够在低功耗消耗和高集成度之间取得平衡。

3. 时钟和时序:时钟在IC设计中起到同步和定时电路的作用,确保各个部分的协调工作。

时序设计涉及到信号的传输延迟、时钟抖动、时序约束等问题。

4. 逻辑门:逻辑门是IC设计中的基本单元,用于执行逻辑操作。

常见的逻辑门有与门、或门、非门等,它们可以组合形成更复杂的逻辑电路。

二、IC设计的流程1. 规划和需求分析:在IC设计之前,需要明确设计的目标和需求,包括功能、性能、功耗等方面的要求。

这些需求将指导后续的设计过程。

2. 电路架构设计:在这一阶段,设计师需要确定电路的整体结构和模块划分。

根据需求分析,选择合适的电路拓扑,并确定模块之间的接口和通信方式。

3. 逻辑设计:逻辑设计是将电路架构转化为逻辑电路图的过程。

使用硬件描述语言(HDL)进行高级抽象描述,并进行功能验证和仿真。

4. 物理设计:物理设计将逻辑电路图转化为布局和布线信息。

包括芯片尺寸和形状的规划,元件的布局,信号线的路径规划等。

5. 验证和测试:在IC设计完成后,需要进行验证和测试以确保其满足设计要求。

常用的验证手段包括静态和动态的功能验证、时序约束验证以及功耗和可靠性测试等。

三、IC设计的常用工具和技术1. EDA工具:EDA(Electronics Design Automation)工具是IC设计中不可或缺的辅助软件。

EDA重点

EDA重点(填空题、解答题、论述题、程序题)以下内容完全根据老师给的重点总结得到,如有不周,敬请谅解第一章VLSI概述1、微电子专业词汇IC(Integrated Circuit): 集成电路VLSI (Very Large Scale Integration):超大规模集成电路VDSM(Very Deep Sub-Micron): 超深亚微米(<=0.25um)ASIC(Application Specific Integrated Circuit): 专用集成电路ASSP(Application Specific Standard Products): 专用标准产品EDA(Electronic Design Automation):电子设计自化ESDA(Electronic System Design Automation): 电子系统设计自动化技术IP(Intellectual Property):指知识产权、著作权SOC(System on a chip): 片上系统(基于IP的半定制设计方法)PGA(Pin Grid Array) :阵栅(网格)阵列BGA(Ball Grid Array): 球栅(网格)阵列EDIF(Electronic Design Interchange Format):电子设计网表格式NRE(Non-Recurring Engineering):非重复性工程成本或一次性工程成本GA(Gate Array): 门阵列P&R(Place and Route): 布局布线LVDS(Low power differential signaling):低电压差分信号ESD(Electro-Static discharge):静电释放EMI(Electro-magnetic Interference) :电磁干扰Foundry:工艺生产线RTL(register Transfer lever):寄存器传输级ISP (In-System Programmability ):在系统可编程SOPC(System on programmable chip): 可编程片上系统2、封装的主要类型:从扦孔形(THP)向表面按装形式(SMP)发展,到现在的MCM(Multi-Chip Module)多芯片组件封装。

IC设计基本知识

IC设计的定义IC设计是将系统、逻辑与性能的设计要求转化为具体的物理版图的过程,也是一个把产品从抽象的过程一步步具体化、直至最终物理实现的过程。

为了完成这一过程,人们研究出了层次化和结构化的设计方法。

层次化的设计方法能使复杂的系统简化,并能在不同的设计层次及时发现错误并加以纠正。

结构化的设计方法是把复杂抽象的系统划分成一些可操作的模块,允许多个设计者同时设计,而且某些子模块的资源可以共享。

IC的分类ic按功能可分为:数字ic、模拟ic、微波ic及其他ic,其中,数字ic是近年来应用最广、发展最快的ic 品种。

数字ic就是传递、加工、处理数字信号的ic,可分为通用数字ic和专用数字ic。

专用ic(ASIC):是指为特定的用户、某种专门或特别的用途而设计的电路。

目前,集成电路产品有以下几种设计、生产、销售模式。

1、ic制造商(IDM)自行设计,由自己的生产线加工、封装,测试后的成品芯片自行销售。

2、ic设计公司(Fabless)与标准工艺加工线(Foundry)相结合的方式。

设计公司将所设计芯片最终的物理版图交给Foundry加工制造,同样,封装测试也委托专业厂家完成,最后的成品芯片作为IC设计公司的产品而自行销售。

通用ic:是指那些用户多、使用领域广泛、标准型的电路,如存储器(DRAM)微控制器(MCU)及微处理器(MPU)等,反映了数字ic的现状和水平。

世界IC设计产业发展的大趋势自ic设计公司诞生以来,其灵活的经营模式显示出旺盛的生命力,由于船小掉头快,紧跟世界热点的半导体应用市场,注重于产品的创新设计,再加上相关的Foundry公司服务体系逐趋完善和加工价格便宜,使其以超常速度发展,并体现出以下特点和发展趋势:1、龙头性ic设计是研究和开发ic的第一步,也是最重要的一步。

没有成功的设计,就没有成功的产品。

一个好的ic产品需要设计、工艺、测试、封装等一整套工序的密切配合,但设计是第一道。

2、创造性ic设计是一项创造力极强的工作。

微电子器件与IC设计基础_第2版_刘刚_陈涛_课后答案(DOC)

课后习题答案1.1 为什么经典物理无法准确描述电子的状态?在量子力学中又是用什么方法来描述的? 解:在经典物理中,粒子和波是被区分的。

然而,电子和光子是微观粒子,具有波粒二象性。

因此,经典物理无法准确描述电子的状态。

在量子力学中,粒子具有波粒二象性,其能量和动量是通过这样一个常数来与物质波的频率ω和波矢k 建立联系的,即k n ch p h E ====υωυ 上述等式的左边描述的是粒子的能量和动量,右边描述的则是粒子波动性的频率ω和波矢k 。

1.2 量子力学中用什么来描述波函数的时空变化规律?解:波函数ψ是空间和时间的复函数。

与经典物理不同的是,它描述的不是实在的物理量的波动,而是粒子在空间的概率分布,是一种几率波。

如果用()t r ,ψ表示粒子的德布洛意波的振幅,以()()()t r t r t r ,,,2ψψψ*=表示波的强度,那么,t 时刻在r 附近的小体积元z y x ∆∆∆中检测到粒子的概率正比于()z y x t r ∆∆∆2,ψ。

1.3 试从能带的角度说明导体、半导体和绝缘体在导电性能上的差异。

解:如图1.3所示,从能带的观点来看,半导体和绝缘体都存在着禁带,绝缘体因其禁带宽度较大(6~7eV),室温下本征激发的载流子近乎为零,所以绝缘体室温下不能导电。

半导体禁带宽度较小,只有1~2eV ,室温下已经有一定数量的电子从价带激发到导带。

所以半导体在室温下就有一定的导电能力。

而导体没有禁带,导带与价带重迭在一起,或者存在半满带,因此室温下导体就具有良好的导电能力。

1.4 为什么说本征载流子浓度与温度有关?解:本征半导体中所有载流子都来源于价带电子的本征激发。

由此产生的载流子称为本征载流子。

本征激发过程中电子和空穴是同时出现的,数量相等,i n p n ==00。

对于某一确定的半导体材料,其本征载流子浓度为kT E V C i g e N N p n n ==002式中,N C ,N V 以及Eg 都是随着温度变化的,所以,本征载流子浓度也是随着温度变化的。

《微电子器件》课件

随着科技的不断发展,新型微电子器件的研究也 在不断推进。目前,新型微电子器件主要集中在 柔性电子器件、生物可穿戴器件、量子器件等领 域。

生物可穿戴器件

生物可穿戴器件是指能够与人体直接接触并监测 人体生理参数的微电子器件。目前,生物可穿戴 器件的研究重点在于提高其舒适性、准确性和稳 定性。

描述模拟电路性能的参数,表示输入与输出 之间的线性关系。

微电子器件的测试方法与设备

测试方法

包括功能测试、性能测试和可靠性测试等。

测试设备

如示波器、信号发生器、频谱分析仪等。

测试环境

需要控制温度、湿度、电磁干扰等环境因素 。

测试标准

根据不同应用领域制定相应的测试标准。

微电子器件可靠性分析

可靠性定义

02

微电子器件的基本结构与 原理

半导体材料基础

半导体材料的分类

元素半导体、化合物半导体、掺 杂半导体等。

半导体的基本性质

导电性、光学特性、热学特性等。

半导体的能带结构

价带、导带、禁带等概念及其对电 子跃迁的影响。

PN结与二极管

PN结的形成

01

扩散、耗尽层、空间电荷区等概念。

二极管的伏安特性

02

性能和热管理技术。

机械可靠性

微电子器件在受到机械 应力时容易发生损坏, 机械可靠性问题不容忽 视。目前,机械可靠性 的研究重点在于提高微 电子器件的抗冲击和抗

振动性能。

电气可靠性

微电子器件在长时间工 作过程中容易出现电迁 移、氧化等问题,影响 其电气性能。目前,电 气可靠性的研究重点在 于提高微电子器件的稳

柔性电子器件

柔性电子器件具有轻薄、可弯曲、可折叠等特点 ,被广泛应用于可穿戴设备、智能家居等领域。 目前,柔性电子器件的研究重点在于提高其稳定 性、可靠性和生产效率。

微电子与集成电路设计导论 第一章 概论

图1.5.4 国内集成电路的供求关系

图1.5.5 集成电路的进口量

➢ 我国的微电子技术的发展大致可以分为两个阶段:

第一个阶段:在2000年之前,1956年,北京大学、复旦大学、东北人民 大学、厦门大学、南京大学在北大联合创建半导体专业。1977年在北京 大学诞生了第一块大规模集成电路。而在1980年以后,初步形成了制造 业、设计业、封装业分离的状态。

➢ 膜集成电路:是在玻璃或陶瓷片等绝缘物体上,以膜的形式制作电阻、电 容等无源器件,并加以封装而成。

➢ 混合集成电路:在实际应用中,多半是在无源膜电路上外加半导体集成电 路或分立元件的二极管、三极管等有源器件,使之构成一个整体,这便是 混合集成电路。

图1.4.1 集成电路的分类

1.5 微电子产业的发展现状

ห้องสมุดไป่ตู้

3. 对信息社会的作用

图1.2.3 信息社会各应用产品市场领域的销售额

4. 对传统产业的带动作用

微电子对传统产业的渗透与带动作用。几乎所有的传统产业与微电子技术结 合,用集成电路芯片进行智能改造,都可以使传统产业重新焕发青春。

对风机、水泵采用变频调速等电子技术进行改造,每年即可节电500亿度以上. 和机械学科的结合,导致很多传统的机械产品逐步电子化。 和生物学结合,生物芯片的诞生得以实现对细胞、蛋白质、DNA以及其他生

图1.3.8 摩尔定律示意图

➢ 早期研制和生产的集成电路都是双极型的。 1930年,德国科学家Lilien-filed提出了关于MOS场效应晶体管的概念、工作原理 以及具体的实施方案。 1960年Kang和Atalla研制出第一个利用硅半导体材料制成的MOS晶体管。 1962年以后出现了由金属-氧化物-半导体(MOS)场效应晶体管组成的MOS集成 电路。

IC设计基础笔试面试常见题目(含详细答案)

3、最基本的三极管曲线特性。

4、描述反馈电路的概念,列举他们的应用。 (仕兰微电子) 负反馈种类: (电压并联反馈( shunt-shunt feedback ) ,电流串联反馈(series-series feedback ) ,电压串联反馈 (series-shunt feedback)和电流并联反馈(shunt-series feedback) ; 负反馈的优点: 4.1 降低放大器的增益灵敏度,因此广泛应用在放大器的设计中(amplifier design) ; 4.2 改变输入电阻和输出电阻; 4.3 改善放大器的线性和非线性失真,因此高质音频放大器通常在 power output stage 采用负反馈; 4.4 有效地扩展放大器的通频带,因此负反馈广泛应用在 broadband amplifiers 中。

关于阻容耦合放大电路阻容耦合放大电路的频带宽度是指上限截至频率与下限截至频率之差阻容耦合放大电路的上限截止频率是指随着频率升高使放大倍数下降到原来的0707倍即3db时的频率阻容耦合放大电路的下限截止频率是指随着频率降低使放大倍数下降到原来的0707倍即3db时的频率

EE 笔试/面试题目集合分类--IC 设计基础

(体效应进一步减小了输入阻抗)

在 RD 较小时输入阻抗为: Z in 共栅极相当于一个电流 buffer 共栅极中,

Cgd 不会在输入-输出产生高频反馈,因此带宽较大;

9.4 共源共栅级放大电路

输出阻抗高: Z out

gm 2 ro 2 ro1 ,容易实现高的本证增益

因为共源共栅具有高的输出阻抗,一种普遍应用是很定电流源。 缺点:M2 叠加在 M1 上导致需要额外的电压余度,输出电压摆幅减小。 三种基本放大电路的对比总结: 相位关系:CS 反相;CG、CD 同相; 放大倍数:CS、CG 较大,CD 小于且接近于 1;

06 场效应晶体管讲解

6.2 MOSFET的基本结构及工作原理 6.2.3、 MOSFET的基本工作原理

6.2 MOSFET的基本结构及工作原理

6.2.3、 MOSFET的基本工作原理

基于“表面场效应”原理。 在垂直于半导体表面的电场作用下,半导体表面层中的

载流子浓度发生变化,导致表面层导电能力的改变。

以增强型MOS为例:

G

S

D

M

D:漏极

O

n+

n+

载流子:S→D

L

S

P

B 衬底电极

栅源电压:VGS

阈值电压VT:S表面达到强反型时的VGS

漏源偏置电压:VDS

6.2 MOSFET的基本结构及工作原理 (2)主要的结构参数:L, W, tox, NA,ND

铝栅: 硅栅:

(3) 平面图形

G

S

D

D S

G

6.2.2、MOSFET的基本类型

CMOS

1 1 1

CoxCS Cox CS

Cox CS

1. VG<0时,半导体表面为积累层,MOS电容等于氧化层电容Cox; 2. VG >0时,耗尽层出现,Cs使CMOS随VG升高而变小; 3. VG升高至反型层出现,耗尽层厚度最大,MOS电容达到最小值; 4. 高频时,反型电荷跟不上交流信号的变化,此时耗尽层电荷会略

VT VOX VS VFB

VOX :栅电压VG 降落在 SiO2 绝缘层上的部分 VS : 栅电压VG 降落在半导体表面的部分 VFB :平带电压

S

P-Si 衬底

D G

Eds Ids

6.3 MOSFET的阈值电压

6.3.2 平带电压 实际MOS结构:

ic设计岗位职责11篇

ic设计岗位职责11篇ic设计岗位职责11篇ic设计岗位职责1岗位描述:1、对线路进行分析整理、仿真及分析,制定适宜的fib方案以及验证fib数据2、芯片命令和码表含义分析3、配合其他部门完成芯片的验证以及芯片的功能分析,以及加解密算法的电路功能分析4、完成技术资料和产品文档的.编写、维护、归档等工作任职要求:1、微电子、电子工程、通信、自动化等相关专业本科以上学历,有五年以上工作者优先2、了解ic器件、工艺等相关知识3、熟悉数字、模拟ic基础,掌握cmos电路结构,具备扎实的半导体物理知识4、精通verilog的编程及仿真5、具有mcu、fpga、cpld、protel开发经验优先6、具有一定的数学理论知识,有算法理论基础及开发经验者的优先7、责任心强,具有良好的沟通表达能力和团队合作意识。

ic设计岗位职责2模拟ic设计师工作职责:1.负责硅基模拟类芯片的研发设计;2.负责设计多种模拟ic,包括但不限于:tia、la、transceiver等光通信和射频ic类芯片、dc-dc,ac-dc,led driver,charger等电源管理类芯片;3.负责完成电路的设计、仿真、验证和debug分析;4.配合版图完成版图设计和绘制。

任职要求:1.微电子、电子工程或相关专业本科或以上学历,具有扎实的模拟电路基础理论知识,cet4级,具有熟练的英文读写能力;2.1-3年及以上模拟ic设计经验,具有射频集成电路或电源管理类芯片设计经验者尤佳;3.熟练掌握模拟ic设计方法,熟悉并深刻理解cmos/bcd工艺;4.熟练运用spectrerf、hspice、ads等eda工具进行电路设计。

工作职责:1.负责硅基模拟类芯片的.研发设计;2.负责设计多种模拟ic,包括但不限于:tia、la、transceiver等光通信和射频ic类芯片、dc-dc,ac-dc,led driver,charger等电源管理类芯片;3.负责完成电路的设计、仿真、验证和debug分析;4.配合版图完成版图设计和绘制。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

集成电路发明的启示

集成电路早在1952年英国Dummer 已经提出其概 念,为什么它的发明不在英国而在美国呢? Michael F. Wolff 曾经总结了下面几条: 1. Kilby 和Noyce 都强调广泛的半导体技术基础 的重要性。1952年的英国并不存在这个基础, 而美国却存在。

2. 客观需求对小型化的要求,特别是军事上应 用提出的迫切需求,促进了集成电路的发明。 基于同一理由,军队需求成为集成电路的最早 用户,促进了集成电路的工业生产。

发 射 极

0.005cm

塑料楔

集 电 极

的间距

锗

蒸金箔

金属 基极

世界上第一个Ge点接触型PNP晶体管

2. 集成电路的发明

1952年5月,英国科学家G. W. A. Dummer达默 第一次提出 了集成电路的设想。1958年以德 克萨斯仪器公司的科学家基尔比 (Clair Kilby)为首的研究小组研制 出了世界上第一块集成电路,并 于1959年公布了该结果

肖克莱 ( William Shockley)

巴丁 (JohnBa rdeen)

布拉顿 (Walter Brattain)

晶体管的发明

二战结束时,诸多半导体方面的研究成果为晶体管的发 明作好了理论及实践上的准备。1946年1月,依据战略 发展思想,Bell实验室成立了固体物理研究组及冶金组, 开展固体物理方面的研究工作。在系统的研究过程中, 肖克莱根据肖特基的整流理论,预言通过“场效应”原 理,可以实现放大器,然而实验结果与理论预言相差很 多。经过周密的分析,巴丁提出表面态理论,开辟了新 的研究思路,兼之对电子运动规律的不断探索,经过多 次实验,于1947年12月实验观测到点接触型晶体管放大 现象。第二年1月肖克莱提出结型晶体管理论,并于 1952年制备出结型锗晶体管,从此拉开了人类社会步入 电子时代的序幕。

赫伯特· 克勒默

杰克· 基尔比

泽罗斯· 阿尔费罗夫

青年基尔比

集成电路草图

第一块集成电路

Ge 衬底上的混合集成电路,

美国专利号3138743

1958年9月12日,TI公司的Jack S.Kilby在德州仪器半导体实验 室展示了一个构造较为简单的设备。第一次将所有有源和无源 元器件都集合到只有一个曲别针大小(不足1/2英寸见方)的 半导体材料上。这块集成电路共集成了十二个元件(两个晶体 管、两个电容和八个电阻)。 Kilby本人也因此与赫伯特· 克勒 默和俄罗斯的泽罗斯· 阿尔费罗夫一起荣获2000年度诺贝尔物 理学奖。

2、芯片面积扩大

随着IC芯片功能的日益强大,电路系统也更加复杂,单 芯片面积也不断增大,以容纳更多的元器件和子单元。单片面 积已由10mm2 扩大到100mm2甚至几百mm2。大约每代产品的 芯片面积增大1.5倍。 3、大圆片Wafer,大直径化 圆片大直径化的发展:

4″ 5″ 6″ 8″ 10″ 12″ 16″

所谓Moore定律是在1965年 由INTEL公司的Gordon.Moore 提出的,其内容是硅集成电路 按照4年(后来发展到3~4年) 为一代、每代的芯片集成度要翻两番、工艺线宽约缩小30%、 IC工作速度提高1.5倍等发展规律发展。

Gordon E.Moore 博士-1965年

微电子发展的规律

3.集成电路发明不是偶然的事件,相反地, 它是对客观存在问题的一系列解决方案 研究的结果,是技术发展的客观必然。 4. Kilby 和Noyce 所在的两个公司TI和 Fairchild公司都是年轻、成长中的公司, 这里的管理者都营造了良好的有利于创 新的氛围。而Dummer 认为这正是当时 的英国所缺乏的。

集成微电子器件

主讲: 徐静平 教授

绪

论

微电子器件的发展历史和现状:

1947年:点接触晶体管问世;

1950年代:可控制导电类型的超高纯度单晶问世,结型 晶体管出现(取代真空管,收音机); 6 Hz 10

10 1960年代:第一代集成电路(IC)出现,电视时代;

1970年代:集成电路(IC) ,微波时代; 1010 Hz

1956年诺贝尔物理学奖授予美国加利福尼 亚州景山(Mountain View)贝克曼仪器公 司半导体实验室的肖克莱(William Shockley,1910—1989)、美国伊利诺斯州 乌尔班那伊利诺斯大学的巴丁(John Bardeen,1908—1991)和美国纽约州缪勒 海尔(Murray Hill)贝尔电话实验室的布拉 顿(Walter Brattain,1902—1987),以表彰 他们在1947年12月23日 发明第一个对半导 体的研究和PNP点接触式Ge晶体管效应的发 现。

1959年 美国仙童/飞兆公司( Fairchilds )的R.Noicy 诺依斯开发出用于IC的Si平面工艺技术,从而推动了IC制造业 的大发展。

1959年仙童公司制造的IC

年轻时代的诺伊斯

集成电路的发明

1958年,J. Kilby在对小型化IF放大器的仔细分析、特别 是进行了成本分析后,他认为用传统的微型化模型的工 作方式是解决不了问题的。解决问题的出路在于全半导 体化—— 一个新的方法。

由于集成电路器件制造能力按每3年翻 两番,即每年58%的速度提升,而电路 设计能力每年只以21%的速度提升,电 路设计能力明显落后于器件制造能力, 且其鸿沟(gap)呈现越来越变宽的趋势。

工艺线建设投资费用越来越高。目 前一条8英寸0.35μm工艺线的投资约20亿 美元,但在几年内一条12英寸0.09μm工 艺线的投资将超过100亿美元。如此巨额 投资已非单独一个公司,甚至一个发展 中国家所能单独负担的。

学习与科学研究是一个艰苦的 过程,需要有艰苦奋斗的准备, 需要终生的努力。

“终生努力,便成天才。”-门捷列夫。

集成电路发展简史

60年代 TTL、ECL出现并得到广泛应用。1966年 MOS LSI发明(集成度高,功耗低)

70年代 MOS LSI得到大发展(出现集成化微处理 器,存储器)VLSI,典型产品64K DRAM ,16位 MPU

集成电路发明的启示

Dummer 还特意强调,美国公司所以具有创新的精神,还 有下列一些条件: 1. 电子工程师往往用自己的资金或用风险基金创业, 因而工作勤奋。 2. 政府支持(政府给予合同)往往帮助他们起步。 3. 国内市场的需求是一个成功的重要因素。 4. 在美国,鼓励员工在公司中持股,给予员工一个 激励的机制。 Dummer 认为,一个企业的成功总是有赖于一些人的 创新和献身精神。 这些总结和归纳虽然发表在20多年前,但对当前的科学 研究工作和科技成果的产业化仍有着深刻的指导意义。

集成电路复杂度不断增加,系统芯 片或称芯片系统SoC (System-on-Chip)成为开发 目标、纳米器件与电路等领域的研究已展开。 英特尔曾于2003年11月底展示了首个能工作的 65纳米制程的硅片,Intel2004 年8月宣布,他 们已经采用65纳米,生产出了70Mbit的SRAM。 并计划于2005年正式进入商业化生产阶段。 SRAM(静态存储器)将用于高速的存储设备, 处理器中非常重要的缓存就是采用SRAM。

1958年第一块集成电路:TI公司的Kilby,12个器件,Ge晶片

1958年发明第一块简单IC的美国TI公司Jack S.Kilby 杰克· 基 尔比、美国加利福尼亚大学的赫伯特· 克勒默和俄罗斯圣彼得 堡约飞物理技术学院的泽罗斯· 阿尔费罗夫一起获得2000年 Nobel物理奖,以表彰他们为现代信息技术的所作出的基础性 贡献,特别是他们发明的IC、激光二极管和异质晶体管 。

8

Hz

1980年代:大规模集成电路(LSI),卫星通信时代; 1012 Hz

1990年代:超大规模集成电路(VLSI),光通信时代 1014 Hz

1. 晶体管的发明

1946年1月,Bell实验室正式成立半 导体研究小组, W. Schokley肖克莱,J. Bardeen巴丁、W. H. Brattain布拉顿。 Bardeen提出了表面态理论, Schokley给 出了实现放大器的基本设想,Brattain设 计了实验。1947年12月23日,第一次观测 到了具有放大作用的晶体管

因此他试图将电阻、电容等无源元件和有源元件都 做在同一块半导体材料上。进一步分析认为有可能将这 些元件同时“在位”制备在一起,并用互连形成电路。 这时,Kilby实际上已完成了集成电路的创新思维过 程。他很快就画出了关于触发器(flip-flop)的构思,用硅 的体电阻做电阻器,用P-N结形成电容器(1959年7月24 日的实验室笔记)。

21世纪

Intel表示,通过采用第二代应变硅技术( 应变硅技 术是一种对晶体管沟道部分的硅施加应力使其变形, 以此提高载流子迁移率的技术。借由加大硅原子间彼 此的距离,电子便能够更加迅速地运行。而电子的运 行速度越快,处理器的性能就越好。 )可以将晶体管 的性能提升10%~15%。与90纳米工艺制造的晶体管相 比,65纳米制程晶体管可以在同样的性能下减少4倍的 漏电电流。未来将会有越来越多的产品采用65纳米工 艺。 Intel公司2004年底宣布首次成功开发出15纳米的 晶体管。Intel的15纳米晶体管基于CMOS工艺,工作 电压为0.8伏,每秒可进行2.63万亿次开关转换。Intel 计划在2009年开发出基于15纳米晶体管的芯片,到时 该公司开发出的处理器将达到20GHz甚至更高。

(1″=1英寸 =2.54cm=25.4mm)

4、简化电路结构 半导体IC的持续发展,不仅有赖于材料和工艺技术的进步, 还需要从设计的角度出发,开发新型的电路结构,以尽可能少的 元件,实现预期的设计指标和性能。

表1.2将来硅基集成电路的要求(ITRS2005

年 份 2005 80 90 54 14 8G 386 2006 70 78 48 13 8G 386 2007 65 68 42 12 16G 386 2008 57 59 38 11 16G 773 2009 51 52 34 10 16G 773 2010 45 45 30 9 32G 773 2011 40 40 27 9 32G 1546 2014 28 28 19 8 64G 3092 2017 20 20 13 7 128G 6184