100进制计数器

基于MSI芯片74160设计模为100的计数器

基于MSI芯片74160设计模为100的计数器1、实验目的:基于MSI芯片74160,利用QuartusII软件设计并实现一个计数器的逻辑功能,通过电路的仿真和硬件验证,进一步了解计数器的特性和功能。

2、实验原理:利用集成计数器MSI芯片的清零端和置数端实现归零,可以按自然态序进行计数的N进制计数器的方法。

集成计数器中,清零、置数均采用异步方式的有74LS163;均采用异步方式的有74LS193、74LS197、74LS192;清零端采用异步方式、置数端采用同步方式的有74LS161、74LS160。

74161/74160功能真值表表1图13、实验环境:PC机(Windowsxp,QuartusII)4、实验内容:按照第五章相关内容,完成计数器的实际,包括原理图输入、编译、综合、适配、仿真,并将此计数器电路设计成一个硬件符号入库。

最后利用两个MSI芯片74160完成一个模为60的计数器的设计,包括原理图的输入、编译、综合、适配、仿真。

5、实验步骤:Step1.启动QuartusII“开始”菜单“所有程序”中的“Altera”程序框中选择“QuartusII”如图1所示:Step2.建立工作库目录文件夹以便设计工程项目的存储EDA工具中的任何一项设计都是一项工程(PROJECT),应首先为此工程建立一个放置与此工程相关的文件的文件夹,此文件夹将被EDA软件默认为工作库(WORK LIBRARY).一般不同的设计项目最好放在相应的文件夹中,注意,一个设计项目可以包含多个设计文件夹。

本项目中的文件夹取名为counter_100,路径为:E:/数字逻辑/作业/100511217/。

注意:文件夹名不能用中文,且不可带空格。

Step3.输入设计(1)打开QuartusII,选择File|New命令。

在New窗口中(如图2所示)的DeviceDesign File中选择硬件设计文件类型为Block Diagram/Schematic File,然后在框图设计文件编辑窗中输入源程序图1的文件。

(完整版)触发器时序逻辑电路习题答案

第4章 触发器4.3 若在图4.5电路中的CP 、S 、R 输入端,加入如图4.27所示波形的信号,试画出其Q 和Q 端波形,设初态Q =0。

SRCP图4.27 题4.3图解:图4.5电路为同步RS 触发器,分析作图如下:S RQ4.5 设图4.28中各触发器的初始状态皆为Q =0,画出在CP 脉冲连续作用下个各触发器输出端的波形图。

Q 11CPQ 3CPCPQ 2Q 6Q 4Q 5CP图4.28 题4.5图解:Q Q nn 111=+ Q Q n n 212=+ Q Q nn 313=+Q Q n n 414=+ Q Q n n 515=+ Q Q nn 616=+Q 1CP Q 2Q 3Q 4Q 5Q64.6 试写出 图4.29(a)中各触发器的次态函数(即Q 1 n+1 、 Q 2 n+1与现态和输入变量之间的函数式),并画出在图4.29(b )给定信号的作用下Q 1 、Q 2的波形。

假定各触发器的初始状态均为Q =0。

1A BCP>1D C1=1A BQ 1Q 2Q 2(a)BA(b)图4.29题4.6图解:由图可见:Q B A AB Q n n 111)(++=+ B A Q n ⊕=+12B A Q 2Q 14.7 图4.30(a )、(b )分别示出了触发器和逻辑门构成的脉冲分频电路,CP 脉冲如图4.30(c )所示,设各触发器的初始状态均为0。

(1)试画出图(a )中的Q 1、Q 2和F 的波形。

(2)试画出图(b )中的Q 3、Q 4和Y 的波形。

Y(b )(c )CPQ 1Q 2(a )图4.30 题4.7图解: (a )Q Q nn 211=+ QQ nn 112=+ Q F 1CP ⊕= R 2 = Q 1 低电平有效CPQ 1Q 2F(b )Q Q Q n n n 4313=+ Q Q Q n n n 4314=+ Q Q Y nn43=CP 3= CP 上降沿触发 CP 4= CP 下降沿触发CPQ 3Q 4Y4.8 电路如图4.31所示,设各触发器的初始状态均为0。

计数器工作原理及应用

计数器工作原理及应用除了计数功能外,计数器产品还有一些附加功能,如异步复位、预置数(注意,有同步预置数和异步预置数两种。

前者受时钟脉冲控制,后者不受时钟脉冲控制)、保持(注意,有保持进位和不保持进位两种)。

虽然计数器产品一般只有二进制和十进制两种,有了这些附加功能,我们就可以方便地用我们可以得到的计数器来构成任意进制的计数器。

下面我们举两个例子。

在这两个例子中,我们分别用同步十进制加法计数器74LS160构成一个六进制计数器和一个一百进制计数器。

因为六进制计数器的有效状态有六个,而十进制计数器的有效状态有十个,所以用十进制计数器构成六进制计数器时,我们只需保留十进制计数器的六个状态即可。

74LS160的十个有效状态是BCD编码的,即0000、0001、0010、0011、0100、0101、0110、0111、1000、1001[图5-1]。

图5-1我们保留哪六个状态呢?理论上,我们保留哪六个状态都行。

然而,为了使电路最简单,保留哪六个状态还是有一点讲究的。

一般情况下,我们总是保留0000和1001两个状态。

因为74LS160从100 1变化到0000时,将在进位输出端产生一个进位脉冲,所以我们保留了0000和1001这两个状态后,我们就可以利用74LS160的进位输出端作为六进制计数器的进位输出端了。

于是,六进制计数器的状态循环可以是0000、0001、0010、0011、0100和1001,也可以是0000、0101、0110、0111、1000和1001。

我们不妨采用0000、0001、0010、0011、0100和1001这六个状态。

如何让74LS160从0100状态跳到1001状态呢?我们用一个混合逻辑与非门构成一个译码器[图5.3.37b],当74LS160的状态为0100时,与非门输出低电平,这个低电平使74LS160工作在预置数状态,当下一个时钟脉冲到来时,由于等于1001,74LS160就会预置成1001,从而我们实现了状态跳跃。

数电第5章习题解答张克农版

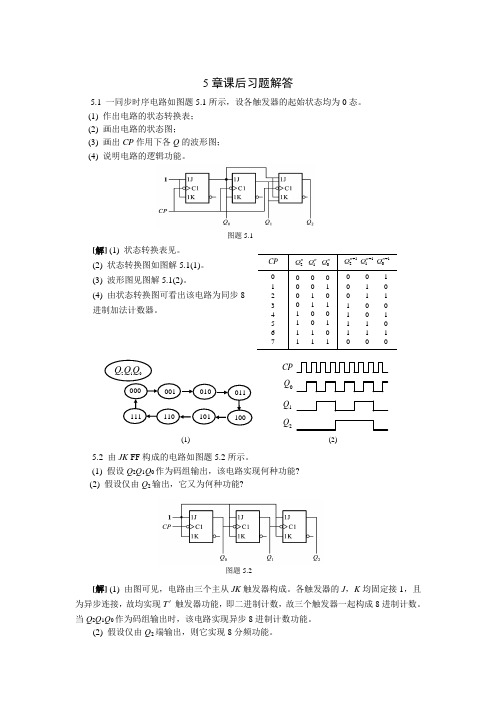

5章课后习题解答5.1 一同步时序电路如图题5.1所示,设各触发器的起始状态均为0态。

(1) 作出电路的状态转换表; (2) 画出电路的状态图;(3) 画出CP 作用下各Q 的波形图; (4) 说明电路的逻辑功能。

[解] (1) 状态转换表见。

(2) 状态转换图如图解5.1(1)。

(3) 波形图见图解5.1(2)。

(4) 由状态转换图可看出该电路为同步8进制加法计数器。

5.2 由JK FF 构成的电路如图题5.2所示。

(1) 假设Q 2Q 1Q 0作为码组输出,该电路实现何种功能?(2) 假设仅由Q 2输出,它又为何种功能?[解] (1) 由图可见,电路由三个主从JK 触发器构成。

各触发器的J ,K 均固定接1,且为异步连接,故均实现T '触发器功能,即二进制计数,故三个触发器一起构成8进制计数。

当Q 2Q 1Q 0作为码组输出时,该电路实现异步8进制计数功能。

(2) 假设仅由Q 2端输出,则它实现8分频功能。

图题 5.1图题5.2000001010 011 111110101100Q Q Q 012CPQ 0Q 1Q 2(1) (2)CP 210 n n n Q Q Q +1+1+1210 n n n Q Q Q 0 1 2 3 4 5 6 70 0 00 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 10 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 0 0 05.3 试分析图题5.3所示电路的逻辑功能。

[解] (1) 驱动程式和时钟方程02nJ Q =,01K =;0CP CP = 111J K ==;01CP Q= 210n nJ Q Q =,21K =;2CP CP = (2) 将驱动方程代入特性方程得状态方程0+1000020 ()n n n n nQ J Q K Q Q Q CP =+=+1111 ()n n Q Q CP = +12210 ()n n n n Q Q Q Q CP =(3) 根据状态方程列出状态转换真值表(4) 作状态转换图(5) 逻辑功能:由状态转换图可见该电路为异步5进制计数器。

100进制减法计数器程序

100进制减法计数器程序计数器一般都是用十进制数计数,但是在某些场景中,需要使用其他进制数进行计数。

100进制是一种常见的进制数,它的进制基数为100,每一位可以表示0-99的数字。

本文将介绍如何实现100进制的减法计数器程序。

首先,我们需要明确100进制的基本概念。

100进制一般可以使用两位来表示一个数位,例如45在100进制中可以表示成45,而120可以表示成1*100+20,即1020。

在程序中,我们可以用数组来表示100进制数,每一位用一个两位数来表示。

在实现减法计数器程序之前,我们需要先了解一下10进制减法的计算方法。

当我们做10进制减法时,如果被减数的某一位小于减数的对应位,我们需要从高位借位,并将被减数该位加上10,然后再计算减法。

在100进制中也是一样的,需要借位和进位操作。

下面,我们来看一下100进制减法计数器程序的具体实现。

首先,我们需要定义一个数组来表示计数器的值,例如:```int counter[4] = {0, 0, 0, 0}; //初始化为0```这个数组的长度为4,表示计数器能够计数的最大值为9999,因为100^4=10000。

接下来,我们定义一个函数来实现100进制减法:```void subtract(int* counter, int value) {int borrow = 0;for (int i = 3; i >= 0; i--) {int diff = counter[i] - (value % 100) - borrow;if (diff < 0) {diff += 100;borrow = 1;} else {borrow = 0;}counter[i] = diff;value /= 100;}}```这个函数接收一个计数器数组和一个减数,然后通过循环实现计数器减去减数的功能。

在每一次循环中,我们将被减的两个两位数相减,并考虑是否需要借位。

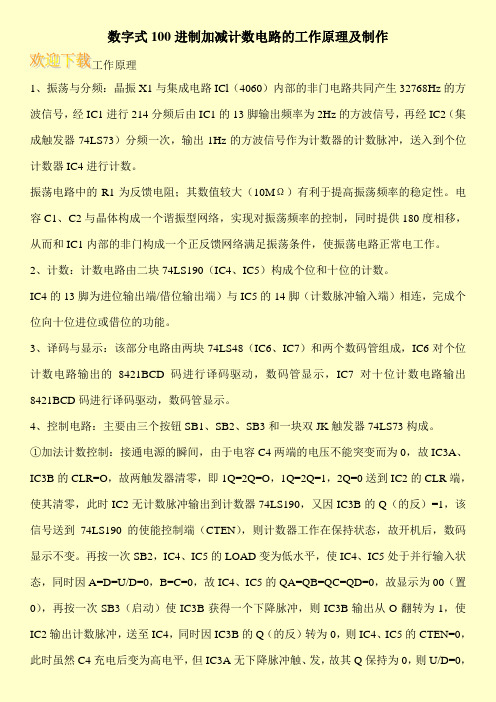

数字式100进制加减计数电路的工作原理及制作

数字式100进制加减计数电路的工作原理及制作工作原理1、振荡与分频:晶振X1与集成电路ICl(4060)内部的非门电路共同产生32768Hz的方波信号,经IC1进行214分频后由IC1的13脚输出频率为2Hz的方波信号,再经IC2(集成触发器74LS73)分频一次,输出1Hz的方波信号作为计数器的计数脉冲,送入到个位计数器IC4进行计数。

振荡电路中的R1为反馈电阻;其数值较大(10MΩ)有利于提高振荡频率的稳定性。

电容C1、C2与晶体构成一个谐振型网络,实现对振荡频率的控制,同时提供180度相移,从而和IC1内部的非门构成一个正反馈网络满足振荡条件,使振荡电路正常电工作。

2、计数:计数电路由二块74LS190(IC4、IC5)构成个位和十位的计数。

IC4的13脚为进位输出端/借位输出端)与IC5的14脚(计数脉冲输入端)相连,完成个位向十位进位或借位的功能。

3、译码与显示:该部分电路由两块74LS48(IC6、IC7)和两个数码管组成,IC6对个位计数电路输出的8421BCD码进行译码驱动,数码管显示,IC7对十位计数电路输出8421BCD码进行译码驱动,数码管显示。

4、控制电路:主要由三个按钮SB1、SB2、SB3和一块双JK触发器74LS73构成。

①加法计数控制:接通电源的瞬间,由于电容C4两端的电压不能突变而为0,故IC3A、IC3B的CLR=O,故两触发器清零,即1Q=2Q=O,1Q=2Q=1,2Q=0送到IC2的CLR端,使其清零,此时IC2无计数脉冲输出到计数器74LS190,又因IC3B的Q(的反)=1,该信号送到74LS190的使能控制端(CTEN),则计数器工作在保持状态,故开机后,数码显示不变。

再按一次SB2,IC4、IC5的LOAD变为低水平,使IC4、IC5处于并行输入状态,同时因A=D=U/D=0,B=C=0,故IC4、IC5的QA=QB=QC=QD=0,故显示为00(置0),再按一次SB3(启动)使IC3B获得一个下降脉冲,则IC3B输出从O翻转为1,使IC2输出计数脉冲,送至IC4,同时因IC3B的Q(的反)转为0,则IC4、IC5的CTEN=0,此时虽然C4充电后变为高电平,但IC3A无下降脉冲触、发,故其Q保持为0,则U/D=0,。

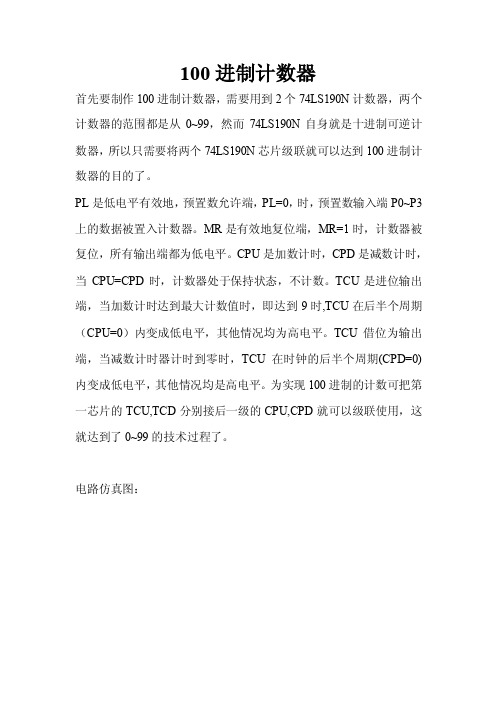

100进制计数器

100进制计数器

首先要制作100进制计数器,需要用到2个74LS190N计数器,两个计数器的范围都是从0~99,然而74LS190N自身就是十进制可逆计数器,所以只需要将两个74LS190N芯片级联就可以达到100进制计数器的目的了。

PL是低电平有效地,预置数允许端,PL=0,时,预置数输入端P0~P3上的数据被置入计数器。

MR是有效地复位端,MR=1时,计数器被复位,所有输出端都为低电平。

CPU是加数计时,CPD是减数计时,当CPU=CPD时,计数器处于保持状态,不计数。

TCU是进位输出端,当加数计时达到最大计数值时,即达到9时,TCU在后半个周期(CPU=0)内变成低电平,其他情况均为高电平。

TCU借位为输出端,当减数计时器计时到零时,TCU在时钟的后半个周期(CPD=0)内变成低电平,其他情况均是高电平。

为实现100进制的计数可把第一芯片的TCU,TCD分别接后一级的CPU,CPD就可以级联使用,这就达到了0~99的技术过程了。

电路仿真图:。

74192实现100进制计数器实验原理

74192是一种常见的集成电路,通常用于实现二进制或十进制的计数器。

虽然74192本身是二进制的计数器,但我们可以通过逻辑设计来将其转换为100进制计数器。

以下是实现100进制计数器的基本原理:

1. 使用四个74192:由于74192是四位计数器,我们需要使用四个74192芯片来构建100进制计数器。

每个74192芯片负责计数器的一个数位。

2. 设置计数范围:根据100进制,我们需要设置计数范围为0-99。

这意味着每个数位需要以100为基数进行计数。

因此,我们需要将每个74192的计数范围设置为0-99。

3. 连接输出:将四个74192芯片的计数输出相连,以形成完整的100进制计数器。

低位计数器的进位输出(Carry Out)将连接到高位计数器的时钟输入(Clock In),以实现进位。

4. 重置和启动:在开始计数之前,需要将所有74192芯片的复位输入(Reset)设置为逻辑高电平,以将计数器复位为0。

然后,通过将任意一个74192的时钟输入(Clock In)设置为逻辑高电平来启动计数器。

5. 结果显示:将每个74192芯片的计数输出连接到适当的显示设备,如数码管或LED灯,以显示计数器的当前值。

通过这种方式,我们可以利用多个74192芯片实现一个100进制计数器。

该实验需要适当的电路设计和连接,以及对集成电路的正确使用和配置。

EDA实验100进制计数器

录的路径字符串中不能包含中文字符。

2007.12.2

(4)检查错误并编译

为了确保输入的逻辑正确,可以保存文件并检查 错误。步骤如下:

a. 选择 FileProjectSave & compile 选项 ,这 将保存上面编辑的文件,并检查输入程序中的错

2007.12.2

b. 选择 FileNew 菜单,或单击 ,

2007.12.2

c. 选中 Text Editor file (文本设计文件)单选按 钮。

•d.图单形击编辑ok输按入钮。弹出 •Te符xt号E编dit辑or输窗入口。 • 文本编辑输入 • 波形编辑输入

(2)输入verilog HDL程序

文件名称和文本文 件一致,扩展名为 “.scf” ,单击OK 保存激励信号编辑 结果。

2007.12.2

(2)电路仿真

电路仿真属于设计校验,包括功能仿真(前仿真) 和时序仿真(后仿真)。本设计采用功能仿真。

a. 选择MAX+plusⅡSimulator选项,弹出仿真器窗口 。

b. 单击 Start 开始仿真 。

选择初始电平为“0”,时钟周期为“20 ns”,倍数为“1” (时钟周期倍数只能为整数倍),单击 OK 确认。

2007.12.2

e. 为输入端口添加信号

选中b输入端 然后点击窗口左侧的时钟信号源图标 出现如图所示的对话框

选择初始电平为“0”,时钟周期为“20 ns”,倍数为“2” (时钟周期倍数只能为整数倍),单击 OK 确认。

2007.12.2

以计数序列覆盖所选的单个组的全部或部分波形

e. 为输入端口添加信号

100以内的十进制计数器EDA课设

目录一、摘要二、任务要求三、基本原理四、实现方法五、基本过程六、分析与结论七、课程总结一、摘要电子设计自动化EDA技术课的目的在于培养学生掌握可编程逻辑器件基本的编程方法与开发应用技能。

在掌握了EDA技术的基础知识、基本操作和Quartus II软件的基本应用与一般流程后,学习EDA技术最有效的方法就是进行EDA 技术的综合应用设计。

本次设计阐述了100以内的十进制计数器的设计思路、VHDL 源程序、管脚设置、时序仿真和逻辑综合结果及分析。

十进制计数器由BCD码(二—十进制码)来设计,把一个数拆为个位(低四位)和十位(高四位),首先设定初值然后计数,同时对部分二进制数进行十进制调整。

二、任务要求首先设定100以内的十进制计数初值,而后每来一次脉冲降沿,计数值加1,加到99,然后计数值回0。

三、基本原理十进制计数器由BCD码(二—十进制码)来设计,把一个数拆为个位FD (低四位)和十位SD(高四位)。

设定计数初值高四位H和低四位L,LD为‘1’时置数,否则开始计数。

当个位为9即二进制的1001时且十位非9时,再来一次脉冲(CLK为0)计数时,个位为0即低四位清零,十位加1即高4位加1;十位为9即1001,且个位非9时,个位加1;十位为9且个位也为9时,个位十位全为0即高、低四位都清零。

四、实现方法1.VHDL源程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT10 ISPORT(CLK,LD:IN STD_LOGIC;H:IN STD_LOGIC_VECTOR(3 DOWNTO 0);L:IN STD_LOGIC_VECTOR(3 DOWNTO 0);FD:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0); SD:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0)); END ENTITY CNT10;ARCHITECTURE ART OF CNT10 ISBEGINPROCESS(CLK) ISBEGINIF(CLK'EVENT AND CLK='0')THENIF(LD='1')THENSD<=H;FD<=L;ELSIF(LD='0')THENIF(FD="1001")THENIF(SD="1001")THENFD<="0000";SD<="0000";ELSEFD<="0000";SD<=SD+1;END IF;ELSEFD<=FD+1;END IF;END IF;END IF;END PROCESS;END ARCHITECTURE ART;2、生成器件管脚如图1-1所示图1-1五、基本过程1、打开Quartus II 6.0软件,新建工程文件CNT10.qpf,然后新建VHDL 文件CNT10.vhd,输入VHDL 源程序,如图1-2图1-22、编译输入成功的VHDL源程序文件,并调试修改错误,最终使编译成功,如图1-3图1-33、设置管脚,使之在空心圆处设置输入端口CLK、H(3~0)、L(3~0)、LD以及输出端口FD(3~0)、SD(3~0),如图1-4图1-44、查看生成的器件,新建CNT10.bsf文件,找到project里的CNT10,并双击,即可观察到如图1-5所示的器件CLK LDH[3..0] L[3..0]FD[3..0] SD[3..0]CNT10inst图1-55、新建.vwf文件,导入输入、输出端口,并设置输出端口时钟信号CLK的波形以及计数初值(例如00100011即23)然后保存文件,如图1-6图1-66、在图1-6的界面中,编译,得到输出波形如图1-7、1-8所示,并分析数据验证是否符合设计要求。

三位二进制加法计数器(精)

成绩评定表学生姓名班级学号专业自动化课程设计题目数字电子课程设计评语组长签字:成绩日期20 年月日课程设计任务书学院信息科学与工程学院专业自动化学生姓名班级学号课程设计题目 1.三位二进制加法计数器(无效态:001,110)2.序列信号发生器的设计(发生序列100101)3.100进制加法计数器设计实践教学要求与任务:数字电子部分1)采用multisim 仿真软件建立电路模型;2)对电路进行理论分析、计算;3)在multisim环境下分析仿真结果,给出仿真波形图。

工作计划与进度安排:第1天:1. 布置课程设计题目及任务。

2. 查找文献、资料,确立设计方案。

第2-3天:1. 安装multisim软件,熟悉multisim软件仿真环境。

2. 在multisim环境下建立电路模型,学会建立元件库。

第4天:1. 对设计电路进行理论分析、计算。

2. 在multisim环境下仿真电路功能,修改相应参数,分析结果的变化情况。

第5天:1. 课程设计结果验收。

2. 针对课程设计题目进行答辩。

3. 完成课程设计报告。

指导教师:201 年月日专业负责人:201 年月日学院教学副院长:201 年月日目录1 课程设计的目的与作用11.1设计目的及设计思想11.2设计的作用11.3 设计的任务12 所用multisim软件环境介绍13 三位二进制同步加法计数器设计33.1 基本原理33.2 设计过程34序列信号发生器的设计..64.1 基本原理64.2 设计过程66 100进制加法器计数器76.1 基本原理76.2 设计过程75 仿真结果分析85.1 三位二进制同步加法计数器仿真85.2 序列信号发生器(发生序列100101)的仿真116 设计总结和体会147 参考文献141 课程设计的目的与作用1.1设计目的及设计思想根据设计要求设计三位二进制加法计数器和序列信号发生器,加强对数字电子技术的理解,进一步巩固课堂上学到的理论知识。

74ls160组成n进制计数器

实验 74LS160组成n进制计数器一、实验内容1.掌握集成计数器的功能测试及应用2.用异步清零端设计6进制计数器,显示选用数码管完成。

3.用同步置零设计7进制计数器,显示选用数码管完成。

二、演示电路74LS160十进制计数器连线图如图1所示。

图1 74LS160十进制计数器连线图CLR:异步清零端CLK:时钟输入端(上升沿有效)A-D:数据输入端ENP,ENT:计数控制端LOAD:同步并行置入控制端RCO:进位输出端74160的功能表如表1所示。

由表1可知,74160具有以下功能:①异步清零当CR(CLR’)=0时,不管其他输入端的状态如何(包括时钟信号CP),计数器输出将被直接置零,称为异步清零。

②同步并行预置数在CR=1的条件下,当LD(LOAD’)=0、且有时钟脉冲CP 的上升沿作用时,D0、D1、D2、D3输入端的数据将分别被Q0~Q3所接收。

由于这个置数操作要与CP上升沿同步,且D 0、D 1、D 2、D 3的数据同时置入计数器,所以称为同步并行置数。

③ 保持在CR =LD =1的条件下,当EN T =EN P =0,即两个计数使能端中有0时,不管有无CP 脉冲作用,计数器都将保持原有状态不变(停止计数)。

需要说明的是,当EN P =0, EN T =1时,进位输出C 也保持不变;而当ENT=0时,不管EN P 状态如何,进位输出RCO=0。

④ 计数当CR =LD =EN P =EN T =1时,74161处于计数状态,电路从0000状态开始,连续输入16个计数脉冲后,电路将从1111状态返回到0000状态,R CO 端从高电平跳变至低电平。

可以利用R CO 端输出的高电平或下降沿作为进位输出信号。

连上十进制加法计数器160,电路如图1所示,给2管脚加矩形波,看数码管显示结果,并记录显示结果。

三、用160和与非门组成6进制加法计数器-用异步清零端设计74160从0000状态开始计数,当输入第6个CP 脉冲(上升沿)时,输出Q 3 Q 2 Q 1 Q 0=0110,此时03Q Q CR==0,反馈给CR 端一个清零信号,立即使Q 3Q 2 Q 1 Q 0返回0000状态,接着,CR 端的清零信号也随之消失,74160重新从0000状态开始新的计数周期。

1、计数器的逻辑功能

典型集成计数器

1、同步四位二进制(十六进制)加法计数器SN74163

CLK R LD EP ET 工作模式

0 X X X 同步置 零

1 0 X X 同步预置数

X 1 101

保持

X 1 1 X 0 保持(C=0)

1 1 1 1 加法计数

Q0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0

Q1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 Q2 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 Q3 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0

C

1 fQ0 2 fCP

1 0 X X 同步预置数

X 1 101

保持

X 1 1 X 0 保持(C=0)

1 1 1 1 加法计数

注:逻辑符号和引脚排列与74163完全相同

小结

•掌握计数器的分类及特点。 •掌握集成计数器74LS163、74LS160的逻辑功能。

作业

补充:查阅集成手册看懂74LS191、74LS190的逻辑功能。

◆ 保持功能

当R’=LD’=1、EP• ET=0时,Q3Q2Q1Q0保持不变。

◆ 进位信号C

C= ET·Q3Q2Q1Q0

只有在ET=1且Q3Q2Q1Q0=1111时,C=1,表明下一个CLK 上升沿到来时将会有进位产生。

实现二进制加法计数功能:

计数

Q3Q2Q1Q0

0000 0001

1

EP Q0 Q1 Q2 Q3 C

1 ET

74163

LD 1

Verilog 实验报告 秒表

Verilog HDL实验报告基于Verilog HDL的数字秒表班级:信科14-04班姓名:温华强学号:08143080教师:王冠军基于Verilog HDL的数字秒表一、秒表功能1. 计时范围:00:00:00—59:59:992. 显示工作方式:八位数码管显示3.具有暂停和清零的功能二、实验设计原理1、秒表的逻辑结构较简单,它主要由十进制计数器、六进制计计数器、分频器、数据选择器和显示译码器组成,在整个秒表中最关键的是如何获得一个精确的100HZ计时脉冲,除此之外,整个秒表还需有一个启动信号和一个清零信号,以便秒表能随意停止、启动以及清零复位。

2、秒表有共有8个输出显示,其中6个显示输出数据,分别为百分之一秒,十分之一秒,秒,十秒,分,十分,所以共有6个计数器与之相对应,另外两个为间隔符,显示‘-’。

8个计数器的输出全都为BCD码输出,这样便与同显示译码器连接。

3、可定义一个24位二进制的寄存器hour用于存放8个计数器的输出,寄存器从高位到低位每连续4位为一组,分别存放百分之一秒,十分之一秒,间隔符,秒,十秒,间隔符,分,十分,由频率信号输出端输出频率为100HZ的时钟信号输入到百分之一秒模块的时钟端ckl,百分之一秒模块为100进制的计数器,当计数器到“1001”时,百分之一秒模块清零,同时十分之一秒模块加1,十分之一秒模块也为100进制的计数器,当计数到“1001”时,十分之一模块清零,同时秒模块加1;以此类推,一直到分模块计数器到59进59。

秒表计数单位与对应的输出信号4、为了消除按键消抖问题,定义寄存器key-inner来存储按键key的输入信号,key-flag作为启动/暂停的转换标志,key-inner[0]出现一个下降沿时,key-flag取反一次,当key-flag为0时计数器启动,1时计数器暂停,当key-flag 为1同时key-inner[1]为9时,计数器清零。

5、定义18位寄存器count用于存放分频和扫描用的计数值。

异步十进制加法计数器

异步十进制加法计数器000有效状态:0000--1001十个状态;无效状态:1010~1111六个状态.三,集成异步计数器CT74LS290为了达到多功能的目的,中规模异步计数器往往采用组合式的结构,即由两个独立的计数来构成整个的计数器芯片.如:74LS90(290):由模2和模5的计数器组成;74LS92:由模2和模6的计数器组成;74LS93:由模2和模8的计数器组成.1.CT74LS290的情况如下.(1)电路结构框图和逻辑功能示意图(2)逻辑功能如下表7.3.1所示.注:5421码十进制计数时,从高位到低位的输出为.2,利用反馈归零法获得N(任意正整数)进制计数器方法如下:(1)写出状态SN的二进制代码.(2)求归零逻辑(写出反馈归零函数),即求异步清零端(或置数控制端)信号的逻辑表达式.(3)画连线图.举例:试用CT74LS290构成模小于十的N进制计数器.CT74LS290则具有异步清零和异步置9功能.讲解教材P215的[例7.3.1].注:CT74LS90的功能与CT74LS290基本相同.7.3.2同步计数器一,同步二进制计数器1.同步二进制加法计数器2,同步二进制减法计数器3,集成同步二进制计数器CT74LS161(1)CT74LS161的引脚排列和逻辑功能示意图注:74LS163的引脚排列和74LS161相同,不同之处是74LS163采用同步清零方式.(2)CT74LS161的逻辑功能①=0时异步清零.C0=0②=1,=0时同步并行置数.③==1且CPT=CPP=1时,按照4位自然二进制码进行同步二进制计数.④==1且CPT·CPP=0时,计数器状态保持不变.4,反馈置数法获得N进制计数器方法如下:·写出状态SN-1的二进制代码.·求归零逻辑,即求置数控制端的逻辑表达式.·画连线图.(集成计数器中,清零,置数均采用同步方式的有74LS163;均采用异步方式的有74LS193,74LS197,74LS192;清零采用异步方式,置数采用同步方式的有74LS161,74LS160;有的只具有异步清零功能,如CC4520,74LS190,74LS191;74LS90则具有异步清零和异步置9功能.等等) 试用CT74LS161构成模小于16的N进制计数器5,同步二进制加/减计数器二,同步十进制加法计数器8421BCD码同步十进制加法计数器电路分析三,集成同计数器1,集成十进制同步加法计数器CT74LS160(1)CT74LS160的引脚排列和逻辑功能示意图图7.3.3CT74LS160的引脚排列图和逻辑功能示意图(2)CT74LS160的逻辑功能①=0时异步清零.C0=0②=1,=0时同步并行置数.③==1且CPT=CPP=1时,按照BCD码进行同步十进制计数.④==1且CPT·CPP=0时,计数器状态保持不变.2.集成十进制同步加/减计数器CT74LS190其逻辑功能示意图如教材图7.3.15所示.功能如教材表7.3.10所示.集成计数器小结:集成十进制同步加法计数器74160,74162的引脚排列图,逻辑功能示意图与74161,74163相同,不同的是,74160和74162是十进制同步加法计数器,而74161和74163是4位二进制(16进制)同步加法计数器.此外,74160和74162的区别是,74160采用的是异步清零方式,而74162采用的是同步清零方式.74190是单时钟集成十进制同步可逆计数器,其引脚排列图和逻辑功能示意图与74191相同.74192是双时钟集成十进制同步可逆计数器,其引脚排列图和逻辑功能示意图与74193相同.7.3.3利用计数器的级联获得大容量N进制计数器计数器的级联是将多个计数器串接起来,以获得计数容量更大的N进制计数器.1,异步计数器一般没有专门的进位信号输出端,通常可以用本级的高位输出信号驱动下一级计数器计数,即采用串行进位方式来扩展容量.举例:74LS290(1)100进制计数器(2)64进制计数器2,同步计数器有进位或借位输出端,可以选择合适的进位或借位输出信号来驱动下一级计数器计数.同步计数器级联的方式有两种,一种级间采用串行进位方式,即异步方式,这种方式是将低位计数器的进位输出直接作为高位计数器的时钟脉冲,异步方式的速度较慢.另一种级间采用并行进位方式,即同步方式,这种方式一般是把各计数器的CP端连在一起接统一的时钟脉冲,而低位计数器的进位输出送高位计数器的计数控制端.举例:74161(1)60进制(2)12位二进制计数器(慢速计数方式)12位二进制计数器(快速计数方式)7.4寄存器和移位寄存器寄存器是由具有存储功能的触发器组合起来构成的.一个触发器可以存储1位二进制代码,存放n位二进制代码的寄存器,需用n个触发器来构成.按照功能的不同,可将寄存器分为基本寄存器和移位寄存器两大类.基本寄存器只能并行送入数据,需要时也只能并行输出.移位寄存器中的数据可以在移位脉冲作用下依次逐位右移或左移,数据既可以并行输入,并行输出,也可以串行输入,串行输出,还可以并行输入,串行输出,串行输入,并行输出,十分灵活,用途也很广.7.4.1基本寄存器概念:在数字电路中,用来存放二进制数据或代码的电路称为寄存器.1,单拍工作方式基本寄存器无论寄存器中原来的内容是什么,只要送数控制时钟脉冲CP上升沿到来,加在并行数据输入端的数据D0~D3,就立即被送入进寄存器中,即有:2.双拍工作方式基本寄存器(1)清零.CR=0,异步清零.即有:(2)送数.CR=1时,CP上升沿送数.即有:(3)保持.在CR=1,CP上升沿以外时间,寄存器内容将保持不变.7.4.2移位寄存器1.单向移位寄存器四位右移寄存器:时钟方程:驱动方程:状态方程:右移位寄存器的状态表: 输入现态次态说明DiCP1↑1↑1↑1↑00001000110011101000110011101111连续输入4个1单向移位寄存器具有以下主要特点:单向移位寄存器中的数码,在CP脉冲操作下,可以依次右移或左移.n位单向移位寄存器可以寄存n位二进制代码.n个CP脉冲即可完成串行输入工作,此后可从Q0~Qn-1端获得并行的n位二进制数码,再用n个CP脉冲又可实现串行输出操作.若串行输入端状态为0,则n个CP脉冲后,寄存器便被清零.2.双向移位寄存器M=0时右移M=1时左移3.集成双向移位寄存器74LS194CT74LS194的引脚排列图和逻辑功能示意图:CT74LS194的功能表:工作状态0×××100×101↑110↑111×异步清零保持右移左移并行输入7.4.3移位寄存器的应用一,环形计数器1,环形计数器是将单向移位寄存器的串行输入端和串行输出端相连,构成一个闭合的环.结构特点:,即将FFn-1的输出Qn-1接到FF0的输入端D0.工作原理:根据起始状态设置的不同,在输入计数脉冲CP的作用下,环形计数器的有效状态可以循环移位一个1,也可以循环移位一个0.即当连续输入CP 脉冲时,环形计数器中各个触发器的Q端或端,将轮流地出现矩形脉冲.实现环形计数器时,必须设置适当的初态,且输出Q3Q2Q1Q0端初始状态不能完全一致(即不能全为"1"或"0"),这样电路才能实现计数,环形计数器的进制数N与移位寄存器内的触发器个数n相等,即N=n2,能自启动的4位环形计数器状态图:由74LS194构成的能自启动的4位环形计数器时序图二,扭环形计数器1,扭环形计数器是将单向移位寄存器的串行输入端和串行反相输出端相连,构成一个闭合的环.实现扭环形计数器时,不必设置初态.扭环形计数器的进制数N与移位寄存器内的触发器个数n满足N=2n的关系结构特点为:,即将FFn-1的输出接到FF0的输入端D0.状态图:2,能自启动的4位扭环形计数器7.4.4顺序脉冲发生器在数字电路中,能按一定时间,一定顺序轮流输出脉冲波形的电路称为顺序脉冲发生器.顺序脉冲发生器也称脉冲分配器或节拍脉冲发生器,一般由计数器(包括移位寄存器型计数器)和译码器组成.作为时间基准的计数脉冲由计数器的输入端送入,译码器即将计数器状态译成输出端上的顺序脉冲,使输出端上的状态按一定时间,一定顺序轮流为1,或者轮流为0.前面介绍过的环形计数器的输出就是顺序脉冲,故可不加译码电路即可直接作为顺序脉冲发生器.一,计数器型顺序脉冲发生器计数器型顺序脉冲发生器一般用按自然态序计数的二进制计数器和译码器构成.举例:用集成计数器74LS163和集成3线-8线译码器74LS138构成的8输出顺序脉冲发生器.二,移位型顺序脉冲发生器◎移位型顺序脉冲发生器由移位寄存器型计数器加译码电路构成.其中环形计数器的输出就是顺序脉冲,故可不加译码电路就可直接作为顺序脉冲发生器.◎时序图:◎由CT74LS194构成的顺序脉冲发生器见教材P233的图7.4.6和图7.4.77.5同步时序电路的设计(略)7.6数字系统一般故障的检查和排除(略)本章小结计数器是一种应用十分广泛的时序电路,除用于计数,分频外,还广泛用于数字测量,运算和控制,从小型数字仪表,到大型数字电子计算机,几乎无所不在,是任何现代数字系统中不可缺少的组成部分.计数器可利用触发器和门电路构成.但在实际工作中,主要是利用集成计数器来构成.在用集成计数器构成N进制计数器时,需要利用清零端或置数控制端,让电路跳过某些状态来获得N进制计数器.寄存器是用来存放二进制数据或代码的电路,是一种基本时序电路.任何现代数字系统都必须把需要处理的数据和代码先寄存起来,以便随时取用.寄存器分为基本寄存器和移位寄存器两大类.基本寄存器的数据只能并行输入,并行输出.移位寄存器中的数据可以在移位脉冲作用下依次逐位右移或左移,数据可以并行输入,并行输出,串行输入,串行输出,并行输入,串行输出,串行输入,并行输出.寄存器的应用很广,特别是移位寄存器,不仅可将串行数码转换成并行数码,或将并行数码转换成串行数码,还可以很方便地构成移位寄存器型计数器和顺序脉冲发生器等电路.在数控装置和数字计算机中,往往需要机器按照人们事先规定的顺序进行运算或操作,这就要求机器的控制部分不仅能正确地发出各种控制信号,而且要求这些控制信号在时间上有一定的先后顺序.通常采取的方法是,用一个顺序脉冲发生器来产生时间上有先后顺序的脉冲,以控制系统各部分协调地工作.顺序脉冲发生器分计数型和移位型两类.计数型顺序脉冲发生器状态利用率高,但由于每次CP信号到来时,可能有两个或两个以上的触发器翻转,因此会产生竞争冒险,需要采取措施消除.移位型顺序脉冲发生器没有竞争冒险问题,但状态利用率低.参考资料:第七章%20时序逻辑电路.doc。

数字式秒表的课程设计

《电子技术》课程设计报告题目数字式秒表学院(部)电控学院专业自动化班级32010701学生姓名罗天美学号3712 月14 日至12 月24 日共2 周指导教师(签字)肖梅前言本课程设计是进一步的数电学习,是数电知识在实际生活当中的主要应用之一,我们本着学以致用的原则,对学过的知识进行进一步的深化理解,以达到最终掌握的目的。

因此本课程设计通过对所学电路的比较分析,选择最优方案,通过这个应用实例,我们在掌握有关知识的过程当中,即可以提高学习兴趣,又可以对数字集成电路器件的使用形成一个完整的概念。

本课设中的各项模块,没有不以仿真软件的结果为实际支撑,这样做的目的可以锻炼我们的动手能力。

在本次课程设计当中,我们通过上网查询我们这个题目的有关资料之外,还通过在图书馆找寻相关书籍,以及我们数电课本和数电实验指导书等众多途径获得相关资料。

首先,秒表的分辨率为0.01秒,故要获得频率为100 HZ的基准毫秒脉冲;其次,分、毫秒计数器为100进制计数器,秒计数器为60进制计数器,还要通过译码器对计数器的输出进行译码,再通过七段数码管进行最后的时间显示。

最后,用一个控制键实现秒表的启动/暂停/继续计数功能,用另一个控制健实现秒表的清零功能。

分别实现以上模块功能,即可设计出符合要求的数字秒表。

在秒表的设计过程中,杨莎莎,李勇霞,罗天美为一组,罗天美负责获取基准脉冲的电路的设计,杨莎莎负责控制电路选择这个模块功能实现的设计,李勇霞同学负责计数□译码□显示单元的设计,而设计的整体框图和最后的总图连接由我们三人共同讨论决定。

最终,经过我们三人的共同努力,实现了要求的功能的逻辑设计,尽管,在最终的仿真阶段还有一些问题未能解决。

在此过程当中,因为我们知识有限,不免会有错误出现,还望老师批评指正。

目录摘要 (5)第一章系统概述 (6)1.1 数字式秒表的设计意义 (6)1.2 数字式秒表的设计要求与分析 (6)1.3 设计方案论证 (6)1.4 总体设计方案框图及分析 (6)第二章单元电路的设计与分析 (7)2.1 基准脉冲的获取 (7)2.2 控制电路的选择 (12)2.3 计数、译码、显示单元的设计 (14)第三章整体电路图 (19)3.1 总体电路图 (19)第四章体会与收获 (19)4.1 遇到的问题及解决方案 (19)4.2 心得体会 (20)参考文献 (21)元器件明细表 (21)鸣谢 (21)附图 (22)摘要本次的设计任务是一个数字秒表,而秒表与普通的钟表不同,它的目的是对从某一时刻到另一时刻的时间间隔进行计时。

multisim建立100进制计数器步骤

multisim建立100进制计数器步骤Multisim是一款非常流行的电路仿真软件,它可以帮助我们快速地设计各种电路并模拟其工作过程。

在实际的电路设计中,计数器经常被使用。

100进制计数器可以实现对0~99的数字进行计数和展示。

下面我们将介绍如何通过Multisim来建立一个简单的100进制计数器。

首先,我们需要打开Multisim软件并新建一个电路图。

在新建电路图的界面中,我们可以选择“文件”->“新建”->“电路图”来创建一个新的电路图文件。

创建好之后,我们就可以开始设计我们的计数器电路了。

第一步,我们需要选择适当的计数器芯片。

在Multisim中,我们可以直接从工具栏中拖拽各种芯片模块到电路图中。

我们需要选择一个100进制的计数器芯片,比如CD4017。

将CD4017拖拽到电路图中。

第二步,我们需要为芯片提供合适的时钟输入。

在Multisim中,我们可以在工具栏中找到各种电子元器件,包括时钟发生器。

我们需要将一个合适的时钟发生器拖拽到电路图中,然后将输出连接到计数器的时钟输入端口上。

第三步,我们需要将计数器的输出连接到适当的显示器上,以展示当前计数器的计数值。

在Multisim中,我们可以选择各种显示器模块,包括数字显示器。

我们需要选择一个100进制数字显示器,并将计数器的输出连接到其输入端口上。

第四步,我们需要为计数器提供复位功能,以便在需要时将计数器的值重置为0。

在Multisim中,我们可以使用一个按钮模块来实现复位功能。

我们需要将按钮的输出连接到计数器的复位端口上。

第五步,我们需要为电路添加电源。

在Multisim中,我们可以通过选择电池模块或一个直流电源来为电路提供电源。

我们需要将电源的正负极分别连接到电路的正负极端口上。

最后,我们需要检查一遍我们的电路图,并确认每个元器件的连接方式和参数设置都是正确的。

如果一切都准备好了,我们就可以开始仿真电路的工作过程,看看我们的计数器是否能够正常工作。

74192实现100进制计数器实验原理

74192实现100进制计数器实验原理100进制计数器是一种用于计算机科学和电子工程中的数字计数器。

它可以用来表示和处理范围在0到99之间的数字。

在这篇文章中,我们将介绍100进制计数器的原理以及如何实现它。

首先,让我们先了解一下计数器的基本工作原理。

计数器是一种递增的电子装置,可以记录或计算输入脉冲的数量。

它们通常是基于时钟信号进行计数,每个时钟脉冲都会导致计数器值的递增。

计数器通常包括输入端、时钟端、复位端和输出端。

输入端用来接收输入脉冲,时钟端用来接收时钟信号,复位端用来将计数器值重置为初始值,输出端用来输出计数器的当前值。

在100进制计数器中,我们需要使用两个10进制计数器来表示两位数字。

每个10进制计数器都可以表示0到9之间的数字。

当第一个计数器的值达到9时,它将发送一个进位信号到第二个计数器,同时将自身的值重置为0。

这样,第二个计数器的值将递增1。

当第二个计数器的值达到9时,它将发送一个进位信号到更高位(如果有的话),并将自身的值重置为0。

这样,我们可以实现一个0到99之间的数字计数器。

为了实现100进制计数器,我们需要使用逻辑门和触发器构建逻辑电路。

逻辑门用于控制输入脉冲的传递和进位信号的生成。

触发器用于存储计数器的当前值。

我们可以使用D触发器来实现这一功能。

让我们以一个简单的示例来说明具体操作。

假设我们要构建一个2位的100进制计数器。

这意味着我们需要使用两个10进制计数器,并且每个计数器都可以表示0到9之间的数字。

我们可以使用两个D触发器(称为D1和D2)来存储计数器的值。

首先,我们将输入脉冲连接到D触发器的时钟端。

每个输入脉冲到达时,D触发器将会根据当前输入(D1和D2)的值来更新输出(Q1和Q2)的值。

我们还需要将Q1和Q2连接到逻辑门中,以便在特定情况下生成进位信号。

接下来,让我们看看如何实现第一个10进制计数器。

我们可以使用两个逻辑门和两个D触发器来完成这个任务。

首先,我们将D1和D2与逻辑门G1和G2连接。

计数器的原理

计数器的原理计数器是数字电路中广泛使用的逻辑部件,是时序逻辑电路中最重要的逻辑部件之一。

计数器除用于对输入脉冲的个数进行计数外,还可以用于分频、定时、产生节拍脉冲等。

计数器按计数脉冲的作用方式分类,有同步计数器和异步计数器;按功能分类,有加法计数器、减法计数器和既具有加法又有减法的可逆计数器;按计数进制的不同,又可分为二进制计数器、十进制计数器和任意进制计数器。

一、计数器的工作原理1、二进制计数器(1)异步二进制加法计数器图1所示为用JK触发器组成的4位异步二进制加法计数器逻辑图。

图中4个触发器F0~F3均处于计数工作状态。

计数脉冲从最低位触发器F0的CP端输入,每输入一个计数脉冲,F0的状态改变一次。

低位触发器的Q端与高位触发器的CP端相连。

每当低位触发器的状态由1变0时,即输出一负跳变脉冲时,高位触发器翻转。

各触发器置0端R D并联,作为清0端,清0后,使触发器初态为0000。

当第一个计数脉冲输入后,脉冲后沿使F0的Q0由0变1,F1、F2、F3均保持0态,计数器的状态为0001;当图1 4位异步二进制加法计数器第二个计数脉冲输入后,Q0由1变为0,但Q0的这个负跳变加至F1的CP端,使Q1由0变为1,而此时F3、F2仍保持0状态,计数器的状态为0010。

依此类推,对于F0来说,每来一个计数脉冲后沿,Q0的状态就改变,而对于F1、F2、F3来说,则要看前一位输出端Q 是否从1跳到0,即后沿到来时,其输出端的状态才改变,否则Q1、Q2、Q3端的状态同前一个状态一样。

这样在第15个计数脉冲输入后,计数器的状态为1111,第16个计数脉冲输入,计数器恢复为0000。

由上述分析可知,一个4位二进制加法计数器有24=16种状态,每经过十六个计数脉冲,计数器的状态就循环一次。

通常把计数器的状态数称之为计数器的进制数(或称计数器的模),因此,4位二进制计数器也可称之为1位十六进制(模16)计数器。

表1所示为4位二进制加法计数器的状态表。

数字式秒表实验报告

数字式秒表实验报告摘要本次设计任务是设计一个数字式秒表经查阅资料后我把实验分为1.脉冲产生部分。

2.电路控制部分。

3.计数部分4.译码部分。

5显示部分。

脉冲产生部分我选择555多谐振荡器,产生100Hz的脉冲。

经参考资料,电路控制部分:启动和暂停控制开关使用由RS触发器组成的无抖动开关。

使用74ls160计数器计数,7447译码器驱动共阳极七段显示器。

实验要求1.秒表最大计时值为99分59.99秒;2. 6位数码管显示,分辨率为0.01秒;3 .具有清零,启动计时,暂停及继续计数等控制功能;4.控制操作间不超过二个。

实验分析数字式秒表,所以必须有一个数字显示。

按设计要求,须用七段数码管来做显示器。

题目要求最大记数值为99,59,99,那则需要六个数码管。

要求计数分辨率为0.01秒,并且需要相应频率的信号发生器。

选择信号发生器时,有两种方案:一种是用晶体震荡器,另一种方案是采用集成电路555定时器与电阻和电容组成的多谐振荡器。

经过查询资料,555多谐振荡器性能稳定,故采用555多谐振荡器。

数字式秒表是一个频率(100HZ)进行计数的计数电路。

由于数字式秒表计数的需要,故需要在电路上加一个控制电路,该控制电路清零、启动计时、暂停及继续计数等控制功能,同时100HZ的时间信号必须做到准确稳定。

数字电子钟的总体图如图所示。

由图可见,数字电子钟由以下几部分组成:555振荡器秒脉冲发生器,防抖开关;秒表控制开关;一百进制秒、分计数器、六十进制秒计数器;以及秒、分的译码显示部分等七段显示器译码器译码器译码器1005551. 555构成的多谐振荡器555构成的多谐振荡器电路图555多谐振荡器工作波形多谐振荡器工作波形周期计算2.多谐振荡器仿真图根据设计要求,需要产生一个频率为100HZ的信号,由于f=1/T,带入可以算出R1=R1=4.7KΩ,在仿真软件上仿真的时候可以设置电阻为4.7KΩ,加上一个50Ω的电位器来调节脉冲信号的精确度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验课程:EDA 实验

实验地点:第五实验室 实验时间:2012/11/12 班级:通信103班 学号: 102193 姓名:杨险峰

100进制计数器

一、实验目的:

1、设计一个100进制计数器;

2、掌握ISE 软件的综合与设计实现流程;

3、掌握采用ISE 软件进行FPGA 开发的过程以及试验箱的使用方法;

4、了解对设计电路进行功耗分析的方法;

5、了解ISE 软件设计报告中电路资源利用率情况分析;

6、掌握使用VHDL 创建测试文件的方法。

二、实验步骤:

1、启动ISE 集成开发环境,新建一个工程;

2、为工程添加设计源文件;

3、对源文件进行语法检查,并改正错误之处;

4、对设计进行时序仿真,分析设计的正确性;

5、锁定引脚,完成设计实现过程,并在试验箱上连线,利用iMPACT 进行程序下载;

6、在试验箱上验证计数器的功能,观察并记录实验结果;

7、打开report 文件查看资源利用率的情况;

三、实验原理:

输入时钟信号,输出接七段数码管的段码,数码管原理图如下:

四、实验代码:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_unsigned.ALL;

entity counter100 is

port(clk1,clk2:in std_logic;

y:out std_logic_vector(6 downto 0);

Y0 Y1 Y2 Y3 Y4

Y5 Y6 EN

clr en clk Vcc

swgw:out std_logic_vector(1 downto 0)); end counter100;

architecture Behavioral of counter100 is

signal xy:std_logic_vector(1 downto 0);

signal gw:std_logic_vector(3 downto 0) :="0000"; signal sw:std_logic_vector(3 downto 0);

signal w:std_logic_vector(3 downto 0);

signal led:std_logic_vector(6 downto 0);

begin

swgw<=xy;

y<=led;

process(clk1)

begin

if(clk1='1') then

xy<="01";

else

xy<="10";

end if;

end process;

process(clk2)

begin

if(clk2' event and clk2='1') then

if(gw="1001") then

gw<="0000";

else

gw<=gw+'1';

end if;

end if;

end process;

process(clk2)

begin

if(clk2' event and clk2='1') then

if(gw="1001") then

if(sw="1001") then

sw<="0000";

else

sw<=sw+'1';

end if;

end if;

end if;

end process;

process(xy)

begin

if(xy="01") then

w<=gw;

else

w<=sw;

end if;

end process;

with w select

led<="0000110" when "0001", --1

"1011011" when "0010", --2

"1001111" when "0011", --3

"1100110" when "0100", --4

"1101101" when "0101", --5

"1111101" when "0110", --6

"0000111" when "0111", --7

"1111111" when "1000", --8

"1101111" when "1001", --9

"0111111" when others; --0

end Behavioral;

所加激励:

五、实验记录及分析:

仿真激励:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

use IEEE.STD_LOGIC_unsigned.ALL;

ENTITY counter_tbw IS

END counter_tbw;

ARCHITECTURE behavior OF counter_tbw IS

-- Component Declaration for the Unit Under Test (UUT) COMPONENT counter100

PORT(

clk1 : IN std_logic;

clk2 : IN std_logic;

y : OUT std_logic_vector(6 downto 0);

swgw : OUT std_logic_vector(1 downto 0)

);

END COMPONENT;

--Inputs

signal clk1 : std_logic := '1';

signal clk2 : std_logic := '1';

--Outputs

signal y : std_logic_vector(6 downto 0);

signal swgw : std_logic_vector(1 downto 0); BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: counter100 PORT MAP (

clk1 => clk1,

clk2 => clk2,

y => y,

swgw => swgw

);

-- Stimulus process

stim_proc:--process

--begin

clk1<= not clk1 after 20 ns;

clk2<= not clk2 after 30 ns;

-- insert stimulus here

--end process;

END;

设计元件:

基准波形:

UCF文件:

NET "y[0]" LOC = B4;

NET "y[1]" LOC = A4;

NET "y[2]" LOC = D5;

NET "y[3]" LOC = C5;

NET "y[4]" LOC = A6;

NET "y[5]" LOC = B6;

NET "y[6]" LOC = E7;

NET "clk1" LOC = F7;

NET "clk2" LOC = D7;

NET "swgw[0]" LOC = C7;

NET "swgw[1]" LOC = F8;

NET "clk2" CLOCK_DEDICATED_ROUTE = FALSE;

表1:可编程器件、拨码开关的关系:

VHDL端口名称FPGA引脚号拨码开关序号Clk1 F7 时钟信号

Clk2 D7 时钟信号

Swgw[0]

C7 数码管段码1 Swgw[1]

F8 数码管段码2 y (6)

E7 接数码管对应短脚

y (5)

B6 y (4)

A6 y (3)

C5 y (2)

D5 y (1)

A4 y (0) B4

六、心得体会:

实验代码是其他同学写好的,在认真了读懂其含义后,完成了实验。

这样写的实验代码的程序比教材上给出的60进制计数器的方法要清晰和方便,能够直接利用数码管的显示观察计数器,更加直观。

这次实验过程,我们最开始没能理解如何“同时”显示多个数码管,并企图用数电课老师给的方法设计电路,频频有误。

后借鉴代码才明白多个数码管显示时并不是同时亮,而是通过clk 控制,使人眼观察为同时显示。

之前未给定个位的初始值,在仿真过程y 的输出信号总是不变化。

后给定初始值“0000”后,能实现仿真。

通过实验我更直观也更容易地明白了老师传授的相关知识。