8位全减器的设计图

八位减法器

课程名称:电子设计自动化技术课题名称: 8位减法器设计姓名:**学号: *********班级:数控卓越111 2013年11 月24 日目录 (1)摘要 (2)一、设计目的 (2)二、任务要求 (2)三、基本原理 (3)四、设计方案及实现方法 (3)五、设计条件 (4)六、设计步骤 (4)6.1、半减器的设计 (5)6.2、全减器的设计 (6)6.3、8位减法器设计 (6)七、结果与分析 (9)7.1、设计原理图或VHDL源程序 (9)7.2、器件及管脚分配图 (9)7.3、仿真波形 (9)八、总结 (10)九、参考文献 (11)摘要:EDA是电子设计自动化(Electronic Design Automation)的缩写,利用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC版图或PCB版图的整个过程的计算机上自动处理完成。

现在EDA广泛应用于机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域。

8位减法器作为数字电路的基础电路,也可以通过EDA设计实现其功能,并且广泛应用于各种电路。

关键词:EDA8位减法器电路一、设计目的1.熟悉EDA技术开发流程2.熟悉Quartes II集成开发软件的使用3.学习用原理图输入法和文本输入法进行简单设计4.熟悉简单组合电路设计,掌握系统仿真,学会分析硬件测试结果5.复习减法器的原理,掌握减法器的设计实现方法二、任务要求1.完成8位减法器的设计2.进行波形仿真,并分析仿真波形图,得出结论三、基本原理1、8位减法器的管脚如图:A0 B0 A1 B1 A2 B2 A3 B3A4 B4 A5 B5 A6 B6 A7 B7 SIN其中A i 为被减数,B i 为减数,SIN 为借位入,S i 为差,因为是8位减法器,在减的时候需要借位,所以有17个输入,分别对应8个全减器的输入,9个输出表示其结果。

VHDL8位减法器的设计共17页

• 5.2全减器源程序如下:

• 5.3减法器源程序如下:

• 5.4仿真波形

• 谢谢大家

56、书不仅是生活,而且是现在、过 去和未 来文化 生活的 源泉。 ——库 法耶夫 57、生命不可能有两次,但许多人连一 次也不 善于度 过。— —吕凯 特 58、问渠哪得清如许,为有源头活水来 。—— 朱熹 59、我的努力求学没有得到别的好处, 只不过 是愈来 愈发觉 自己的 无知。 ——笛 卡儿

拉

60、生活的道路一旦选定,就要勇敢地 走到底 ,决不 回头。 ——左

• 2.2半减器真值表

• 2.3全减器的原理

• 1.全减器是两个二进制的数进行减法运 算时使用的一种运算单元。

• 2.最简单的全减器是采用本位结果和借 位来显示,二进制中是借一当二,所以 可以使用两个输出变量的高低电平变化 来实现减法运算。

• 2.4全减器电路图

• 2.5全减器真值表

• 三、设计方案及设计方法

• 1、用VHDL语言设计一个半减器,并进行编用元件例化语句, 设计一个一位的全减器,并编译仿真;

• 3、在全减器的基础上,利用元件例化语句, 编写8位减法器程序,再进行编译仿真,可以 验证设计。

• 四、设计条件 • 1.计算机 • 2.Quartus Ⅱ

• 五、设计步骤 • 5.1半减器的设计 • 半减器的源程序如下:

VHDL8位减法器的设计

怎样思想,就有怎样的生活

VHDL8位减法器的设计

一、设计要求 二、基本原理 三、设计方案及实现方法 四、设计条件 五、设计步骤 六、结果与分析

• 一、设计要求

• 1.完成8位减法器的设计

• 2.进行波形仿真,并分析仿真波形图, 得出结论

二、基本原理 • 2.1半减器电路图

c616卧式车床八工位数控回转刀架毕业设计(全套图纸)[管理资料]

![c616卧式车床八工位数控回转刀架毕业设计(全套图纸)[管理资料]](https://img.taocdn.com/s3/m/86f442d12f60ddccdb38a092.png)

C616卧式车床八工位数控回转刀架设计【摘要】数控加工的加工精度高,生产率高,能减轻操作者劳动强度、改善劳动条件,有利于生产管理的现代化以及经济效益的提高,它的发展和运用,影响着制造业水平高低,实现生产过程的数控化,已经成为当今制造业的发展方向,所以非常值得我们去研究。

本设计通过对八工位卧式电动控制刀架的工作原理的分析,确定了多种方案,综合考虑各种方案的优缺点、性价比后,采用电动回转刀架。

其刀架机构的主要部件包括减速传动机构、刀架的抬起机构、锁紧与转位精定位机构等,控制系统软件包括控制系统的选择,控制系统软硬件的设计,收发信电路的设计等,设计中所采用螺杆抬起机构、端齿盘定位机构和单片机控制系统都计较经济实用,适合我们我国现阶段数控机床的发展需要。

【关键词】八工位,电动刀架,自动化,8051单片机[Abstract]The machining precision of NC machining high, high productivity, reduces the labor intensity of operator, improve working conditions, is conducive to the modernization of production management and improving economic benefit, its development and use, affect the manufacturing industry level, realizes the numerical control of the production process, has become the development direction of manufacturing industry, it is worth we are going to study.This design through the analysis of the work principle of the eight station horizontal electric control tool, to determine the various schemes, considering the advantages and disadvantages of various schemes, cost-effective, with electric rotary cutter. The tool holder mechanism consists of a deceleration transmission mechanism, cutter lifting mechanism, locking and indexing precision positioning mechanism, control system software includes the choice of the control system, the design of hardware and software of control system, transceiver circuit design, the screw lifting mechanism, the tooth disk positioning mechanism and a microcomputer control system all care about the economic and practical design, need to develop suitable for our country at thepresent stage of CNC machine tools.Key word.Eight station, electric tool, automation, 8051 single chip microcomputer目录1 绪论 (5)引言 (5)国内外研究现状 (5)存在的问题 (6)解决的方法 (7)2 方案设计 (8)自动刀架的基本要求和类型 (8) (8) (8)方案的拟定和确定 (9)3 总体结构设计 (11)减速传动机构方案设计 (11)刀架抬起机构设计 (12)上刀体锁紧与精定位机构设计 (13)4 主要部件的设计计算 (15)减速传动机构的设计计算 (15) (15) (15) (15) (19) (19)螺杆的设计计算 (20) (20) (21) (21)端齿盘设计 (21)端齿盘的特点 (22)端齿盘主要参数的设计计算 (22)5 电气控制部分设计 (26)控制系统的选择 (26)控制方式的选择 (27)硬件电路设计 (27) (27) (29)控制软件设计 (31)6 致谢 (37)7 参考文献 (38)1 绪论引言电动刀架是数控车床重要的传统结构,应用了自动控制、微电子、传感测量等方面的最新成就,是典型的机电一体化产品。

减法运算电路图

同加法运算一样,减法运算可采用减法器来实现。

半减器和全减器的设计方法和步骤与设计加法器相同。

实用上,为了简化系统结构,通常不另外设计减法器,而是将减法运算变为加法运算来处理,使运算器既能实现加法运算,又可实现减法运算。

一般采用加补码的方法代替减法运算,下面先来介绍这种方法的原理。

1.反码和补码这里只讨论数值码,即数码中不包括符号位。

以前应用的自然二进制码称为原码,所谓反码就是将原码中的所有0变为1,所有1变为0后的代码。

观察如下几组原码与反码之间的关系。

显然,每组反码都是从1111中减去原码的结果,所以,可得如下反码与原码的一般关系式:N反=(2n-1)-N原其中N等于数码的位数。

定义补码为:N补=2n-N原于是,便可得到补码和反码的关系式:N补=N反+1由以上分析可知,一个数的反码可将原码经反相器获得,而由反码加1就可得到补码。

2.由加补码完成减法运算由反码与原码的一般关系式可得两数A、B相减的表达式:上式表明A减B可由A加B的补码并减2n完成。

下图为4位减法运算电路图:由4个反相器将B的各位反相(求反),并将进位输入端C-1接逻辑1以实现加1,由此求得B的补码。

显然,只能由高位的进位信号与2n相减。

当最高位的进位信号为1(2n)时,它们的差为0;最高位的进位信号为0时,它与2n相减所得的差为1,同时还应发出借位信号。

因此,只要将最高位的进位信号反相即实现了减2n的运算,反相器的输出V为1时需要借位,故V为借位信号。

下面分两种情况分析减法运算过程。

(1)A-B≥0的情况。

设A=0101,B=0001。

求补相加演算过程如下:直接作减法演算,则有比较两种运算结果,它们完全相同。

在A-B≥0时,所得的差就是差的原码,借位信号为0。

(2)A-B<0的情况。

设A=0001,B=0101。

求补相加演算过程如下:直接作减法运算,则有:比较两种运算结果可知,前者正好是后者的绝对值的补码,借位信号V为1时表示差为负数,V为0时差为正数。

第三组(全加(减)器)05

课程设计(论文)课程名称:数字电子技术基础题目:全加(减)器的设计院(系):机械电子工程系专业班级:电信0901姓名:詹志鹏学号:200906030105指导教师:史毅敏2011年12月30日全加(减)器一、全减器是两个二进制的数进行减法运算时使用的一种运算单元。

最简单的全减器是采用本位结果和借位来显示,二进制中是借一当二,所以可以使用两个输出变量的高低电平变化来实现减法运算。

二、全加器是两个二进制的数进行加法运算时使用的一种运算单元。

最简单的全加器是采用本位结果和借位来显示,二进制中是逢二进一,所以可以使用两个输出变量的高低电平变化来实现加法运算。

我们的设计题目是采用Multisim设计一个全加(减)器,(当X=0实现加法运算;当X=1实现减法运算),用译码器和选择器分别实现。

关键词:全减器,全加器,选择器,译码器,Multisim目录1 设计任务 (3)2 设计方案 (3)3 电路设计 (8)4 整体电路图的仿真测试及性能检测 (10)5 收获与心得体会 (12)6 参考书目 (13)全加(减)器第一部分设计任务1、实验目的:(1)了解全加器和全减器的原理及逻辑功能,掌握全加器和全减器用途,熟悉全加器和全减器之间的相同点和不同点。

(2)了解译码器和选择器的原理及逻辑功能,掌握译码器和选择器用途,熟悉如何用译码器和选择器设计全加器和全减器。

(3)了解Multisim的工作特点,掌握Multisim设计方法,并用它设计出全加器和全减器。

2、实验要求:我们的设计题目是采用Multisim设计一个全加(减)器,(当X=0实现加法运算;当X=1实现减法运算),用译码器和选择器分别实现。

第二部分设计方案一、实验原理:(一)全加器是两个二进制的数进行加法运算时使用的一种运算单元。

最简单的全加器是采用本位结果和借位来显示,二进制中是逢二进一,所以可以使用两个输出变量的高低电平变化来实现加法运算。

1、元器件介绍译码器:译码是编码的逆过程,译码器的逻辑功能是将输入二进制代码的原意“译成”相应的状态信息。

全加器全减器设计实验报告

全加器全减器设计实验报告1. 引言全加器和全减器是数字电路中常用的基本电路模块之一。

全加器用于将两个二进制数相加,全减器用于将两个二进制数相减。

在本实验中,我们将设计并实现一个4位的全加器和一个4位的全减器电路。

2. 原理2.1 全加器全加器是由两个半加器和一个或门组成的电路。

一个半加器用于计算两个输入位的和,另一个半加器用于计算进位值。

将两个半加器的结果和进位值通过或门进行运算,即可得到全加器的输出。

如下图所示为全加器的逻辑电路图:其中,A和B为输入信号,用于表示待相加的两个二进制数的对应位;S为输出信号,表示两个输入数的对应位相加的结果;C为进位信号,表示相加时产生的进位。

2.2 全减器全减器是由两个半减器和一个与非门组成的电路。

与全加器类似,一个半减器用于计算两个输入位的差,另一个半减器用于计算借位值。

将两个半减器的结果和借位值通过与非门进行运算,即可得到全减器的输出。

如下图所示为全减器的逻辑电路图:其中,A和B为输入信号,用于表示待相减的两个二进制数的对应位;D为输出信号,表示两个输入数的对应位相减的结果;B为借位信号,表示相减时需要借出的位。

3. 设计和实现3.1 全加器设计根据2.1中的原理,我们可以使用两个半加器和一个或门来实现一个4位的全加器电路。

根据全加器的逻辑电路图,我们可以将四个输入位(A0, A1, A2, A3)依次与另外四个输入位(B0, B1, B2, B3)连接到两个半加器中,然后将两个半加器的和(S0, S1, S2, S3)通过或门进行运算。

此外,计算进位值需要使用到四个位的与门(And)。

具体电路图如下:3.2 全减器设计根据2.2中的原理,我们可以使用两个半减器和一个与非门来实现一个4位的全减器电路。

根据全减器的逻辑电路图,我们可以将四个输入位(A0, A1, A2, A3)依次与另外四个输入位取反连接到两个半减器中,然后将两个半减器的差(D0, D1, D2, D3)通过与非门进行运算。

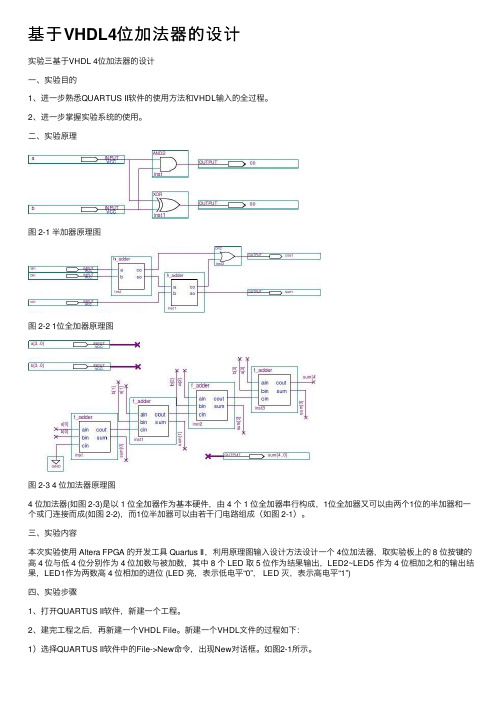

基于VHDL4位加法器的设计

基于VHDL4位加法器的设计实验三基于VHDL 4位加法器的设计⼀、实验⽬的1、进⼀步熟悉QUARTUS II软件的使⽤⽅法和VHDL输⼊的全过程。

2、进⼀步掌握实验系统的使⽤。

⼆、实验原理图 2-1 半加器原理图图 2-2 1位全加器原理图图 2-3 4 位加法器原理图4 位加法器(如图 2-3)是以 1 位全加器作为基本硬件,由 4 个 1 位全加器串⾏构成,1位全加器⼜可以由两个1位的半加器和⼀个或门连接⽽成(如图 2-2),⽽1位半加器可以由若⼲门电路组成(如图 2-1)。

三、实验内容本次实验使⽤ Altera FPGA 的开发⼯具 Quartus Ⅱ,利⽤原理图输⼊设计⽅法设计⼀个 4位加法器,取实验板上的 8 位按键的⾼ 4 位与低 4 位分别作为 4 位加数与被加数,其中 8 个 LED 取 5 位作为结果输出,LED2~LED5 作为 4 位相加之和的输出结果,LED1作为两数⾼ 4 位相加的进位 (LED 亮,表⽰低电平“0”, LED 灭,表⽰⾼电平“1”)四、实验步骤1、打开QUARTUS II软件,新建⼀个⼯程。

2、建完⼯程之后,再新建⼀个VHDL File。

新建⼀个VHDL⽂件的过程如下:1)选择QUARTUS II软件中的File->New命令,出现New对话框。

如图2-1所⽰。

图2-1 新建设计⽂件选择窗⼝2)在New对话框(图2-1)中选择Design Files页下的VHDL File,点击OK按钮,打开VHDL编辑器对话框,如图2-2所⽰。

图2-2 VHDL编辑窗⼝3、按照实验原理和⾃⼰的想法,在VHDL编辑窗⼝编写1位半加器的VHDL程序。

如图2-3所⽰。

图2-3 1位半加器VHDL程序4、编写完半加器VHDL程序后,保存,⽂件名为h_adder.vhd(注意⽂件名要与实体名保持⼀致),再将半加器⽂件设置为顶层⽂件,然后进⾏编译并仿真,对程序的错误进⾏修改。

第3章 组合电路的VHDL设计(四)—习题讲解学习

习题

3-4 给出1位全减器的VHDL描述;最终实现8位全减器。要求: (3)以1位全减器为基本硬件,构成串行借位的8位减法器,要求用例化语句来 完成此项设计(减法运算是x-y-sun_in=difft)

x7 xin sub_out sout

y7 yin u7

sub_in diff_out diff7 a6 ……………….

………………. a1

x1 xin sub_out

y1 yin u1

sub_in diff_out diff1 a0

x0 xin sub_out

y0 yin u0

sin sub_in diff_out diff0

串行借位的 8 位减法器

习题

3-5 用VHDL设计一个3-8译码器,要求分别用(条件)赋值语句、case语句、 if else语句或移位操作符来完成。比较这4种方式中,哪一种最节省逻辑资源。 (1)case语句实现:

习题

3-10 利用if语句设计一个3位二进制数A[2:0]、B[2:0]的比较器电路。对于比 较(A<B)、(A>B)、(A=B)的结果分别给出输出信号LT=1、GT=1、EQ=1

习题

3-14 用循环语句设计一个7人投票表决器。

习题

3-5 用VHDL设计一个3-8译码器,要求分别用(条件)赋值语句、case语句、 if else语句或移位操作符来完成。比较这4种方式中,哪一种最节省逻辑资源。 (2)if_else语句实现:

习题

3-6 设计一个比较电路,当输入的8421BCD码大于5时输出1,否则输出0。

习题

3-9 设计一个格雷码 至二进制数的转换器。

习题

3-4 给出1位全减器的VHDL描述;最终实现8位全减器。要求: (1)首先设计1位半减器,然后用例化语句将它们连接起来,图3-18中h_suber 是半减器,diff是输出差(diff=x-y),s_out是借位输出(s_out=1,x<y),sub_in是借 位输入。

减法器

目录第1章概述 (1)1.1 EDA技术及其发展 (1)1.2 Quartus II 软件介绍 (1)第2章减法器的设计 (3)2.1半减器的设计 (3)2.2 全减器的设计 (5)2.3八位全减器的设计 (7)第3章引脚锁定和编程下载 (10)3.1引脚锁定 (10)3.2编程下载 (10)结论 (12)参考文献 (13)第1章概述1.1 EDA技术及其发展EDA是电子设计自动化(Electronic Design Automation)的缩写,在20世纪60年代中期从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。

20世纪90年代,国际上电子和计算机技术较先进的国家,一直在积极探索新的电子电路设计方法,并在设计方法、工具等方面进行了彻底的变革,取得了巨大成功。

在电子技术设计领域,可编程逻辑器件(如CPLD、FPGA)的应用,已得到广泛的普及,这些器件为数字系统的设计带来了极大的灵活性。

这些器件可以通过软件编程而对其硬件结构和工作方式进行重构,从而使得硬件的设计可以如同软件设计那样方便快捷。

这一切极大地改变了传统的数字系统设计方法、设计过程和设计观念,促进了EDA技术的迅速发展。

EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

利用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC版图或PCB版图的整个过程的计算机上自动处理完成。

EDA技术是指以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。

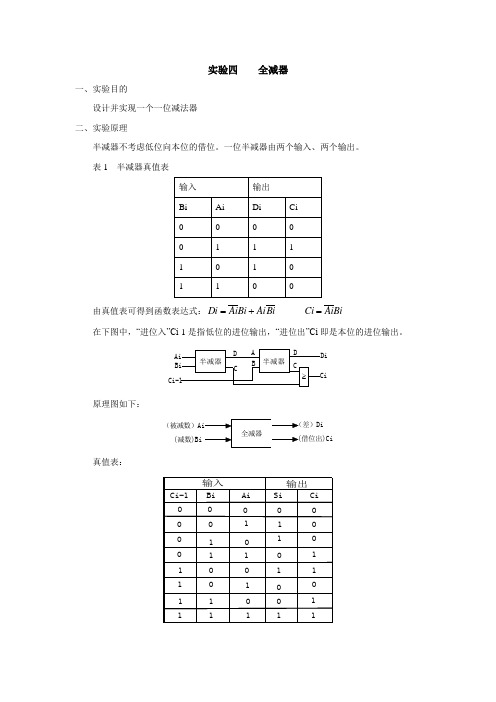

实验四 全减器

实验四 全减器一、实验目的设计并实现一个一位减法器 二、实验原理半减器不考虑低位向本位的借位。

一位半减器由两个输入、两个输出。

表1 半减器真值表输入 输出 Bi Ai Di Ci 0 0 0 0 0 1 1 1 1 0 1 0 11由真值表可得到函数表达式:Bi Ai Bi Ai Di += Bi Ai Ci =在下图中,“进位入”Ci -1是指低位的进位输出,“进位出”Ci 即是本位的进位输出。

Ai Bi A BCDDi CiC D 半减器半减器≥Ci-1原理图如下:全减器(被减数)Ai(减数)Bi(差)Di (借位出)Ci真值表:输入输出Ci-1Bi Ai Si Ci 0000000000000000000011111111111111111111根据真值表写出逻辑表达式:111i i i i i i i i i i D A B C A B C A B C ---=++三、实验步骤1、建立工程fullsub,新建VHDL 文件输入以下代码保存为fullsub1.vhdl 。

打开addern.vhdl 文件,选择File → Creat/Update → Creat Symbol Files for Current Files 生成顶层符号文件。

(参考实验一、二)----------------------半减器程序 library ieee;use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity halfsub is port(a,b:in std_logic; d,c:out std_logic); end halfsub;architecture half1 of halfsub is begind<=((a and (not b))or ((not a)and b)); c<=(not a)and b; end half1;-----------------------------------全减器程序 library ieee;use ieee.std_logic_1164.all; entity fullsub1 isport(ai,bi,ci:in std_logic; di,co:out std_logic); end fullsub1;architecture full1 of fullsub1 iscomponent halfsub-----------声明半减器调用 port(a,b:in std_logic;d,c:out std_logic); end component;signal halfsub1_d,halfsub1_c,halfsub2_c:std_logic;begin----------------------------------------------------------调用半减器 halfsub1:halfsub port map (ai,bi,halfsub1_d,halfsub1_c); halfsub2:halfsub port map (halfsub1_d,ci,di,halfsub2_c); co<=(halfsub1_c or ci); end full1;2、新建一个Block Diagramm/Schematic File 原理图文件,,在空白处双击添加生成的顶层原理图,并连接input 、output (输入输出管脚)重命名后如图所示,保存文件fullsub.bdf 。

全加器与全减器设计.

WHEN OTHERS=>NULL;

END CASE;

END PROCESS;

END ARCHITECTURE one;

三、总结

本次关于全加器与全减器的设计是由本组三人共同合作配合完成,知道了合作完成任务的重要性。

通过这次课程设计,加强了我们思考和解决问题的能力,巩固数字逻辑电路的理论知识,进一步发现自身的优点与不足:当面对问题时我们能冷静的想出解决问题的思路,同时也会去付诸实施。然而,在处理事情的过程中,也遇到了一些困难,我们虚心的与同学讨论,向老师请教。

WHEN"0011"=>S<='0';D<='1';

WHEN"0100"=>S<='1';D<='0';

WHEN"0101"=>S<='0';D<='1';

WHEN"0110"=>S<='0';D<='1';

WHEN"0111"=>S<='1';D<='1';

WHEN"1000"=>S<='0';D<='0';

总的来说,我认为这次的数电设计课程对我们来说都受益匪浅。课程设计反映的就是一个理论到实际应用的过程,更远一点可以联系到毕业以后从学校转到踏入社会的一个过程,我们要培养和同学间的合作,自身的动脑与努力是必然的,合作可能是更为重要的,但都是以后上社会工作必不可少的。

全减器设计

用半减器跟或门ห้องสมุดไป่ตู้成全减器电路图

程序

底层文件设计:半减器

1,布尔方程描述方法:

2,真值表描述法设计半减器

底层文件:或门

1位二进制全减器顶层设计描述

时序仿真结果

电路图综合

欢迎学习交流,本人联系qq:565768900

相对全减器半减器不用考虑低位的借位diffx?yxy?xysoutx?y全减器真值表x是被减数y是减数sunin是低位从本位的借位sout是本位从高位的借位diff是本位的差

全减器设计

学校:郑州大学 姓名:金义飞 班级:测控一班

半减器真值表

相对全减器,半减 器不用考虑低位的 借位

diff=x'y+xy'=x⊕y s_out=x'y

x是被减数,y是减数, s_out是本位从高位的借 位,diff是本位的差。

全减器真值表

diff=xyz+x'y'z+x'yz'+xy'z'=x⊕y⊕z s_out=x'y+x'z+yz

(sub_in用z代替)

x是被减数,y是减数,sun_in是 低位从本位的借位,s_out是本位 从高位的借位,diff是本位的差。

EDA技术与应用课后习题答案(2)

EDA技术与应用课后习题答案(2)END IF;END PROCESS;PR02:PROCESS(s1)BEGINIF s1=”0” THEN outy<=a1;ELSE outy<=tmp;END IF;END PROCESS;END ARCHITECTURE ONE;END CASE;4-4.下图是一个含有上升沿触发的D触发器的时序电路,试写出此电路的VHDL设计文件。

4-4.答案LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MULTI ISPORT(CL:IN STD_LOGIC; --输入选择信号CLK0:IN STD_LOGIC; --输入信号OUT1:OUT STD_LOGIC);--输出端END ENTITY;ARCHITECTURE ONE OF MULTI ISSIGNAL Q : STD_LOGIC;BEGINPR01: PROCESS(CLK0)BEGINIF CLK ‘EVENT AND CLK=’1’THEN Q<=NOT(CL OR Q);ELSEEND IF;END PROCESS;PR02: PROCESS(CLK0)BEGINOUT1<=Q;END PROCESS;END ARCHITECTURE ONE;END PROCESS;4-5.给出1位全减器的VHDL描述。

要求:(1) 首先设计1位半减器,然后用例化语句将它们连接起来,图3-32中h_suber是半减器,diff是输出差,s_out是借位输出,sub_in 是借位输入。

(2) 以1位全减器为基本硬件,构成串行借位的8位减法器,要求用例化语句来完成此项设计(减法运算是 x – y - sun_in = diffr) 4-5.答案底层文件1:or2a.VHD实现或门操作LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY or2a ISPORT(a,b:IN STD_LOGIC;c:OUT STD_LOGIC);END ENTITY or2a;ARCHITECTURE one OF or2a ISBEGINc <= a OR b;END ARCHITECTURE one;底层文件2:h_subber.VHD实现一位半减器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY h_subber ISPORT(x,y:IN STD_LOGIC;diff,s_out::OUT STD_LOGIC);END ENTITY h_subber;ARCHITECTURE ONE OF h_subber ISSIGNAL xyz: STD_LOGIC_VECTOR(1 DOWNTO 0); BEGINxyz <= x & y;PROCESS(xyz)BEGINCASE xyz ISWHEN "00" => diff<='0';s_out<='0';WHEN "01" => diff<='1';s_out<='1';WHEN "10" => diff<='1';s_out<='0';WHEN "11" => diff<='0';s_out<='0';WHEN OTHERS => NULL;END CASE;END PROCESS;END ARCHITECTURE ONE;顶层文件:f_subber.VHD实现一位全减器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY f_subber ISPORT(x,y,sub_in:IN STD_LOGIC;diffr,sub_out:OUT STD_LOGIC);END ENTITY f_subber;ARCHITECTURE ONE OF f_subber IS COMPONENT h_subberPORT(x,y:IN STD_LOGIC;diff,S_out:OUT STD_LOGIC);END COMPONENT;COMPONENT or2aPORT(a,b:IN STD_LOGIC;c:OUT STD_LOGIC);END COMPONENT;SIGNAL d,e,f: STD_LOGIC;BEGINu1: h_subber PORT MAP(x=>x,y=>y,diff=>d,s_out=>e);u2: h_subber PORT MAP(x=>d,y=>sub_in,diff=>diffr,s_out=>f);u3: or2a PORT MAP(a=>f,b=>e,c=>sub_out);END ARCHITECTURE ONE;END ARCHITECTURE ART;4-6.根据下图,写出顶层文件MX3256.VHD的VHDL设计文件。

《EDA技术实用教程(第五版)》习题答案(第1-10章)--潘(DOC)

《EDA技术实用教程(第五版)》习题1 习题1-1EDA技术与ASIC设计和FPGA开发有什么关系?FPGA在ASIC设计中有什么用途?P3~4EDA技术与ASIC设计和FPGA开发有什么关系?答:利用EDA技术进行电子系统设计的最后目标是完成专用集成电路ASIC的设计和实现;FPGA和CPLD是实现这一途径的主流器件。

FPGA和CPLD的应用是EDA技术有机融合软硬件电子设计技术、SoC(片上系统)和ASIC设计,以及对自动设计与自动实现最典型的诠释。

FPGA在ASIC设计中有什么用途?答:FPGA和CPLD通常也被称为可编程专用IC,或可编程ASIC。

FPGA实现ASIC设计的现场可编程器件。

1-2 与软件描述语言相比,VHDL有什么特点? P4~6答:编译器将软件程序翻译成基于某种特定CPU的机器代码,这种代码仅限于这种CPU 而不能移植,并且机器代码不代表硬件结构,更不能改变CPU的硬件结构,只能被动地为其特定的硬件电路结构所利用。

综合器将VHDL程序转化的目标是底层的电路结构网表文件,这种满足VHDL设计程序功能描述的电路结构,不依赖于任何特定硬件环境;具有相对独立性。

综合器在将VHDL(硬件描述语言)表达的电路功能转化成具体的电路结构网表过程中,具有明显的能动性和创造性,它不是机械的一一对应式的“翻译”,而是根据设计库、工艺库以及预先设置的各类约束条件,选择最优的方式完成电路结构的设计。

l-3什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么?P6什么是综合? 答:在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

有哪些类型?答:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。

(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。

实验6 结构化设计8位全减器

实验6 结构化设计8位全减器1 实验目的:利用Quartus II设计8位全减器,掌握Verilog HDL层次化设计的方法。

2 实验原理:一个8位全减器可以由8个1位全减器构成,1位全减器间的借位可以串行方式实现,即将低位全减器的借位输出bout与相邻的高位全减器的最低借位输入信号bin相接。

利用Verilog HDL的实例化语句实现模块重用,进行层次设计。

3 实验内容1:建立工程,参考4.1.5节完成1位半减器的连续赋值方式的设计。

3.1 给出1位半减器的真值表,写出输出表达式;3.2 编写1位半减器的Verilog HDL代码,保存(注意模块名和文件名要一致),将其设置为工程的顶层文件。

全程编译。

3.3 自行设计合理的波形并仿真,记录结果。

4 实验内容2:参考4.1.5节完成1位全减器的连续赋值方式的设计。

3.1 给出1位半减器的真值表,写出输出表达式;3.2 编写1位半减器的Verilog HDL代码,保存(注意模块名和文件名要一致),将其设置为工程的顶层文件。

全程编译。

3.3 自行设计合理的波形并仿真,记录结果。

3.4 利用上面设计的1位半减器,参照例4-9,进行实例化设计1位全减器,编写VerilogHDL代码,保存,将其设置为工程的顶层文件。

全程编译。

3.5 自行设计合理的波形并仿真,记录结果。

5 实验内容3:再次设计更高层次的8位加法器,利用以上获得的1位全减器实例化构成8位全减器。

5.1 编写Verilog HDL代码,保存,将其设置为工程的顶层文件。

全程编译。

5.2 自行设计合理的波形并仿真,记录结果。

要求波形中包含:被减数为学号的后两位,减数为任意大于被减数的数。

6 实验报告要求:将实验目的、原理、内容写进实验报告。

根据以上的实验内容写出实验报告,包括设计代码、程序分析报告、软件编译、仿真波形图及其分析报告。

要求详细叙述8位加法器的设计流程;给出各层次的代码及其对应的仿真波形图。

数电报告全加全减器的设计

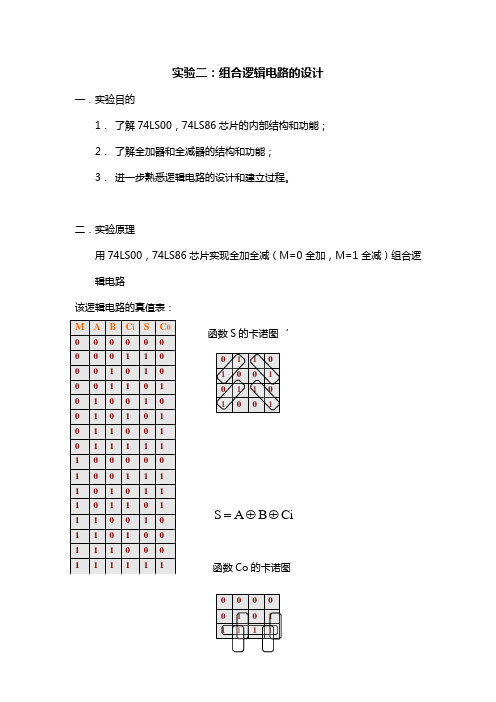

实验二:组合逻辑电路的设计

一.实验目的

1. 了解74LS00,74LS86芯片的内部结构和功能; 2. 了解全加器和全减器的结构和功能; 3. 进一步熟悉逻辑电路的设计和建立过程。

二.实验原理

用74LS00,74LS86芯片实现全加全减(M=0全加,M=1全减)组合逻辑电路

该逻辑电路的真值表: 函数S 的卡诺图‘ Ci B A S ⊕⊕=

函数Co 的卡诺图

0 1 0 1

Co⊕

)

=

B Ci

+

+

Ci

(A

M

B

)(

M,A,B,Ci分别代表四个输入端,S,Co分别为两个输出端,电路图如下图:

函数S的电路图

图一

函数Co的电路图

图二

三.实验内容

1.按图一搭建逻辑电路,先将输入都分别接在开关上,输入输出接在小灯上,测试实验结果,与真值表进行对照。

再将A接在Vpp=5V,f=1KHz 的方波上,将输出S接在示波器上,对比A与S的波形。

2.按图二搭建逻辑电路,先将输入都分别接在开关上,输入输出接在小灯上,测试实验结果,与真值表进行对照。

再将A接在Vpp=5V,f=1KHz 的方波上,将输出Co接在示波器上,对比A与Co的波形。

四.实验结果。

8位减法器设计课程设计

8位减法器设计课程设计一、课程目标知识目标:1. 让学生理解8位减法器的基本原理,掌握减法器的电路构成和功能。

2. 学会运用所学的数字电路知识,设计并实现8位减法器的电路图。

3. 掌握8位减法器的真值表,并能运用真值表进行逻辑功能分析。

技能目标:1. 培养学生运用所学知识解决实际问题的能力,具备一定的电路设计及分析技能。

2. 培养学生动手实践能力,能够独立完成8位减法器的搭建和调试。

3. 培养学生团队协作能力,通过小组讨论、合作完成课程任务。

情感态度价值观目标:1. 培养学生对电子技术的兴趣,激发学生的创新意识。

2. 培养学生严谨的科学态度,注重实验数据的真实性。

3. 培养学生面对困难勇于挑战的精神,提高学生的自信心。

课程性质分析:本课程为电子技术基础课程,通过设计8位减法器,使学生掌握数字电路的基本原理和设计方法。

学生特点分析:学生已经具备一定的数字电路基础,具有一定的逻辑思维能力和动手实践能力。

教学要求:1. 理论与实践相结合,注重培养学生的实际操作能力。

2. 采用任务驱动法,激发学生的探究欲望,培养学生的自主学习能力。

3. 强化团队合作,锻炼学生的沟通协调能力。

二、教学内容本课程教学内容以《数字电路与逻辑设计》教材中有关8位减法器的设计部分为基础,具体包括以下几部分:1. 数字电路基础知识回顾:使学生复习数字电路的基本概念、逻辑门电路及逻辑代数。

2. 8位减法器原理讲解:详细讲解8位减法器的原理,包括补码运算、加减运算电路等。

3. 电路设计与分析:- 介绍8位减法器电路的构成及各部分功能。

- 分析8位减法器的真值表,引导学生运用真值表进行逻辑功能分析。

4. 8位减法器电路图设计:指导学生运用所学知识设计8位减法器的电路图。

5. 实践操作:- 学生分组进行8位减法器的搭建和调试。

- 教师巡回指导,解答学生在实践过程中遇到的问题。

6. 课程总结与评价:对学生设计的8位减法器进行评价,总结课程中的重点和难点,巩固所学知识。

8位可控加减法电路设计

8位可控加减法电路设计电路设计是电子学的核心内容之一,也是实际应用中最为常见的任务之一、在这个任务中,我们需要设计一个8位可控加减法电路。

这个电路可以实现8位数的加法和减法运算,并且可以根据输入的控制信号来选择是进行加法还是减法运算。

在我们的电路设计中,我们将使用逻辑门和触发器来实现这个功能。

首先,我们需要一个8位的加法器和一个8位的减法器,这样才能实现加法和减法运算。

我们可以使用全加器来设计8位的加法器,该全加器可以用逻辑门和触发器来实现。

接下来,我们需要一个8位的选择器,该选择器可以根据输入的控制信号来选择是进行加法还是减法运算。

最后,我们需要一个8位的寄存器,该寄存器可以保存加法或减法运算的结果。

下面是我们的电路设计的详细步骤:1.首先,我们需要实现一个全加器。

全加器的输入包括两位的输入数和一个进位。

全加器的输出包括一个和位和一个进位。

我们可以使用逻辑门和触发器来实现全加器。

具体实现方法可以参考全加器的电路原理图。

2.然后,我们需要把8个全加器连接在一起,形成一个8位的加法器。

将输入的两个8位数和一个进位信号分别连接到每个全加器的输入端,将每个全加器的和位依次连接到寄存器中,将每个全加器的进位依次连接到下一个全加器的进位输入端,最后一个全加器的进位输出端不需要连接。

3.接下来,我们需要实现一个8位的减法器。

减法器的输入包括两个8位的输入数和一个借位。

减法器的输出是一个差位和一个借位。

我们可以使用逻辑门和触发器来实现减法器。

具体实现方法可以参考减法器的电路原理图。

4.然后,我们需要把8个减法器连接在一起,形成一个8位的减法器。

将输入的两个8位数和一个借位信号分别连接到每个减法器的输入端,将每个减法器的差位依次连接到寄存器中,将每个减法器的借位依次连接到下一个减法器的借位输入端,最后一个减法器的借位输出端不需要连接。

5.最后,我们需要实现一个8位的选择器。

选择器的输入包括两个8位的输入数和一个控制信号。

实验五 译码器和数据选择器的使用

实验五:译码器和数据选择器的使用1.实验目的1) 熟悉数据分配器和译码器的工作原理与逻辑功能。

2) 掌握数据分配器和译码器的使用2.理论准备1) 具有译码功能的逻辑电路称为译码器。

译码即编码的逆过程,将具有特定意义的二进制码进行辨别,并转换成控制信号。

按用途来分,译码器大体上有以下3类:(1)变量译码器;(2)码制变换译码器;(3)显示译码器。

2) 数据选择器又称多路开关,它是以“与或非”门或以“与或”门为主体的组合电路。

它在选择控制信号的作用下,能从多个输入数据中选择某一个数据作为输出。

常见的数据选择器有以下5种:(4)4位2通道选1数据选择器;(5)4通道选1数据选择器;(6)无“使能”端双4通道选1数据选择器;(7)具有“使能”端的互补输出地单8选1数据选择器。

3.实验内容1) 3线-8线译码器(74138)的功能测试2) 用3-8译码器设计一位全减器3) 用双4选1数据选择器(74153)设计一位全减器提示说明:①用译码器设计组合逻辑电路设计原理;②利用译码器产生输入变量的所有最小项,再利用输出端附加门实现最小项之和;③双4选1数据选择器:在控制信号的作用下,从多通道数据输入端中选择某一通道的数据输出Y=[D0(A1’A0’)+D1(A1’A0)+D2(A1A0’)+D3(A1A0)].S。

4.设计过程1)用3-8译码器设计一位全减器。

(1)分析设计要求,列出真值表。

如表一。

输入输出G1 G2A+G2B C B A Y0YY1 Y2 Y3 Y4 Y5 Y60 x x x x 1 1 1 1 1 1 1 1 x 1 x x x 1 1 1 1 1 1 1 1 1 0 0 0 0 0 1 1 1 1 1 1 11 0 0 0 1 1 0 1 1 1 1 1 11 0 0 1 0 1 1 0 1 1 1 1 11 0 0 1 1 1 1 1 0 1 1 1 11 0 1 0 0 1 1 1 1 0 1 1 11 0 1 0 1 1 1 1 1 1 0 1 11 0 1 1 0 1 1 1 1 1 1 0 11 0 1 1 1 1 1 1 1 1 1 1 0表一3-8译码器设计一位全减器真值表(2)根据真值表,写出逻辑函数表达式。

EDA(第4讲)第3章 VHDL入门3

13三人表决器的设计——CSE语句课堂练习题 语句课堂练习题

输入变量 输出 a b 0 0 0 0 0 1 1 1 1 0 1 1 0 0 1 1 c 0 1 0 1 0 1 0 1 y 0 0 0 1 0 1 1 1 要求: 根据真值表,写出VHDL程序 bjq a b c y

14

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; END PROCESS; ENTITY bjq IS END ARCHITECTURE aa ; PORT (a, b, c : IN STD_LOGIC; y : OUT STD_LOGIC); END ENTITY bjq; ARCHITECTURE aa OF bjq is SIGNAL abc : STD_LOGIC_VECTOR(1 DOWNTO 0) ; BEGIN 输入变量 输出 abc <= a & b & c; PROCESS(abc) a b c y BEGIN 0 0 0 0 CASE abc IS

0 0 0

0 1 1 0 0 1 1

1 0 1 0 1 0 1

0 0 1 0 1 1 1

15

; ; ; ;

1 1 1 1

外部端口

内部端口

端口连线: 端口连线:信号

16

或门的VHDL描述:or2a.vhd 描述: 或门的 描述

LIBRARY IEEE ; USE IEEE.STD_LOGIC_1164.ALL; ENTITY or2a IS PORT (a, b :IN STD_LOGIC; c : OUT STD_LOGIC ); END ENTITY or2a; ; ARCHITECTURE one OF or2a IS BEGIN c <= a OR b ; END ARCHITECTURE one ;