试谈半导体铜线工艺流程图

半导体铜制程

半导体铜制程随着现代科技的进步,半导体技术在各个领域都得到了广泛的应用。

而半导体铜制程作为一种重要的制程技术,在半导体工业中扮演着重要的角色。

本文将从半导体铜制程的定义、工艺流程、应用以及未来发展等方面进行阐述。

一、半导体铜制程的定义半导体铜制程,简称Cu制程,是指在半导体工艺中使用铜材料代替传统的铝材料作为金属导线的制程。

相比于铝制程,铜制程具有更低的电阻、更高的导电性能和更好的热稳定性,能够提高芯片性能和可靠性。

二、半导体铜制程的工艺流程半导体铜制程的工艺流程主要包括以下几个步骤:1. 清洗与准备:在制程开始之前,需要对芯片表面进行清洗和准备工作,以确保杂质的去除和表面的平整度。

2. 模板和光刻:在芯片表面涂覆一层光刻胶,然后使用光刻机将图案投射到光刻胶上,形成光刻模板。

3. 蚀刻:使用蚀刻液将光刻模板上的图案转移到芯片表面,去除不需要的材料。

4. 铜填充:将铜材料填充到蚀刻后的孔洞中,形成金属导线。

5. 漂镀:通过电化学方法在芯片表面形成一层保护层,以提高导线的导电性和抗氧化性。

6. 研磨和抛光:将芯片表面进行研磨和抛光,使其平整度更高,以便后续工艺步骤的进行。

7. 后续工艺:根据具体需求,可以进行多次重复的蚀刻、填充、漂镀等工艺步骤,以形成复杂的电路结构。

三、半导体铜制程的应用半导体铜制程在现代半导体工业中得到了广泛的应用。

其主要应用领域包括:1. 微电子芯片:半导体铜制程可以用于制造微电子芯片中的金属导线,提高芯片的电路性能和可靠性。

2. 太阳能电池:半导体铜制程可以用于太阳能电池的制造,提高电池的光电转换效率。

3. 集成电路:半导体铜制程可以用于集成电路的制造,提高电路的性能和集成度。

4. 电子元器件:半导体铜制程可以用于制造各种电子元器件,如电容器、电感器等,提高元器件的性能和可靠性。

四、半导体铜制程的未来发展随着半导体技术的不断发展,半导体铜制程也在不断完善和创新。

未来,半导体铜制程的发展趋势主要包括以下几个方面:1. 制程精度的提高:随着制程精度要求的不断提高,半导体铜制程需要更加精细的工艺控制和设备技术,以满足高性能芯片的制造需求。

半导体制作工艺流程+版图设计必备

N+ N+ P-

P+

N-Si

PSG P+

CMOS集成电路工艺 --以P阱硅栅CMOS为例

• 12。光刻Ⅷ---引线孔光刻。

N+ N+ P-

P+

N-Si

PSG P+

CMOS集成电路工艺 --以P阱硅栅CMOS为例

• 13。光刻Ⅸ---引线孔光刻(反刻AL)。

PSG

N+ N+ P-

N+-BL

P-SUB

去SiO2—氧化--涂胶—烘烤---掩膜(曝光)---显影---坚膜 —蚀刻—清洗—去膜—清洗—蒸铝

CMOS工艺集成电路

CMOS集成电路工艺 --以P阱硅栅CMOS为例

• 1。光刻I---阱区光刻,刻出阱区注入孔

SiO2

N-Si

N-Si

CMOS集成电路工艺 --以P阱硅栅CMOS为例

三、IC构装制程

• IC構裝製程(Packaging):利用塑膠 或陶瓷包裝晶粒與配線以成積體電路

• 目的:是為了製造出所生產的電路的保 護層,避免電路受到機械性刮傷或是高 溫破壞。

半导体制造工艺分类

MOS型

双极型

PMOS型 NMOS型 CMOS型 饱和型

非饱和型

BiMOS TTL I2L ECL/CML

第五次光刻—引线接触孔

•

SiO2

P P+

N+-BL

P N-epi P+ N-epi

N+ P+

N+-BL

P-SUB

去SiO2—氧化--涂胶—烘烤---掩膜(曝光)---显影---坚膜 —蚀刻—清洗—去膜—清洗

半导体制造工艺流程_图文

SiO2 P+

AL

N+ N-epi

P-SUB

Al P+

主要制程介绍

矽晶圓材料(Wafer)

圓晶是制作矽半導體IC所用之矽晶片,狀似圓 形,故稱晶圓。材料是「矽」, IC( Integrated Circuit)厂用的矽晶片即為 矽晶體,因為整片的矽晶片是單一完整的晶體 ,故又稱為單晶體。但在整體固態晶體內,眾 多小晶體的方向不相,則為复晶體(或多晶體 )。生成單晶體或多晶體与晶體生長時的溫度 ,速率与雜質都有關系。

外延层电阻

SiO2

R

N+

R

P+

P

P+

N-epi

P-SUB

集成电路中电阻5

MOS中多晶硅电阻

多晶硅

SiO2氧化层Si源自其它:MOS管电阻集成电路中电容1

SiO2 P+

A-

N+E P+-I

N+-BL P-SUB

B+

A-

B+

N P+ Cjs

发射区扩散层—隔离层—隐埋层扩散层PN电容

集成电路中电容2

N+

後段backend构装packaging测试制程initialtestandfinaltest一晶圆处理制程晶圆处理制程之主要工作为在矽晶圆上制作电路与电子元件如电晶体电容体逻辑闸等为上述各制程中所需技术最复杂且资金投入最多的过程以微处理器microprocessor为例其所需处理步骤可达数百道而其所需加工机台先进且昂贵动辄数千万一台其所需制造环境为为一温度湿度与含尘particle均需控制的无尘室cleanroom虽然详细的处理程序是随著产品种类与所使用的技术有关

半导体IC的制做工艺图解

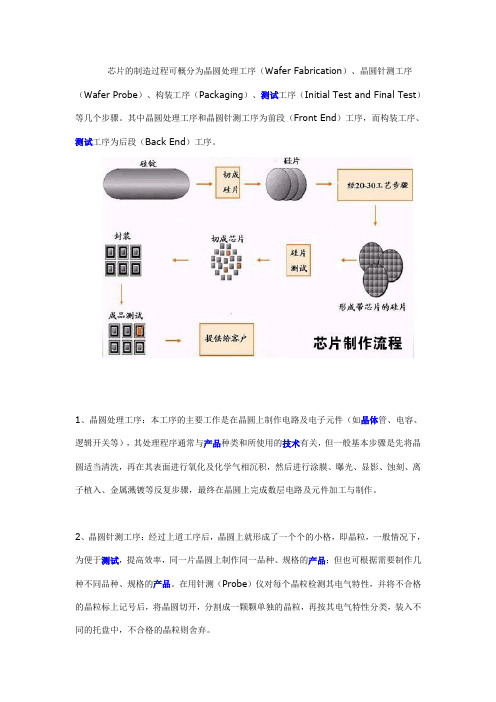

芯片的制造过程可概分为晶圆处理工序(Wafer Fabrication)、晶圆针测工序(Wafer Probe)、构装工序(Packaging)、测试工序(Initial Test and Final Test)等几个步骤。

其中晶圆处理工序和晶圆针测工序为前段(Front End)工序,而构装工序、测试工序为后段(Back End)工序。

1、晶圆处理工序:本工序的主要工作是在晶圆上制作电路及电子元件(如晶体管、电容、逻辑开关等),其处理程序通常与产品种类和所使用的技术有关,但一般基本步骤是先将晶圆适当清洗,再在其表面进行氧化及化学气相沉积,然后进行涂膜、曝光、显影、蚀刻、离子植入、金属溅镀等反复步骤,最终在晶圆上完成数层电路及元件加工与制作。

2、晶圆针测工序:经过上道工序后,晶圆上就形成了一个个的小格,即晶粒,一般情况下,为便于测试,提高效率,同一片晶圆上制作同一品种、规格的产品;但也可根据需要制作几种不同品种、规格的产品。

在用针测(Probe)仪对每个晶粒检测其电气特性,并将不合格的晶粒标上记号后,将晶圆切开,分割成一颗颗单独的晶粒,再按其电气特性分类,装入不同的托盘中,不合格的晶粒则舍弃。

3、构装工序:就是将单个的晶粒固定在塑胶或陶瓷制的芯片基座上,并把晶粒上蚀刻出的一些引接线端与基座底部伸出的插脚连接,以作为与外界电路板连接之用,最后盖上塑胶盖板,用胶水封死。

其目的是用以保护晶粒避免受到机械刮伤或高温破坏。

到此才算制成了一块集成电路芯片(即我们在电脑里可以看到的那些黑色或褐色,两边或四边带有许多插脚或引线的矩形小块)。

4、测试工序:芯片制造的最后一道工序为测试,其又可分为一般测试和特殊测试,前者是将封装后的芯片置于各种环境下测试其电气特性,如消耗功率、运行速度、耐压度等。

经测试后的芯片,依其电气特性划分为不同等级。

而特殊测试则是根据客户特殊需求的技术参数,从相近参数规格、品种中拿出部分芯片,做有针对性的专门测试,看是否能满足客户的特殊需求,以决定是否须为客户设计专用芯片。

很完整半导体制造工艺流程

半导体制造环境要求

主要污染源:微尘颗粒、中金属离子、有机物残留物和钠离子等轻金属例 子。

超净间:洁净等级主要由 微尘颗粒数/m3

I级 10 级 100级 1000级

0.1um 35 350 NA NA

HCl:H2O2:H2O

=1:1:5

溶液槽

除去表面颗粒

除去重金属粒 子

DI清洗

去离子水

溶液槽

除去清洗溶剂

光学显影

光学显影是在感光胶上经过曝光和显影的程序,把光罩上的图形转换到感光胶下 面的薄膜层或硅晶上。光学显影主要包含了感光胶涂布、烘烤、光罩对准、 曝光和显影等程序。

关键技术参数:最小可分辨图形尺寸Lmin(nm) 聚焦深度DOF

二、晶圆针测制程

经过Wafer Fab之制程後,晶圆上即形成一格格的小格 ,我们称之为晶方 或是晶粒(Die),在一般情形下,同一片晶圆上皆制作相同的晶片,但是 也有可能在同一片晶圆 上制作不同规格的产品;这些晶圆必须通过晶片允 收测试,晶粒将会一一经过针测(Probe)仪器以测试其电气特性, 而不 合格的的晶粒将会被标上记号(Ink Dot),此程序即 称之为晶圆针测制 程(Wafer Probe)。然後晶圆将依晶粒 为单位分割成一粒粒独立的晶粒

半导体制造工艺流程

半导体相关知识

本征材料:纯硅 9-10个9 250000Ω.cm

N型硅: 掺入V族元素--磷P、砷As、锑Sb P型硅: 掺入 III族元素—镓Ga、硼B PN结:

P

--

--

+++++

半导体制造工艺课件(PPT 98页)

消除损伤

退火方式:

炉退火

快速退火:脉冲激光法、扫描电子束、连续波激 光、非相干宽带频光源(如卤光灯、电弧灯、石墨 加热器、红外设备等)

氧化工艺

氧化:制备SiO2层 SiO2的性质及其作用 SiO2是一种十分理想的电绝缘材料,

去掉氮化硅层

P阱离子注入,注硼

推阱

去掉N阱区的氧化层 退火驱入

形成场隔离区

生长一层薄氧化层 淀积一层氮化硅

光刻场隔离区,非隔离区被 光刻胶保护起来

反应离子刻蚀氮化硅 场区离子注入 热生长厚的场氧化层 去掉氮化硅层

形成多晶硅栅

生长栅氧化层 淀积多晶硅 光刻多晶硅栅 刻蚀多晶硅栅

掺杂的均匀性好 温度低:小于600℃ 可以精确控制杂质分布 可以注入各种各样的元素 横向扩展比扩散要小得多。 可以对化合物半导体进行掺杂

离子注入系统的原理示意图

离子注入到无定形靶中的高斯分布情况

退火

退火:也叫热处理,集成电路工艺中所有的 在氮气等不活泼气氛中进行的热处理过程都 可以称为退火

Salicide工艺

淀积多晶硅、刻蚀 并形成侧壁氧化层;

淀积Ti或Co等难熔 金属

RTP并选择腐蚀侧 壁氧化层上的金属;

最后形成Salicide 结构

形成硅化物

淀积氧化层 反应离子刻蚀氧化层,形成侧壁氧化层 淀积难熔金属Ti或Co等 低温退火,形成C-47相的TiSi2或CoSi 去掉氧化层上的没有发生化学反应的Ti或Co 高温退火,形成低阻稳定的TiSi2或CoSi2

氧化层刻蚀掉,并去掉光刻胶 进行大剂量As+注入并退火,形成n+埋层

半导体工艺流程简介ppt

半导体工艺流程的成就与挑战

进一步缩小特征尺寸

三维集成技术

绿色制造技术

智能制造技术

未来半导体工艺流程的发展趋势

01

02

03

04

THANKS

感谢观看

互连

通过金属化过程,将半导体芯片上的电路元件连接起来,实现芯片间的通信和电源分配功能。

半导体金属化与互连

将半导体芯片和相关的电子元件、电路板等封装在一个保护壳内,以防止外界环境对芯片的损伤和干扰。

封装

对封装好的半导体进行功能和性能的检测与试验,以确保其符合设计要求和实际应用需要。

测试

半导体封装与测试

半导体工艺流程概述

02

半导体制造步骤-1

1

半导体材料的选择与准备

2

3

通常使用元素半导体,如硅(Si)、锗(Ge)等,或化合物半导体,如砷化镓(GaAs)、磷化铟(InP)等。

材料类型

高纯度材料对于半导体制造至关重要,杂质含量需要严格控制。

纯净度要求

材料应具有立方、六方或其他特定晶体结构。

晶格结构

蚀刻

使用化学试剂或物理方法,将半导体基板表面未被光刻胶保护的部分进行腐蚀去除。根据蚀刻方法的不同,可以分为湿蚀刻和干蚀刻两种。

去胶

在完成蚀刻后,使用去胶液等化学试剂,去除光刻胶。去胶过程中需要注意控制温度和时间,以避免对半导体基板造成损伤或污染。

半导体的蚀刻与去胶

05

半导体制造步骤-4

金属化

通常使用铝或铜作为主要材料,通过溅射、蒸发或电镀等手段,在半导体表面形成导线图案。

涂布

在半导体基板上涂覆光刻胶,使其覆盖整个基板表面。通常使用旋转涂布法,将光刻胶滴在基板中心,然后通过旋转基板将其展开并涂布在整个表面上。

半导体制造工艺流程课件

04

半导体制造的后处理

金属化

01

02

03

金属化

在半导体制造的后处理中 ,金属化是一个关键步骤 ,用于在芯片上形成导电 电路。

金属材料

通常使用铜、铝、金等金 属作为导电材料,通过物 理或化学沉积方法将金属 薄膜沉积在芯片表面。

连接电路

金属化过程将芯片上的不 同元件连接成完整的电路 ,实现电子信号的传输和 处理。

高纯度材料

半导体制造需要使用高纯度材料,以确保芯片的性能和可 靠性。然而,高纯度材料的制备和加工难度较大,需要克 服许多技术难题。

制程控制

半导体制造过程中,制程控制是至关重要的。制程控制涉 及温度、压力、流量、电流、电压等众多参数,需要精确 控制这些参数以确保芯片的性能和可靠性。

环境影响

能源消耗

半导体制造是一个高能耗的过程 ,需要大量的电力和能源。随着 半导体产业的发展,能源消耗也 在不断增加,对环境造成了很大 的压力。

废弃物处理

半导体制造过程中会产生大量的 废弃物,如化学废液、废气等。 这些废弃物如果处理不当,会对 环境造成很大的污染和危害。

碳排放

半导体制造过程中的碳排放也是 一个重要的问题。减少碳排放是 半导体产业可持续发展的关键之 一。

未来发展趋势

先进封装技术

随着摩尔定律的逐渐失效,先进封装技术成为半导体制造的重要发展方向。通过将多个 芯片集成在一个封装内,可以实现更小、更快、更低功耗的芯片系统。

沉积薄膜质量

影响沉积薄膜质量的因素包括反应温度、气体流量、压强等,需通 过实验优化获得最佳工艺参数。

外延生长

外延生长目的

在半导体材料表面外延生长一层单晶层,用 于扩展器件尺寸、改善材料性能和提高集成 度。

半导体铜线工艺流程

半导体铜线工艺流程半导体铜线工艺流程时刻:2010-09-03 剩余:0天扫瞄: 37 次收藏该信息一、铜线键合工艺A、铜线工艺对框架的专门要求-------铜线对框架的的要求要紧有以下几点:1、框架表面光滑,镀层良好;2、管脚共面性良好,不承诺有扭曲、翘曲等不良现象管脚粗糙和共面性差的框架拉力无法保证且容易显现翘丝和切线造成的烧球不良,压焊过程中容易断丝及显现tail t ooshort ;B、爱护气体----安装的时候保证E-torch上表面和right nozzle的下表面在同一个平面上.才能保证烧球的时候,氧化爱护良好.同时气嘴在可能的情形下尽量靠近劈刀,以保证气体最大范畴的爱护C、劈刀的选用——同金线相比较,铜线选用劈刀差不不是专门大,但依旧有一定的差异:1、铜线劈刀T 太小2nd容易切断,造成拉力不够或不平均2、铜线劈刀CD不能太大,也不能太小,不然容易显现不粘等现象3、铜线劈刀H与金线劈刀无太大区不(H比铜丝直径大8µm即可,太小容易从颈部拉断)4、铜线劈刀CA太小线弧颈部容易拉断,太大易造成线弧不平均;5、铜线劈刀FA选用一样要求8度以下(4-8度)6、铜线劈刀OR选用大同小异D压焊夹具的选用铜线产品对压焊夹具的选用要求专门严格,第一夹具制作材料要选用得当,同时夹具表面要光滑,要保证载体和管脚无松动要,否则将直截了当阻碍产品键合过程中烧球不良、断线、翘丝等一系列焊线咨询题。

二、铜线的特性及要求切实可行的金焊线替代产品。

细铜焊线(<1.3mil)铜焊线,机械、电气性质优异,适用于多种高端、微间距器件,引线数量更高、焊垫尺寸更小。

铜焊线(1.3-4mil)铜焊线,不仅具有铜焊线明显的成本优势,而且降低了铜焊点中的金属间生长速度,如此就为大功率分立封装带来了超一流的可靠性。

铜焊线的成本优势由于铜的成本相对较低,因此人们更情愿以铜作为替代连接材料。

关于1mil焊线,成本最高可降低75%*,2mil可达90%*,具体则取决于市场状况。

半导体制造工艺流程

01

02

• 集成多种制程技术:提高生

• 改进工艺参数:提高工艺性

产效率、降低生产成本

能、降低生产成本

• 优化工艺流程:简化工艺步

• 优化设备配置:提高设备利

骤、提高工艺稳定性

用率、降低设备维护成本

绿色制造与可持续发展

绿色制造:降低生产过程中的能耗、污染等

• 采用环保材料:降低生产过程中的环境污染

• 陶瓷:具有良好的热性能、抗冲击性能等优点

• 金属:具有良好的导热性能、电磁屏蔽性能等优点

测试工艺:测试方法与设备

测试方法:功能测试、参数测试、可靠性测试等

• 功能测试:检查器件是否正常工作

• 参数测试:测试器件的各项性能指标

• 可靠性测试:测试器件的寿命、稳定性等

测试设备:测试机、示波器、热阻仪等

• 抛光:提高晶圆表面的平整度和

• 扩散:将掺杂剂扩散到晶圆内部

所需尺寸的晶圆

光洁度

• 清洗:去除晶圆表面的污染物和

残留物

中道工艺:光刻与刻蚀

光刻工艺:通过光刻胶将图形转移到

晶圆表面的过程

刻蚀工艺:通过化学或

物理方法将晶圆表面的

图形转移到晶圆内部

光刻与刻蚀的工艺优化

与解决方案

• 光刻胶的涂覆:在晶圆表面涂覆

特点

前道工艺:晶圆制备与加工

晶圆制备:将半导体材料加工成晶圆

的过程

晶圆加工:对晶圆进行

表面处理、掺杂等工艺

掺杂工艺:通过扩散或

离子注入等方法改变晶

圆内部的杂质浓度

• 硅晶棒的生长:通过化学气相沉

• 研磨:去除晶圆表面的杂质和损

• 离子注入:将掺杂剂离子注入到

积等方法制备硅晶棒

半导体的生产工艺流程共14页word资料

半导体的生产工艺流程微机电制作技术,尤其是最大宗以硅半导体为基础的微细加工技术(silicon- based micromachining),原本就肇源于半导体组件的制程技术,所以必须先介绍清楚这类制程,以免沦于夏虫语冰的窘态。

一、洁净室一般的机械加工是不需要洁净室(clean room)的,因为加工分辨率在数十微米以上,远比日常环境的微尘颗粒为大。

但进入半导体组件或微细加工的世界,空间单位都是以微米计算,因此微尘颗粒沾附在制作半导体组件的晶圆上,便有可能影响到其上精密导线布局的样式,造成电性短路或断路的严重后果。

为此,所有半导体制程设备,都必须安置在隔绝粉尘进入的密闭空间中,这就是洁净室的来由。

洁净室的洁净等级,有一公认的标准,以class 10为例,意谓在单位立方英呎的洁净室空间内,平均只有粒径0.5微米以上的粉尘10粒。

所以class后头数字越小,洁净度越佳,当然其造价也越昂贵(参见图2-1)。

为营造洁净室的环境,有专业的建造厂家,及其相关的技术与使用管理办法如下:1、内部要保持大于一大气压的环境,以确保粉尘只出不进。

所以需要大型鼓风机,将经滤网的空气源源不绝地打入洁净室中。

2、为保持温度与湿度的恒定,大型空调设备须搭配于前述之鼓风加压系统中。

换言之,鼓风机加压多久,冷气空调也开多久。

3、所有气流方向均由上往下为主,尽量减少突兀之室内空间设计或机台摆放调配,使粉尘在洁净室内回旋停滞的机会与时间减至最低程度。

4、所有建材均以不易产生静电吸附的材质为主。

5、所有人事物进出,都必须经过空气吹浴 (air shower) 的程序,将表面粉尘先行去除。

6、人体及衣物的毛屑是一项主要粉尘来源,为此务必严格要求进出使用人员穿戴无尘衣,除了眼睛部位外,均需与外界隔绝接触 (在次微米制程技术的工厂内,工作人员几乎穿戴得像航天员一样。

) 当然,化妆是在禁绝之内,铅笔等也禁止使用。

7、除了空气外,水的使用也只能限用去离子水 (DI water, de-ionized water)。

半导体制造工艺流程图文

激光技术

激光技术在半导体制造中主要用于材料加工、表面处理和 检测等领域。

通过高能激光束对材料表面进行快速加热和冷却,可以实 现高精度和高效率的加工和表面处理。

激光技术在半导体制造中主要用于划片、打标和表面处理 等方面。

04 制造工艺中的设备与材料

通过控制反应气体和温度等参数,可以在硅片 上形成均匀、连续和高质量的薄膜。

常用的化学气相沉积技术包括热化学气相沉积、 等离子增强化学气相沉积和金属有机化学气相 沉积等。

物理气相沉积

物理气相沉积是一种利用物理过程在硅片上沉积薄膜 的方法。

通过控制气体流量和能量等参数,可以在硅片上形成 具有高附着力和致密性的薄膜。

光刻与刻蚀、离子注入和化学机械平坦化等步骤。

这些步骤的精确控制对于制造高性能、高可靠性的半导体器件

03

至关重要。

晶圆制备

01

02

03

晶圆制备是半导体制造 工艺的起始步骤,涉及 切割和研磨单晶硅锭, 以获得平滑、无缺陷的

晶圆表面。

晶圆制备过程中,需要 严格控制温度、压力和 化学试剂的浓度,以确 保晶圆的表面质量和几

03 制造工艺中的关键技术

真空技术

01

真空技术是半导体制造中不可或缺的关键技术之一,主要用 于制造薄膜和清洗表面。

02

在真空环境下,可以控制各种物理和化学过程,从而实现高 质量的薄膜沉积和表面处理。

03

常用的真空技术包括真空蒸发、溅射和化学气相沉积等。

化学气相沉积

化学气相沉积是半导体制造中常用的方法之一, 用于在硅片上沉积各种薄膜材料。

制造工艺设备

清洗设备

用于清除晶圆表面的杂质和污 染物,确保表面的洁净度。

半导体工艺流程简介

AL

P+ P-SUB

集成电路中电阻2

发射区扩散电阻

SiO2 P+ N+ N-epi N+-BL P-SUB R

R

P+

集成电路中电阻3

基区沟道电阻

SiO2 P+ P N+ R

R

N-epi

N+-BL P-SUB

P+

集成电路中电阻4

外延层电阻

SiO2 P+ N+ P N-epi P-SUB R

R

P+

第五次光刻—引线接触孔

•

SiO2 P N+

N+-BL

P+

P

N+-BL

N-epi P+ N-epi

P+

P-SUB

去SiO2—氧化--涂胶—烘烤---掩膜(曝光)---显影---坚膜 —蚀刻—清洗—去膜—清洗

第六次光刻—金属化内连线:反刻铝

•

AL

P P+ N+-BL

N-epiP+N-epi

P N+ P+ N+-BL

试谈半导体铜线工艺流程

试谈半导体铜线工艺流程首先,半导体铜线工艺流程的第一步是材料准备。

在这一步骤中,需要使用高纯度的铜材料,以确保制造出的铜线具有良好的导电性能和稳定的性能。

同时,还需要进行材料的预处理、清洗和表面处理,以确保铜材料的表面光滑和清洁,为后续的加工工艺做好准备。

接下来,是制备铜线的加工工艺。

在这一步骤中,首先需要将铜材料通过拉丝机进行拉丝加工,将铜材料拉制成所需直径的铜丝。

随后,需要进行铜丝的成型、切割和整形加工,以制备成所需规格和尺寸的铜线材料。

然后,是铜线的表面处理和包覆工艺。

在这一步骤中,需要对铜线进行表面涂层处理,以提高其抗氧化、耐腐蚀和焊接性能。

同时,还需要对铜线进行包覆加工,以保护其表面不受外界环境的影响,同时增强其连接性能和耐用性。

最后,是铜线的测试和检验工艺。

在这一步骤中,需要对制备好的铜线进行严格的测试和检验,以确保其性能和质量符合要求。

测试包括导电性能、抗拉强度、耐腐蚀性能等方面的检测,以确保铜线符合半导体器件的制造标准和要求。

综上所述,半导体铜线工艺流程是一个复杂而重要的半导体制造工艺,包括材料准备、加工工艺、表面处理和包覆、测试和检验等多个环节。

只有经过严格的工艺流程和质量监控,才能制备出高质量的半导体铜线,确保半导体器件的性能和可靠性。

半导体铜线工艺流程在半导体制造中扮演着至关重要的角色。

铜线是半导体器件中不可或缺的一部分,用于连接不同的元件和传输电信号。

为了确保半导体器件的性能和可靠性,铜线的制备必须经过严格的工艺流程和质量监控。

在进行半导体铜线工艺流程时,首先需要精心挑选适用的铜材料。

通常采用高纯度的铜材料,以确保铜线具有较低的电阻率和良好的导电性能。

在今天的半导体制造工艺中,通常使用电沉积铜(EDC)或铜箔作为主要的铜材料。

在选择和准备铜材料之后,需要进行表面处理,以确保其表面的平整度和纯净度。

这一步骤是至关重要的,因为表面的光滑度和清洁度直接影响着铜线的导电性能和成型质量。

试谈半导体铜线工艺流程

试谈半导体铜线工艺流程引言半导体技术在现代电子行业中扮演着重要的角色。

半导体器件中的金属线路是电子元件的重要组成部分,因此半导体铜线的工艺流程显得至关重要。

本文将介绍半导体铜线的工艺流程,包括准备工作、图案形成、电镀操作和最终的检测与包装等过程。

通过对这些工艺流程的详细分析,我们可以了解半导体铜线的制备过程、优化工艺条件以及提高半导体器件的性能。

一、准备工作在进行半导体铜线的制备之前,我们需要进行一系列的准备工作。

这些准备工作包括材料准备、设备准备和环境准备。

1.1 材料准备半导体铜线的制备需要一系列的材料,包括基片、铜膏、光刻胶和电镀液等。

基片是半导体器件的载体,通常采用硅基片。

铜膏是制备铜线的材料,可以通过混合铜粉和有机溶剂来制备。

光刻胶是用于形成铜线的图案,需要根据设计要求选择适当的光刻胶。

电镀液是将铜沉积在基片上的溶液,需要根据电镀工艺选择合适的电镀液。

1.2 设备准备制备半导体铜线需要一些专门的设备,包括光刻机、曝光机、洗涤机和电镀机等。

光刻机用于将光刻胶涂覆在基片上并形成图案,曝光机用于对光刻胶进行曝光,洗涤机用于洗去未曝光的光刻胶。

电镀机用于在基片上电镀铜。

1.3 环境准备在制备半导体铜线的过程中,需要保持一定的环境条件。

例如,在光刻工艺中,需要在无尘室的干燥环境下进行操作,以避免灰尘对图案形成的影响。

二、图案形成图案形成是制备半导体铜线的关键步骤。

这一步骤主要通过光刻技术来实现。

2.1 光刻胶涂覆首先,将选择好的光刻胶涂覆在基片上。

通过旋涂机将光刻胶均匀涂覆在基片表面,然后利用加热和旋转的方式将光刻胶均匀分布,形成光刻胶层。

2.2 曝光接下来,将光刻胶层暴露在特定的光源下,以形成所需的图案。

通过光刻机和曝光机,将光刻胶层进行曝光。

2.3 显影曝光之后,需要进行显影,以去除未曝光的光刻胶。

将基片放入洗涤机中,在显影液的作用下,未曝光的光刻胶将被洗掉,只剩下所需的图案。

2.4 退光刻胶经过显影之后,还需要进行退光刻胶的处理。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

⏹⏹半导体铜线工艺流程时间:2010-09-03 剩余:0天浏览: 37 次收藏该信息一、铜线键合工艺A、铜线工艺对框架的特殊要求-------铜线对框架的的要求主要有以下几点:1、框架表面光滑,镀层良好;2、管脚共面性良好,不允许有扭曲、翘曲等不良现象管脚粗糙和共面性差的框架拉力无法保证且容易出现翘丝和切线造成的烧球不良,压焊过程中容易断丝及出现tail tooshort ;B、保护气体----安装的时候保证E-torch上表面和right nozzle的下表面在同一个平面上.才能保证烧球的时候,氧化保护良好.同时气嘴在可能的情况下尽量靠近劈刀,以保证气体最大围的保护C、劈刀的选用——同金线相比较,铜线选用劈刀差别不是很大,但还是有一定的差异:1、铜线劈刀T 太小2nd容易切断,造成拉力不够或不均匀2、铜线劈刀CD不能太大,也不能太小,不然容易出现不粘等现象3、铜线劈刀H与金线劈刀无太大区别(H比铜丝直径大8µm即可,太小容易从颈部拉断)4、铜线劈刀CA太小线弧颈部容易拉断,太大易造成线弧不均匀;5、铜线劈刀FA选用一般要求8度以下(4-8度)6、铜线劈刀OR选用小异D压焊夹具的选用铜线产品对压焊夹具的选用要求非常严格,首先夹具制作材料要选用得当,同时夹具表面要光滑,要保证载体和管脚无松动要,否则将直接影响产品键合过程中烧球不良、断线、翘丝等一系列焊线问题。

二、铜线的特性及要求切实可行的金焊线替代产品。

细铜焊线(<1.3mil)铜焊线,机械、电气性质优异,适用于多种高端、微间距器件,引线数量更高、焊垫尺寸更小。

铜焊线(1.3-4mil)铜焊线,不仅具有铜焊线显著的成本优势,而且降低了铜焊点中的金属间生长速度,这样就为大功率分立封装带来了超一流的可靠性。

铜焊线的成本优势由于铜的成本相对较低,因此人们更愿意以铜作为替代连接材料。

对于1mil焊线,成本最高可降低75%*,2mil可达90%*,具体则取决于市场状况。

铜焊线的优异性能铜线的导热导电性能显著优于金线和铝线,因此能够以更细的焊线直径达到更好的散热性能及更高的额定功率。

与金相比,铜的机械性质更强,这样在模压和封闭过程中可以得到优异的球颈强度和较高的弧线稳铜焊线的优点(与金焊线相比)材料成本低 • 降低单位封装成本,提高竞争优势导电性好金焊线4.55 10 E7/ Ohm m铜焊线5.88 10 E7 / Ohm m • 在微间距封装中可以采用更细的焊线• 微间距应用性能优异(焊垫尺寸较小)• 提高功率调节器件(TO220、TO92、DPAK等等)的电流容量和性能导热性好金31.1 kW/m2 K铜39.5kW/m2 K • 传热效率更高机械性质高 • 抗拉强度更大、延伸特性更好• 模压中具有优异的球颈强度和较高的弧线稳定性金属间(IMC)生长速度慢 • 提高机械稳定性、降低电阻增加量• IMC生长较为温和,从而提高了键合强度降低金属间生长速度,提高可靠性与金线焊点相比,铜线焊点中的金属间生长速度显著减小。

这就降低了电阻、减小了产热,并最终提高了焊接可靠性和器件性能。

由于铜线中的金属间生长速度、电阻和产热均低于金线,故而电阻随时间的增加量和老化速度同时得到减小。

铜线在焊接后能够形成比金线更稳定、刚性更好的弧形能够适应更长的弧度(最长弧度7mm)铜焊线典型尺寸及标准机械规格直径 um 20 25 2830 38 50 65 75密耳 0.8 1.0 1.11.2 1.52.0 2.53.0延伸率(%) 8-16 8-16 10-20 10-20 10-20 15-25 15-2515-30断裂荷载(g) 5-10 8-15 10-20 12-22 20-30 40-55 60-8080-120铜焊线的包装与存放铜具有较强的亲氧性,因此必须对铜焊线进行保护以延长其保存期。

为此各卷铜焊线均采用吸塑包装,并在塑料袋单独密封除了以上优点为,铜线还有以下特性:1.铜线易氧化,原则上拆封的铜线48小时用完。

2.铜线硬度高,容易产生弹坑、不粘、断丝、、烧球不良三、铜线和金线在键合工艺参数的区别1.EG-60 铜线压焊工艺参数与金线相比较最大的变化是加大了contactforce,以增加产品的可焊性,为了减小弹坑风险,一般情况下1mil以下铜线采用LOW-Power模式,而1.2mil以上一般采用High-power模式Set up machine Set up machine(改为铜线方式) F16(2009) 1090ABBB bond sequence[normal(gold wire)->copper F16 Tail control (减少tail too short 报警) F16 1090ABB40 Menu 1 12-16 Menu 9 20 Menu A 8 F15 bond process control(减少 NSOP NSOL) F15 (2002)10803 Menu 0 比gold wire 要大一些 Menu 3 0 Menu 4 比bond force 稍小Set up machine Search high ( 减少 NSOP & tail too short) Gold wire : 8-12 copper wire : 10-15 EFO parameter Wire size (mil) 0.8 1.01.52.0 Current (mA) 5000-700012000-15000 time (us) 500-8001200-1800Set up machine BQM set up Wire size (mil) 0.8-1.21.5-2.0 Rise time 1-22-3 Power level lowhigh Power control const-pconst- p Speed set F15 比gold wire 稍低. 512-640 384-512Set up machine Set up machine To Copper Wire 1 Higher EFO current for Cu 2 Shorter EFO time for Cu 3 In general, higher force & power 4 Longer Time factor 5 Higher WC force due to Cu hardness 6 Less Contact Power, use force to deform theball during the contact stage then apply more base power Production issue Ball 球不良原因: 吹气保护不好 铜线后防止时间太长.线有氧化(72小时)  Tail length 不稳定导致烧球不好 Capillary 选择型号不对 Action: 调整吹气装置和E-TORCE位置,保证保护良好  更换铜线 调整2nd 焊接参数(base power and base force)保证taillength 稳定. 选用合适的capillaryProduction issue 1st NSOP 原因: Bond power 太小 Bond force 太大 Action: 在保证无crater 的前提下.调整power and forceProduction issue 2nd NSOL 原因: Bond power 太小或者太大 Bond force 太大或者太小 Action: 如果焊接后无留金痕迹应该调大 base power  如果焊接后有明显压断痕迹,应该调小 base power and forceProduction issue 2nd 后 tail too short 原因: 管脚位置浮动. Bond power 太小或者太大 Bond force 太大或者太小 Action: 调整该焊点位置 如果报警后可以直接从capillary 穿下线,应该是base power较小,应该调大base power 或者减小base force 如果报警后线不能直接穿下capillary,必须把线拔除再穿的话,应该减小base power或者增大base force.四、铜线对生产效率和产品质量的影响1、产能相对较低---铜线硬度要强于金线,压焊过程中断丝几率和不粘相对增大,考虑到可焊性等因素,压焊速度相对较慢,正常情况下设备利用率是金线设备的2/3左右。