STM32复位和时钟控制(RCC)

STM32L4复位和时钟控制(RCC)介绍

Clocks: PLL

• 3 PLLs

• Each with 3 independent outputs • PLLs input frequency must be between 4 and 16 MHz • PLL input can be MSI/HSI or HSE f(VCO clock) = (f(PLL clock input)/PLLM) × PLLN f(PLL_P) = f(VCO clock) / PLLP f(PLL_Q) = f(VCO clock) / PLLQ f(PLL_R) = f(VCO clock) / PLLR PLLM from 1 to 8 PLLN from 8 to 86 PLLP = 7 or 17 PLLQ = 2, 4, 6, 8 PLLR = 2, 4, 6, 8

100 kHz, 200 kHz, 400 kHz, 800 kHz, 1 MHz, 2 MHz, 4 MHz (reset value), 8 MHz, 16 MHz, 24 MHz, 32 MHz, 48 MHz.

89

• After Reset and Shutdown, MSI frequency is 4 MHz, selected by MSISRANGE in RCC_CSR register • After Standby: Frequency selected from 1, 2, 4 or 8 MHz with MSISRANGE in RCC_CSR register. • MSIRGSEL must be set in RCC_CR to switch to the frequency selected by MSIRANGE

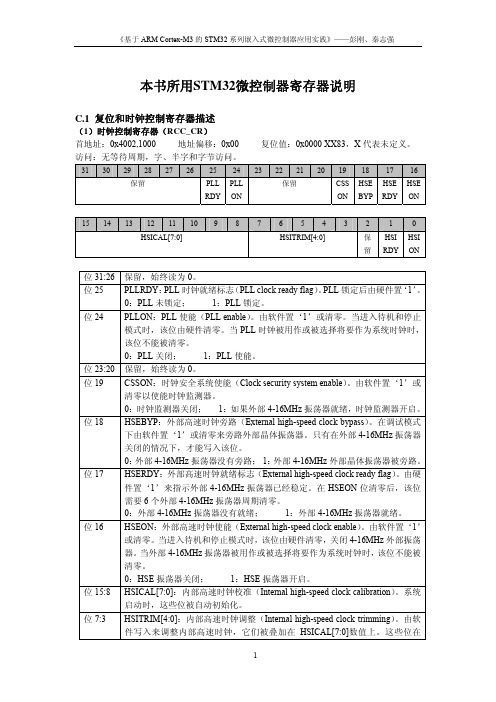

STM32微控制器寄存器说明

PLLXTPRE:HSE 分频器作为 PLL 输入(HSE divider for PLL entry)。由软件

置‘1’或清‘0’来分频 HSE 后作为 PLL 输入时钟。只能在关闭 PLL 时才能

写入此位。

0:HSE 不分频; 1:HSE 2 分频

PLLSRC:PLL 输入时钟源(PLL entry clock source)。由软件置‘1’或清‘0’

保 HSI HSI

留 RDY ON

位 31:26 位 25 位 24

位 23:20 位 19 位 18

位 17

位 16

位 15:8 位 7:3

保留,始终读为 0。 PLLRDY:PLL 时钟就绪标志(PLL clock ready flag)。PLL 锁定后由硬件置‘1’。 0:PLL 未锁定; 1:PLL 锁定。 PLLON:PLL 使能(PLL enable)。由软件置‘1’或清零。当进入待机和停止 模式时,该位由硬件清零。当 PLL 时钟被用作或被选择将要作为系统时钟时, 该位不能被清零。 0:PLL 关闭; 1:PLL 使能。 保留,始终读为 0。 CSSON:时钟安全系统使能(Clock security system enable)。由软件置‘1’或 清零以使能时钟监测器。 0:时钟监测器关闭; 1:如果外部 4-16MHz 振荡器就绪,时钟监测器开启。 HSEBYP:外部高速时钟旁路(External high-speed clock bypass)。在调试模式 下由软件置‘1’或清零来旁路外部晶体振荡器。只有在外部 4-16MHz 振荡器 关闭的情况下,才能写入该位。 0:外部 4-16MHz 振荡器没有旁路; 1:外部 4-16MHz 外部晶体振荡器被旁路。 HSERDY:外部高速时钟就绪标志(External high-speed clock ready flag)。由硬 件置‘1’来指示外部 4-16MHz 振荡器已经稳定。在 HSEON 位清零后,该位 需要 6 个外部 4-16MHz 振荡器周期清零。 0:外部 4-16MHz 振荡器没有就绪; 1:外部 4-16MHz 振荡器就绪。 HSEON:外部高速时钟使能(External high-speed clock enable)。由软件置‘1’ 或清零。当进入待机和停止模式时,该位由硬件清零,关闭 4-16MHz 外部振荡 器。当外部 4-16MHz 振荡器被用作或被选择将要作为系统时钟时,该位不能被 清零。 0:HSE 振荡器关闭; 1:HSE 振荡器开启。 HSICAL[7:0]:内部高速时钟校准(Internal high-speed clock calibration)。系统 启动时,这些位被自动初始化。 HSITRIM[4:0]:内部高速时钟调整(Internal high-speed clock trimming)。由软 件写入来调整内部高速时钟,它们被叠加在 HSICAL[7:0]数值上。这些位在

STM32F103的复位及时钟控制模块头文件

STM32F103的复位及时钟控制模块头文件在处理器正常工作前,肯定要做一些初始化工作,其中最主要的一个就是初始化各种时钟。

通过对STM32F103的复位及时钟控制(RCC)模块分析之后,自己写了一个RCC的头文件,这样使用起来更方便。

头文件中首先定义了最基本的几个寄存器,然后再对每个寄存器中的域使用结构体做了定义,可以直接使用寄存器中的位来操作。

注意设置系统时钟时要先设置好FLASH的等待周期,不然程序就可能会跑飞。

该测试工程是在以前的GPIO实验的基础上增加系统时钟初始化代码,设置系统时钟为72M。

通过流水灯可以看到,比未配置系统时钟之前(8M)流水灯的速度快了很多。

从这里下载完整的测试工程:系统时钟初始化的代码如下://以下时钟配置为最高性能void SystemClockInit(void){//设置flash等待周期为2,否则设置为72M系统时钟时就会跑飞FLASH_ACR=0x32;pbRCC_CR->HSEON=1; //使能外部高速时钟while(!(pbRCC_CR->HSERDY)); //等待外部高速时钟稳定pbRCC_CFGR->MCO=0; //MCO无时钟输出pbRCC_CFGR->USBPRE=1; //USB时钟1.5分频pbRCC_CFGR->PLLMUL=9-2; //PLL倍频设置为9倍(外部时钟8M,PLL输出72M)pbRCC_CFGR->PLLXTPRE=0; //HSE不分频pbRCC_CFGR->PLLSRC=1; //HSE选作做为PLL时钟源输入pbRCC_CFGR->ADCPRE=0; //ADC时钟2分频pbRCC_CFGR->PPRE2=1+6; //APB2设置为1分频pbRCC_CFGR->PPRE1=2+6; //APB1设置为2分频pbRCC_CFGR->HPRE=0; //AHB无分频pbRCC_CR->PLLON=1; //启动PLLwhile(!(pbRCC_CR->PLLRDY)); //等待PLL稳定pbRCC_CFGR->SW=2; //选择PLL输出为时钟源//pbRCC_AHBENR->SRAMEN=1;//pbRCC_AHBENR->FLITFEN=1;//IO口第二功能时钟使能pbRCC_APB2ENR->AFIOEN=1;//各通用IO口时钟使能pbRCC_APB2ENR->IOPAEN=1;pbRCC_APB2ENR->IOPBEN=1;pbRCC_APB2ENR->IOPCEN=1;pbRCC_APB2ENR->IOPDEN=1;pbRCC_APB2ENR->IOPEEN=1;//ADC时钟使能pbRCC_APB2ENR->ADC1EN=1;pbRCC_APB2ENR->ADC2EN=1;//定时器1时钟使能//SPI1时钟使能pbRCC_APB2ENR->SPI1EN=1;//串口1时钟使能pbRCC_APB2ENR->USART1EN=1;//定时器2、3、4时钟使能pbRCC_APB1ENR->TIM2EN=1; pbRCC_APB1ENR->TIM3EN=1; pbRCC_APB1ENR->TIM4EN=1;//窗口看门狗时钟不使能pbRCC_APB1ENR->WWDGEN=0;//SPI2时钟使能pbRCC_APB1ENR->SPI2EN=1;//串口2、3时钟使能pbRCC_APB1ENR->USART2EN=1; pbRCC_APB1ENR->USART3EN=1;//I2C1、2时钟使能pbRCC_APB1ENR->I2C2EN=1;//USB时钟使能pbRCC_APB1ENR->USBEN=1;//CAN时钟使能pbRCC_APB1ENR->CANEN=1;//备份接口时钟使能pbRCC_APB1ENR->BKPEN=1;//电源接口时钟使能pbRCC_APB1ENR->PWREN=1;//外部低速时钟启动pbRCC_BDCR->LSEON=1;pbRCC_BDCR->LSEBYP=0;pbRCC_BDCR->RTCSEL=1; //选择外部时钟为RTC时钟}STM32/STM8意法半导体/ST/STM。

STM32系统时钟RCC(基于HAL库)

STM32系统时钟RCC(基于HAL库)基础认识为什么要有时钟:时钟就是单⽚机的⼼脏,其每跳动⼀次,整个单⽚机的电路就会同步动作⼀次。

时钟的速率决定了两次动作的间隔时间。

速率越快,单⽚机在单位时间内所执⾏的动作将越多。

时钟是单⽚机运⾏的基础,时钟信号推动单⽚机内各个部分执⾏相应的指令。

时钟系统就是CPU的脉搏,决定cpu速率。

为什么这么多个时钟源:STM32系统是复杂的,⾼精度、低精度、⾼速、低速等,且可以对每个时钟源进⾏开关操作,可以把不需要使⽤的关闭掉。

这可以让单⽚机适⽤更多的环境中,把选择权利交个了开发者,开发者可以从精度、功耗、资源等多⽅⾯考虑。

STM32时钟:从时钟源的⾓度可分为:l 外部时钟(E)l 内部时钟(I)从时钟速率的⾓度分为:l ⾼速时钟(HS)l 低速时钟(LS)STM32在芯⽚复位后默认选⽤的是内部的⾼速时钟(HSI)进⾏⼯作,如果需要使⽤外部⾼速时钟(HSE)的话需要经过软件操作相关的寄存器配置。

外部时钟模式外部的⾼速和低速时钟均有这三个可选项⽬,图中是CubeMX提供的外部时钟选择:可选类型为l Disable(关闭,不使⽤外部时钟)l BYPASS Clock Source(旁路时钟源)l Crystal/Ceramic Resonator(外部晶体/陶瓷谐振器)外部晶体/陶瓷谐振器模式该模式较为常见,这可以为系统时钟提供较为精确的时钟源。

该时钟源是由外部⽆源晶体与MCU内部时钟驱动电路共同配合形成,有⼀定的启动时间,精度较⾼。

为了减少时钟输出的失真和缩短启动稳定时间,晶体/陶瓷谐振器和负载电容必须尽可能地靠近振荡器引脚。

负载电容值必须根据所选择的晶体来具体调整。

整体上讲,陶瓷晶体和⽯英晶体的主要区别就在于精度和温度稳定性上。

⽯英晶体⽐陶瓷晶体精度要⾼,温度稳定性要好。

旁路时钟源模式该模式下必须提供外部时钟。

外部时钟信号(50%占空⽐的⽅波、正弦波或三⾓波)必须连到SOC_IN引脚,此时OSC_OUT引脚对外呈⾼阻态。

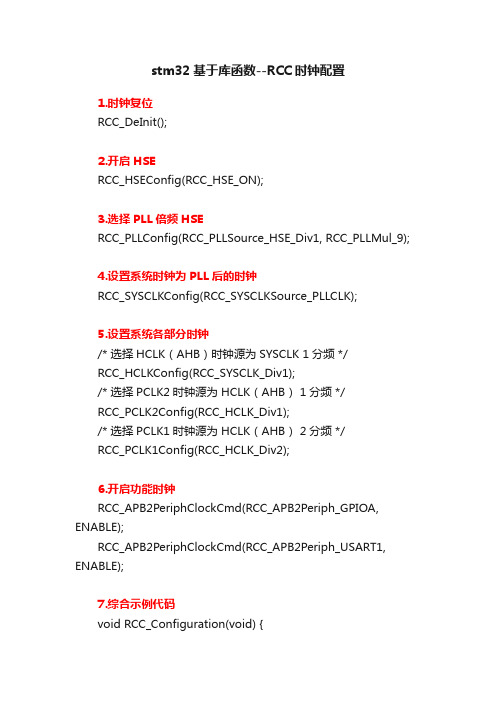

stm32基于库函数--RCC时钟配置

stm32基于库函数--RCC时钟配置1.时钟复位RCC_DeInit();2.开启HSERCC_HSEConfig(RCC_HSE_ON);3.选择PLL倍频HSERCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9);4.设置系统时钟为PLL后的时钟RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);5.设置系统各部分时钟/* 选择HCLK(AHB)时钟源为SYSCLK 1分频 */RCC_HCLKConfig(RCC_SYSCLK_Div1);/* 选择PCLK2时钟源为 HCLK(AHB) 1分频 */RCC_PCLK2Config(RCC_HCLK_Div1);/* 选择PCLK1时钟源为 HCLK(AHB) 2分频 */RCC_PCLK1Config(RCC_HCLK_Div2);6.开启功能时钟RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA, ENABLE);RCC_APB2PeriphClockCmd(RCC_APB2Periph_USART1, ENABLE);7.综合示例代码void RCC_Configuration(void) {/* 定义枚举类型变量 HSEStartUpStatus */ErrorStatus HSEStartUpStatus;/* 复位系统时钟设置*/RCC_DeInit();/* 开启HSE*/RCC_HSEConfig(RCC_HSE_ON);/* 等待HSE起振并稳定*/HSEStartUpStatus = RCC_WaitForHSEStartUp();/* 判断HSE起是否振成功,是则进入if()内部 */if(HSEStartUpStatus == SUCCESS) {/* 选择HCLK(AHB)时钟源为SYSCLK 1分频 */RCC_HCLKConfig(RCC_SYSCLK_Div1);/* 选择PCLK2时钟源为 HCLK(AHB) 1分频 */RCC_PCLK2Config(RCC_HCLK_Div1);/* 选择PCLK1时钟源为 HCLK(AHB) 2分频 */RCC_PCLK1Config(RCC_HCLK_Div2);/* 设置FLASH延时周期数为2 */FLASH_SetLatency(FLASH_Latency_2);/* 使能FLASH预取缓存 */FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable); /* 选择锁相环(PLL)时钟源为HSE 1分频,倍频数为9,则PLL输出频率为 8MHz * 9 = 72MHz */RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9);/* 使能PLL */RCC_PLLCmd(ENABLE);/* 等待PLL输出稳定 */while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET);/* 选择SYSCLK时钟源为PLL */RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);/* 等待PLL成为SYSCLK时钟源 */while(RCC_GetSYSCLKSource() != 0x08); }/* 打开APB2总线上的GPIOA时钟*/RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA|RCC_AP B2Periph_USART1, ENABLE);}2018-7-15 11:41:46 meetwit。

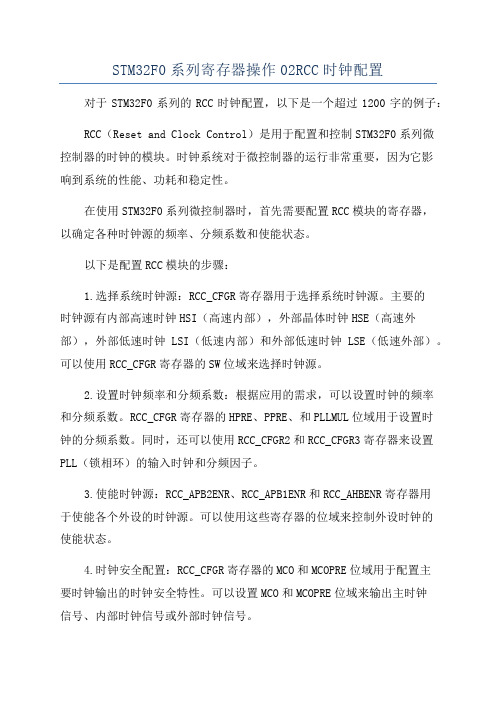

STM32F0系列寄存器操作02RCC时钟配置

STM32F0系列寄存器操作02RCC时钟配置对于STM32F0系列的RCC时钟配置,以下是一个超过1200字的例子:RCC(Reset and Clock Control)是用于配置和控制STM32F0系列微控制器的时钟的模块。

时钟系统对于微控制器的运行非常重要,因为它影响到系统的性能、功耗和稳定性。

在使用STM32F0系列微控制器时,首先需要配置RCC模块的寄存器,以确定各种时钟源的频率、分频系数和使能状态。

以下是配置RCC模块的步骤:1.选择系统时钟源:RCC_CFGR寄存器用于选择系统时钟源。

主要的时钟源有内部高速时钟HSI(高速内部),外部晶体时钟HSE(高速外部),外部低速时钟LSI(低速内部)和外部低速时钟LSE(低速外部)。

可以使用RCC_CFGR寄存器的SW位域来选择时钟源。

2.设置时钟频率和分频系数:根据应用的需求,可以设置时钟的频率和分频系数。

RCC_CFGR寄存器的HPRE、PPRE、和PLLMUL位域用于设置时钟的分频系数。

同时,还可以使用RCC_CFGR2和RCC_CFGR3寄存器来设置PLL(锁相环)的输入时钟和分频因子。

3.使能时钟源:RCC_APB2ENR、RCC_APB1ENR和RCC_AHBENR寄存器用于使能各个外设的时钟源。

可以使用这些寄存器的位域来控制外设时钟的使能状态。

4.时钟安全配置:RCC_CFGR寄存器的MCO和MCOPRE位域用于配置主要时钟输出的时钟安全特性。

可以设置MCO和MCOPRE位域来输出主时钟信号、内部时钟信号或外部时钟信号。

配置完毕后,需要等待时钟系统配置完成。

通过读取RCC_CFGR寄存器的SWS位域,可以确保时钟系统配置已经生效。

一旦配置完成后,系统将按照配置的时钟源和频率来运行。

在使用STM32F0系列微控制器时,正确配置RCC时钟是非常重要的。

这样可以确保系统的稳定性、性能和功耗都能达到预期的要求。

通过操作RCC模块的相关寄存器,可以实现对时钟源和频率的灵活配置,以满足不同应用的需求。

STM32 RCC复位时钟配置寄存器

RCCSTM32 的RCC看起来还是蛮复杂的,英文全称是Reset Clock Config,复位时钟配置,以下基本网上贴的,整理了一下,非原创哈。

一、时钟概述STM32有多个时钟源,分别是:HSI: 内部高速时钟(上电默认启动),因精度不高所以先不采用,以后如果需要再使用LSI:内部低速时钟,精度不高,一般用于IWDGCLKHSE:外部高速时钟,系统时钟一般采用它,经过PLL倍频作为系统同时钟LSE:外部低速时钟,一般专门用于RTC,等到RTC模块时再使用二、配置流程1.将RCC寄存器重新设置为默认值RCC_DeInit(default 默认)2.打开外部高速时钟晶振HSE RCC_HSEConfig(RCC_HSE_ON);3.等待外部高速时钟晶振工作HSEStartUpStatus = RCC_WaitForHSEStartUp();4.设置AHB时钟RCC_HCLKConfig;5.设置高速APB2时钟 RCC_PCLK2Config;6.设置低速速APB1时钟RCC_PCLK1Config7.设置PLL RCC_PLLConfig8.打开PLL RCC_PLLCmd(ENABLE);9.等待PLL工作while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET)10.设置系统时钟RCC_SYSCLKConfig11.判断是否PLL是系统时钟while(RCC_GetSYSCLKSource() != 0x08)至此系统时钟已经配置完成,STM32的每个模块都有自己的时钟,如果要使用某个模块,必须使能这个模块的时钟。

使能对应模块的时钟,STM32有个库函数,RCC_APB2PeriphClockCmd(对应模块,ENABLE)(72MHZ)或者RCC_APB1PeriphClockCmd(对应模块,ENABLE)(36MHZ);其中不同的模块有不同的时钟源,下面列举各个模块的时钟源:AHB2 时钟用于以下资源:(APB2:72MHZ)RCC_APB2Periph_AFIO 功能复用 IO 时钟RCC_APB2Periph_GPIOA GPIOA 时钟RCC_APB2Periph_GPIOB GPIOB 时钟RCC_APB2Periph_GPIOC GPIOC 时钟RCC_APB2Periph_GPIOD GPIOD 时钟RCC_APB2Periph_GPIOE GPIOE 时钟RCC_APB2Periph_ADC1 ADC1 时钟RCC_APB2Periph_ADC2 ADC2 时钟RCC_APB2Periph_TIM1 TIM1 时钟RCC_APB2Periph_SPI1 SPI1 时钟RCC_APB2Periph_USART1 USART1 时钟RCC_APB2Periph_ALL 全部 APB2外设时钟AHB1 时钟用于以下资源:(APB1:36MHZ)RCC_APB1Periph_TIM2 TIM2 时钟RCC_APB1Periph_TIM3 TIM3 时钟RCC_APB1Periph_TIM4 TIM4 时钟RCC_APB1Periph_WWDG WWDG时钟RCC_APB1Periph_SPI2 SPI2 时钟RCC_APB1Periph_USART2 USART2 时钟RCC_APB1Periph_USART3 USART3 时钟RCC_APB1Periph_I2C1 I2C1 时钟RCC_APB1Periph_I2C2 I2C2时钟RCC_APB1Periph_USB USB 时钟RCC_APB1Periph_CAN CAN时钟RTC 时钟来源:RCC_RTCCLKSource_LSE 选择 LSE 作为RTC 时钟RCC_RTCCLKSource_LSI 选择 LSI 作为RTC 时钟RCC_RTCCLKSource_HSE_Div128 选择 HSE 时钟频率除以 128 作为 RTC时钟ADC 时钟来源:该时钟源自 APB2 时钟(PCLK2)RCC_PCLK2_Div2 ADC 时钟= PCLK / 2RCC_PCLK2_Div4 ADC 时钟= PCLK / 4RCC_PCLK2_Div6 ADC 时钟= PCLK / 6RCC_PCLK2_Div8 ADC 时钟= PCLK / 8USB 时钟来源:该时钟来源于PLLCLK时钟的预分频三、RCC配置实例代码,与解析void RCC_Configuration(void){ErrorStatus HSEStartUpStatus;RCC_DeInit();//复位RCC模块的寄存器,复位成缺省值RCC_HSEConfig(RCC_HSE_ON);//开启HSE时钟,咱是用HSE的时钟作为PLL的时钟源HSEStartUpStatus = RCC_WaitForHSEStartUp();//获取HSE启动状态if(HSEStartUpStatus == SUCCESS) //如果HSE启动成功{FLASH_PrefetchBufferCmd(ENABLE);//开启FLASH的预取功能FLASH_SetLatency(FLASH_Latency_2);//FLASH延迟2个周期,RCC_HCLKConfig(RCC_SYSCLK_Div1);//配置HCLK,PCLK2,PCLK1,PLLRCC_PCLK2Config(RCC_HCLK_Div1);RCC_PCLK1Config(RCC_HCLK_Div2);RCC_PLLConfig(RCC_PLLSource_HSE_Div1,RCC_PLLMul_9);RCC_PLLCmd(ENABLE);//启动PLLwhile(RCC_GetFlagStatus(RCC_FLAG_PLLRDY)==RESET){}//等待PLL启动完成RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);//配置系统时钟while(RCC_GetSYSCLKSource() !=0x80)//检查是否将HSE 9倍频后作为系统时钟{}}}和STM32超频比较相关,Ourdev上有个超频的帖蛮有意思的有兴趣的可以看看,附上网址:/bbs/bbs_content_all.jsp?bbs_sn=3554410总之,STM32的时钟看起来比较复杂,但是可以不用去深究,使用STM32的库函数还是很好用的,虽然效率低了点,但是其实只使用很少的次数,无所谓了,要想STM32跑起来,按照上述配置就好了,千万不要忘记为使用的模块分配时钟,不要像我,跑个LED,忘记给IO分配时钟,还在纳闷呢,为什么不亮.(摘自网络).总结:我比这位原作者好点,我第一次让STM32跑两个灯一下就顺利了.就是第一次KEIL联不上STM32有点郁闷,在网上升级了,STLINK还是不行.后来得知,原来STLINK升级版本好几个了,找了新的版本总算跟4.12联上了.我的STLINK版本号J1STM32有五个时钟源:HSI、HSE、LSI、LSE、PLL1.1HSI:高速内部时钟、RC振荡器、频率为8MHz、时钟精度较差(上电默认启动),可作为备用时钟源(时钟安全系统CSS)。

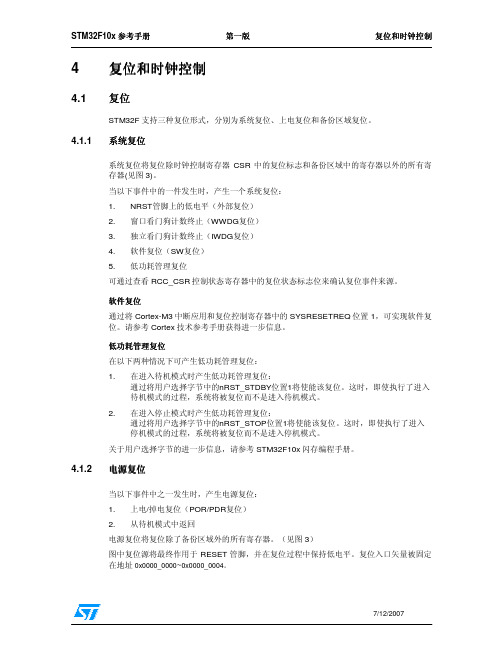

STM32技术参考手册第4章复位和时钟控制(上)

4 复位和时钟控制4.1 复位STM32F支持三种复位形式,分别为系统复位、上电复位和备份区域复位。

4.1.1 系统复位系统复位将复位除时钟控制寄存器CSR中的复位标志和备份区域中的寄存器以外的所有寄存器(见图3)。

当以下事件中的一件发生时,产生一个系统复位:1. NRST管脚上的低电平(外部复位)2. 窗口看门狗计数终止(WWDG复位)3. 独立看门狗计数终止(IWDG复位)4. 软件复位(SW复位)5. 低功耗管理复位可通过查看RCC_CSR控制状态寄存器中的复位状态标志位来确认复位事件来源。

软件复位通过将Cortex-M3中断应用和复位控制寄存器中的SYSRESETREQ位置1,可实现软件复位。

请参考Cortex技术参考手册获得进一步信息。

低功耗管理复位在以下两种情况下可产生低功耗管理复位:1. 在进入待机模式时产生低功耗管理复位:通过将用户选择字节中的nRST_STDBY位置1将使能该复位。

这时,即使执行了进入待机模式的过程,系统将被复位而不是进入待机模式。

2. 在进入停止模式时产生低功耗管理复位:通过将用户选择字节中的nRST_STOP位置1将使能该复位。

这时,即使执行了进入停机模式的过程,系统将被复位而不是进入停机模式。

关于用户选择字节的进一步信息,请参考STM32F10x闪存编程手册。

4.1.2 电源复位当以下事件中之一发生时,产生电源复位:1. 上电/掉电复位(POR/PDR复位)2. 从待机模式中返回电源复位将复位除了备份区域外的所有寄存器。

(见图3)图中复位源将最终作用于RESET管脚,并在复位过程中保持低电平。

复位入口矢量被固定在地址0x0000_0000~0x0000_0004。

图4-1.复位电路备份区域拥有两个专门的复位,它们只影响备份区域。

4.1.3 备份域复位当以下事件中之一发生时,产生备份区域复位。

1. 软件复位,备份区域复位可由设置备份区域控制寄存器RCC_BDCR中的BDRST位产生。

STM32固件与寄存器关系整理

常用图标:1:2:3:一.RCC模块:复位和时钟设置1.RCC寄存器结构RCC 寄存器结构,RCC_TypeDeff,在文件“stm32f10x_map.h”中定义如下:typedef struct{vu32 CR;vu32 CFGR;vu32 CIR;vu32 APB2RSTR;vu32 APB1RSTR;vu32 AHBENR;vu32 APB2ENR;vu32 APB1ENR;vu32 BDCR;vu32 CSR;} RCC_TypeDef;寄存器描述CR 时钟控制寄存器RCC_CR :HSI、HSE、PLL时钟使能以及就绪标志。

(默认HIS时钟使能)。

CFGR 时钟配置寄存器RCC_CFGR:系统时钟、PLL时钟切换,AHB、APB1、APB2、ADC、USB分频系数设置,PLL倍频系数设置CIR 时钟中断寄存器:HSI、HSE、LSI、LSE、PLL就绪中断使能和中断标志以其清除各就绪中断。

(默认HSI作为系统时钟,HSI时钟2分频后作为PLL输入时钟,)APB2RSTR APB2外设复位寄存器:APB2相连接的外设进行复位。

APB1RSTR APB1外设复位寄存器:APB1相连接的外设进行复位。

AHBENR AHB外设时钟使能寄存器:与AHB相连的DMA1时钟、DMA2时钟、SRAM 时钟(默认)、闪存接口电路时钟(默认)、CRC时钟、FSMC时钟、SDIO时钟使能。

APB2ENR APB2外设时钟使能寄存器:APB2相连接的外设时钟使能。

APB1ENR APB1外设时钟使能寄存器:APB1相连接的外设时钟使能。

BDCR 备份域控制寄存器:外部低速振荡器、RTC时钟使能和就绪标志以其旁路,RTC时钟源选择,备份域软件复位。

CSR 控制/状态寄存器:内部低速振荡器使能和就绪标志,各种复位标志和清除复位标志。

STM32嵌入式开发常见缩写

ARM:Advanced RISC MachineAAPCS:ARM Architecture Process call standard ARM体系结构过程调用标准DMA:Direct Memory Access 存储器直接访问EXTI: External Interrupts 外部中断FSMC: Flexible static memory controller 可变静态存储控制器FPB:flash patch and breakpoint FLASH 转换及断电单元HSE:Hign speed externalHSI: High speed internalLSE: Low Speed externalLSI: Low Speed InternalLSU: load store unit 存取单元PFU:prefetch unit 预取单元ISR:Interrupt Service Routines 中断服务程序NMI:Nonmaskable Interrupt 不可屏蔽中断NVIC: Nested Vectored Interrupt Controller 嵌套向量中断控制器MPU: Memory Protection Unit 内存保护单元MIPS:million instructions per second 每秒能执行的百万条指令的条数RCC:Reset and clock control 复位和时钟控制RTC: Real-Time Clock 实时时钟RISC:Reduced Instruction Set Computer 精简指令集计算机RTOS:Real Time Operating System 实时操作系统IWDG: independent watchdog 独立看门狗WWDG:Window watchdog 窗口看门狗TIM:timer 定时器TIM1:高級控制定時器GAL:generic array logic 通用阵列逻辑PAL:programmable array logic 可编程阵列逻辑ASIC:Application Specific Integrated Circuit 专用集成电路FPGA:Field-Programmable Gate Array 现场可编程门阵列CPLD:Complex Programmable Logic Device 可编程逻辑器件端口AFIO:alternate function IO 复用IO端口GPIO:general purpose input/output 通用IO端口IOP(A-G):IO port A - IO port G (例如:IOPA:IO port A)CAN:Controller area network 控制器局域网FLITF:The Flash memory interface 闪存存储器接口I2C:Inter-integrated circuit 微集成电路IIS:integrate interface of sound 集成音频接口JTAG:joint test action group 联合测试行动小组,調試接口SPI:Serial Peripheral Interface 串行外围设备接口SDIO: SD I/OUART: Universal Synchr./Asynch. Receiver Transmitter 通用异步接收/发送装置,串口USB: Universal Serial Bus 通用串行总线寄存器相关CPSP:Current Program Status Register 当前程序状态寄存器SPSP:saved program status register 程序状态备份寄存器CSR:clock control/status register 时钟控制状态寄存器LR:link register 链接寄存器SP:stack pointer 堆栈指针MSP: main stack pointer 主堆栈指针PSP:process stack pointer 进程堆栈指针PC:program counter 程序计数器调试相关ICE:in circuit emulator 在线仿真ICE: Breaker 嵌入式在线仿真单元DBG:debug 调试IDE:integrated development environment 集成开发环境DWT: data watchpoint and trace 数据观测与跟踪单元ITM: instrumentation trace macrocell 测量跟踪单元ETM:embedded trace macrocell 嵌入式追踪宏单元TPIU:trace port interface unit 跟踪端口接口单元TAP:test access port 测试访问端口DAP: debug access prot 调试访问端口TP: trace port 跟踪端口DP:debug port 调试端口SWJ-DP: serial wire JTAG debug port 串行-JTAG 调试接口SW-DP: serial wire debug port 串行调试接口JTAG-DP:JTAG debug port JTAG 调试接口系统类IRQ:interrupt request 中断请求FIQ:fast interrupt request 快速中断请求SW:software 软件SWI:software interrupt 软中断RO:read only 只读(部分)RW:read write 读写(部分)ZI:zero initial 零初始化(部分)BSS:Block Started by Symbol 以符号开始的块(未初始化数据段)总线Bus Matrix总线矩阵Bus Splitter 总线分割AHB-AP:advanced High-preformance Bus-access port APB:advanced peripheral busAPB1: low speed APB APB2: high speed APBPPB:Private Peripheral Bus 专用外设总线杂类ALU:Arithmetic Logical Unit 算术逻辑单元CLZ:count leading zero 前导零计数(指令)SIMD:single instruction stream multiple data stream单指令流,多数据流VFP:vector floating point 矢量浮点运算词汇/词组Big Endian 大端存储模式Little Endian 小端存储模式context switch 任务切换(上下文切换)(CPU 寄存器内容的切换)task switch 任务切换literal pool 数据缓冲池词汇类/单词arbitration 仲裁access 访问assembler 汇编器disassembly 反汇编binutils 连接器bit-banding 位段(技术)bit-band alias 位段别名bit-band region 位段区域banked 分组buffer 缓存/ceramic 陶瓷fetch 取指decode 译码execute 执行Harvard 哈佛(架构)handler 处理者heap 堆stack 栈latency 延时load (LDR) 加载(存储器内容加载到寄存器Rn)store (STR) 存储(寄存器Rn内容存储到存储器)Loader 装载器optimization 优化process 进程/过程thread 线程prescaler 预分频器prefetch 预读/预取指perform 执行pre-emption 抢占tail-chaining 尾链late-arriving 迟到resonator 共振器指令相关instructions 指令pseudo-instruction 伪指令directive 伪操作comments 注释FA full ascending 满栈递增(方式)EA empty ascending 空栈递增(方式)FD full desending 满栈递减(方式)ED empty desending 空栈递减(方式)。

STM32复位和时钟控制(RCC)

S T M32复位和时钟控制(R C C)-CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIAN复位STM32F10xxx支持三种复位形式,分别为系统复位、电源复位和备份区域复位。

1、系统复位系统复位将所有寄存器设置成复位值,除了RCC_CSR(控制状态寄存器)中的相关复位标志位,通过查看RCC_CSR寄存器,可以识别复位源。

系统复位可由以下5种方式产生:1)外部引脚NRST复位(低电平触发);2)窗口看门狗(WWDG)计数终止3)独立看门狗(IDOG)计数终止4)软件复位(SW RESET),通过将中断应用和复位控制寄存器( Application Interrupt and Reset Control Register )中SYSRESETREQ位置1。

具体参考Cortex-M3 programmingmanual。

5)低功耗管理复位:①通过进入等待模式(StandBy)产生复位:通过User Option Bytes中设置nRST_STDBY位使能这种复位模式。

这时,即使执行了进入待机模式的过程,系统将被复位而不是进入待机模式。

②通过进入停止模式(STOP)产生复位:通过User Option Bytes中设置nRST_STOP位使能这种复位模式。

这时,即使执行了进入停止模式的过程,系统将被复位而不是进入停止模式。

2、电源复位电源复位设置所有寄存器置初始值,除了备份区域。

电源复位可由以下2种方式产生:1)上电复位和掉电复位(POR/PDR reset)2)退出等待(StandBy)模式这些复位源都作用在NRST引脚上,并且在复位延迟期间保持低电平。

提供给设备的系统复位信号都由NRST引脚输出,对每一个内部/外部复位源,脉冲发生器都将保证一个20us最小复位周期。

对于外部复位,当NRST位置低时,将产生复位信号。

3、备份区复位备份区复位仅仅影响被分区域,有以下两种产生方式:1)软件复位,设置备份区域控制寄存器RCC_BDCR BDRST=1;2)在V DD和V BAT两者掉电的前提下,V DD或V BAT上电。

STM32电源、时钟及 复位电路

串行调试接口(SW-DP)为AHP-AP模块提供2针(时钟+数 据)接口。

SWJ调试端口脚表

JTAG连接实现图

启动配置

3.5调试接口

调试接口

硬件调试工具 JTAG或SWD连接器 调试线

SWJ调试端口(serial wire and JTAG)

STM32F10xxx内核集成了串行/JTAG调试接口(SWJDP)。

这是标准的ARM CoreSight调试接口,包括JTAGDP接口(5个引脚)和SW-DP接口(2个引脚)。

用户可以利用PVD对VDD电压与电源控制寄存器(PWR_CR)中的 PLS[2:0]位进行比较来监控电源。

通过设置PVDE位来使能PVD 电源控制/状态寄存器(PWR_CSR)中的PVDO标志用来表明VDD是 高于还是低于PVD的电压阀值。

该事件在内部连接到外部中断的第16线,如果该中断在外部 中断寄存器中是使能的,该事件就会产生中断。

3.1.2 电源管理器

1、上电复位(POR)和掉电复位(PDR) STM32内部有一个完整的上电复位(POR)和掉电复 位(PDR)电路,当供电电压达到2V时系统就能正常 工作。 当VDD/VDDA低于指定的限位电VPOR/VPDR时,系统 保持为复位状态,而无需外部复位电路。

2、可编程电压监测器(PVD)

NRST引脚上的低电平(外部复位) 窗口看门狗计数终止(WWDG复位) 独立看门狗计数终止(IWDG复位) 软件复位(SW复位) 低功耗管理复位

2、电源复位

电源复位

当以下事件中之一发生时,产生电源复位:

上电/掉电复位(POR/PDR复位) 从待机模式中返回

STM32RCC分析与使用

STM32RCC分析与使用STM32系列微控制器是意法半导体公司(STMicroelectronics)推出的一款32位嵌入式微控制器,广泛应用于各种各样的嵌入式应用中。

在STM32中,RCC(Reset and Clock Control)模块是用来控制系统复位和时钟的重要模块。

下面将对RCC模块进行分析与使用。

首先,RCC模块的主要功能是对系统时钟进行控制和配置。

在STM32中,系统时钟用于驱动处理器和外设,因此RCC模块的配置对整个系统的性能和功能都有着重要的影响。

RCC模块提供了多个时钟源和分频器来满足不同需求。

RCC模块主要包括以下功能:1.时钟源选择:RCC可以选择多个时钟源,包括内部和外部时钟源。

常见的时钟源包括内部高速时钟(HSI)、内部低速时钟(LSI)、外部高速时钟(HSE)和外部低速时钟(LSE)等。

通过选择不同的时钟源,可以满足不同的功耗和精度要求。

2.时钟分频:RCC模块提供了多个分频器,可以对系统时钟进行分频,以得到所需的时钟频率。

可以通过调整分频系数来满足不同的应用需求,例如减小系统时钟频率以降低功耗。

3.时钟输出:RCC模块还可以将系统时钟输出到特定的管脚,以供其他外设使用。

这对于一些需要同步时钟的应用非常有用。

在使用RCC模块时,一般需要进行以下几个步骤:1.使能对应的时钟源:根据实际需求选择合适的时钟源,并使能该时钟源。

对于外部时钟源,还需要设置相关的参数,如频率和稳定性。

2.配置时钟分频器:根据应用需求配置时钟分频器,以得到所需的时钟频率。

通常可以通过寄存器设置来完成。

3.选择系统时钟源:根据实际需求选择合适的系统时钟源。

一般可以选择内部高速时钟(HSI)、内部低速时钟(LSI)、外部高速时钟(HSE)或外部低速时钟(LSE)作为系统时钟源。

4.配置系统时钟分频器:根据应用需求配置系统时钟分频器,以得到所需的系统时钟频率。

通常可以通过寄存器设置来完成。

5.配置时钟输出:如果需要将系统时钟输出到特定的管脚,可以通过设置相应的寄存器来完成。

STM32F407-RCC配置

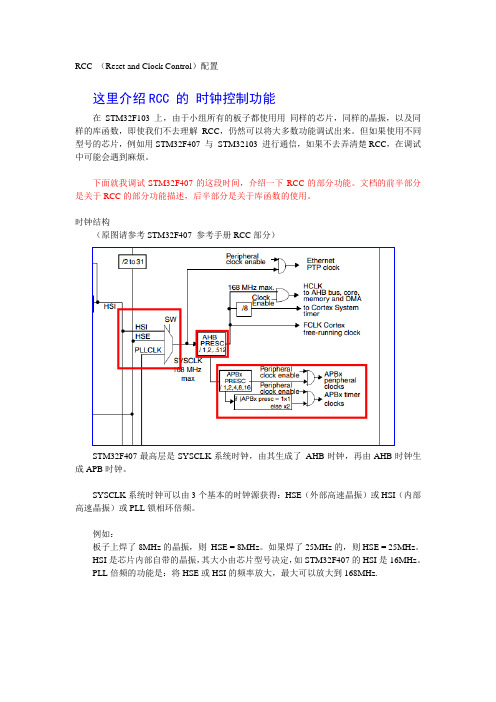

RCC (Reset and Clock Control)配置这里介绍RCC 的时钟控制功能在STM32F103上,由于小组所有的板子都使用用同样的芯片,同样的晶振,以及同样的库函数,即使我们不去理解RCC,仍然可以将大多数功能调试出来。

但如果使用不同型号的芯片,例如用STM32F407 与STM32103 进行通信,如果不去弄清楚RCC,在调试中可能会遇到麻烦。

下面就我调试STM32F407的这段时间,介绍一下RCC的部分功能。

文档的前半部分是关于RCC的部分功能描述,后半部分是关于库函数的使用。

时钟结构(原图请参考STM32F407 参考手册RCC部分)STM32F407最高层是SYSCLK系统时钟,由其生成了AHB时钟,再由AHB时钟生成APB时钟。

SYSCLK系统时钟可以由3个基本的时钟源获得:HSE(外部高速晶振)或HSI(内部高速晶振)或PLL锁相环倍频。

例如:板子上焊了8MHz的晶振,则HSE = 8MHz。

如果焊了25MHz的,则HSE = 25MHz。

HSI是芯片内部自带的晶振,其大小由芯片型号决定,如STM32F407的HSI是16MHz。

PLL倍频的功能是:将HSE或HSI的频率放大,最大可以放大到168MHz.SYSCLK系统时钟可以由HSE/HSI/PLL提供。

例如使用库函数:RCC_SYSCLKConfig( RCC_SYSCLKSource_HSE);代表用HSE外部高速晶振作为系统时钟源。

如果HSE =8MHz,则SYSCLK = 8M,即STM32F407就会运行在8M的速度;如果HSE=25M,则SYSCLK = 25M,即STM32F407就会运行在25M。

RCC_SYSCLKConfig( RCC_SYSCLKSource_HSI );代表用HSI内部高速晶振作为系统时钟源,如果HSI=16M,则SYSCLK=16M,即STM32F407 就会运行在16M的速度。

STM32F0系列寄存器操作02RCC时钟配置

STM32F0系列寄存器操作02RCC时钟配置RCC(Reset and Clock Control)模块是STM32F0系列微控制器中的一个重要模块,用于配置系统时钟。

在这里,我们将详细介绍如何通过寄存器操作来配置RCC模块。

RCC模块的寄存器位于设备的的地址空间中,通过写入特定的值来配置和控制系统时钟。

以下是与RCC模块相关的一些重要寄存器:1. RCC_CR(RCC Control Register):用于配置内部和外部时钟、使能外部时钟和使能内部时钟等。

2. RCC_CFGR(RCC Configuration Register):用于配置系统时钟源、时钟分频等。

3. RCC_AHBENR(RCC AHB Peripheral Clock Enable Register):用于使能或禁用AHB总线上的外设时钟。

4. RCC_APBENR(RCC APB Peripheral Clock Enable Register):用于使能或禁用APB总线上的外设时钟。

根据需求,我们可以按照以下步骤配置RCC模块:1.确定系统时钟源:使用RCC_CFGR寄存器来选择主时钟源,可以从内部时钟(HSI或HSI48)、外部时钟(HSE或HSE32)或PLL时钟中选择。

2.配置时钟分频:使用RCC_CFGR寄存器来设置HCLK、PCLK1和PCLK2的分频系数,以确定这些时钟频率。

3.使能外设时钟:使用RCC_AHBENR和RCC_APBENR寄存器来使能或禁用需要使用的外设时钟。

下面是一个示例代码,用于配置STM32F0系列微控制器的RCC模块:```c#include "stm32f0xx.h"void RCC_Config(void)//使能外部时钟RCC->CR,=RCC_CR_HSEON;//等待外部时钟稳定while(!(RCC->CR & RCC_CR_HSERDY));//配置PLL时钟RCC->CFGR,=RCC_CFGR_PLLSRC_HSE_PREDIV;RCC->CFGR,=RCC_CFGR_PLLMUL6;//使能PLL时钟RCC->CR,=RCC_CR_PLLON;//等待PLL时钟稳定while(!(RCC->CR & RCC_CR_PLLRDY));//配置系统时钟源为PLL时钟RCC->CFGR,=RCC_CFGR_SW_PLL;//等待系统时钟源切换完成while((RCC->CFGR & RCC_CFGR_SWS) != RCC_CFGR_SWS_PLL);//配置时钟分频RCC->CFGR,=RCC_CFGR_HPRE_DIV1;//AHB时钟不分频RCC->CFGR,=RCC_CFGR_PPRE_DIV2;//APB1时钟分频为2//使能外设时钟RCC->AHBENR,=RCC_AHBENR_GPIOAEN;RCC->APBENR,=RCC_APBENR_TIM2EN;```在这个示例中,首先使能外部时钟(HSE)并等待其稳定,然后配置PLL时钟和分频系数。

STM32F2系列之复位和时钟控制RCC详解

TIMxCLK TIM2..7,12..14

PCLK2 up to 60MHz VCO /P PLL48CLK (USB FS, SDIO & RNG) /Q xN /R APB2 Prescaler /1,2,4,8,16

If (APB2 pres =1)

x1

Else

x2

TIMxCLK TIM1,8..11

PLL

VCO

/P

HSI HSE MCO1 /1..5 PLLCLK LSE

/Q

Ext. Clock SPI2S_CKI N I2SCLK PLLI2SCLK MACTXCLK MACRXCLK MACRMIICL K

xN

/R

PLLI2S

USB HS ULPI clock

SYSCLK

MCO2 /1..5 PLLCLK / 2, 20 HSE

TIMxCLK TIM2..7,12..14

PCLK2 up to 60MHz VCO /P PLL48CLK (USB FS, SDIO & RNG) /Q xN /R APB2 Prescaler /1,2,4,8,16

If (APB2 pres =1)

x1

Else

x2

TIMxCLK TIM1,8..11

HSI RC 4 -26 MHz OSC_OUT OSC_IN

16MHz HSI

/M HSE PLLCLK

HSE Osc

SYSCLK AHB Prescaler 120 MHz max

/1,2…512

APB1 Prescaler /1,2,4,8,16

If (APB1 pres =1) Else

x1 x2

TB复位和时钟控制介绍(RCC)

TB复位和时钟控制介绍(RCC)STM32 RCC分析与使用由于STM32 系列微控制器系统比较复杂,时钟系统也相对于普通MCU 更多样化,这加大了我们设计程序和学习的难度.比如普通的MCU延时程序,我们直接可以使用“for 循环”或者“while”来轻易实现;而在Cortex 核的STM32 系列微控制器上则不行:因为无法判断当时的时钟频率,做不到精确的延时.如果详细地了解其时钟系统后,我们知道可以使用SYSCLK 来实现精确延时.RCC的学习可以说没有实验,但所有的模块都会用到时钟,我们进行I/O口的初始化,配置函数中第一行代码一般都是对时钟的初始化,足可见其重要性.一般而言,要是真正理解了STM32中所有的时钟,学习其他外设都是易如反掌了.[编辑] 实验要求深入理解STM32系统时钟和复位控制.[编辑] 实验目的学习STM32系列的时钟.[编辑] 硬件分析[编辑] 时钟树.在STM32 系统中,共有五个时钟源,分别为HSE、HSI、LSE、LSI、PLL.由图可以看出,HSI 和LSI 为片内RC 振荡器,HSI 为8MHz 而LSI 为32KHz;HSE 和LSE 为外部时钟源;PLL 则需要HSE 和HSI 来提供时钟.(1)HSE:高速外部时钟信号可以通过外部直接提供时钟,从OSC_IN 输入,或使用外部陶瓷/晶体谐振器.外部直接提供的时钟可以达到25MHz,用户可以通过设置时钟信号控制寄存器RCC_CR 中的HSEBYP 和HSEON 位来选择该模式.此时OSC_OUT 引脚为高阻状态.(2)HSI:高速内部时钟信号该时钟通过8MHz 的内部RC 振荡器产生,并且可被直接用做系统时钟,或者经过2 分频后作为PLL 的输入.它比HSE 有更快的启动时间,但频率精确度没有外部晶体振荡器高.而且根据制造工艺的不同,不同芯片之间的RC 振荡器频率也是不同.出厂时,每个设备频率已被校准至1%(25 摄氏度).出厂校验值被装载到时钟控制寄存器RCC_CR 的HSICAL [7:0] 位.在不同的电压或者温度下,可以通过RCC_CR 中的HSITRIM[4:0]位来调整HSI 的频率.并可以通过时钟控制寄存器RCC_CR 的HISON 位打开或者禁用.(3) LSE:低速外部时钟信号振荡器是一个32.768KHz 的低速外部晶体/陶瓷振荡器,它可以向RTC 提供高精准时钟.LSI:低速内部时钟信号振荡频率为32KHz 左右(30-60KHz 之间).(5)PLL:锁相环倍频输出其时钟输入源可选择为HSI/2、HSE 或者HSE/2.倍频可选择为2~16 倍,但是其输出频率最大不得超过72MHz.系统时钟(SYSCLK)系统时钟SYSCLK 是供STM32 中绝大部分部件工作的时钟源.系统时钟可选择为PLL 输出、HSI 或者HSE.HSI 与HSE 可以通过分频加至PLLSRC,并由PLLMUL 进行倍频后经选择直接充当SYSCLK.PLLCLK 经1.5 分频或1 分频后为USB 串行接口引擎提供一个48MHz 的振荡频率.即当需要使用USB 时,PLL 必须使能,并且时钟频率配置为48MHz 或者72MHz.但这并不意味着USB 模块工作时需要48MHz,48MHz 仅提供给USB 串行接口引擎(SIE),而USB 模块工作是由APBH1 提供的.系统时钟最大频率为72MHz,它通过AHB 分频器分频后送给各模块使用,AHB 分频器可选择1、2、4、8、16、64、128、256、512 分频.AHB 分频器输出的时钟送给5 大模块使用:(1)送给AHB 总线、内核、内存和DMA 使用的HCLK 时钟.(2)通过8 分频后送给Cortex 的系统定时器时钟.(3)直接送给Cortex 的空闲运行时钟FCLK.(4)送给APB1 分频器.APB1 分频器可选择为1、2、4、8、16 分频,其输出中一路供APB1 外设使用(PCLK1,最大频率36MHz);另一路送给定时器(Timer)2、3、4 的倍频器使用(TIMXCLK),该倍频器可选择1或者2 倍频,输出供定时器2、3、4 使用.(5)送给APB2 分频器.APB2 分频器可供选择为1、2、4、8、16 分频,其输出一路供APB2 外设使用(PCLK2,最大频率72MHz);一路送给定时器(Timer)1 的倍频器使用(TIM1CLK),该倍频器可选择1 或者2 倍频,输出供定时器1 使用;另外,APB2 分频器还有一路输出供ADC 分频器使用,分频后送给ADC 模块使用,ADC 分频器可选择为2、4、6、8 分频.时钟安全系统(CSS)图中在SYSCLK 选择端下方有个CSS 模块,CSS 是一个时钟安全系统,用来保证系统时钟在HSE 失效时能继续工作.时钟检测器在HSE 振荡器启动延时后被使能,并当振荡器停止时禁用.如果在HSE振荡器时钟上检测到一个失效,这个振荡器将被自动禁用;一个时钟失效事件打断TIM1 高级控制定时器的输入,并且产生一个中断来通知软件该次失效,使得MCU 能够进行补救措施.系统时钟输出(MCO)图的左下方为系统时钟输出(MCO)模块.使得时钟能够输出到外部MCO 引脚,相关的GPIO 端口的配置寄存器必须被编程为复用功能模式.下面4 个时钟的任意一个可被选作MCO 时钟:(1)SYSCLK(2)HIS(3)HSE(4)2 分频的PLLCLK可通过时钟配置寄存器RCC_CFGR 的MCO[2:0]位进行选择.几点说明:(1)在以上的时钟输出中,有很多是带使能控制端的(如图中的Peripheral Clock Enable),例如AHB 总线时钟、内核时钟、各种APB1外设、APB2 外设等等.当需要使用某模块时,记得一定要先使能对应的时钟.(2)需要注意的是定时器的倍频器,当APB 的分频为1 时,它的倍频值为1,否则它的倍频值就为2.(3)连接在APB1(低速外设)上的设备有:电源接口、备份接口、CAN、USB、I2C1、I2C2、UART2、UART3、SPI2、窗口看门狗、Timer2、Timer3、Timer4.(4)连接在APB2( 高速外设)上的设备有:UART1、SPI1、Timer1、ADC1、ADC2、所有普通IO 口(PA~PE)、第二功能IO 口.(5)如果独立的看门狗(IWDG)被硬件选项或者软件访问启动了,LSI 振荡器将被强制打开,并且不能被禁用,在LSI 振荡器开始工作后,它的时钟被提供给IWDG.[编辑] 复位STM32F10xxx支持三种复位形式,分别为系统复位、上电复位和备份区域复位.[编辑] 系统复位除了时钟控制器的RCC_CSR寄存器中的复位标志位和备份区域中的寄存器(见上图)以外,系统复位将复位所有寄存器至它们的复位状态.当发生以下任一事件时,产生一个系统复位:1. NRST引脚上的低电平(外部复位)2. 窗口看门狗计数终止(WWDG复位)3. 独立看门狗计数终止(IWDG复位)4. 软件复位(SW复位)5. 低功耗管理复位可通过查看RCC_CSR控制状态寄存器中的复位状态标志位识别复位事件来源.[编辑] 软件复位通过将Cortex?M3中断应用和复位控制寄存器中的SYSRESETREQ位置’1’,可实现软件复位.请参考Cortex?M3技术参考手册获得进一步信息.[编辑] 低功耗管理复位在以下两种情况下可产生低功耗管理复位:在进入待机模式时产生低功耗管理复位:通过将用户选择字节中的nRST_STDBY位置’1’将使能该复位.这时,即使执行了进入待机模式的过程,系统将被复位而不是进入待机模式.在进入停止模式时产生低功耗管理复位:通过将用户选择字节中的nRST_STOP位置’1’将使能该复位.这时,即使执行了进入停机模式的过程,系统将被复位而不是进入停机模式.[编辑] 电源复位当以下事件中之一发生时,产生电源复位:上电/掉电复位(POR/PDR复位)从待机模式中返回电源复位将复位除了备份区域外的所有寄存器.复位电路如下所示:..图中复位源将最终作用于RESET引脚,并在复位过程中保持低电平.复位入口矢量被固定在地址0x0000_0004.芯片内部的复位信号会在NRST引脚上输出,脉冲发生器保证每一个(外部或内部)复位源都能有至少20μs的脉冲延时;当NRST引脚被拉低产生外部复位时,它将产生复位脉冲.[编辑] 时钟详细分析三种不同的时钟源可被用来驱动系统时钟(SYSCLK):● HSI振荡器时钟● HSE振荡器时钟● PLL时钟这些设备有以下2种二级时钟源:● 40kHz低速内部RC,可以用于驱动独立看门狗和通过程序选择驱动RTC.RTC用于从停机/待机模式下自动唤醒系统.● 32.768kHz低速外部晶体也可用来通过程序选择驱动RTC(RTCCLK).当不被使用时,任一个时钟源都可被独立地启动或关闭,由此优化系统功耗.[编辑] HSE时钟高速外部时钟信号(HSE)由以下两种时钟源产生:● HSE外部晶体/陶瓷谐振器● HSE用户外部时钟为了减少时钟输出的失真和缩短启动稳定时间,晶体/陶瓷谐振器和负载电容器必须尽可能地靠近振荡器引脚.负载电容值必须根据所选择的振荡器来调整..上图为外部时钟源的硬件配置在外部时钟源(HSE旁路)这个模式下,必须提供外部时钟.它的频率最高可达25MHz.用户可通过设置在时钟控制寄存器中的HSEBYP和HSEON位来选择这一模式.外部时钟信号(50%占空比的方波、正弦波或三角波)必须连到SOC_IN引脚,同时保证OSC_OUT引脚悬空.具体见上图.上图为晶体/陶瓷谐振器的硬件配置在外部晶体/陶瓷谐振器(HSE晶体)这个模式下 4~16Mz外部振荡器可为系统提供更为精确的主时钟.相关的硬件配置可参考上图,进一步信息可参考数据手册的电气特性部分.在时钟控制寄存器RCC_CR中的HSERDY位用来指示高速外部振荡器是否稳定.在启动时,直到这一位被硬件置’1’,时钟才被释放出来.如果在时钟中断寄存器RCC_CIR中允许产生中断,将会产生相应中断.HSE晶体可以通过设置时钟控制寄存器里RCC_CR中的HSEON 位被启动和关闭.[编辑] HSI时钟HSI时钟信号由内部8MHz的RC振荡器产生,可直接作为系统时钟或在2分频后作为PLL输入.HSI RC振荡器能够在不需要任何外部器件的条件下提供系统时钟.它的启动时间比HSE晶体振荡器短.然而,即使在校准之后它的时钟频率精度仍较差.校准制造工艺决定了不同芯片的RC振荡器频率会不同,这就是为什么每个芯片的HSI时钟频率在出厂前已经被ST校准到1%(25°C)的原因.系统复位时,工厂校准值被装载到时钟控制寄存器的HSICAL[7:0]位.如果用户的应用基于不同的电压或环境温度,这将会影响RC振荡器的精度.可以通过时钟控制寄存器里的HSITRIM[4:0]位来调整HSI频率.时钟控制寄存器中的HSIRDY位用来指示HSI RC振荡器是否稳定.在时钟启动过程中,直到这一位被硬件置’1’,HSI RC输出时钟才被释放.HSI RC可由时钟控制寄存器中的HSION位来启动和关闭.如果HSE晶体振荡器失效,HSI时钟会被作为备用时钟源.[编辑] PLL内部PLL可以用来倍频HSI RC的输出时钟或HSE晶体输出时钟.参考时钟树图和时钟控制寄存器.PLL的设置(选择HIS振荡器除2或HSE振荡器为PLL的输入时钟,和选择倍频因子)必须在其被激活前完成.一旦PLL被激活,这些参数就不能被改动.如果PLL中断在时钟中断寄存器里被允许,当PLL准备就绪时,可产生中断申请.如果需要在应用中使用USB接口,PLL必须被设置为输出48或72MHZ时钟,用于提供48MHz的USBCLK时钟.[编辑] LSE时钟LSE晶体是一个32.768kHz的低速外部晶体或陶瓷谐振器.它为实时时钟或者其他定时功能提供一个低功耗且精确的时钟源.LSE晶体通过在备份域控制寄存器(RCC_BDCR)里的LSEON位启动和关闭.在备份域控制寄存器(RCC_BDCR)里的LSERDY指示LSE晶体振荡是否稳定.在启动阶段,直到这个位被硬件置’1’后,LSE时钟信号才被释放出来.如果在时钟中断寄存器里被允许,可产生中断申请.外部时钟源(LSE旁路) 在这个模式里必须提供一个32.768kHz频率的外部时钟源.你可以通过设置在备份域控制寄存器(RCC_BDCR)里的LSEBYP和LSEON位来选择这个模式.具有50%占空比的外部时钟信号(方波、正弦波或三角波)必须连到OSC32_IN引脚,同时保证OSC32_OUT引脚悬空.[编辑] LSI时钟LSI RC担当一个低功耗时钟源的角色,它可以在停机和待机模式下保持运行,为独立看门狗和自动唤醒单元提供时钟.LSI时钟频率大约40kHz(在30kHz和60kHz之间).进一步信息请参考数据手册中有关电气特性部分.LSI RC可以通过控制/状态寄存器(RCC_CSR)里的LSION位来启动或关闭.在控制/状态寄存器(RCC_CSR)里的LSIRDY位指示低速内部振荡器是否稳定.在启动阶段,直到这个位被硬件设置为’1’后,此时钟才被释放.如果在时钟中断寄存器(RCC_CIR)里被允许,将产生LSI中断申请.LSI校准可以通过校准内部低速振荡器LSI来补偿其频率偏移,从而获得精度可接受的RTC时间基数,以及独立看门狗(IWDG)的超时时间(当这些外设以LSI为时钟源).校准可以通过使用TIM5的输入时钟(TIM5_CLK)测量LSI时钟频率实现.测量以HSE的精度为保证,软件可以通过调整RTC的20位预分频器来获得精确的RTC时钟基数,以及通过计算得到精确的独立看门狗(IWDG)的超时时间.LSI校准步骤如下:打开TIM5,设置通道4为输入捕获模式;设置AFIO_MAPR的TIM5_CH4_IREMAP位为’1’,在内部把LSI连接到TIM5的通道4;通过TIM5的捕获/比较4事件或者中断来测量LSI时钟频率;根据测量结果和期望的RTC时间基数和独立看门狗的超时时间,设置20位预分频器.系统时钟(SYSCLK)选择系统复位后,HSI振荡器被选为系统时钟.当时钟源被直接或通过PLL间接作为系统时钟时,它将不能被停止.只有当目标时钟源准备就绪了(经过启动稳定阶段的延迟或PLL稳定),从一个时钟源到另一个时钟源的切换才会发生.在被选择时钟源没有就绪时,系统时钟的切换不会发生.直至目标时钟源就绪,才发生切换.在时钟控制寄存器(RCC_CR)里的状态位指示哪个时钟已经准备好了,哪个时钟目前被用作系统时钟.[编辑] 时钟安全系统(CSS)在实际应用中,经常出现由于晶体振荡器在运行中失去作用,造成微处理器的时钟源丢失,从而出现死机的现象,导致系统出错.严重时,由于系统的死机造成监控失效,导致无法挽回的损失!STM32作为一个可靠稳定的微处理器,但是不能排除由于某些外界特殊因素可能造成STM32的外部振荡器失效,STM32内部的时钟安全系统(CCS)正是为解决出现这种问题而设计的.一旦外部晶体振荡器(HSE)失效,CCS系统将STM32的系统时钟源切换到一个稳定的时钟源,以保证STM32能够继续运行,并进行相应的保护操作..时钟安全系统可以通过软件被激活.一旦其被激活,时钟监测器将在HSE振荡器启动延迟后被使能,并在HSE时钟关闭后关闭.如果HSE时钟发生故障,HSE振荡器被自动关闭,时钟失效事件将被送到高级定时器(TIM1和TIM8)的刹车输入端,并产生时钟安全中断CSSI,允许软件完成营救操作.此CSSI中断连接到Cortex?M3的NMI中断(不可屏蔽中断).注意:一旦CSS被激活,并且HSE时钟出现故障,CSS中断就产生,并且NMI也自动产生.NMI将被不断执行,直到CSS中断挂起位被清除.因此,在NMI的处理程序中必须通过设置时钟中断寄存器(RCC_CIR)里的CSSC位来清除CSS中断.如果HSE振荡器被直接或间接地作为系统时钟,(间接的意思是:它被作为PLL输入时钟,并且PLL时钟被作为系统时钟),时钟故障将导致系统时钟自动切换到HSI振荡器,同时外部HSE振荡器被关闭.在时钟失效时,如果HSE振荡器时钟(被分频或未被分频)是用作系统时钟的PLL的输入时钟,PLL也将被关闭.应用举例启动时钟安全系统CSS:RCC_ClockSecuritySystemCmd(ENABLE);//NMI中断是不可屏蔽的!//外部振荡器实现时,产生中断,对应的中断程序:void NMIException(void){if (RCC_GetITStatus(RCC_IT_CSS) != RESET){ // HSE、PLL已被禁止(但是PLL设置未变)… … // 客户添加相应的系统保护代码处// 下面为HSE恢复后的预设置代码RCC_HSEConfig(RCC_HSE_ON); // 使能HSERCC_ITConfig(RCC_IT_HSERDY, ENABLE); // 使能HSE就绪中断RCC_ITConfig(RCC_IT_PLLRDY, ENABLE); // 使能PLL就绪中断RCC_ClearITPendingBit(RCC_IT_CSS); // 清除时钟安全系统中断的挂起位// 至此,一旦HSE时钟恢复,将发生HSERDY中断,在RCC中断处理程序里,系统时钟可以设置到以前的状态}}在RCC的中断处理程序中,再对HSE和PLL进行相应的处理[编辑] RTC时钟通过设置备份域控制寄存器(RCC_BDCR)里的RTCSEL[1:0]位,RTCCLK时钟源可以由HSE/128、LSE或LSI时钟提供.除非备份域复位,此选择不能被改变..LSE时钟在备份域里,但HSE和LSI时钟不是.因此:● 如果LSE被选为RTC时钟:─ 只要VBAT维持供电,尽管VDD供电被切断,RTC仍继续工作.● 如果LSI被选为自动唤醒单元(AWU)时钟:─ 如果VDD供电被切断, AWU状态不能被保证.有关LSI校准. ● 如果HSE时钟128分频后作为RTC时钟:─ 如果VDD供电被切断或内部电压调压器被关闭(1.8V域的供电被切断),则RTC状态不确定.─ 必须设置电源控制寄存器(见4.4.1节)的DPB位(取消后备区域的写保护)为’1’.[编辑] 看门狗时钟如果独立看门狗已经由硬件选项或软件启动,LSI振荡器将被强制在打开状态,并且不能被关闭.在LSI振荡器稳定后,时钟供应给IWDG.[编辑] 时钟输出在实际应用中,一些用户常常遇到某些外设需要对其输入外部时钟或方波,针对这一需求,常用的方法是使用软件模拟,或使用有源晶振为其提供时钟或方波.STM32的PA.8引脚具有复用功能——时钟输出(MCO),该功能能将STM32内部的时钟通过PA.8输出,这解决客户的问题,同时降低了硬件成本.微控制器允许输出时钟信号到外部MCO引脚.相应的GPIO端口寄存器必须被配置为相应功能.以下四个时钟信号可被选作MCO时钟:.● SYSCLK ● HSI ● HSE ● 除2的PLL时钟时钟的选择由时钟配置寄存器(RCC_CFGR)中的MCO[2:0]位控制.由于STM32 GPIO输出管脚的最大响应频率为50MHz,如果输出频率超过50MHz,则输出的波形会失真.应用举例//设置PA.8为复用Push-Pull模式.<br/>GPIO_InitStructure.GPIO_Pin = GPIO_Pin_8;GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;GPIO_Init(GPIOA, &GPIO_InitStructure);//输出时钟:时钟的选择由时钟配置寄存器(RCC_CFGR)中的MCO[2:0]位控制.<br/>RCC_MCOConfig(RCC_MCO);参数RCC_MCO为要输出的内部时钟: RCC_MCO_NoClock --- 无时钟输出RCC_MCO_SYSCLK --- 输出系统时钟(SysCLK)RCC_MCO_HSI --- 输出内部高速8MHz的RC振荡器的时钟(HSI)RCC_MCO_HSE --- 输出高速外部时钟信号(HSE)RCC_MCO_PLLCLK_Div2 --- 输出PLL倍频后的二分频时钟(PLLCLK/2)[编辑] RCC寄存器分析[编辑] 时钟控制寄存器(RCC_CR)偏移地址: 0x00复位值: 0x0000 XX83 X代表未定义.位31:26 保留,始终读为0.位25 PLLRDY:PLL时钟就绪标志 (PLL clock ready flag) PLL锁定后由硬件置’1’.0:PLL未锁定;1:PLL锁定.位24 PLLON:PLL使能 (PLL enable) 由软件置’1’或清零. 当进入待机和停止模式时,该位由硬件清零.当PLL时钟被用作或被选择将要作为系统时钟时,该位不能被清零.0:PLL关闭;1:PLL使能.位23:20 保留,始终读为0.位19 CSSON:时钟安全系统使能(Clock security system enable)由软件置’1’或清零以使能时钟监测器.0:时钟监测器关闭;1:如果外部4-16MHz振荡器就绪,时钟监测器开启.位18 HSEBYP:外部高速时钟旁路 (External high-speed clock bypass)在调试模式下由软件置’1’或清零来旁路外部晶体振荡器.只有在外部4-16MHz振荡器关闭的情况下,才能写入该位.0:外部4-16MHz振荡器没有旁路;1:外部4-16MHz外部晶体振荡器被旁路.位17 HSERDY:外部高速时钟就绪标志(External high-speed clock ready flag)由硬件置’1’来指示外部4-16MHz振荡器已经稳定.在HSEON位清零后,该位需要6个外部4-25MHz振荡器周期清零.0:外部4-16MHz振荡器没有就绪;1:外部4-16MHz振荡器就绪.位16 HSEON:外部高速时钟使能(External high-speed clock enable) 由软件置’1’或清零.当进入待机和停止模式时,该位由硬件清零,关闭4-16MHz外部振荡器.当外部4-16MHz振荡器被用作或被选择将要作为系统时钟时,该位不能被清零.0:HSE振荡器关闭;1:HSE振荡器开启.位15:8 HSICAL[7:0]:内部高速时钟校准(Internal high-speed clock calibration)在系统启动时,这些位被自动初始化位7:3 HSITRIM[4:0]:内部高速时钟调整(Internal high-speed clock trimming)由软件写入来调整内部高速时钟,它们被叠加在HSICAL[5:0]数值上.这些位在HSICAL[7:0]的基础上,让用户可以输入一个调整数值,根据电压和温度的变化调整内部HSI RC振荡器的频率.默认数值为16,可以把HSI调整到8MHz±1%;每步HSICAL的变化调整约40kHz.位2 保留,始终读为0.位1 HSIRDY:内部高速时钟就绪标志(Internal high-speed clock ready flag)由硬件置’1’来指示内部8MHz振荡器已经稳定.在HSION位清零后,该位需要6个内部8MHz振荡器周期清零.0:内部8MHz振荡器没有就绪;1:内部8MHz振荡器就绪.位0 HSION:内部高速时钟使能(Internal high-speed clock enable)由软件置’1’或清零.当从待机和停止模式返回或用作系统时钟的外部4-16MHz振荡器发生故障时,该位由硬件置’1’来启动内部8MHz的RC振荡器.当内部8MHz振荡器被直接或间接地用作或被选择将要作为系统时钟时,该位不能被清零.0:内部8MHz振荡器关闭; 1:内部8MHz振荡器开启.[编辑] 时钟配置寄存器(RCC_CFGR)偏移地址: 0x04复位值: 0x0000 0000访问: 0到2个等待周期,字,半字和字节访问只有当访问发生在时钟切换时,才会插入1或2个等待周期..位31:27 保留,始终读为0.位26:24 MCO:微控制器时钟输出(Microcontroller clock output)由软件置’1’或清零.0xx:没有时钟输出;100:系统时钟(SYSCLK)输出;101:内部RC振荡器时钟(HSI)输出;110:外部振荡器时钟(HSE)输出;111:PLL时钟2分频后输出.注意:- 该时钟输出在启动和切换MCO时钟源时可能会被截断.- 在系统时钟作为输出至MCO引脚时,请保证输出时钟频率不超过50MHz (I/O口最高频率).位22 USBPRE:USB预分频(USB prescaler) 由软件置’1’或清’0’来产生48MHz的USB时钟.在RCC_APB1ENR寄存器中使能USB时钟之前,必须保证该位已经有效.如果USB时钟被使能,该位不能被清零.0:PLL时钟1.5倍分频作为USB时钟1:PLL时钟直接作为USB时钟位21:18 PLLMUL:PLL倍频系数 (PLL multiplication factor) 由软件设置来确定PLL倍频系数.只有在PLL关闭的情况下才可被写入.注意:PLL的输出频率不能超过72MHz0000:PLL 2倍频输出 1000:PLL 10倍频输出0001:PLL 3倍频输出 1001:PLL 11倍频输出0010:PLL 4倍频输出 1010:PLL 12倍频输出0011:PLL 5倍频输出 1011:PLL 13倍频输出0100:PLL 6倍频输出 1100:PLL 14倍频输出0101:PLL 7倍频输出 1101:PLL 15倍频输出0110:PLL 8倍频输出 1110:PLL 16倍频输出0111:PLL 9倍频输出 1111:PLL 16倍频输出位17 PLLXTPRE:HSE分频器作为PLL输入 (HSE divider for PLL entry)由软件置’1’或清’0’来分频HSE后作为PLL输入时钟.只能在关闭PLL时才能写入此位.0:HSE不分频1:HSE 2分频位16 PLLSRC:PLL输入时钟源 (PLL entry clock source)由软件置’1’或清’0’来选择PLL输入时钟源.只能在关闭PLL时才能写入此位.0:HSI振荡器时钟经2分频后作为PLL输入时钟1:HSE时钟作为PLL输入时钟.位15:14 ADCPRE[1:0]:ADC预分频 (ADC prescaler)由软件置’1’或清’0’来确定ADC时钟频率00:PCLK2 2分频后作为ADC时钟01:PCLK2 4分频后作为ADC时钟10:PCLK2 6分频后作为ADC时钟11:PCLK2 8分频后作为ADC时钟位13:11 PPRE2[2:0]:高速APB预分频(APB2) (APB high-speed prescaler (APB2))由软件置’1’或清’0’来控制高速APB2时钟(PCLK2)的预分频系数.0xx:HCLK不分频100:HCLK 2分频101:HCLK 4分频110:HCLK 8分频111:HCLK 16分频位10:8 PPRE1[2:0]:低速APB预分频(APB1) (APB low-speed prescaler (APB1))由软件置’1’或清’0’来控制低速APB1时钟(PCLK1)的预分频系数.警告:软件必须保证APB1时钟频率不超过36MHz.0xx:HCLK不分频100:HCLK 2分频101:HCLK 4分频110:HCLK 8分频111:HCLK 16分频位7:4 HPRE[3:0]: AHB预分频 (AHB Prescaler)由软件置’1’或清’0’来控制AHB时钟的预分频系数.0xxx:SYSCLK 不分频1000:SYSCLK 2分频1001:SYSCLK 4分频1010:SYSCLK 8分频1101:SYSCLK 16分频1100:SYSCLK 64分频1101:SYSCLK 128分频1110:SYSCLK 256分频1111:SYSCLK 512分频注意:当AHB时钟的预分频系数大于1时,必须开启预取缓冲器.位3:2 SWS[1:0]:系统时钟切换状态(System clock switch status)由硬件置’1’或清’0’来指示哪一个时钟源被作为系统时钟.00:HSI作为系统时钟;01:HSE作为系统时钟;10:PLL输出作为系统时钟;11:不可用.位1:0 SW[1:0]:系统时钟切换 (System clock switch)由软件置’1’或清’0’来选择系统时钟源.在从停止或待机模式中返回时或直接或间接作为系统时钟的HSE出现故障时,由硬件强制选择HSI作为系统时钟(如果时钟安全系统已经启动)00:HSI作为系统时钟;01:HSE作为系统时钟;10:PLL输出作为系统时钟;11:不可用.[编辑] 时钟中断寄存器 (RCC_CIR)偏移地址: 0x08复位值: 0x0000 0000访问:无等待周期, 字, 半字和字节访问.位31:24 保留,始终读为0.位23 CSSC:清除时钟安全系统中断(Clock security system interrupt clear)由软件置’1’来清除CSSF安全系统中断标志位CSSF.0:无作用;1:清除CSSF安全系统中断标志位.位22:21 保留,始终读为0.位20 PLLRDYC:清除PLL就绪中断 (PLL ready interrupt clear) 由软件置’1’来清除PLL就绪中断标志位PLLRDYF.0:无作用;1:清除PLL就绪中断标志位PLLRDYF.位19 HSERDYC:清除HSE就绪中断 (HSE ready interrupt clear) 由软件置’1’来清除HSE就绪中断标志位HSERDYF.0:无作用;1:清除HSE就绪中断标志位HSERDYF.位18 HSIRDYC:清除HSI就绪中断 (HSI ready interrupt clear) 由软件置’1’来清除HSI就绪中断标志位HSIRDYF.0:无作用;1:清除HSI就绪中断标志位HSIRDYF.位17 LSERDYC:清除LSE就绪中断 (LSE ready interrupt clear) 由软件置’1’来清除LSE就绪中断标志位LSERDYF.0:无作用;1:清除LSE就绪中断标志位LSERDYF.位16 LSIRDYC:清除LSI就绪中断 (LSI ready interrupt clear) 由软件置’1’来清除LSI就绪中断标志位LSIRDYF.0:无作用;1:清除LSI就绪中断标志位LSIRDYF.位15:13 保留,始终读为0.位12 PLLRDYIE:PLL就绪中断使能 (PLL ready interrupt enable) 由软件置’1’或清’0’来使能或关闭PLL就绪中断.0:PLL就绪中断关闭;1:PLL就绪中断使能.位11 HSERDYIE:HSE就绪中断使能(HSE ready interrupt enable)由软件置’1’或清’0’来使能或关闭外部4-16MHz振荡器就绪中断.。

STM32RCC分析与使用

STM32RCC分析与使用STM32 RCC(Reset and Clock Control)模块是基于STMicroelectronics公司的STM32系列微控制器(MCU)的一部分。

RCC 模块用于对MCU的时钟和复位进行控制和配置。

本文将对STM32 RCC模块进行分析与使用进行详细介绍。

一、RCC模块概述RCC模块包含多个寄存器和位域,用于配置MCU的时钟源和时钟分频器,以及对复位进行控制。

RCC模块的主要功能如下:1.时钟源选择:RCC模块允许选择MCU的时钟源,包括内部时钟源(HSI、LSI)、外部时钟源(HSE、LSE)和PLL。

2.时钟分频器:RCC模块允许对时钟源进行分频,从而获得所需的系统时钟频率。

3.复位控制:RCC模块提供了多个复位信号,包括软件复位、外部复位和低功耗复位。

4.时钟使能:RCC模块允许对不同模块的时钟进行使能或禁用,以节省功耗。

二、RCC模块寄存器RCC模块包含多个寄存器,用于配置和控制时钟和复位。

以下是一些常用的RCC模块寄存器:1.RCC_CR:时钟控制寄存器,包含时钟源选择和使能控制位。

2.RCC_CFGR:时钟配置寄存器,包含PLL、时钟分频器和USBOTGFS时钟配置等。

3.RCC_APB1ENR/RCC_APB2ENR:外设时钟使能寄存器,用于使能或禁用不同外设的时钟。

4.RCC_AHB1RSTR/RCC_APB1RSTR/RCC_APB2RSTR:复位寄存器,用于控制不同外设的复位。

5.RCC_CSR:复位状态寄存器,用于读取和清除复位原因。

三、RCC模块的使用以下是一些常见的RCC模块的使用方法:1.时钟源选择:通过设置RCC_CR寄存器的位域,选择所需的时钟源。

例如,可以选择HSE作为系统时钟源。

2.时钟分频器配置:通过设置RCC_CFGR寄存器的位域,配置所需的时钟频率。

例如,可以将PLL分频系数设置为2,以获得系统时钟频率为HSE/23.外设时钟使能:通过设置RCC_APB1ENR/RCC_APB2ENR寄存器的位域,使能或禁用所需外设的时钟。

STM32时钟详细配置

STM32时钟详细配置STM32时钟配置STM32时钟配置步骤// 开启HSI时钟寄存器操作1).开启高速时钟HSE // 设置时钟控制寄存器RCC_CR 位16 置1使能RCC->CR|= 0x00010000;位16 :HSEON:外部高速时钟使能当进入待机和停止模式时,该位由硬件清零,关闭4-16MHz外部振荡器。

当外部4-16MHz 振荡器被用作或被选择将要作为系统时钟时,该位不能被清零。

2).等待高速时钟就绪// 读取时钟控制寄存器RCC_CR位17为1就位while(!(RCC-> CR>>17));位17:HSERDY:外部高速时钟就绪标志由硬件置’1’来指示外部4-16MHz振荡器已经稳定。

在HSEON位清零后,该位需要6个外部4-25MHz振荡器周期清零。

3).设置APB1,APB2,AHB分频系数// 设置时钟配置寄存器RCC_CFGRRCC_CFGR=0x00000400;(AHB :位4-7, (低速)APB1 :位8-10, (高速)APB2 :位11-13)位7:4:HPRE[3:0]:AHB预分频(AHB Prescaler)0xxx:SYSCLK 不分频位10:8:PPRE1[2:0]:低速APB预分频(APB1) 100:HCLK 2分频位13:11:PPRE2[2:0]:高速APB预分频(APB2) 0xx:HCLK不分频4).设置PLL倍频// 配置时钟配置寄存器RCC_CFGR 位18-21RCC_CFGR|=7<<18;位21:18:PLLMUL:PLL倍频系数0111:PLL 9倍频输出5).PLL输入时钟源选择// 配置时钟配置寄存器RCC_CFGR 位16RCC_CFGR|=1<<16;位16:PLLSRC:PLL输入时钟源(PLL entry clock source) 1:HSE时钟作为PLL输入时钟。

stm32复位和时钟控制

以下模块多个时钟源可选择

ADC模块

PCLK经过2或4分频,专用的14MHz-HSI 如果选择专用14MHz作为ADC时钟,可以配置是否由ADC自动开启/关闭14MHz RC

USART1

PCLK,系统时钟,HSI,LSE

I2C1

HSI,系统时钟

CEC

HSI/244,LSE

TI1_RMP @ TIM14_OR

TIM14

GPIO

TI1

RTCCLK HSE/32 MCO

7

低功耗模式下的时钟表现

睡眠模式

CPU时钟停止 用户可以设置是否也停止片上闪存和SRAM的接口时钟 如果所有连在APB总线上的外设的时钟都被用户关闭,则AHB到APB 桥的时钟也被硬件关闭

LSI

35~40~55 KHz

85 us

PLL

输入时钟频率 输出时钟频率

1~24 MHz 16~48 MHz

4

LSE起振能力动态可调

5

特殊外设时钟供给

片上闪存编程接口,HSI Option byte loader,HSI I2S1,系统时钟 IWWDG,LSI

由软件或硬件开启;一旦开启LSI就不能关闭

1

时钟树框图

OSC32_IN OSC32_OUT ~40kHz LSI RC 8MHz HSI RC /2 4 -32 MHz OSC_OUT OSC_IN /2, 4 [16MHz,48MHz] HSI14 RC ADC HSE Osc /2, 3, ..16 HSI IWWDGCLK CSS PCLK HCLK 32.768KHz LSE Osc HSE /32 RTCCLK /8 SysTick

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

复位

STM32F10xxx支持三种复位形式,分别为系统复位、电源复位和备份区域复位。

1、系统复位

系统复位将所有寄存器设置成复位值,除了RCC_CSR(控制状态寄存器)中的相关复位标志位,通过查看RCC_CSR寄存器,可以识别复位源。

系统复位可由以下5种方式产生:

1)外部引脚NRST复位(低电平触发);

2)窗口看门狗(WWDG)计数终止

3)独立看门狗(IDOG)计数终止

4)软件复位(SW RESET),通过将中断应用和复位控制寄存器

(Application Interrupt and Reset Control Register )中SYSRESETREQ位置1。

具体参考Cortex-M3 programming manual。

5)低功耗管理复位:

①通过进入等待模式(StandBy)产生复位:

通过User Option Bytes中设置nRST_STDBY位使能这种复

位模式。

这时,即使执行了进入待机模式的过程,系统将

被复位而不是进入待机模式。

②通过进入停止模式(STOP)产生复位:

通过User Option Bytes中设置nRST_STOP位使能这种复

位模式。

这时,即使执行了进入停止模式的过程,系统将

被复位而不是进入停止模式。

2、电源复位

电源复位设置所有寄存器置初始值,除了备份区域。

电源复位可由以下2种方式产生:

1)上电复位和掉电复位(POR/PDR reset)

2)退出等待(StandBy)模式

这些复位源都作用在NRST引脚上,并且在复位延迟期间保持低电平。

提供给设备的系统复位信号都由NRST引脚输出,对每一个内部/外部复位源,脉冲发生器都将保证一个20us最小复位周期。

对于外部复位,当NRST位置低时,将产生复位信号。

3、备份区复位

备份区复位仅仅影响被分区域,有以下两种产生方式:

1)软件复位,设置备份区域控制寄存器RCC_BDCR BDRST= 1;

2)在V DD和V BAT两者掉电的前提下,V DD或V BAT上电。

时钟

系统时钟(SYSCLK)可由3种时钟源驱动:

●内部高速震荡时钟(HSI)

●外部高速震荡时钟(HSE)

●PLL时钟

设备有如下2种二级时钟源:

●40KHz的内部低速RC震荡时钟(LSI),用来驱动独立看门狗

(IDOG)、或驱动用来从停止/等待模式中恢复的RTC时钟;

●32.768KHz的低速外部晶振时钟(LSE),用来驱动RTC时钟

以上5中时钟都可以独立的打开或关闭。

时钟树如下:

1、外部高速震荡时钟(HSE)

外部时钟信号来源:

①外部时钟信号。

在这种模式下,OSC_IN 接时钟输入信号,OSC_OUT

引脚悬空,输入信号是最高25Mhz的占空比是50%的方波、正弦波、三角波信号。

使能方式:RCC_CR→HSEBYP 和HSEON 置1

②外部晶体/陶瓷谐振产生信号,晶振频率范围在4~16Mhz。

通过

RCC_CR→ HSEON 可以开/关外部晶振

2、内部高速震荡时钟(HSI)

内部高速时钟由一个8MHz的RC震荡电路产生,能直接用作系

统时钟(SYSCLK)或2分频后作为PLL输入端信号。

HEI比HSE有跟快的启动延迟,但时钟信号不如HSE精确。

当HSE停止工作时,HSI自动为系统提供时钟。

通过RCC_CR→HSION

可以开/关内部时钟。

3、PLL时钟

PLL主要用来倍频内部高速时钟(HSI)和外部高速时钟(HSE)。

在是能PLL之前,需要选择PLL输入信号(HIS/2、HSE)、配置倍

频因子。

当在应用中使用USB接口时,PLL输出必须配置成48MHz

或72MHz。

4、外部低速时钟(LSE)

外部低速时钟信号由一个32.768KHz的低速外部谐振器产生,可以为RTC时钟/日历提供低功耗,高精确度的时钟信号。

可以通过发(Backup domain control register)RCC_BDCR LSEON 来控制LSE 的开关。

此外,外部低速时钟也可以通过旁路(bypass)产生,时钟周期最高位1MHz,具体配置流程可参照外部高速时钟(HSE)。

5、内部低速时钟(LSI)

内部低速时钟主要用来在停止(STOP)模式和等待(StandBy)模式为独立看门狗(IWDG)和自动唤醒单元(AWU)提供提供低功耗时钟信号,时钟信号在40KHz左右(30~60KHz之间)。

内部低速时钟可以通过人工校正,具体流程参见STM32参考手册Page87~88。

系统时钟(SYSCLK)

系统复位后,内部高速时钟(HSI)作为默认的系统时钟,当时钟源直接或通过PLL倍频后作为系统时钟源后,将不能被停止。

只有当目标始终源准备就绪(经过时钟开启延迟和PLL延迟),从一个时钟源切换到另一个时钟源才可能执行。

否则必须等到目标时钟准备好再执行。

在时钟控制寄存器(RCC_CR)里的状态位指示哪个时钟已经准备好了,哪个时钟目前被用作系统时钟。

RTC时钟

RTC时钟源可由HSE/128、LSE或LSI时钟提供。

通过修改备份

区控制寄存器RCC_BDCR→RTCSEL[1:0]来选择。

注意:除非复位备

份区,否则时钟选择后不能被修改。

LSE时钟在备份区,HSE和LSI不在。

1)如果LSE被选择作为RTC的时钟源,则当V DD掉电时,RTC不会

停止工作,只要V BAT仍然保持。

2)如果LSI被选择作为自动唤醒单元(AWU)的时钟源,则当V DD

掉电时,AWU的状态不能够被保证。

3)如果HSE的128分频作为RTC的时钟源,取消后备区写保护位要

置位:PWR_CR→DPB = 1(允许写入RTC和后备区寄存器)。

如

果VDD掉电,或者器件内部的电压调节器掉电时,RTC的状态不能被保证。

看门狗(Watchdog)时钟

如果独立看门狗已经由硬件选项或软件启动,LSI振荡器将被强制在打开状态,并且不能被关闭。

在LSI振荡器稳定后,时钟供应给IWDG。

时钟输出(Clock-Out)功能

时钟信号可由MCO 引脚对外输出,相应的GPIO端口寄存器必须被配置为相应功能。

通过配置RCC_CFGR→MCO[2:0]来选择输出时钟信号源:

1)系统时钟(SYSCLK)

2)外部高速时钟(HSE)

3)内部高速时钟(HSI)

4)PLL时钟2分频(PLL/2)。