半导体工艺干法刻蚀铝刻蚀

半导体八大工艺顺序

半导体八大工艺顺序半导体制造是一个复杂的过程,需要经过八个主要的工艺步骤才能完成。

这些工艺步骤包括晶圆清洗、沉积、光刻、蚀刻、清洗、离子注入、退火和测试。

下面将对这些工艺步骤进行详细介绍。

1. 晶圆清洗晶圆清洗是制造半导体的第一步,目的是去除晶圆表面的杂质和污染物,以确保后续工艺的顺利进行。

晶圆清洗通常使用化学物质和超声波来实现。

首先将晶圆浸泡在去离子水中,然后使用化学物质和超声波来去除表面污染物。

2. 沉积沉积是将材料沉积在晶圆表面的过程。

这个过程通常使用化学气相沉积(CVD)或物理气相沉积(PVD)来实现。

在CVD中,化学反应会产生气体,然后将其放置在晶圆上,在高温下发生反应并形成所需的材料层。

在PVD中,原子或分子会通过真空管道传输到晶圆表面,然后在晶圆表面生成所需的材料层。

3. 光刻光刻是将图案转移到晶圆表面的过程。

这个过程通常使用光刻胶和掩模来实现。

首先,在晶圆表面涂上一层光刻胶,然后将掩模放置在光刻胶上,并使用紫外线照射掩模。

这会使光刻胶在掩模的开口处固化,形成所需的图案。

4. 蚀刻蚀刻是将材料从晶圆表面移除的过程。

这个过程通常使用干法或湿法蚀刻来实现。

在干法蚀刻中,使用等离子体或化学反应来去除不需要的材料层。

在湿法蚀刻中,使用化学物质来溶解不需要的材料层。

5. 清洗清洗是去除蚀刻残留物和其他污染物的过程。

这个过程通常使用酸、碱和有机溶剂来实现。

首先将晶圆浸泡在酸、碱或有机溶剂中,然后用去离子水冲洗干净。

6. 离子注入离子注入是将离子注入晶圆表面的过程。

这个过程通常用于形成掺杂层和修饰材料的电学性质。

在离子注入过程中,使用加速器将离子加速到非常高的速度,然后将它们注入晶圆表面。

7. 退火退火是在高温下加热晶圆以改善其电学性质的过程。

在退火过程中,晶圆被放置在高温炉中,并暴露于高温下一段时间。

这会使掺杂层扩散并形成所需的电学性质。

8. 测试测试是检查芯片是否正常运行的过程。

这个过程通常使用测试设备来实现。

半导体刻蚀工艺技术——ICP.

半导体刻蚀工艺技术——ICP摘要:ICP技术是微纳加工中的常用技术之一,本文简单介绍了ICP刻蚀技术(inductively coupled plasma)的基本原理和刻蚀设备的结构,对ICP工艺所涉及的化学、物理过程做了简要分析。

阐述了ICP刻蚀参数对刻蚀结果的影响以及干法刻蚀的生成物。

由于ICP技术在加工过程中可控性高,具有越来越重要的地位。

以在硅基MEMS器件的ICP刻蚀为例,详细的介绍了在硅基MEMS制作过程中ICP刻蚀的反应过程,说明了在ICP刻蚀过程中如何实现控制加工深度和角度。

据近年来国内外ICP技术的发展现状和发展趋势,对其在光电子器件、半导体氧化物、Ⅲ一V族化合物等方面的应用作了一些简要介绍。

关键词:ICP、刻蚀、参数、模型、等离子体Process technology of semiconductor etching——ICPLIU Zhi Wei(Xi'an Electronic and Science University, School of Microelectronics.1411122908)Abstract:ICP technology is one of the commonly used in micro nano processing technology,This paper simply introduces ICP etching technology (inductively coupled plasma) structure and the basic principles of etching equipment,To do a brief analysis on the ICP process involved in chemical, physical process.Describes the effects of ICP etching parameters on the etching results and the resultant dry etching. Because the ICP technology in the process of processing high controllability, plays a more and more important role. Using ICP etching in silicon MEMS device as an example, describes in detail in the reaction process of silicon based MEMS in the production process of ICP etching, explains how to realize the control of machining depth and angle in the ICP etching process. According to the development status and development trend at home and abroad in recent years of ICP technology, its application in optoelectronic devices and semiconductor oxide, III a group V compound as well as some brief introduction.Key words:ICP、etching, parameter, model, plasma1引言刻蚀是微细加工技术的一个重要组成部分,微电子学的快速发展推动其不断向前。

综述报告——刻蚀简介

微加工技术——刻蚀简介自从半导体诞生以来,很大程度上改变了人类的生产和生活。

半导体除了在计算机领域应用之外,还广泛地应用于通信、网络、自动遥控及国防科技领域。

本文主要介绍半导体制造工艺中的刻蚀工艺。

随着半导体制造大规模集成电路技术的发展,图形加工线条越来越细,硅片尺寸越来越大,对刻蚀工艺的要求也越来高。

因此,学习了解刻蚀工艺十分必要。

本文将主要从刻蚀简介、刻蚀参数及现象、干法刻蚀和湿法刻蚀四个方面进行论述。

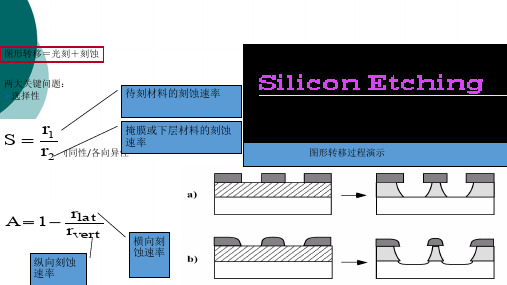

1、刻蚀简介1.1 刻蚀定义及目的刻蚀就是用化学的、物理的或同时使用化学和物理的方法,有选择地把没有被抗蚀剂掩蔽的那一部分薄膜层除去,从而在薄膜上得到和抗蚀剂膜上完全一致的图形。

刻蚀的基本目的,是在涂光刻胶(或有掩膜)的硅片上正确的复制出掩膜图形[1]。

刻蚀,通常是在光刻工艺之后进行。

通过刻蚀,在光刻工艺之后,将想要的图形留在硅片上。

从这一角度而言,刻蚀可以被称之为最终的和最主要的图形转移工艺步骤。

在通常的刻蚀过程中,有图形的光刻胶层〔或掩膜层)将不受到腐蚀源显著的侵蚀或刻蚀,可作为掩蔽膜,保护硅片上的部分特殊区域,而未被光刻胶保护的区域,则被选择性的刻蚀掉。

其工艺流程示意图如下。

1.2 刻蚀的分类从工艺上分类的话,在半导体制造中有两种基本的刻蚀工艺:干法刻蚀和湿法腐蚀。

干法刻蚀,是利用气态中产生的等离子体,通过经光刻而开出的掩蔽层窗口,与暴露于等离子体中的硅片行物理和化学反应,刻蚀掉硅片上暴露的表面材料的一种工艺技术法[1]。

该工艺技术的突出优点在于,是各向异性刻蚀(侧向腐蚀速度远远小于纵向腐蚀速度,侧向几乎不被腐蚀),因此可以获得极其精确的特征图形。

超大规模集成电路的发展,要求微细化加工工艺能够严格的控制加工尺寸,要求在硅片上完成极其精确的图形转移。

任何偏离工艺要求的图形或尺寸,都可能直接影响产品性能或品质,给生产带来无法弥补的损害。

由于干法刻蚀技术在图形转移上的突出表现,己成为亚微米尺寸下器件刻蚀的最主要工艺方法。

金属铝刻蚀工艺简介

在金属铝中通常会加入少量的硅和铜来提

高电子器件的可靠性。硅和Cl反应生成挥发性的

SiCl ,很容易被带出反应腔。铜与Cl反应生成的 4

CuCl2 挥发性却不高,因此需要加大物理性的离 子轰击把铜原子去掉,一般可以通过加大 Ar 和

AlCl 被气流带出反应腔。BCl 一方面提供BCl +,

3

3

3

垂直轰击硅片表面,达到各向异性的刻蚀。另一

方面,由于铝表面极易氧化成氧化铝,这层自生

氧化铝在刻蚀的初期阻隔了 Cl 和铝的接触,阻 2

碍了刻蚀的进一步进行。添加 BCl 则利于将这 3

层氧化层还原(如方程式 1),促进刻蚀过程的继

续进行。

基础知识 HOW TO MAKE A CHIP

金属铝刻蚀工艺简介

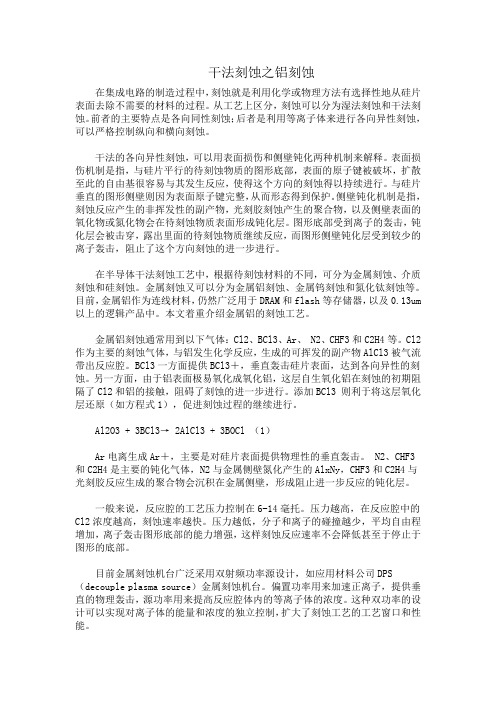

在 集成电路的制造过程中,刻蚀就是利 用化学或物理方法有选择性地从硅片 表面去除不需要的材料的过程。从工

艺上区分,刻蚀可以分为湿法刻蚀和干法刻蚀。

前者的主要特点是各向同性刻蚀;后者是利用等

离子体来进行各向异性刻蚀,可以严格控制纵向

和横向刻蚀。

蚀和氮化钛刻蚀等。目前,金属铝作为连线材

料,仍然广泛用于 DRAM 和 flash 等存储器,以

及 0.13um 以上的逻辑产品中。本文着重介绍金

属铝的刻蚀工艺。

金属铝刻蚀通常用到以下气体:Cl 、BCl 、

2

3

Ar、 N 、CHF 和 C H 等。Cl 作为主要的刻蚀气

2

3

24

2

体,与铝发生化学反应,生成的可挥发的副产物

半导体八大工艺顺序

半导体八大工艺顺序半导体八大工艺顺序,是指半导体制造过程中的八个主要工艺步骤。

这些工艺步骤包括晶圆清洗、光刻、沉积、刻蚀、扩散、离子注入、退火和包封。

下面将逐一介绍这些工艺步骤的顺序及其作用。

1. 晶圆清洗晶圆清洗是半导体制造过程中的第一步。

在这一步骤中,晶圆将被放入化学溶液中进行清洗,以去除表面的杂质和污染物。

这样可以确保后续工艺步骤的顺利进行,同时也可以提高器件的质量和性能。

2. 光刻光刻是半导体制造中的关键工艺步骤之一。

在这一步骤中,将使用光刻胶覆盖在晶圆表面上,并通过光刻机将图形投射到光刻胶上。

然后,利用化学溶液将未曝光的光刻胶去除,从而形成所需的图形。

3. 沉积沉积是指在晶圆表面上沉积一层薄膜的工艺步骤。

这一层薄膜可以用于改变晶圆表面的性质,增加其导电性或绝缘性。

常用的沉积方法包括化学气相沉积和物理气相沉积。

4. 刻蚀刻蚀是将多余的材料从晶圆表面去除的工艺步骤。

在这一步骤中,利用化学溶液或等离子刻蚀机将不需要的材料去除,从而形成所需的图形和结构。

5. 扩散扩散是将杂质或掺杂物diffused 到晶圆中的工艺步骤。

这一步骤可以改变晶圆的电学性质,并形成PN 结等器件结构。

常用的扩散方法包括固体扩散和液相扩散。

6. 离子注入离子注入是将离子注入到晶圆中的工艺步骤。

这可以改变晶圆的导电性和掺杂浓度,从而形成电子器件的结构。

离子注入通常在扩散之前进行。

7. 退火退火是将晶圆加热至一定温度并保持一段时间的工艺步骤。

这可以帮助晶圆中的杂质扩散和掺杂物活化,从而提高器件的性能和稳定性。

8. 包封包封是将晶圆封装在外部保护材料中的工艺步骤。

这可以保护晶圆不受外部环境的影响,同时也可以方便晶圆的安装和使用。

半导体制造过程中的八大工艺顺序是一个复杂而精密的过程。

每个工艺步骤都起着至关重要的作用,只有严格按照顺序进行,才能生产出高质量的半导体器件。

希望通过本文的介绍,读者对半导体制造过程有了更深入的了解。

半导体八大工艺顺序

半导体八大工艺顺序半导体八大工艺顺序是指半导体器件制造过程中的八个主要工艺步骤。

这些工艺步骤的顺序严格按照一定的流程进行,确保半导体器件的质量和性能。

下面将逐一介绍这八大工艺顺序。

第一步是晶圆清洁工艺。

在半导体器件制造过程中,晶圆是最基本的材料。

晶圆清洁工艺旨在去除晶圆表面的杂质和污染物,确保后续工艺步骤的顺利进行。

第二步是光刻工艺。

光刻工艺是将图形模式转移到晶圆表面的关键步骤。

通过光刻工艺,可以在晶圆表面形成所需的图形结构,为后续工艺步骤提供准确的参考。

第三步是沉积工艺。

沉积工艺是将材料沉积到晶圆表面的过程,包括化学气相沉积、物理气相沉积和溅射等技术。

通过沉积工艺,可以在晶圆表面形成所需的材料结构。

第四步是刻蚀工艺。

刻蚀工艺是将多余的材料从晶圆表面去除的过程,以形成所需的图形结构。

刻蚀工艺通常使用化学刻蚀或物理刻蚀的方式进行。

第五步是离子注入工艺。

离子注入工艺是向晶圆表面注入掺杂物质的过程,以改变晶体的电学性质。

通过离子注入工艺,可以实现半导体器件的掺杂和调控。

第六步是热处理工艺。

热处理工艺是将晶圆置于高温环境中进行退火、烘烤或氧化等处理的过程。

通过热处理工艺,可以改善晶体的结晶质量和电学性能。

第七步是清洗工艺。

清洗工艺是在制造过程中对晶圆进行清洗和去除残留污染物的过程,以确保半导体器件的质量和可靠性。

第八步是封装测试工艺。

封装测试工艺是将完成的半导体器件封装成最终产品,并进行性能测试和质量检验的过程。

通过封装测试工艺,可以确保半导体器件符合规格要求,并具有稳定可靠的性能。

总的来说,半导体八大工艺顺序是半导体器件制造过程中的关键步骤,每个工艺步骤都至关重要,任何一环节的不慎都可能影响整个制造过程的质量和性能。

通过严格按照八大工艺顺序进行制造,可以确保半导体器件具有优良的性能和可靠性,从而满足现代电子产品对半导体器件的高要求。

半导体干法蚀刻的介绍

半导体干法蚀刻的介绍《半导体干法蚀刻:新兴技术的应用与发展》引言:半导体干法蚀刻是一种关键的制造工艺,在半导体行业中有着广泛的应用。

本文将着重介绍半导体干法蚀刻的原理、特点以及其在新兴技术领域的应用与发展。

正文:一、半导体干法蚀刻的原理半导体干法蚀刻是利用气体或等离子体与半导体表面发生反应来实现物质的去除。

通过将气体或者气体混合物注入到真空环境中,让气体产生等离子体,利用等离子体中的活性粒子或自由基对半导体表面进行化学反应或破坏性物理反应,从而移除半导体表面的一层材料。

二、半导体干法蚀刻的特点1. 制程精度高:通过控制反应气体、温度、时间等参数,可以实现较高的制程精度,满足半导体器件的要求。

2. 制程可控性强:半导体干法蚀刻过程中可以精确控制蚀刻速率和选择性,从而实现对半导体的精确加工。

3. 无需接触:与湿法蚀刻相比,半导体干法蚀刻是一种无需接触半导体表面的加工方式,可以避免因接触引起的损伤和污染。

4. 适用性广:半导体干法蚀刻可以适用于各种材料,包括硅、氮化硅、氮化铝等,可满足不同材料的蚀刻需求。

5. 环保高效:半导体干法蚀刻是一种无废液产生的加工方式,不会对环境造成污染,同时也节约了大量的水资源。

三、半导体干法蚀刻在新兴技术的应用与发展1. 三维芯片制造:随着半导体器件的发展,传统的二维芯片逐渐无法满足需求。

半导体干法蚀刻可以实现对芯片表面的精确加工,为三维芯片制造提供了重要工艺支持。

2. 纳米加工:随着纳米科技的快速发展,半导体干法蚀刻在纳米加工中广泛应用。

通过控制蚀刻参数,可以实现纳米尺寸的结构制造,为纳米电子学和纳米光学等领域的研究提供了有力支持。

3. 新型材料加工:随着新型材料的涌现,传统的湿法蚀刻技术面临挑战。

半导体干法蚀刻可以适用于新型材料的加工,如氮化硅、氮化铝等,为新型材料的应用拓展提供了技术保障。

结论:半导体干法蚀刻是一种重要的制造工艺,具有制程精度高、制程可控性强、适用性广、环保高效等特点。

半导体芯片干法刻蚀工艺

半导体芯片干法刻蚀工艺在这个数字化的时代,半导体芯片可谓是科技界的小明星,大家对它们的热情,就像追星族追逐偶像一样,热火朝天。

而提到半导体芯片,干法刻蚀工艺绝对是一个不可忽视的环节。

今天咱们就来聊聊这个“干法刻蚀”的故事,让你在轻松中了解这门高深的技术。

1. 什么是干法刻蚀?1.1 定义首先,干法刻蚀就是用气体来处理材料,简单来说就是通过气体将多余的部分“刻”掉。

就像我们平时用刀削水果,削掉外皮,露出里面美味的果肉。

干法刻蚀用的可不是普通的刀,而是高科技的气体分子,神奇吧?1.2 为什么需要它?为什么要干法刻蚀呢?其实这背后有个大秘密。

半导体材料上需要留下微小的电路图案,这些图案就像是一幅精美的画作,而干法刻蚀就是这个画家的工具。

没有它,芯片就像一盘没有调味料的菜,毫无生气。

2. 干法刻蚀的过程2.1 设备与准备干法刻蚀的设备可不是家里那种简单的工具,而是需要高科技的机器。

首先要准备好材料,这就像做菜前先把食材准备齐全。

材料要干净,没有杂质,否则结果就像炒饭时夹杂了不该有的调料,味道会很差。

2.2 刻蚀步骤接下来就是真正的“刻蚀”过程。

我们把准备好的材料放入刻蚀机中,然后把气体注入,气体和材料发生反应,把不需要的部分给“消灭”掉。

这一步就像是让一位雕刻家在大理石上精雕细琢,细致入微,最终形成我们想要的图案。

整个过程需要极高的温度和压力,真是热火朝天,紧张又刺激。

3. 干法刻蚀的优势与挑战3.1 优势干法刻蚀的优势可不少。

首先,它能实现高精度的刻蚀,就像精准的手艺人,毫不马虎。

此外,干法刻蚀能处理各种不同的材料,这样一来,适应性强,真是让人赞叹不已。

3.2 挑战不过,挑战也随之而来。

比如,气体的选择、刻蚀的速度等等,都是需要精确把控的,要是稍有差池,就可能导致整个工艺的失败。

这就像是在走钢丝,一不小心就得“摔”下来,真是心惊胆战。

4. 总结干法刻蚀工艺就像一门艺术,既有技术的严谨,也有创意的灵动。

干法刻蚀的优点和过程

干法刻蚀的优点和过程硅湿法刻蚀典型的硅刻蚀是用含氮的物质与氢氟酸的混合水溶液。

这一配比规则在控制刻蚀中成为一个重要的因素。

在一些比率上,刻蚀硅会有放热反应。

加热反应所产生的热可加速刻蚀反应,接下来又产生更多的热,这样进行下去会导致工艺无法控制。

有时醋酸和其他成分被混合进来控制加热反应。

三国迷的福音!《三国志》再出新作,实...广告一些器件要求在晶圆上刻蚀出槽或沟。

刻蚀配方要进行调整以使刻蚀速率依靠晶圆的取向。

<1,1,1>取向的晶圆以45°角刻蚀,<1,0,0>取向的晶圆以“平”底刻蚀。

其他取向的晶圆可以得到不同形状的沟槽。

多晶硅刻蚀也可用基本相同的规则。

二氧化硅湿法刻蚀最普通的刻蚀层是热氧化形成的二氧化硅。

基本的刻蚀剂是氢氟酸,它有刻蚀二氧化硅而不伤及硅的优点。

然而,饱和浓度的氢氟酸在室温下的刻蚀速率约为300A/s。

这个速率对于一个要求控制的工艺来说太快了。

展开剩余79%在实际中,氢氟酸与水或氟化铵及水混合。

以氟化铵来缓冲加速刻蚀速率的氢离子的产生。

这种刻蚀溶液称为缓冲氧化物刻蚀或BOE。

针对特定的氧化层厚度,他们以不同的浓度混合来达到合理的刻蚀时间。

一些BOE公式包括一个湿化剂用以减小刻蚀表面的张力,以使其均匀地进入更小的开孔区。

暴露硅晶圆表面的过刻蚀可以引起表面的粗糙。

在氢氟酸工艺期间,当暴露于OH-离子时,在刻蚀中硅表面会变粗糙。

铝膜湿法刻蚀对于铝和铝合金层有选择性的刻蚀溶液是居于磷酸的。

遗憾的是,铝和磷酸反应的副产物是微小的氢气泡。

这些气泡附着在晶圆表面,并阻碍刻蚀反应。

结果既可能产生导致相邻引线短路的铝桥连,又可能在表面形成不希望出现的雪球的铝点。

特殊配方铝刻蚀溶液的使用缓解了这个问题。

典型的活性溶液成分配比是:16:1:1:2。

除了特殊配方外,典型的铝刻蚀工艺还会包含以搅拌或上下移动晶圆舟的搅动。

有时超声波或兆频超声波也用来去除气泡。

淀积氧化物湿法刻蚀晶圆上的最终膜层之一是一层在铝膜上的二氧化硅钝化膜。

干法刻蚀技术

蚀刻技术最早的蚀刻技术是利用特定的溶液与薄膜间所进行的化学反应来去除薄膜未被光阻覆盖的部分,而达到蚀刻的目的,这种蚀刻方式也就是所谓的湿式蚀刻。

因为湿式蚀刻是利用化学反应来进行薄膜的去除,而化学反应本身不具方向性,因此湿式蚀刻过程为等向性,一般而言此方式不足以定义3微米以下的线宽,但对于3微米以上的线宽定义湿式蚀刻仍然为一可选择采用的技术。

湿式蚀刻之所以在微电子制作过程中被广泛的采用乃由于其具有低成本、高可靠性、高产能及优越的蚀刻选择比等优点。

但相对于干式蚀刻,除了无法定义较细的线宽外,湿式蚀刻仍有以下的缺点:1) 需花费较高成本的反应溶液及去离子水;2) 化学药品处理时人员所遭遇的安全问题;3) 光阻附着性问题;4) 气泡形成及化学蚀刻液无法完全与晶圆表面接触所造成的不完全及不均匀的蚀刻;5) 废气及潜在的爆炸性。

湿式蚀刻过程可分为三个步骤:1) 化学蚀刻液扩散至待蚀刻材料之表面;2) 蚀刻液与待蚀刻材料发生化学反应; 3) 反应后之产物从蚀刻材料之表面扩散至溶液中,并随溶液排出(3)。

三个步骤中进行最慢者为速率控制步骤,也就是说该步骤的反应速率即为整个反应之速率。

大部份的蚀刻过程包含了一个或多个化学反应步骤,各种形态的反应都有可能发生,但常遇到的反应是将待蚀刻层表面先予以氧化,再将此氧化层溶解,并随溶液排出,如此反复进行以达到蚀刻的效果。

如蚀刻硅、铝时即是利用此种化学反应方式。

湿式蚀刻的速率通常可藉由改变溶液浓度及温度予以控制。

溶液浓度可改变反应物质到达及离开待蚀刻物表面的速率,一般而言,当溶液浓度增加时,蚀刻速率将会提高。

而提高溶液温度可加速化学反应速率,进而加速蚀刻速率。

除了溶液的选用外,选择适用的屏蔽物质亦是十分重要的,它必须与待蚀刻材料表面有很好的附着性、并能承受蚀刻溶液的侵蚀且稳定而不变质。

而光阻通常是一个很好的屏蔽材料,且由于其图案转印步骤简单,因此常被使用。

但使用光阻作为屏蔽材料时也会发生边缘剥离或龟裂的情形。

半导体干法刻蚀工艺流程

半导体干法刻蚀工艺流程English Answer:Dry Etching Process Flow for Semiconductor Fabrication.1. Substrate Preparation.Clean the substrate to remove any contaminants or particles.Apply a photoresist or mask to define the areas to be etched.2. Etching.Expose the substrate to a plasma or ion beam.The plasma or ion beam reacts with the surface of the substrate, etching away the exposed areas.The etching process can be controlled by varying the plasma or ion beam parameters, such as power, pressure, and gas flow.3. Photoresist Removal.Remove the photoresist or mask after etching is complete.This can be done using a solvent or plasma ashing.4. Post-Etching Treatment.Clean the substrate to remove any residual contaminants.Apply a protective coating or passivation layer to protect the etched surface.Additional Considerations.The choice of etching process depends on the material being etched, the desired etch profile, and the desiredthroughput.Dry etching processes are often used for high-precision applications, such as in the fabrication of integrated circuits.Chinese Answer:半导体干法刻蚀工艺流程。

Metal干法刻蚀工艺介绍

PMD

n+

n+

STI

p+

p+

P-Well

N-Well

EPI

AL 还有什么作用?

Passivation (PE CVD)

Planarized PVD Al, CVD Al

IMD/CMP (PE / SA, HDP-CVD) Al Stack (PVD)

W Plug/CMP WCVD + CMP

均为ESC(Electrostatic Chuck)类型设备;

• P5K Metal:APPLIED公司产品, 高压力,单功率源设备. • DPS Metal:APPLIED公司产品,与TCP9600 同一代设备,

工作原理一致,都是低压力,双功率源设备。

TCP9600:

TCP9600:

TCP9600 圆 片 传 输 主 要 有 以 下7个步骤:

• 为什么要用AL? ✓ 电阻系数较低:2.65µΩ-cm ✓ 容易淀积, 价格便宜 ✓ 易腐蚀 ✓ 与介质层附着良好 ✓ 与衬底形成欧姆接触

与Cu相比呢?

✓ 铝膜中搀入Cu, Si的目的:防止电迁移(EM)、 小丘(Hillock )、硅 析出(Si Concrete)、铝刺(Al Spiking)

Metal形貌定义:

Metal形貌:

带胶形貌

dense

无胶形貌

open

负载效应(Microloading):

负载效应(microloading):不同的孔尺寸或纵深比例对腐蚀速率和

选择比的影响。

EXAMPLE OF PROFILE MICROLOADING

OPEN AREA

半导体工艺-干法刻蚀-铝刻蚀

干法刻蚀之铝刻蚀在集成电路的制造过程中,刻蚀就是利用化学或物理方法有选择性地从硅片表面去除不需要的材料的过程。

从工艺上区分,刻蚀可以分为湿法刻蚀和干法刻蚀。

前者的主要特点是各向同性刻蚀;后者是利用等离子体来进行各向异性刻蚀,可以严格控制纵向和横向刻蚀。

干法的各向异性刻蚀,可以用表面损伤和侧壁钝化两种机制来解释。

表面损伤机制是指,与硅片平行的待刻蚀物质的图形底部,表面的原子键被破坏,扩散至此的自由基很容易与其发生反应,使得这个方向的刻蚀得以持续进行。

与硅片垂直的图形侧壁则因为表面原子键完整,从而形态得到保护。

侧壁钝化机制是指,刻蚀反应产生的非挥发性的副产物,光刻胶刻蚀产生的聚合物,以及侧壁表面的氧化物或氮化物会在待刻蚀物质表面形成钝化层。

图形底部受到离子的轰击,钝化层会被击穿,露出里面的待刻蚀物质继续反应,而图形侧壁钝化层受到较少的离子轰击,阻止了这个方向刻蚀的进一步进行。

在半导体干法刻蚀工艺中,根据待刻蚀材料的不同,可分为金属刻蚀、介质刻蚀和硅刻蚀。

金属刻蚀又可以分为金属铝刻蚀、金属钨刻蚀和氮化钛刻蚀等。

目前,金属铝作为连线材料,仍然广泛用于DRAM和flash等存储器,以及0.13um 以上的逻辑产品中。

本文着重介绍金属铝的刻蚀工艺。

金属铝刻蚀通常用到以下气体:Cl2、BCl3、Ar、 N2、CHF3和C2H4等。

Cl2作为主要的刻蚀气体,与铝发生化学反应,生成的可挥发的副产物AlCl3被气流带出反应腔。

BCl3一方面提供BCl3+,垂直轰击硅片表面,达到各向异性的刻蚀。

另一方面,由于铝表面极易氧化成氧化铝,这层自生氧化铝在刻蚀的初期阻隔了Cl2和铝的接触,阻碍了刻蚀的进一步进行。

添加BCl3 则利于将这层氧化层还原(如方程式1),促进刻蚀过程的继续进行。

Al2O3 + 3B Cl3→ 2AlCl3 + 3BOCl (1)Ar电离生成Ar+,主要是对硅片表面提供物理性的垂直轰击。

N2、CHF3和C2H4是主要的钝化气体,N2与金属侧壁氮化产生的AlxNy,CHF3和C2H4与光刻胶反应生成的聚合物会沉积在金属侧壁,形成阻止进一步反应的钝化层。

半导体制造工艺流程简介 (2)

半导体NPN高频小功率晶体管制造的工艺流程为:外延片——编批——清洗——水汽氧化——一次光刻——检查——清洗——干氧氧化——硼注入——清洗——UDO淀积——清洗——硼再扩散——二次光刻——检查——单结测试——清洗——干氧氧化——磷注入——清洗——铝下CVD——清洗——发射区再扩散——三次光刻——检查——双结测试——清洗——铝蒸发——四次光刻——检查——氢气合金——正向测试——清洗——铝上CVD——检查——五次光刻——检查——氮气烘焙——检查——中测——中测检查——粘片——减薄——减薄后处理——检查——清洗——背面蒸发——贴膜——划片——检查——裂片——外观检查——综合检查——入中间库。

PNP小功率晶体管制造的工艺流程为:外延片——编批——擦片——前处理——一次氧化——QC检查(tox)——一次光刻—□□—QC检查——单结测试——磷注入——前处理——发射区氧化——前处理——发射区再扩散——前处理——POCl3预淀积(R□)——后处理——前处理——HCl退火、N2退火——三次光刻——QC检查——双结测试——前处理——铝蒸发——QC检查(t Al)——四次光刻——QC检查——前处理——氮氢合金——氮气烘焙——正向测试(ts)——外协作(ts)——前处理——五次光刻——QC检查——大片测试——测试ts——中测编批——中测——中测检查——入中间库。

变容管制造的工艺流程为:外延片——编批——擦片——前处理——一次氧化——QC检查——N+光刻——QC检查——前处理——干氧氧化——QC检查——P+注入——前处理——N+扩散——P+光刻——QC检查——硼注入1——前处理——CVD(LTO)——QC检查——硼注入2——前处理——LPCVD ——QC检查——前处理——P+扩散——特性光刻——电容测试——是否再加扩——电容测试——......(直到达到电容测试要求)——三次光刻——QC检查——前处理——铝蒸发——QC检查(t Al)——铝反刻——QC检查——前处理——氢气合金——氮气烘焙——大片测试——中测——电容测试——粘片——减薄——QC检查——前处理——背面蒸发——综合检查——入中间库。

半导体刻蚀工艺简介

半导体刻蚀⼯艺简介此保护膜可保护多晶硅的侧壁,进⽽形成⾮等向性刻蚀。

使⽤Cl2等离⼦体对多晶硅的刻蚀速率⽐使⽤F原⼦团慢很多,为兼顾刻蚀速率与选择⽐,有⼈使⽤SF6⽓体中添加SiCl4或CHCl3。

SF6的⽐例越⾼,刻蚀速率越快;⽽SiCl4或CHCl3的⽐例越⾼,多晶硅/SiO2的刻蚀选择⽐越⾼,刻蚀越趋向⾮等向性刻蚀。

除了Cl和F的⽓体外,溴化氢(HBr)也是⼀种常⽤的⽓体,因为在⼩于0.5µm的制程中,栅极氧化层的厚度将⼩于10nm,⽤HBr等离⼦体时多晶硅/SiO2的刻蚀选择⽐⾼于以Cl为主的等离⼦体。

4.⾦属的⼲法刻蚀⾦属刻蚀主要是互连线及多层⾦属布线的刻蚀,⾦属刻蚀有以下⼏个要求:⾼刻蚀速率(⼤于1000nm/min);⾼选择⽐,对掩蔽层⼤于4:1,对层间介质⼤于20:1;⾼的刻蚀均匀性;关键尺⼨控制好;⽆等离⼦体损伤:残留污染物少;不会腐蚀⾦属。

①铝的刻蚀。

铝是半导体制备中最主要的导线材料,具有电阻低、易于淀积和刻蚀等优点。

铝刻蚀通常采⽤加⼊卤化物的氯基⽓体,最常⽤的是BCl3。

因为铝在常温下表⾯极易氧化⽣成氧化铝,氧化铝阻碍了刻蚀的正常进⾏,⽽BCl3可将⾃然氧化层还原、保证刻蚀的进⾏,⽽且BCl3还容易与氧⽓和⽔反应,可吸收反应腔内的⽔汽和氧⽓,从⽽降低氧化铝的⽣成速率。

1.4质量评价⼀、⼲法刻蚀的终点监测近⼏年发展起来的⼲法刻蚀⼯艺,为了提⾼刻蚀精度,深⼊研究刻蚀机理,实现刻蚀设备的⾃动化,需要解决⼯艺过程的监控问题,特别是精确控制刻蚀终点。

因为⼲法刻蚀的选择性不如湿法,终点监控不当极易造成过腐蚀,甚⾄破坏下层图形。

早期的监控⽅法是计时法。

假设被刻蚀材料的膜厚已知,先通过实验确定刻蚀速率,然后在⼯艺过程中,由计时确定终点。

但由于影响刻蚀速率的因素太多(如压⼒、温度、流量、⽓体配⽐等),刻蚀速率难于重复(如前所述,对铝的等离⼦体刻蚀更是如此),不能满⾜⼯艺要求。

表1-1⼏种等离⼦体刻蚀终点检测⽅法⼆、⼲法刻蚀的质量检测刻蚀⼯艺的最后⼀步是进⾏检查以确保刻蚀的质量,通常都是⽤⾃动检测系统进⾏的。

半导体制造工艺_ 刻蚀

HBr/NF3/O2/SF6

浅Si沟槽

HBr/Cl2/O2

多晶硅

HBr/Cl2/O2, HBr/O2, BCl3/Cl2, SF6

Al

BCl3/Cl2, SiCl4/Cl2, HBr/Cl2

AlSiCu

BCl3/Cl2N2

W

只有SF6, NF3/Cl2

TiW WSi2,TiSi2,CoSi2

只有SF6 CCl2F2/NF3, CF4/Cl2, Cl2/N2/C2F6

35

其他高密度等离子体刻蚀机

由于ULSI的线宽持续缩小,逼近传统的RIE系统极限,除了ECR系统外,其他形式的高密度等离 子体源(HDP),如电感耦合等离子体源(ICP)、变压器耦合等离子体源(TCP)、表面波耦 合等离子体源(SWP)也已开始发展。这些设备拥有高等离子体密度与低工艺压强。 另外,HDP等离子体源对衬底的损伤较小(因为衬底有独立的偏压源与侧电极电势),并有高的 的各向异性(因为在低压下工作但有高活性的等离子体密度)。 然而,由于其复杂且成本较高,这些系统可能不会使用于非关键性的工艺,如侧壁间隔与平坦化 工艺。

氯基或溴基的化学剂对硅有高刻蚀速率,且对以二氧化硅为掩蔽层的硅刻蚀有高选择比。 HBr+NF3+SF6+O2混合气可用于形成深度约7um的沟槽电容,此气体也用于浅沟槽的刻蚀。亚 微米的深硅沟槽刻蚀时,常可观测到与高宽比有管的刻蚀,这是因深窄沟槽中的离子与中性原子 的输运会受到限制。

半导体刻蚀金属工艺流程

半导体刻蚀金属工艺流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!半导体刻蚀金属工艺是半导体制造过程中的关键步骤之一,它通过去除半导体表面的金属材料,形成所需的金属线路图案。

半导体刻蚀.

九.颗粒沾污

等离子体带来的硅片损伤有时也由 硅片表面附近的等离子体产生的颗粒沾 污而引起。研究表明,由于电势的差异, 颗粒产生在等离子体和壳层的界面处。 当没有了等离子体时,这些颗粒就会掉 到硅片表面。颗粒沾污的控制可通过优 化刻蚀设备,合适的操作和关机,对被 刻蚀的膜层选用合适的化学气体来达到。

包含带能离子、电子和激发分子的等 离子体可引起对硅片上的敏感器件引起 等离子体诱导损伤。一种主要的损伤是 非均匀等离子体在晶体管栅电极产生陷 阱电荷,引起薄栅氧化硅的击穿。差的 设备或在优化的工艺窗口之外进行刻蚀 工艺会使等离子体变得不均匀。另一种 器件损伤是能量离子对曝露的栅氧化层 的轰击。等离子体损伤有时可以通过退 火或湿法化学腐蚀消除。

聚合物的形成有时是有意的是为了在刻蚀图形的侧壁上形成抗腐蚀膜从而防止横向刻蚀见图128这样做能形成高的各向异性图形因为聚合物能阻挡对侧壁的刻蚀增强刻蚀的方向性从而实现对图形关键尺寸的良好控制

第十二章 刻 蚀

刻蚀是用化学或物理方法有选择地从 硅片表面去除不需要的材料的过程。刻蚀 的基本目标是在涂胶的硅片上正确的复制 掩膜图形。有图形的光刻胶层在刻蚀中不 受到腐蚀源显著的侵蚀。这层掩蔽膜用来 在刻蚀中保护硅片上的特殊区域而选择性 地刻蚀掉未被光刻胶保护的区域(见图 12.1)。在通常的CMOS工艺流程中刻蚀 都是在光刻工艺之后进行的。从这一点来 说,刻蚀可以看成在硅片上复制所想要的 图形的最后主要图形转移工艺步骤。

高密度等离子体刻蚀机中等离子体 通常处于磁场中。在等离子体刻蚀中采 用磁场的理由是: 1)产生的等离子体能更有效地获得 进入高深宽比窗口的高方向性低能离子 以及较少的硅片损伤; 2)等离子体密度较大,有更多的反 应基和带电粒子以增大刻蚀速率; 3)能减小硅片上的直流偏置电压, 从而可减少粒子轰击(或损伤)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

干法刻蚀之铝刻蚀

在集成电路的制造过程中,刻蚀就是利用化学或物理方法有选择性地从硅片表面去除不需要的材料的过程。

从工艺上区分,刻蚀可以分为湿法刻蚀和干法刻蚀。

前者的主要特点是各向同性刻蚀;后者是利用等离子体来进行各向异性刻蚀,可以严格控制纵向和横向刻蚀。

干法的各向异性刻蚀,可以用表面损伤和侧壁钝化两种机制来解释。

表面损伤机制是指,与硅片平行的待刻蚀物质的图形底部,表面的原子键被破坏,扩散至此的自由基很容易与其发生反应,使得这个方向的刻蚀得以持续进行。

与硅片垂直的图形侧壁则因为表面原子键完整,从而形态得到保护。

侧壁钝化机制是指,刻蚀反应产生的非挥发性的副产物,光刻胶刻蚀产生的聚合物,以及侧壁表面的氧化物或氮化物会在待刻蚀物质表面形成钝化层。

图形底部受到离子的轰击,钝化层会被击穿,露出里面的待刻蚀物质继续反应,而图形侧壁钝化层受到较少的离子轰击,阻止了这个方向刻蚀的进一步进行。

在半导体干法刻蚀工艺中,根据待刻蚀材料的不同,可分为金属刻蚀、介质刻蚀和硅刻蚀。

金属刻蚀又可以分为金属铝刻蚀、金属钨刻蚀和氮化钛刻蚀等。

目前,金属铝作为连线材料,仍然广泛用于DRAM和flash等存储器,以及0.13um 以上的逻辑产品中。

本文着重介绍金属铝的刻蚀工艺。

金属铝刻蚀通常用到以下气体:Cl2、BCl3、Ar、 N2、CHF3和C2H4等。

Cl2作为主要的刻蚀气体,与铝发生化学反应,生成的可挥发的副产物AlCl3被气流带出反应腔。

BCl3一方面提供BCl3+,垂直轰击硅片表面,达到各向异性的刻蚀。

另一方面,由于铝表面极易氧化成氧化铝,这层自生氧化铝在刻蚀的初期阻隔了Cl2和铝的接触,阻碍了刻蚀的进一步进行。

添加BCl3 则利于将这层氧化层还原(如方程式1),促进刻蚀过程的继续进行。

Al2O3 + 3BCl3→ 2AlCl3 + 3BOCl (1)

Ar电离生成Ar+,主要是对硅片表面提供物理性的垂直轰击。

N2、CHF3和C2H4是主要的钝化气体,N2与金属侧壁氮化产生的AlxNy,CHF3和C2H4与光刻胶反应生成的聚合物会沉积在金属侧壁,形成阻止进一步反应的钝化层。

一般来说,反应腔的工艺压力控制在6-14毫托。

压力越高,在反应腔中的Cl2浓度越高,刻蚀速率越快。

压力越低,分子和离子的碰撞越少,平均自由程增加,离子轰击图形底部的能力增强,这样刻蚀反应速率不会降低甚至于停止于图形的底部。

目前金属刻蚀机台广泛采用双射频功率源设计,如应用材料公司DPS(decouple plasma source)金属刻蚀机台。

偏置功率用来加速正离子,提供垂直的物理轰击,源功率

用来提高反应腔体内的等离子体的浓度。

这种双功率的设计可以实现对离子体的能量和浓度的独立控制,扩大了刻蚀工艺的工艺窗口和性能。

在金属铝的上下通常会淀积金属钛或氮化钛,形成氮化钛/铝/氮化钛/钛的结构。

用来刻蚀铝的Cl2与钛反应生成挥发性相对较低的TiCl4,刻蚀氮化钛的速率只有刻蚀铝的1/3-1/4,因此减少Cl2或是增加BCl3和偏置功率,都有利于提高氮化钛和钛的刻蚀速率。

在金属铝中通常会加入少量的硅和铜来提高电子器件的可靠性。

硅和Cl反应生成挥发性的SiCl4,很容易被带出反应腔。

铜与Cl反应生成的CuCl2挥发性却不高,因此需要加大物理性的离子轰击把铜原子去掉,一般可以通过加大Ar和增加偏置功率来实现。

当铝刻蚀完成之后,硅片表面、图形侧壁和光刻胶表面残留的Cl,会和铝反应生成AlCl3,继而与空气中的水分发生自循环反应(如方程式2),造成对铝的严重侵蚀(corrosion)。

因此,在刻蚀工艺完成后,一般会用H2O和O2的等离子体把氯和光刻胶去除, 并且在铝表面形成氧化铝来保护铝。