1_第一讲_基础知识

01第一章 集合与计数原理【讲义】

第一讲 集合与计数原理一、基础知识定义1 一般地,一组确定的、互异的、无序的对象的全体构成集合,简称集,用大写字母来表示;集合中的各个对象称为元素,用小写字母来表示,元素x 在集合A 中,称x 属于A ,记为A x ∈,否则称x 不属于A ,记作A x ∉。

例如,通常用N ,Z ,Q ,B ,Q +分别表示自然数集、整数集、有理数集、实数集、正有理数集,不含任何元素的集合称为空集,用∅来表示。

集合分有限集和无限集两种。

集合的表示方法有列举法:将集合中的元素一一列举出来写在大括号内并用逗号隔开表示集合的方法,如{1,2,3};描述法:将集合中的元素的属性写在大括号内表示集合的方法。

例如{有理数},}0{>x x 分别表示有理数集和正实数集。

定义2 子集:对于两个集合A 与B ,如果集合A 中的任何一个元素都是集合B 中的元素,则A 叫做B 的子集,记为B A ⊆,例如Z N ⊆。

规定空集是任何集合的子集,如果A 是B 的子集,B 也是A 的子集,则称A 与B 相等。

如果A 是B 的子集,而且B 中存在元素不属于A ,则A 叫B 的真子集。

定义3 交集,}.{B x A x x B A ∈∈=且 定义4 并集,}.{B x A x x B A ∈∈=或定义5 补集,若},{,1A x I x x A C I A ∉∈=⊆且则称为A 在I 中的补集。

定义6 差集,},{\B x A x x B A ∉∈=且。

定义7 集合},,{b a R x b x a x <∈<<记作开区间),(b a ,集合},,{b a R x b x a x <∈≤≤记作闭区间],[b a ,R 记作).,(+∞-∞定理1 集合的性质:对任意集合A ,B ,C ,有:(1));()()(C A B A C B A = (2))()()(C A B A C B A =; (3));(111B A C B C A C = (4)).(111B A C B C A C =定理2 加法原理:做一件事有n 类办法,第一类办法中有1m 种不同的方法,第二类办法中有2m 种不同的方法,…,第n 类办法中有n m 种不同的方法,那么完成这件事一共有n m m m N +++= 21种不同的方法。

第一讲 电厂化学基础知识

碱度和酸度

碱度:表示水中能接受氢离子的一类物质的量,在水 中碱度主要是OH-、1/2CO32-、HCO3-。天然水中的 碱度主要是HCO3-。 酸度:表示水中能接受氢氧根离子的一类物质的量, 在水中酸度主要有各种酸类及强酸弱碱盐,天然水中 的酸度主要是H2CO3。 阳床出水的酸度主要是强酸HCI、H2SO4。及碳酸 H2CO3。

• 例 某水分析结果为:Ca2+的浓度为60.0mg/L ; Mg2+的浓度为24.3mg/L,试用各种方法表示总硬度。 解:1/2Ca2+和1/2Mg2+的摩尔质量分别为20g/mol和 。 • YD=() • YD=5.0mmol/L×2.8 oG/ mmol/L =14 oG • YD=5.0 mmol/L×50 ppm/mmol/L=250ppm

碱度和酸度可用酸碱滴定法测定。

有机物

COD:

在一定的条件下,用一定的强氧化剂与水中各 种有机物及亚硝酸盐、亚铁盐、硫化物等作用, 然后将所消耗的氧化剂的量,计算折合成氧的 质量浓度,称为化学耗氧量,单位以mg/L来表 示。

有机物

BOD:

在指定的条件下,水中的有机物进行生物氧化时 所消耗溶解氧的量,即为生化需氧量,单位用 mg/LO2表示。

水的介电常数81 (25℃) 温度升高水的介电常数减小

水的的表面张力(20℃时为72.8×10-3N/m2) 温度升高水的表面张力减小

3. 高温(300℃以上)炉水的性质

高温炉水温度升高至接近临界点时:

水的临界点:

蒸气压直线上升

374.15 ℃ ,

水的密度直线下降 水蒸汽的密度直线上升 水的比热直线下降

TOC:

水样中的有机物在900℃高温和催化剂的条件下 气化、燃烧,这时水样中的有机碳和无机碳全部 氧测差化定即成 总 为C总的OC有2O,机2然量碳后和。利无用机红碳红产外生线的气C体O2分量析,仪两分者别只

第一讲1数列基础知识.docx

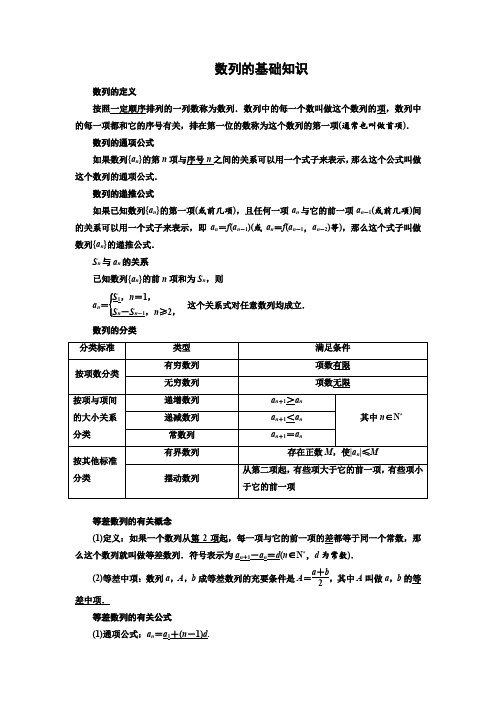

数列的基础知识数列的定义 按照一定顺序排列的一列数称为数列.数列中的每一个数叫做这个数列的项,数列中的每一项都和它的序号有关,排在第一位的数称为这个数列的第一项(通常也叫做首项). 数列的通项公式如果数列{a n }的第n 项与序号n 之间的关系可以用一个式子来表示,那么这个公式叫做这个数列的通项公式.数列的递推公式如果已知数列{a n }的第一项(或前几项),且任何一项a n 与它的前一项a n -1(或前几项)间的关系可以用一个式子来表示,即a n =f (a n -1)(或a n =f (a n -1,a n -2)等),那么这个式子叫做数列{a n }的递推公式.S n 与a n 的关系已知数列{a n }的前n 项和为S n ,则a n =⎩⎪⎨⎪⎧S 1,n =1,S n -S n -1,n ≥2,这个关系式对任意数列均成立. 数列的分类等差数列的有关概念(1)定义:如果一个数列从第2项起,每一项与它的前一项的差都等于同一个常数,那么这个数列就叫做等差数列.符号表示为a n +1-a n =d (n ∈N *,d 为常数).(2)等差中项:数列a ,A ,b 成等差数列的充要条件是A =a +b 2,其中A 叫做a ,b 的等差中项.等差数列的有关公式(1)通项公式:a n =a 1+(n -1)d .(2)前n 项和公式:S n =na 1+n (n -1)2d =n (a 1+a n )2. 等差数列的常用性质 (1)通项公式的推广:a n =a m +(n -m )d (n ,m ∈N *).(2)若{a n }为等差数列,且k +l =m +n (k ,l ,m ,n ∈N *),则a k +a l =a m +a n .(3)若{a n }是等差数列,公差为d ,则{a 2n }也是等差数列,公差为2d .(4)若{a n }是等差数列,公差为d ,则a k ,a k +m ,a k +2m ,…(k ,m ∈N *)是公差为md 的等差数列.(5)若数列{a n },{b n }是公差分别为d 1,d 2的等差数列,则数列{pa n },{a n +p },{pa n +qb n }都是等差数列(p ,q 都是常数),且公差分别为pd 1,d 1,pd 1+qd 2.等比数列的有关概念(1)定义:如果一个数列从第2项起,每一项与它的前一项的比等于同一常数(不为零),那么这个数列就叫做等比数列.这个常数叫做等比数列的公比,通常用字母q 表示,定义的表达式为a n +1a n=q . (2)等比中项:如果a ,G ,b 成等比数列,那么G 叫做a 与b 的等比中项.即:G 是a 与b 的等比中项⇔a ,G ,b 成等比数列⇒G 2=ab .等比数列的有关公式(1)通项公式:a n =a 1q n -1.(2)前n 项和公式:S n =⎩⎪⎨⎪⎧ na 1,q =1,a 1(1-q n )1-q=a 1-a n q 1-q ,q ≠1. 运用方程的思想求解等比数列的基本量(1)若已知n ,a n ,S n ,先验证q =1是否成立,若q ≠1,可以通过列方程(组)⎩⎪⎨⎪⎧ a n =a 1q n -1,S n =a 1(1-q n )1-q ,求出关键量a 1和q ,问题可迎刃而解. (2)若已知数列{a n }中的两项a n 和a m ,可以利用等比数列的通项公式,得到方程组⎩⎪⎨⎪⎧a n =a 1q n -1,a m =a 1q m -1,计算时两式相除可先求出q ,然后代入其中一式求得a 1,进一步求得S n .另外,还可以利用公式a n =a m ·q n-m 直接求得q ,可减少运算量.公式法与分组转化法(1)公式法 直接利用等差数列、等比数列的前n 项和公式求和.①等差数列的前n 项和公式:S n =n (a 1+a n )2=na 1+n (n -1)2d . ②等比数列的前n 项和公式: S n =⎩⎪⎨⎪⎧ na 1,q =1,a 1-a n q 1-q=a 1(1-q n )1-q ,q ≠1. (2)分组转化法若一个数列是由若干个等差数列或等比数列或可求和的数列组成,则求和时可用分组转化法,分别求和后相加减.倒序相加法与并项求和法(1)倒序相加法如果一个数列{a n }的前n 项中首末两端等“距离”的两项的和相等或等于同一个常数,那么求这个数列的前n 项和可用倒序相加法,如等差数列的前n 项和公式就是用此法推导的.(2)并项求和法在一个数列的前n 项和中,可两两结合求解,则称之为并项求和.形如a n =(-1)n f (n )类型,可采用两项合并求解.例如,S n =1002-992+982-972+…+22-12=(1002-992)+(982-972)+…+(22-12)=(100+99)+(98+97)+…+(2+1)=5 050.裂项相消法(1)把数列的通项拆成两项之差,在求和时中间的一些项可以相互抵消,从而求得其和.(2)常见的裂项技巧①1n (n +1)=1n -1n +1. ②1n (n +2)=12⎝⎛⎭⎫1n -1n +2. ③1(2n -1)(2n +1)=12⎝⎛⎭⎫12n -1-12n +1. ④1n +n +1=n +1-n .错位相减法如果一个数列的各项是由一个等差数列和一个等比数列的对应项之积构成的,那么这个数列的前n 项和即可用错位相减法来求,如等比数列的前n 项和公式就是用此法推导的.。

第一讲-OFFICE基础知识

常规查找: 编辑→查找 (1)若要限定查找的范围,则应选定文本区域,否 则系统将在整个文档范围内查找。 (2)选择“编辑”菜单栏中的“查找”命令或按 Ctrl+F组合键,打开“查找”对话框,如图所示。 (3)在“查找内容”编辑框内输入查找的字符串, 如“人生”。 (4)单击“查找下一处”按钮即开始进行查找工作。

第二部分: Excel知识要点

7、数据筛选: “数据”→“筛选”→“自动筛选”

注意: 若要移去数据列表的筛 选,重新显示所有数据,执行 “数据”→“筛选”→“全部 显示”命令即可。再执行“数 据”→“筛选”→“自动筛选” 就可以取消所有的筛选按钮。

第二部分: Excel知识要点

8、数据分类汇总: 数据→分类汇总

表达式。Value_if_true是logical_test为TRUE时返回的值。 Value_if_false是logical_test为FALSE时返回的值。例: 如果B3单元的值大于等于60,则IF(B3>=60,”合格”,”不合 格”)等于“合格”,否则等于“不合格”。

其他函数: MAX、MIN、AND.OR

2.编辑演示文稿: (1)设计模板:外观设计的整体调整 (2)母版: 幻灯片排版的整体调整

第三部分: PPT知识要点

2.编辑演示文稿: (3)配色方案

(4)设计幻灯片版式

第三部分: PPT知识要点

3.动画方案:

第三部分: PPT知识要点

4.超级链接: “幻灯片放映”→ “动作设置”

第三部分: PPT知识要点

第二部分: Excel知识要点

2.函数应用:

常用函数:

SUM函数 功能: SUM函数用于计算单个或多个参数之和。 语法: SUM(number1,number2,……) number1,number2,……为1到30个需要求和的参数。参数可以是: 逻辑值、数字、数字的文本形式、单元格的引用。例: SUM(10,20) 等于30;SUM(A1: E1)等于从A1到E1共5个单元格中数值的和。

物理高一第一讲知识点归纳总结

物理高一第一讲知识点归纳总结物理是一门研究物质和能量以及它们之间相互关系的自然科学。

在高中物理的学习过程中,我们需要掌握一系列的基础知识点,这些知识点将为我们建立起物理学的基础。

本文将对高一第一讲的物理知识点进行归纳总结,帮助同学们更好地理解和掌握这些内容。

1. 运动与力1.1 运动的描述物体的运动可以通过位置和时间的函数关系进行描述。

常见的描述方式有位移、速度和加速度。

1.2 牛顿第一定律牛顿第一定律也被称为惯性定律,指出物体在没有外力作用时将保持静止或匀速直线运动的状态。

1.3 牛顿第二定律牛顿第二定律描述了物体受力和加速度之间的关系。

公式为F=ma,其中F表示物体所受的力,m表示物体的质量,a表示物体的加速度。

1.4 牛顿第三定律牛顿第三定律指出:相互作用的两个物体之间,彼此的作用力大小相等、方向相反,且作用在两个物体上。

2. 动量与动量守恒定律2.1 动量的概念动量是物体的运动状态的量度,是质量和速度的乘积。

动量的单位是千克·米/秒。

2.2 动量守恒定律在一个封闭系统中,当没有外力作用时,系统的总动量保持不变。

即物体的动量在碰撞或相互作用过程中守恒。

2.3 弹性碰撞与非弹性碰撞弹性碰撞指的是碰撞前后物体的总动能保持不变的碰撞,而非弹性碰撞则是指碰撞过程中物体的总动能发生了改变的碰撞。

3. 力的合成与分解3.1 力的合成多个力作用在同一物体上时,可以通过合成这些力获得一个与它们等效的合力。

3.2 力的分解如果一个力可以分解成多个分力,那么这些分力的合力将等于原来的力。

4. 引力与重力4.1 引力的概念引力是两个物体之间相互作用的力。

根据万有引力定律,两个物体之间的引力与物体质量成正比,与它们之间距离的平方成反比。

4.2 重力的概念重力是地球对物体的吸引力。

根据万有引力定律,物体在地球表面上的重力大小与它的质量成正比。

5. 静电与电场5.1 电荷与电荷之间的相互作用电荷是物体所带的电性质,同种电荷相互排斥,异种电荷相互吸引。

第1讲 Pascal语言基础知识一

2)readln语句与read语句的第二个区别是:

read 后一定要有参数表,

readln可以不带参数表,即可以没有任何输入项, 只是等待读入一个换行符(回车)。经常用于暂停 程序的运行,直到输入一个回车

program ex1; var x1,x2,x3,x4,n:integer; begin n:=0; for x1:=1 to 10 do for x2:=1 to 20 do for x3:=1 to 50 do for x4:=1 to 100 do if (10*x1+5*x2+2*x3+x4=100)and(x1+x2+x3+x4=40) then n:=n+1; writeln(n); end.

三、基本语句

1、赋值语句

赋值语句是最简单的语句. 1)、赋值语句的格式 变量名:=表达式; 其中“:=”称为赋值号。 2)、执行过程 计算机先计算赋值号右边表达式的值,然后将表达式的值 赋给变量名代表的变量。 如:A:=(9*8)-(2-1)*a1; A:=A+1

2、输入语句read和readln 功能: 从键盘读入数据项,并把它存到变量中去,使该数据能在 以后的计算中使用。 输入语句的一般形式为: read(v1,v2,…,vn); readln(v1,v2,…,vn); 从键盘逐次读入数据,分别赋给变量v1,v2,…,vn, 一行输入多个变量值时,要求数据之间用空格分隔, readln语句要求输入数据后必须回车,使得后继操作从下 一行的头上开始。

第一讲 应用文写作基础知识

点评:

300多字已经浓缩了英雄光辉的一生和舍 己救人的英雄事迹,体现了应用文书叙述事 实材料的写作特征。

材料与观点的组织形式

(一)先列材料,后亮观点

先介绍事实,说明论据,或列举数字,然后归纳 观点、推出结论。 由事到理,说服力强。 常用于叙事性较强的片断。

(二)先亮观点,后列材料

常用层、段、条首句先概括亮出观点或问题,然 后列举事例、陈述观点。 或用理论材料和事实材料论述这个观点。 这种写法,观点鲜明,头绪清楚,先声夺人,引 人注目。

• 什么是应用文写作?

是机关或个体应用于日常工作和生活需要的一种 写作活动,应用文是应用写作的成果。

应用文的特点 1.广泛性。应用文是人类社会赖以处理事务、 沟通关系的书面工具。 2.实用性。应用文是为了处理事务、解决实 际问题而写的。 3.程式性。各类应用文一般都有惯用的格式, 这种比较固定的格式,有的是约定俗成 的, 即人们在长期的实际使用中形成的。

应用文的“五Biblioteka 素”: 主题、材料、结构、语言、表达方式。

第一节 主 题 一、什么是主题 主题,是作者通过文章的内容所表达出 来的基本观点或中心思想。主题是文章 的灵魂, 决定着文章的质量。 二、主题的特征 1.直露性。 2.完整性。

主题的要求

(一)正确 主旨正确的体现:

符合国家的法律、法规,符合党和国 家的路线、方针、政策。 符合客观实际情况,能反映客观事物 本质规律,经得起实践和时间的检验。 要符合本地区、本单位、本部门领导 的意图,切实可行。

如:《××人民政府关于严厉打击加工销售注 水猪肉非法行为的通知》一文,在提出问题、 说明“我市加工销售注水猪肉的不法行为十分 猖獗”之后,通过分析指出其“危害极大,侵 害群众利益,破坏肉猪声誉,扰乱市场正常秩 序”,然后转而提出:“各级人民政府及其有 关职能部门,要采取有力措施,坚决打击加工 销售注水猪肉的不法行为”,之后便引出7条 对策措施。而提出解决问题的对策和措施才是 该文的主旨。

第一讲_应用文写作基础知识和应用文概述

5、政策明确风格庄严

财经应用文是财经专业工作中的公务文书,它的 政策性很强。因此,在写作前,要认真学习有关 方针、政策,领会政策精神,掌握政策界限。在 写作中,要处处注意以政策为准绳,根据政策分 析问题,解决问题。

应用文写作风格要庄重、典雅、朴实、自然。

第二节 应用文的构成要素

应用文

或生歧义,古有“一字入公文,九牛拔不出”之说。

△《笑府》(冯梦龙) 清光一片照姑苏

△著名法国小说家福楼拜:“我们不论描写什么事物,要把 它表现出来,唯有一个名词;要赋于它运动,唯有一个动 词;要说明它的性质,唯有一个形容词,我们须继续不断 地苦心思索,非发现这唯一的名词、动词和形容词不可。”

△判断下列词句是否准确

2、通用事务类:包括调查报告、工作总结、述职报 告、简报、计划、规章制度和会议材料等。

3、个人事务类:如日记、读书笔记及各类信函等。

(二)专用文书:指专业性较强的文书。 1、科技类:如毕业论文、学术论文、专利申

请书和实验报告等。 2、财经类:如市场预测报告、市场调查报告

、经济活动分析报告及经济合同等。 3、司法类:如诉状、辩护词、公证书和判决

例:如《 2001 年经济形势展望》一开头就指出 : “展望 2001 年,经济回升的势头还比较微弱,促 进经济的持续向好仍然需要克服许多困难。” 开宗明 义,点明主题

(3)结尾点旨,这种方式是在文章的的结尾 之处点明文章主题。

例:《基础、应用科学与生产三者关系》一文

就是采用这一方法结尾。文章的结尾指出: “我再 重复一下,没有基础学科就没有应用学科,没有应 用学科就没有生产学科,三者是紧密结合在一起的 。” 非常清晰地显示了主题。

的主题是由作者直接表达出来显露在文章中的。 那么怎么才能做到主题从文章中显露出来呢?下面

1 奥林匹克化学竞赛培训纲要 基础知识

均裂(homolysis): 以上均为均裂,均裂能即为键能。

异裂(heterolysis): 异裂是分解成正负离子的方式。这种断 裂比均裂所需能量高4200 KJ/mole.。因此,在气相中,反应 均以均裂方式进行,而在液相中的反应,尤其在极性溶剂中, 由于溶剂的溶剂化效应,异裂变得较容易进行。所以,在极性 溶剂中反应均以异裂方式进行。

H2的分子轨道

1

2

乙烯的分子轨道 C C

σ-键

HC H

π-键

H CH

乙炔的分子轨道

CC

HCC H

σ-键

π-键

1.5.4 有机化合物的表示方法

构造简式,如:CH3CH2CH3, (CH3)3CCH2CH3等。 键线式,如:

PDF created with pdfFactory Pro trial version

第一讲:基础知识

1.1 有机化合物 定义:从有机体中得到的化合物叫有机化合物 有机化合物的特性:

1. 易燃(少数不燃烧,如聚四氟乙烯); 2. 不溶于水(因无极性,少数溶于水); 3. 不导电; 4. 熔点低(极少数超过300℃); 5. 反应速度慢,副反应多。

PDF created with pdfFactory Pro trial version

1.5.3.2 原子轨道理论Atomic orbital theory:

要点:

1.原子轨道: 原子中电子的运动状态叫原子轨道, 用波函数 φ表示,它是电子运动的空间坐标的函数。电子绕原子核运 动无固定路线,在某一点周围出现的几率与φ2成正比。统 计的结果象一团云,离核越近,密度越大。原子轨道即电子 云出现几率大的区域。如:

如:已知某化合物的分子量为60,C、H、O的含量分别为 60.00%、13.40% 和26.60,

第一讲文献信息检索基础知识

(三)不同加工层次的文献信息

一次文献

二次文献

三次文献

按文献 的加工 深度分

一次文献

* 作者以自己的研究成果为基础创作或撰写, 并通过某种渠道而公开的文献;

* 对知识的第一次加工;具有创造性; * 大多数期刊论文、科技报告、学位论文、会

议文献、专利文献、技术档案等。

二次文献

* 对一次文献进行浓缩、整序及加工处理而成 的具有报道和检索作用的文献;

报纸

是以报道新闻及评论 为主,出版周期比期刊 更短,多为活页性连续 出版物。其特点是内容 丰富、信息量大、出版 迅速、发行量大、读者 众多。

科技报告

科技报告是科技工作者对科学、技术研究结果或研 究进展的记录。

科技报告的特点

(1)反映新的科研成果迅速; (2)内容多样化; (3)质量参差不齐; (4)保密性强; (5)每份报告独立成册,有连续编号。

第一讲文献信息检索基础 知识

第一节 信息与信息素养 第二节 科技文献的类型 第三节 信息检索与文献检索工具 第四节 信息检索原理 第五节 信息检索的方法和途径 第六节 信息检索常用技术及检索效果评价

第一节 信息与信息素养

一、信息的基本含义

1、图书馆学和情报学领域,信息被定义为事物 或记录。 2、综合学术界对信息的定义,可以认为信息是 以物质介质为载体,传递和反映世界各种事物存 在方式、运动规律及特点的表征。

美国信息产业协会主席保罗 . 泽考斯基(Paul Zurkowaski)1974年在美国全国图书馆与情报学委 员会上,最早提出了信息素养的概念,他把信息素 养概括为:“利用大量的信息工具及主要信息源使 问题得到解答的技术和技能。”

信息素养为什么重要

在科技飞速发展、信息资源激增的当今时代,信息 素养越来越显示其重要性

1、运动学基础知识一

1、运动学基础知识⼀第⼀讲:运动的描述⼀知识点⼀、质点1、定义:⽤来代替物体的有质量的点叫做质点。

2、使⽤条件:物体的⼤⼩、形状对所研究问题的影响可以忽略不计时,可视物体为质点。

理解:(1)、物体的⼤⼩、形状对所研究问题的影响可以忽略不计时,可视物体为质点。

(2)、质点不是很⼩的点,不能简单的认为很⼩的物体就可以看作质点,也不能说很⼤的物体就不能看作质点;(3)、同⼀个物体,在不同的情况下,有时可以看作质点,有时不可以看作质点。

例如:例1、下列物体可以当作质点的是()A、研究地球⾃转对昼夜变化影响时的地球B、研究⽉球公转周期时的⽉球C、判断100⽶短跑运动员撞线先后时的运动员D、要研究运动时间时,从北京到⼤同的⽕车例2、在研究下列问题时,可以把汽车看作质点的是()A、研究汽车在通过⼀座桥梁时所⽤的时间B、研究⼈在汽车上的位置C、研究汽车在上坡时有⽆翻到的危险D、计算汽车从云冈⽯窟开往实验⼆中的时间知识点⼆、坐标系1、坐标系:要准确的描述物体的位置及位置的变化需要建⽴坐标系。

2、坐标系的种类:(1)、直线坐标系;(2)、平⾯直⾓坐标系;(3)、空间坐标系;知识点三、时间与时刻1、时间:时间段,有长短。

例如:前4S内,第5S内,后2S内,等2、时刻:时间点,⽆长短。

例如:第4S初,第7S末,等注意:第4S初和第3S末是同⼀时刻。

3、时间的单位:秒、分钟、⼩时,符号:S、min、h。

例4、以下的计时数据指时间间隔的是()A.从北京开往⼴州的⽕车预计10时到站 B.“神⾈”六号点⽕倒计时…2、1、0C.某⼈百⽶跑的成绩是13s D.某场⾜球赛开赛了15min时主队攻⼊⼀球例5、在图中所⽰的时间轴上标出的是下列哪些时间或时刻()A.第4s初 B.第3s末 C.第3s D.前3s知识点四、标量与⽮量1、标量:只有⼤⼩,没有⽅向;运算遵从算数法则。

例如:长度、质量、时间、路程、温度、能量、等。

2、⽮量:既有⼤⼩,⼜有⽅向;求和运算遵从平⾏四边形定则。

第一讲:地球知识-经纬网(好)

安徽含山中学

地球—经纬网—纬线

特 点—— 1.都自成圆圈——纬线圈。 2.赤道最长,往两极纬线

圈越来越小两极为点。

3.所有的纬线都相互平行。 4.纬线指示东西方向。 (相对的)

安徽含山中学

N

经纬线小结

纬线 定义

线圈 形状 长度 顺着东西方向,环绕地 球一周的圆圈 圆,所以又称纬线圈, 赤道平分地球

S

欧洲 亚洲

非洲

大洋洲 南极洲

北美洲

南美洲 南极洲

北半球

南北半 球划分

南半球

北半球 赤道

南半球

安徽含山中学

北美洲

非洲

欧洲

亚洲

大洋洲 非洲 南极洲

南美洲

三、经度和纬度

划分方法 判断方法 度数向东增大为__经,向 西增大为_经 西 应用

东 经,以西 经 0°经线以东为___ 西 经,东西各有180 度 为____ ___度。

劣弧定向法 在以极地为中心的经纬网图上,判断东西方 位的最简捷方法是在相比较的两地之间的劣弧上 ,画出地球自转方向箭头,箭尾为西,箭头为东(

如上图)。根据图中南极点(S),我们先画出A、B

两点间的地球自转方向箭头,根据上述法则,B

点在A点的东方,C点在D点的东南方向。

练习

165° 150° 135° 120° 105°

180°

165° 150° 135° 120° 105°

90°

北极

90°

75° 60° 45°

75° 60°

45°

30° 15° 0° 15° 30°

西经

东经

安徽含山中学

90°

75° 60°

45°

30°

第一讲 传热基础知识

Q q A

式中 A──总传热面积,m2。

二、稳态与非稳态传热 非稳态传热 Q , q , t f x , y , z , 稳态传热

Q , q, t f x , y , z

t 0

三、冷热流体通过间壁的传热过程

T1 Q t2

对流 导热 对流 冷 流 体

式中 K──总传热系数,W/(m2·℃)或W/(m2·K); Q──传热速率,W或J/s; A──总传热面积,m2; tm──两流体的平均温差,℃或K。

2.4.2 热量衡算和传热速率方程间的关系

热流体 G1, T1,cp1,H1

t2 h2

冷流体 G2, t2,cp2,h1 T2 H2

无热损失: Q吸 Q放

t1

t T1 t2 T2 t1 A

t1 t 2 t m t1 ln t 2

t2

t1 T 1t 2

t 2 T2 t1

T1 t1 t t2 dt dA dT t t t1 T T2 t2

t1 T 1t 2

A

t 2 T2 t1

1)也适用于并流

2.4.6 壁温的计算

稳态传热 Q KAt m

T TW Tw tW tw t 1 b 1 1 A1 Am 2 A2

Q T 1 A1

tW

bQ TW Am

TW

tW

Q t 2 A2

1.大,即b/Am小,热阻小,tW=TW

2.当tW=TW,得

d1 1 1 b d1 1 d1 R1 R2 dm d2 2 d2 K 1

式中 R1、R2——传热面两侧的污垢热阻,m2·K/W。

列管换热器总传热系数K的经验数据

第一讲概率论基本知识

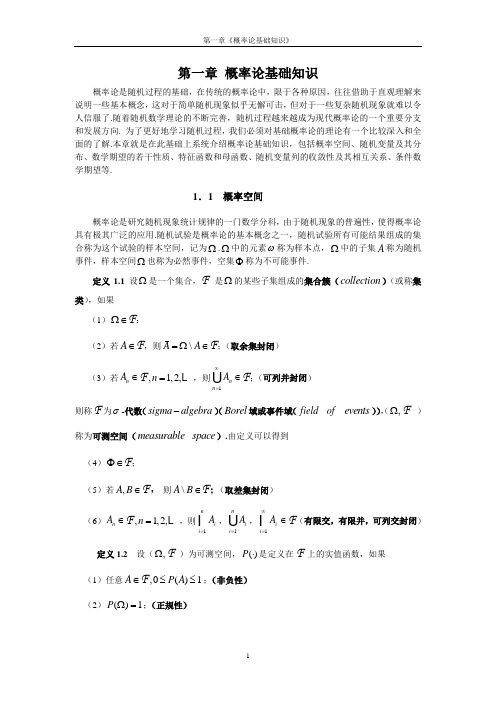

第一章 概率论基础知识概率论是随机过程的基础,在传统的概率论中,限于各种原因,往往借助于直观理解来说明一些基本概念,这对于简单随机现象似乎无懈可击,但对于一些复杂随机现象就难以令人信服了.随着随机数学理论的不断完善,随机过程越来越成为现代概率论的一个重要分支和发展方向. 为了更好地学习随机过程,我们必须对基础概率论的理论有一个比较深入和全面的了解.本章就是在此基础上系统介绍概率论基础知识,包括概率空间、随机变量及其分布、数学期望的若干性质、特征函数和母函数、随机变量列的收敛性及其相互关系、条件数学期望等.1.1 概率空间概率论是研究随机现象统计规律的一门数学分科,由于随机现象的普遍性,使得概率论具有极其广泛的应用.随机试验是概率论的基本概念之一,随机试验所有可能结果组成的集合称为这个试验的样本空间,记为Ω.Ω中的元素ω称为样本点,Ω中的子集A 称为随机事件,样本空间Ω也称为必然事件,空集Φ称为不可能事件.定义 1.1 设Ω是一个集合,F 是Ω的某些子集组成的集合簇(collection )(或称集类),如果 (1)Ω∈F ;(2)若A ∈F ,则\A A =Ω∈F ;(取余集封闭) (3)若n A ∈F ,1,2,n = ,则1n n A ∞=∈ F ;(可列并封闭)则称F 为σ-代数(sigma algebra -)(B orel 域或事件域(field of events )),(,ΩF )称为可测空间(m easurable space ).由定义可以得到 (4)Φ∈F ;(5)若,A B ∈F ,则\A B ∈F ;(取差集封闭)(6)n A ∈F ,1,2,n = ,则1ni i A = ,1ni i A = ,1i i A ∞= ∈F (有限交,有限并,可列交封闭)定义1.2 设(,ΩF )为可测空间,()P ⋅是定义在F 上的实值函数,如果 (1)任意A ∈F ,0()1P A ≤≤;(非负性) (2)()1P Ω=;(正规性)(3)对两两互不相容事件12,,A A (当i j ≠时,i j A A =Φ ),有11()i ii i P A P A ∞∞==⎛⎫=⎪⎝⎭∑ (可列可加性). 则称P 是(,Ω F)上的概率(p r o b a b i l i ),(,ΩF ,P )称为概率空间(probability space ),()P A 为事件A 的概率. 由定义知(4),A B ∈F ,A B ⊂,则(\)()()P B A P B P A =- (可减性)一事件列{,1}n A n ≥称为单调增列,若1,1n n A A n +⊂≥;称为单调减列,若1,n n A A +⊃1n ≥. 显然,如果{,1}n A n ≥为单调增列,则1lim n in i A A∞→∞==;如果{,1}n A n ≥为单调减列,则1lim n in i A A∞→∞==.(5)(概率的连续性)若{,1}n A n ≥是递增或递减的事件列,则lim ()(lim )n n n n P A P A →∞→∞=定义1.3 设(,ΩF ,P )为概率空间,B ∈F ,且()0P B >,如果对任意A ∈F ,记()(|)()P AB P A B P B =则称(|)P A B 为事件B 发生条件下事件A 发生的条件概率(conditional probability ). 由条件概率的定义可得到: (1)乘法公式 设,A B ∈F ,则()()(|)P AB P B P A B =一般地,若i A ∈F ,1,2,,i n = ,且121()0n P A A A -> ,则121121312121()()(|)(|)(|)n n n P A A A P A P A A P A A A P A A A A --=(2) 全概率公式 设(,ΩF ,P )是概率空间,A ∈F ,i B ∈F ,1,2,,i n =()i j B B i j =Φ≠,且1,()0,ni i i B P B ==Ω> ,则1()()(|)niii P A P B P A B ==∑(3) (Bayes 公式)设(,ΩF ,P )是概率空间,A ∈F ,i B ∈F ,1,2,,i n =()i j B B i j =Φ≠,且1,()0,()0ni i i B P B P A ==Ω>> ,则1()(|)(|)()(|)i i i niii P B P A B P B A P B P A B ==∑一般地,若12,,,n A A A ∈ F ,有11()()nni ii i P A P A ===∏ , 则称F 为独立事件簇.1.2 随机变量及其分布随机变量是概率论的主要研究对象之一,随机变量的统计规律用分布函数来描述. 定义 1.4 设(,ΩF ,P )为概率空间,()X X ω=是定义在Ω上的实值函数,如果对于任意实数x ,有()1(,]Xx --∞={}:()X x ωω≤∈F ,则称()X ω为F上的随机变量(random variable ),简记为..r v X .随机变量实质上是(,ΩF )到(,R B ()R )上的可测映射(函数),记1(){()|X XB B σ-=∈B ()R }⊂F ,称()X σ为随机变量X 所生成的σ域.称{}()1()():()((,])(,]F x P X x P X xP X x P Xx ωω-=≤=≤=∈-∞=-∞为随机变量X 的分布函数(distribution function )(简记.d f ).由定义,分布函数有如下性质:(1)()F x 为不降函数:即当12x x <时,有12()()F x F x ≤; (2)()lim ()0,x F F x →-∞-∞==()lim ()1x F F x →+∞+∞==;(3)()F x 是右连续的,即()()F x F x ο+=可以证明,定义在R 上的实值函数()F x ,若满足上述三个性质,必能作为某个概率空间(,ΩF ,P )上某个随机变量的分布函数.推广到多维情形,类似可得到定义 1.5 设(,ΩF ,P )为概率空间,()12()(),(),,()n X X X X X ωωωω== 是定义在Ω上的n 维空间n R 中取值的向量实值函数.对于任意12(,,,)n n x x x x R =∈ ,有{}1122:(),(),,()n n X x X x X x ωωωω≤≤⋅⋅⋅≤∈F ,则称()X X ω=为n 维随机变量,称12()(,,,)n F x F x x x P =⋅⋅⋅={}1122:(),(),,()n n X x X x X x ωωωω≤≤⋅⋅⋅≤为()12()(),(),,()n X X X X X ωωωω==⋅⋅⋅的联合分布函数.随机变量有两种类型:离散型随机变量和连续型随机变量,离散型随机变量的概率分布用概率分布列来描述:(),1,2,k k p P X x k === ,其分布函数为()k k x xF x p ≤=∑;连续型随机变量的概率分布用概率密度函数()f x 来描述,其分布函数为()()x F x f t dt -∞=⎰.类似地可定义n 维随机变量12(,,,)n X X X X = 的联合分布列和联合分布函数如下: 对于离散型随机变量12(,,,)n X X X X = ,联合分布列为()121122,,,n x x x n n p P X x X x X x ====其中,i i i x I I ∈为离散集,1,2,,i = n ,X 的联合分布函数为: 1,12,,121,2,,(,,,)(,,,)n i i nn x x n x y i n F y y y p y y y R ≤==⋅⋅⋅∈∑对于连续型随机变量12(,,,)n X X X X = ,如果存在n R 上的非负函数12(,,,)n f x x x ,对于任意12(,,,)nn y y y R ∈ ,有12(,,,)n X X X X = 的联合分布函数12121212(,,,)...(,,,)n y y y n n n F y y y f x x x dx dx dx -∞-∞-∞⋅⋅⋅=⋅⋅⋅⋅⋅⋅⎰⎰⎰12(,,,)n f x x x 为X 的联合密度函数.1.3 数学期望及其性质设()X X =⋅是定义在概率空间(,ΩF ,P )上的.r v ,如果||X dP Ω<∞⎰,就称.r v .X的数学期望(expectation )或均值存在(或称.r v .X 是可积的),记为E X ,有下列定义:EX XdP Ω=⎰利用积分变换,也可写成()EX xdF x +∞-∞=⎰.设()g x 是1R 上的B orel 可测函数,如果.r v .()g X 的数学期望存在,即|()|E g X <∞,由积分变换可知()()()()Eg X g X dP g x dF x +∞Ω-∞==⎰⎰设k 是正整数,若.r v .k X 的数学期望存在,就称它的k 阶原点矩(k th -moment aboutthe origin ),记为k α,即()kkk EXx dF x α+∞-∞==⎰设k 是正整数,若.r v .||k X 的数学期望存在,就称它的k 阶绝对原点矩(k th - absolute m o m e n tabout the origin ),记为k β,即 ||||()kkk E X x dF x β+∞-∞==⎰类似地,X 的k 阶中心矩(k th - central moment )k μ和k 阶绝对中心矩(k th -absolutely central moment )k υ分别定义为1()()()kkk E X EX x dF x μα+∞-∞=-=-⎰1||||()kkk E X EX x dF x να+∞-∞=-=-⎰我们称二阶中心矩为方差(variance ),记为V a r X 或D X ,显然有22221VarX μναα===-关于数学期望,容易验证下列的性质:(1)若.r v .X ,Y 的期望E X 和E Y 存在,则对任意实数,αβ,()E X Y αβ+也存在,且()E X Y EX EY αβαβ+=+(2)设A ∈F ,用A I 表示集A 的示性函数,若E X 存在,则()A E XI 也存在,且()A AE XI XdP =⎰(3)若{}k A 是Ω的一个划分,即()i j A A i j =Φ≠ ,且i iA Ω= ,则iA i EX XdP XdP Ω==∑⎰⎰关于矩的存在性,有如下的必要条件和充分条件定理1.1 设对.r v X 存在0p >,使||pE X <∞,则有lim (||)0px x P X x →∞≥=定理1.2 设对.r v X 0(.)a s ≥,它的.d f 为()F x ,那么E X <∞的充要条件是(1())F x dx ∞-<∞⎰此时EX =(1())F x dx ∞-⎰推论1.1 ||E X <∞的充要条件是0()F x dx -∞⎰与0(1())F x dx +∞-⎰均有限,这时有EX =(1())F x dx ∞-⎰()F x dx -∞-⎰推论 1.2 对于0,||pp E X <<∞<∞的充要条件是11(||)p n P X n ∞=≥<∞∑,也等价于11(||)p n nP X n ∞-=≥<∞∑1.4 特征函数和母函数特征函数是研究随机变量分布又一个很重要的工具,用特征函数求分布律比直接求分布律容易得多,而且特征函数有良好的分析性质.定义 1.6 设X 是n 维随机变量(随机向量),分布函数为()F x ,称()F x 的Fourier Stieltjes -变换()()(),itXitxg t E ee dF x t ∞-∞==-∞<<∞⎰为X 的特征函数(characteristic function ).简记.c f从本质上看,特征函数是实变量t 的复值函数,随机变量的特征函数一定是存在的. 当X 是离散型随机变量,分布列(),1,2,k k p P X x k === ,则1()kitx k k g t ep ∞==∑当X 是连续型随机变量,概率密度函数为()f x ,则()(),itxg t ef x dx t ∞-∞=-∞<<∞⎰从定义,我们能够看出特征函数有如下性质: (1)(0)1;g =(2)(有界性)|()|1;g t ≤ (3)(共轭对称性)()();g t g t -=(4)(非负定性)对于任意正整数n 及任意实数12,,,n t t t 和复数12,,,n z z z ,有,1()0nk l k l k l g t t z z =-≥∑(5)(连续性)()g t 为n R 上一致连续函数;(6)有限多个独立随机变量和的特征函数等于各自特征函数的乘积,即随机变量12,,,n X X X 相互独立,12n X X X X =+++ 的特征函数为:12()()()()n g t g t g t g t =其中()i g t 为随机变量i X 的特征函数;(7)(特征函数与矩的关系)若随机变量X 的n 阶矩n EX 存在,则X 的特征函数()g t 可微分n 次,且当k n ≤时,有()(0)k k k g i EX =;(8)随机变量的分布函数由其特征函数唯一确定.定理1.3 (B ocher 定理) n R 上函数()g t 是某个随机变量特征函数当且仅当()g t 连续非负定且(0)1g =.定理1.4 (逆转公式) 设()F x 是随机变量X 的分布函数,相应的特征函数为()g t 若12,x x 为()F x 的连续点,则12211()()lim()2itx itx TT Tee F x F x g t dt itπ--→∞---=-⎰很显然,具有相同特征函数的两个分布函数是恒等的.由此还可推出一个事实:一个随机变量是对称的,当且仅当它的特征函数是实的. 事实上,由X 的对称性知X 和X -有相同的分布函数,根据定义()()()itX itXg t E e E eg t g t -===-=,也就是说()g t 是实的;反之,从()()()itX itXg t Ee g t g t Ee -===-=知X 和X -有相同的特征函数,因此,它们的分布函数相等,这说明X 是对称的.例1.1 设X 服从(,)B n p ,求X 的特征函数()g t 及2,,EX EX D X解 X 的分布列为{},1,0,1,2,,k k n kn P X k C p q q p k n -===-=()()()n nitxk k n kk it k n kit nnnk k g t eC p qCpe qpe q --=====+∑∑因此 0(0)()|itt d E X ig ipe qnp dt='=-=-+=22222202()(0)()()|it t d EXi g i pe q npq n p dt=''=-=-+=+故 22()D X EX EX npq =-= 例1.2 设~(0,1)X N ,求X 的特征函数()g t解 22()itx xg t edx ∞--∞=由于2222||||itx xxixe xe--=221||xx edx ∞--∞<∞⎰,可对上式两边求导,得2222()()itx xitx xg t ixedx e de∞∞---∞-∞'==-⎰2222()x x itx itx edx tg t ∞∞---∞-∞=--=-于是得到微分方程 ()()g t t g t '+=. 这是变量可分离型方程,有()()dg t tdt g t =-两边积分得 2l n ()2g t tc=-+,得方程的通解为 22()tcg t e -+=.由于(0)1g =,因此,0c =.于是X 的特征函数为22()tg t e -=例1.3 设,X Y 相互独立,~(,),~(,)X B n p Y m p ,证明:~(,)X Y n m p ++ 证明 ,X Y 的特征函数分别为()(),()(),1itnitmX Y g t q pe g t q pe q p =+=+=-X Y +的特征函数为()()()(),1it n mX Y X Y g t g t g t q pe q p ++==+=-即X Y +的特征函数是服从参数为,n m p +二项分布的特征函数,由唯一性定理~(,)X Y n m p ++附表一给出了常用分布的均值、方差和特征函数.在研究只取非负整数值的随机变量时,以母函数代替特征函数比较方便.定义1.7 设随机变量X 的分布列为(),0,1,2,k p P X k k === 其中01k k p ∞==∑,称()()kk k k P s E s p s ∞===∑为X 的母函数(或称概率生成函数)(p r o b a b i l i t y generating function ).母函数具有下列性质:(1)非负整数值随机变量的分布列由其母函数唯一确定; (2)(1)1P =,()P s 在||1s ≤绝对且一致收敛;(3)若随机变量X 的l 阶矩存在,则可以用母函数在1s =的导数值来表示,特别地, 有2(1),(1)(1)EX P EXP P ''''==+;(4)独立随机变量之和的母函数等于母函数的积.证明 (1)01(),0,1,2,nkkkk k k k k k n P s p s p s p s n ∞∞===+==+=∑∑∑两边对s 求n 阶导数,得到()1()!(1)(1)n k nn k k n Ps n p k k k n p s∞-=+=+--+∑令0s =,则()(0)!n n p n p =,因此()(0),0,1,!n n pp n n ==(3)由0()kk k P s p s ∞==∑,得到11()k kk P s kps∞-='=∑,令1s ↑,得到1(1)kk EX kpP ∞='==∑,类似可得到 2(1)(1)E X PP '''=+ 例1.4 从装有号码为1,2,3,4,5,6的小球的袋中,有放回地抽取5个球,求所得号码总和为15的概率.解 令i X 为第i 次取得的小球的号码,且i X 相互独立,125X X X X =+++ 为所取的球的号码的总和.i X 的母函数为261()()6i P s s s s =+++X 的母函数为 5265655551()()(1)(1)66s P s s s s s s -=+++=--所求概率为()P s 展开式的15s 的系数,因此,5651{15}6P X ==1.5 随机变量列的收敛性定义 1.8设{},;1n X X n ≥概率空间(,ΩF ,P )上随机变量,如果存在集A ∈F ,()0P A =,当cA ω∈时,有lim ()()n n X X ωω→∞=,则称n X 几乎处处收敛(convergencealm ost everywhere )到X ,简称n X ..a s 收敛到X ,记为n X X → ..a s下面我们给出..a s 收敛的一个判别准则.定理1.5 n X X → ..a s 的充分必要条件是任一ε>0,有lim (||)0m n m n P X X ε∞→∞=⎧⎫-≥=⎨⎬⎩⎭下面给出定理1.3的一个应用.例1.5 设{}n X 是..r v 列,且11()()2n n n P X n P X n +===-=,1111122n n n P X P X n n ⎧⎫⎧⎫⎛⎫===-=-⎨⎬⎨⎬ ⎪⎩⎭⎩⎭⎝⎭对于给定的ε>0,考虑1n ε>,有 1(||)0,2m mm nm n P X n ε∞∞==⎧⎫≥≤→→∞⎨⎬⎩⎭∑,因此 0n X →,..a s定义1.9 设{},;1n X X n ≥概率空间(,ΩF ,P )上随机变量,如果对任一0ε>,{}lim ||0n n P X X ε→∞-≥=则称n X 依概率收敛(convergence in probability )到X ,简记Pn X X −−→. 由定义,n X 依概率收敛到X ,那么极限随机变量X ..a s 是唯一的.定义 1.10 设{},;1n X X n ≥概率空间(,ΩF ,P )上随机变量,若||rn E X (0r >)存在,且lim ||0rn n E X X →∞-=,则称 n X r 阶平均收敛(convergence in mean oforder r )到X ,特别地,当2r =时,称为均方收敛.定义1.11 设{},;1n X X n ≥概率空间(,ΩF ,P )上随机变量,其分布函数序列()n F x 满足lim ()()n n F x F x →∞=在每个()F x 连续点处成立,则称n X 依分布收敛(convergence indistribution )到X .简记dn X X −−→.这里()F x 为X 的分布函数.下面我们不加证明地给出几种收敛之间的关系.a sPn n X X X X −−→⇒−−→dn X X ⇒−−→⇓..k a s n X X −−→且11(||)2kn kk P X X ∞=-≥<∞∑⇑,r rn n X X X X '−−→⇒−−→ 0r r '<< 1.6 条件数学期望设,X Y 是离散型随机变量,对一切使{}0P Y y =>的y ,定义给定Y y =时,X 的条件概率为 {,}{|}{}P X x Y y P X x Y y P Y y ======;给定Y y =时,X 的条件分布函数为(|){|}F x y P X x Y y =≤=; 给定Y y =时,X 的条件期望为(|)(|){|}xE X Y y xdF x y xP Xx Y y =====∑⎰设,X Y 是连续型随机变量,其联合密度函数为(,)f x y ,对一切使()0Y f y ≥,给定Y y =时,X 的条件密度函数为(,)(|)()Y f x y f x y f y =;给定Y y =时,X 的条件分布函数(|){|}F x y P X x Y y =≤==(|)xf x y dx ⎰; 给定Y y =时,X 的条件期望定义为 (|)(|)(|)E X Y y x d F x y x f x y d x===⎰⎰由定义可以看出,条件概率具有无条件概率的所有性质.(|)E X Y y =是y 的函数,y 是Y 的一个可能值,若在Y 已知的条件下,全面考察X 的均值,需要用Y 替代y ,(|)E X Y y =是Y 的函数,显然,它也是随机变量,称为X 在Y 条件下的条件期望(conditional expectation ).条件期望在概率论、数理统计和随机过程中是一个十分重要的概念,下面我们列举以下性质:设,,X Y Z 为随机变量,()g x 在R 上连续,且,,,[()]EX EY EZ E g Y Z ⋅都存在. (1) 当X 和Y 相互独立时,(|)E X Y EX =; (2) [(|)]EX E E X Y =;(3) [()|]()(|)E g Y X Y g Y E X Y ⋅=; (4) (|)E c Y c =,c 为常数;(5) (线性可加性)[()|](|)(|)E aX bY Z aE X Z bE Y Z +=+ (,a b 为常数); (6) 若0,X ≥则(|)0,..E X Y a s ≥ 下面只对(2)和(3)证明:证明 (2)离散型情况.设(,)X Y 的联合分布列为{,},,1,2,i j ij P X x Y y p i j ====则 [(|)](|){}jj j y E E X Y E XY y P Y y ===∑{|}{}ji i i j j y x x P X x Y y P Y y ⎡⎤====⎢⎥⎣⎦∑∑ {,}{}ji ii i j i y x x x P X x Y y P Xx EX ⎡⎤======⎢⎥⎣⎦∑∑∑由此可见,E X 是给定j Y y =时X 条件期望的一个加权平均值,每一项(|)j E X Y y =所加的权数是作为条件事件的概率,称(|){}jj j y EX E XY y P Y y ===∑为全期望公式.连续型情形:设(,)X Y 的联合密度函数为(,)f x y ,则[](|)(|)()(|)()Y Y E E X Y E X Y y f y dy xf x y dx f y dy ∞∞∞-∞-∞-∞⎡⎤===⎢⎥⎣⎦⎰⎰⎰(,)(,)x f x y d x d yx f x y dy d x∞∞∞∞-∞-∞-∞-∞⎡⎤⎡⎤==⎢⎥⎢⎥⎣⎦⎣⎦⎰⎰⎰⎰()X xf x dx EX ∞-∞==⎰(|)()Y EX E X Y y f y dy ∞-∞==⎰也称为全期望公式.全期望公式表明:条件期望的期望是无条件期望. (3)只需证明对任意使[]()|E g Y X Y y ⋅=存在的y 都有[]()|()(|)E g y X Y y g y E X Y y ⋅===因为[|](|)E X Y y xdF x y ∞-∞==⎰,因此,当y 固定时,[]()|()(|)()(|)E g y X Y y g y xdF x y g y xdF x y ∞∞-∞-∞⋅===⎰⎰()[|]g y E X Y y ==例1.6 设在某一天走进商店的人数是期望为1000的随机变量,又设这些顾客在该商店所花钱数都为期望为100元的相互独立的随机变量,并设一个顾客花钱数和进入该商店的总人数独立,问在给定的一天内,顾客们在该商店所花钱数的期望是多少?解 设N 表示这天进入该商店的总人数,i X 表示第i 个顾客所花的钱数,则N 个顾客所花的总数为1Ni i X =∑.由于 11|N N i i i i E X E E X N ==⎡⎤⎡⎤⎛⎫=⎢⎥ ⎪⎢⎥⎣⎦⎝⎭⎣⎦∑∑而 1111||N n n i i i i i i E X N n E X N n E X nEX ===⎡⎤⎡⎤⎡⎤=====⎢⎥⎢⎥⎢⎥⎣⎦⎣⎦⎣⎦∑∑∑因此 11|,N i i E X N N E X =⎡⎤=⎢⎥⎣⎦∑[]111N i i E X E N E X E N E X =⎡⎤=⋅=⎢⎥⎣⎦∑由题设 11000,100EN EX == 于是11000100100000Ni i X ==⨯=∑即该天顾客花费在该商店的钱数的期望为100000元.。

第一讲 普通话基础

普通话的音变

在汉语普通话连续的动态语流中,音节 和音节之间互相影响发生变化叫做语流 音变,简称音变。 普通话音变主要包括变调、轻声、儿化 和语气词“啊”的音变。

由于邻近音节声调的影响,有些音节的 声调调值往往要发生变化,通常把音节 不变的声调调值叫本调或原调,连读的 声调变化叫变调。 常见的变调有: 上声的变调、 “一”、“不”的变调和 重叠形容词的变调。

轻声 在普通话连续的语流中,有的音节失去 了它原来的调,变成一种既轻又短又模 糊的调子,我们把它叫做轻声。 这个念轻声调子的音节叫做轻声音节。 轻声不是一个独立的调类,而是四声的 一种特殊音变。

听感上的“轻短模糊”是轻声音节的本 质特征。 轻声是普通话语音的一个重要特点,许 多方言没有或很少有轻声。在普通话里, 轻声词的使用频率很高。轻声能区别词 性、区分词义,能使语言节奏轻重有致、 富于美感。轻声是方言区人学习普通话 的重点之一。

声调 声调是音节声音的高低升降变化,由音高决 定,在汉语里具有区别意义的作用。 调值和调类 调值即声调的实际读法,调类指声调的种类。 汉语普通话有四种基本调类和调值:阴平 (55)、阳平(35)、上声(214)、去声 (51)。

阴平调的读法:高平调55,起调要高, 并将音高保持不变。 训练:虚心 夸张 吹风 冰川 阳平调的读法:上扬调35,发音时要避 免有的方言中下降调型的影响。 训练:学习 昂扬 银铃 求实 上声调的读法:降升调214,完整的调型 是:音高起调较低,然后由2降到1,随后上 扬升到4。 训练:泥土 参考 获奖

注意方言韵母io、üu、uê的转读 (一)一些方言读io韵母,在普通话里很少 用,只有“哟”、“唷”, 方言读io韵母的在普通话里读üe、iɑo。 Üe 决 却 略 觉 缺 雀 学 掠 约 乐 iɑo 药 脚 钥 (二)一些方言读üu韵母,普通话里读作ü。 局 桔 曲 屈 旭 续 育 浴 (三)一些方言读uê韵母,普通话里读作uo。 国 郭 阔 扩 括 或 获 惑

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

D B

+ v DS -

+ -

G

vGS

S

v DS

vGS

+ +

G D

B S

n+

n+

p-

耗尽层

15

(2)当VGS>0,VGB>0,VDS=0

衬底中的电子受到吸引,向衬 底表面运动;空穴受到排斥,向 衬底内部运动。向上运动的电子 与表面的空穴复合,形成了一层 耗尽层,形成一个栅极指向衬底 的垂直电场EV 。

=1/Ron

深线性区等 效电阻

29

(四)IV特性总结

截止区: VGS VTH 深线性区: 线性区: VDS VGS VTH 饱和区:

ID 0

I D n Cox

I D nCox

W VGS VTH VDS L

ID

1 W 2 nCox VGS VTH 2 L

模拟CMOS集成电路设计

Design of Analog CMOS Integrated Circuit

Institute of VLSI Design, Hefei U.of Tech

第一讲 基础知识

1

1.1 概 述

2

1、为什么需要模拟集成电路?

(1)为什么需要模拟电路

自然界的信 号大多是模 拟信号

8

仿真验证电路性能

修改电路参数、拓扑

版图设计

版图参数提取

测试方案设计

工 艺

芯片制造

测试与分析

单元库

系统要求

综合

系统设计和 功能划分

系 统 及 功 能 级 设 计

门级仿真

单元库

逻 辑 及 电 路 设 计

系统仿真

自动布局布线 版

寄存器传输 级(RTL)设计

物理验证 后 仿真

图 设 计

功能仿真

制版流片

封装测试

数字ASIC设计流程

9

1.2 金属氧化物半导体晶体管(MOSFET)

10

MOSTET,导电性由电容控制的器件。

◦ 电容上的电压用来控制导电沟道电流强度。

◦ 氧化层构成控制电容

栅极

源极

S G L

漏极

D

W

当Vgs>Vth时, 形成一个N型的 反型层(少子), 构成导电沟道。

n+ p CBC

CGC 氧化层 导电沟道 Leff

(九)PMOS小信号模型

可用 r0=1/λIsd来 替代

41

L’

V(x)= VGS-VTH

24

因此:

当忽略L的变化,VDS≥VGS-VTH时,饱和区电流为:

工作在饱和区的MOS管可以看作是一个电流源,其电流 受过驱动电压控制。

数字电路的晶体管工作在什么区域?

25

(二)PMOS管工作原理

1、工作原理

给栅极加负电压,即 VSG>0,负电压吸引空穴 到衬底表面,形成耗尽 层。 当VSG增加到一定值 (阈值电压)时,在栅 极绝缘层和耗尽层之间 形成P型反型层,从而形 成导电沟道。

定义:

受VDS控制

1 W 2 nCox VGS VTH 1+VDS 2 L 为沟道长度调制系数,对于较长的沟道,较小 ID

λ∝1/L

34

3、亚阈值导电性

VGS<VTH时,沟道内仍然有一个弱反型层,并有漏电 流存在,与VGS成指数关系。

栅极电压对漏极电流的控制从饱和区的平方律变成 亚阈值区的指数规律

W 1 2 V V V VDS GS TH DS L 2

un :载流子迁移率 Cox :单位面积栅氧电容 宽长比 VTH : 阈值电压

W/L:

30

(五)对NMOS和PMOS工作状态的判别

当VGD不足以形成反型层时,沟道被夹断,饱和

VG-VD<VTH,夹断发生, 饱和; VD-VG<VTH,夹断发生, 饱和。

27

2、IV特性

μp为空穴的迁移率,是电子迁移率的1/2到1/4,因此 PMOS具有较低的“电流驱动能力”。 当PMOS工作在饱和区时,电流为:

28

(三)跨导

MOS管工作时,其漏极电流受过驱动电压控制,定义 跨导为电压转换电流的能力:

当MOS管工作在饱和区时,其跨导为

当MOS管进 入线性区时, 跨导下降, 故作为放大 应用,通常 使MOS管工 作在饱和区

主流工艺,集 成度高、功耗 低、速度快、 抗干扰性强 速度高, 功耗大, 集成度低 最早MOS工 艺,速度低

6

CMOS工艺

B S G D B S p+ n 型阱 p 型衬底 n 阱CMOS工艺 B S n+ p 型阱 n 型衬底 p 阱CMOS工艺 G D B S p+ G D p+ G D n+ n+ p+

VGS I D =I0 exp VT

漏电流以有限的速率 下降,亚阈值导电导 致较大的功率损耗。

35

(七)MOS器件电容

栅和沟道间的氧化层电容 C1 WLCOX 衬底和沟道间的耗尽层电容 C2 WL q si N sub / 4F 栅与源和漏间的交叠电容C3、C4 源/漏区与衬底之间的结电容。 分为:下极板电容Cj和侧壁电容Cjsw 不同结构的管子会 具有不同的结电容

处理自然界信号 —信号的采集、接收、放大、滤波 (传感器、无线射频接收器、放大器、模拟滤波器) 数字信号处理链路必需且重要的器件 —模拟信号到数字信号的转换,如ADC —数字信号到模拟信号的转换,如DAC

模拟集成电路的重要性

3

(2)为什么要集成

电子(便携)设备的需求 —减小尺寸、重量 —降低功耗 —提高可靠性

n+ 耗尽层

通过Vgs、Vds 电压控制导电沟 道中的电流强度。

衬底或(硅)体B

NMOS管结构

11

MOS晶体管的版图和电路符号

沟道宽度 沟道宽度 沟道长度

12

13

1.3 MOS管工作原理

14

(一)NMOS管工作原理

1、工作原理

(1)VGS =0 -两个有源区被衬底分 隔,等效于背靠背的 两个PN结 -源极和漏极之间没有 电流。

VDS -

+

VGS B p+ S n+

+

随着VGS的升高,电场EV越来越 强,表面层吸引的电子越来越多, 耗尽层也越来越厚。

G D

n+ EV

p-

16

当VGS 增大到一定值时,在耗尽层和绝 缘层之间形成一个N型薄层,称为“反 型层”。

该反型层将漏极和源极两个N+有源区 连通,构成了源漏之间的导电沟道。 刚好产生反型层所需的VGS电压称为阈 值电压或开启电压(Vth)。 VGS电压越大,电场EV越强,吸引的电 子越多,导电沟道就越厚。 导电沟道出现后,若VDS=0,还不能 产生沟道电流。

N衬底

26

I

当VSD>0,开始有电流。电流的方向从源到漏。沟道 电流随VSG增加而增加。 当VSG<VTH时,截止; 当VSD<VSG-VTH时,PMOS工作在线性区; 当VSD<<VSG-VTH时,PMOS工作在深线性区; 当VSD≥VSG-VTH时,沟道被夹断,PMOS进入饱和区, 电流相对恒定。

阈值电压 是耗尽层 电荷数的 函数

VTH VTH 0 ( 2 | F | VSB 2 | F |)

2q Si Nsub

N SUB kT Cox , 体效应系数;F (V ) ln( ),反型层表面电势 q ni

33

2、沟道长度调制效应

当VDS≥VGS-VTH时,导电沟道产生夹断 MOS管的漏源电压VDS控制夹断区长度L’=(L-△L) 夹断区长度的变化导致MOS管沟道电流变化

B S p+ n+ n+ VDS +

VGS

+ G D

p-

反型层

17

(3)当VGS>0,VDS>0 如果VDS >0,则电子从源极向漏 极移动,产生了沟道电流ID。 同时,由漏极沿沟道至源极将产生 压降,栅极与沟道中各点的电压差 不再相等,栅极与源极之间的电压 VGS最高,和漏极之间的电压VGD最 低。

VDS

-

+ +

VGS

G D n+

B p+ p-

S n+

夹断区

19

2、NMOS 管IV特性推导与分析

(1)IV特性推导

Id

载流子从源级运动至漏极,设沟道中的电流为I,沿电流 方向的的电荷密度为Qd(C/m),电荷移动的速度为v (m/s),则 当VGS=VTH时,开始形成反型层,其电荷密度正比于VGS- VTH 。

电容存在于四 个端子中的任 意两个之间

36

(八)NMOS小信号模型

MOS管的I/V特性构成MOSFET的大信号模型。 当信号对偏臵影响小,就可以用小信号模型简化计算, 小信号模型是工作点附近的大信号模型的近似。

基本小信号模型, ID=gmVGS

模拟电路中大 多MOS被偏 臵在饱和区

沟道长度调制 效应等效模型 体效应等 效模型

单位长度总电荷 单位长度总电容

20

沿沟道x点处的电荷密度为:

沟道x点的电势,以源级为参考点

电流为:

载流子为电子,电荷为负,电荷运动方向与电流 方向相反

其中:

v=μE μ为载流子的迁移率,E为电场 E=-dV(x)/dx

得到:

21

在整个沟道长度内积分得:

由于ID沿沟道方向是常数,因此: