2012-2013-1_pld期末复习题试题

PLC期末考试试题和答案

PLC期末考试试题和答案1.电弧会导致电路分断时间加长,需要注意。

2.熔断器的额定电流和熔体的额定电流不是同一个概念。

3.实现接触器互锁控制,需要在两个接触器的线圈电路中互串对方的动断触点。

4.断电延时型时间继电器的延时动合触点是瞬时断开延时闭合的。

5.与电流继电器相比,电压继电器的线圈匝数多,导线细,电阻大。

6.电气原理图中,同一电器的各个部件可以不画在一起。

7.热继电器不能实现短路保护。

8.在延时精度要求不高,电源电压波动较大的场合应选用空气阻尼式时间继电器。

9.CJ20-160型交流接触器在380V时的额定电流是160A。

10.按用途或控制对象分,按钮、行程开关、万能转换开关属于低压控制电器。

1.判断交流或直流接触器的依据是主触点电流的性质。

2.分励脱扣器用于远距离断开电路。

3.吸引线圈的作用是将电能转化成磁场能量。

4.熔断器作为短路保护的电器,通常串接于被保护电路中。

5.将线圈额定电压为220V的交流接触器线圈误接入380V 的交流电源上会导致烧毁线圈。

6.PLC存储器存放用户程序、数据和系统程序,但不存放输入信号。

7.分析电气原理图的基本原则是先分析主电路,后分析辅助电路。

8.自动空气开关的电气符号是QF。

9.PLC软继电器有无数对常开和常闭触点供编程时使用。

10.ST指令的作用是用于单个常开触点与母线连接。

1.低压电器标准规定,低压电器通常指工作在交流电压小于(A)和直流电压小于(B)的电路中,起通断、保护、控制或调节作用的电器设备。

2.对于交流电磁铁,铁心、线圈和吸引线圈都采用易于散热的设计,且线圈骨架与铁心非接触。

其中,短而厚的矮胖型发热,而高而薄的瘦长型不发热。

3.直流电磁铁的励磁电流大小与气隙无关,动作过程中保持恒磁通工作,吸力随气隙的减小而增大。

4.中间继电器实质上是一种电压继电器,具有较多的触点对数和较小的触点容量,动作灵敏度高。

5.电压继电器的线圈与负载并联,线圈匝数较多,导线较细。

fpga期末复习题(答案)知识点题型

一、填空题:1、 FPGA结构一般分为三部分:可编程逻辑块(CLB)、可编程I/O模块和可编程内部连线。

2、 CPLD的内部连线为连续式布线互连结构,任意一对输入、输出端之间的延时是固定;FPGA的内部连线为分段式布线互连结构,各功能单元间的延时不定(不可预测)。

3、大规模可编程器件主要有CPLD和FPGA两类,其中CPLD通过可编程乘积项逻辑实现其逻辑功能。

基于SRAM的FPGA器件,每次上电后必须进行一次配置。

FPGA内部阵列的配置一般采用在电路可重构技术,编程数据保存在静态存储器(SRAM) ,掉电易失。

4、目前世界上有十几家生产CPLD/FPGA的公司,最大的两家是:Altera,Xilinx。

5、硬件描述语言(HDL)是EDA技术的重要组成部分,是电子系统硬件行为描述、结构描述、数据流描述的语言,它的种类很多,如VHDL、Verilog HDL、AHDL6、 WHEN_ELSE条件信号赋值语句和 IF_ELSE顺序语句的异同:* WHEN_ELSE条件信号赋值语句中无标点,只有最后有分号;必须成对出现;是并行语句,必须放在结构体中。

* IF_ELSE顺序语句中有分号;是顺序语句,必须放在进程中7、可编程逻辑器件设计输入有原理图输入、硬件描述语言输入和波形输入三种方式。

原理图输入方式是一种最直接的设计描述方式,波形设计输入适用于时序逻辑和有重复性的逻辑函数。

硬件描述语言的突出优点是:* 语言与工艺的无关性;语言的公开可利用性,便于实现大规模系统的设计;* 具有很强逻辑描述和仿真功能,而且输入效率高,在不同设计输入库之间的转换非常方便,用不着对底层的电路和PLD结构的熟悉。

8、用VHDL/Veilog HDL语言开发可编程逻辑电路的完整流程:文本编辑→功能仿真→逻辑综合→布局布线→时序仿真。

*所谓综合,就是根据设计功能和实现该设计的约束条件(如面积、速度、功耗和成本等),将设计输入转换成满足要求的电路设计方案,该方案必须同时满足与其的功能和约束条件。

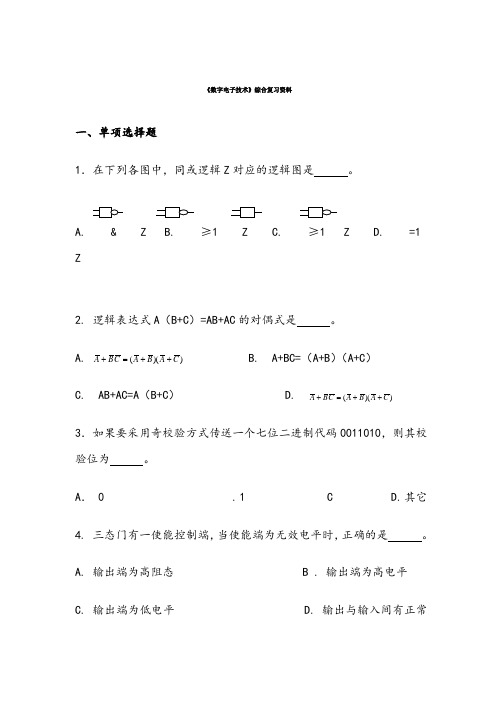

数字逻辑电路复习题与答案

_、单选题1、十进制整数转换为二进制数一般采用()。

A.除2取整法B.除10取余法C.除2取余法D.除10取整法正确答案:C2、将十进制小数转换为二进制数一般采用()。

A.乘2取整法B.乘10取余法C.乘2取余法D.乘10取整法正确答案:A3、十进制数"13",用三进制表示为()。

A.211B.111C.112D.101正确答案:B4、将十进制数18转换成八进制是().A.20B.24C.22D.21正确答案:C5、十进制数25用8421 BCD码表示为()A.10 010100B.0010 0101C.10 101D.10 000101正确答案:B6、以下代码中为恒权码的是()。

A.余3循坏码B右移码C.5211 码D.余3码正确答案:C7、T立八进制数可以用()位二进制数来表示。

A.4B.3C.1D.2正确答案:B&十进制数43用8421BCD码表示为()。

A.10011B.0100 0011C.101011D.1000011正确答案:B9、A+BC=()A.AB+ACB.BCC・(A+B)(A+C)正确答案:C10、4变量逻辑函数的真值表,表中的输入变量的取值应有()种。

A.4B.2C.16D.8正确答案:C11、f 16选1的数据选择器,其选择控制(地址)输入端有()个,数据输入端有16个,输出端有1个。

A.4B.16C.1D.2正确答案:A12、一个译码器若有100个译码输出端,则译码输入端至少有()个。

A.5B.8C.7D.6正确答案:C13、能实现并-串转换的是()。

A.数据选择器B.数据分配器C.译码器D.数值比较器正确答案:A14、欲设计一个3位无符号数乘法器(即3x3),需要6位输入及()位输出信号。

B.6C.4D.5正确答案:B15、4位输入的二逬制译码器,其输出应有()位。

A.4B.1C.8D.16正确答案:D16、对于8线一3线优先编码器,下面说法正确的是()A.有8根输入线,8根输出线B.有8根输入线,3根输出线C.有3根输入线,8根输出线D.有3根输入线,3根输出线正确答案:B17、3线-8线译码电路是()译码器A.八进制B.三进制C.三位二进制D.H-A进制正确答案:C18、实现多输入、单输出逻辑函数,应选()。

PL期末试题和答案

复习参考一、选择题1.世界上第一台可编程序控制器PDP-4是 A 在1969年研制出来的。

A. 美国B. 德国C. 日本D. 中国2.PLC的各种系统参数、I/O映像等参数存放到PLC的 B 中。

A. 系统ROMB. 系统RAMC. 用户ROMD. 用户RAM3.PLC的CPU与现场I/O装置的设备通信的桥梁是 C 。

A. I模块B. O模块C. I/O模块D. 外设接口4.为了拓宽输入电压范围,提高电源的效率和抗干扰能力, PLC的内部电源一般采用 D 。

A. 并联稳压电源B. 串联稳压电源C. 锂电池D. 开关稳压电源5.S7-300/400 PLC的电源模块为背板总线提供的电压是 A 。

A. DC5VB. +DC12VC. –DC12VD. DC24V6.下列不属于PLC的特点的是 C 。

A. 通用性好,适应性强B. 可靠性高,抗干扰能力强C. 设计、安装、调试和维修工作量大D. 编程简单、易学7.下列不具有通信联网功能的PLC是 D 。

A. S7-200B. S7-300C. GE90UD. F1-30MR8.作为德国国家标准和欧洲标准,由3个系列组成的现场总线是 B 。

A. FF???????????????????B. PROFIBUS ???C. LonWorks? ???D. CAN9.SIMATIC NET中, C 属于多点接口,适用于少量、慢,实时性要求不高的场合。

A. ETHERNETB. PROFIBUSC. MPID. AS-I10.按组成结构形式、容量和功能分,S7-300属于 D 。

A. 小型中档整体式B. 小型高档模块式C. 大/中型高档整体式D. 大/中型高档模块式11.下列输出模块可以交直流两用的是( B )A. 光电耦合输出模块B. 继电器输出模块C. 晶体管输出模块D. 晶闸管输出模块12.输入采样阶段,PLC的CPU对各输入端子进行扫描,将输入信号送入 C 。

大学期末考试电力拖动自动控制系统往年题答案范围总结

⼤学期末考试电⼒拖动⾃动控制系统往年题答案范围总结2012~2013年(本)1、平波电抗器的⼤⼩是如选择的?答:⼀般按低速轻载时保证电流连续的条件来选择,通常⾸先给定最⼩电流I(以A为单位),再利⽤它计算所需的总电感(以mH为单位)。

减去电枢电感,即得平波电抗应有的电感值。

2、转速负反馈单闭环有静差调速系统中,电枢电阻、转速反馈系数,这些参数变化时系统是否有调节作⽤?为什么?答:在电压负反馈单闭环有静差调速系统中,当放⼤器的放⼤系数Kp发⽣变化时系统有调节作⽤再通过反馈控制作⽤,因为他们的变化最终会影响到转速,减⼩它们对稳态转速的影响。

当电动机励磁电流、电枢电阻Ra发⽣变化时仍然和开环系统⼀样,因为电枢电阻处于反馈环外。

当供电电⽹电压发⽣变化时系统有调节作⽤。

因为电⽹电压是系统的给定反馈控制系统完全服从给定。

当电压反馈系数γ发⽣变化时,它不能得到反馈控制系统的抑制,反⽽会增⼤被调量的误差。

反馈控制系统所能抑制的只是被反馈环包围的前向通道上的扰动。

(⽆调节作⽤。

因为反馈控制系统所能抑制的只是被反馈包围的前向通道上的扰动。

)3、对于经常正、反运⾏的调速系统,理想的起动过渡过程应什么样?答:始终保持电流(电磁转矩)为允的最⼤值,使调速系统以最⼤的加(减)速度运⾏。

当到达稳态转速时,最好使电流⽴即降下来,使电磁转矩与负载转矩相平衡,从⽽迅速转⼊稳态运⾏。

(起动电流呈矩形波,转速按线性增长)4、什么是软起动器?答:当电压降低时,起动电流将随电压成正⽐地降低,从⽽可以避开起动电流冲击的⾼峰。

起动转矩与电压的平成正⽐,起动转矩的减⼩将⽐起动电流的降低更多,降压起动时⼜会出现起动转矩不够的问题。

降压起动只适⽤于中、⼤容量电动机空载(或轻载)起动的场合。

5、对于通⽤变频器,所谓的“通⽤”有什么含义?答:⼀是可以和通⽤的笼型异步电动机配套使⽤;⼆是具有多种可供选择的功能,适⽤于各种不同性质的负载。

6、什么是正弦脉宽调制技术?答:由它们的交点确定逆变器开关器件的通断时刻,从⽽获得幅值相等、宽度按正弦规律变化的脉冲序列,这种调制法称作正弦波脉宽调制7、⽐例积分控制中⽐例和积分部分各有什么特点?答:⽐例部分能迅速响应控制作⽤,积分部分则最终消除稳态偏差。

PLD复习资料整理

(选择)PLD器件4个发展阶段:PLD器件的分类(1)按可编程的部位分类(填空)库的种类(1)IEEE库(2)VITAL库(3)STD库(4)WORK库VHDL 文字规则(除了数字、字母、下划线,其他全部不合法)(考小题)VHDL共有4类数据对象:常量、变量、信号和文件VHDL数据类型(DATA TYPES)(1)标量类型(Scalar Type)(2)复合类型(Complex Type)(3)存取类型(Access Type) (4)文件类型(File Type)操作符列表VHDL的预定义数据类型(1)布尔类型(BOOLEAN)其取值只能为FALSE(伪)和TRUE(真)两者之一。

(2)位类型(BIT)取值只能是1或0(3)位矢量类型(BIT_VECTOR)位矢量是基于位数据类型的数组,使用位矢量必须注明位宽。

(4)字符类型(CHARACTER)(字符类型要用单引号引起来表示,在VHDL程序设计中标识符一般不区分大小写,但用了单引号的字符则区分大小写)(5)整数类型(INTEGER)(在程序包中指定了整数的取值范围是)(6)自然数和正整数类型(NA TURAL AND POSITIVE)(7)实数类型(REAL)()(8)字符串类型(STRING)(9)时间类型(TIME)(10)错误等级(SEVERITY LEVEL)(11)综合器不支持类型:1物理类型2浮点类型3存取类型4文件类型常见输入方式3种:VHDL语言电路图输入波形输入简答题(6题)现代数字系统设计的一般步骤:1确定设计任务,划分各功能模块2设计输入3逻辑验证4逻辑综合5时序仿真6物理实现同步时序电路的设计步骤:1建立原始状态图2化简原始状态图3分配状态代码4选择触发器类型,确定输出函数及触发器的激励函数5画电路图6检查多余状态程序设计题1.“与”门的VHDL描述及仿真波形library ieee;use ieee.std_logic_1164.all;entity Vhdl1 isport(a,b:in std_logic;c: out std_logic);end entity Vhdl1;architecture behav of Vhdl1 isbeginc<=a and b;end architecture behav;2.“与非”门的VHDL描述及仿真波形library ieee;use ieee.std_logic_1164.all;entity Vhdl2 isport(a,b:in std_logic;c: out std_logic);end entity Vhdl1;architecture behav of Vhdl2 isbeginc<=not(a and b);end architecture behav;3.“或非”门的VHDL及仿真波形library ieee;use ieee.std_logic_1164.all;entity Vhdl3 isport(a,b:in std_logic;c: out std_logic);end entity Vhdl3;architecture behav of Vhdl3 isbeginc<=not(a or b);end architecture behav;4.“异或非”门的VHDL描述及仿真波形library ieee;use ieee.std_logic_1164.all;entity Vhdl4 isport(a,b:in std_logic;c: out std_logic);end entity Vhdl4;architecture behav of Vhdl4 isbeginc<=not(((not a)and b) or(a and(not b)));end architecture behav;5. 4选1多路选择器的VHDL程序及波形仿真library ieee;use ieee.std_logic_1164.all;entity mux41 isport(a,b,c,d:in std_logic;ena:in std_logic_vector(1 downto 0);p:out std_logic);end mux41;architecture choice of mux41 isbeginprocess(ena)beginif(ena="00")thenp<=a;elsif(ena="01")thenp<=b;elsif(ena="10")thenp<=c;elsep<=d;end if;end process;end choice;6.设计一个具有异步复位、置位功能的D触发器并仿真。

PLD复习资料(已排版)(补充版)

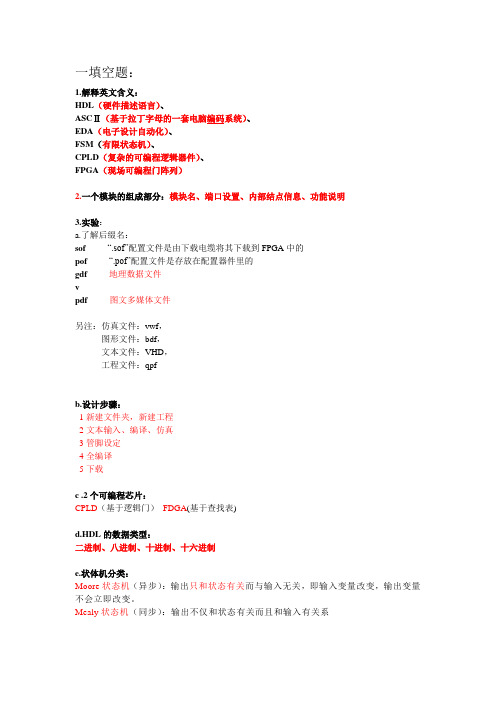

一填空题:1.解释英文含义:HDL(硬件描述语言)、ASCⅡ(基于拉丁字母的一套电脑编码系统)、EDA(电子设计自动化)、FSM(有限状态机)、CPLD(复杂的可编程逻辑器件)、FPGA(现场可编程门阵列)2.一个模块的组成部分:模块名、端口设置、内部结点信息、功能说明3.实验:a.了解后缀名:sof“.sof”配置文件是由下载电缆将其下载到FPGA中的pof “.pof”配置文件是存放在配置器件里的gdf 地理数据文件vpdf 图文多媒体文件另注:仿真文件:vwf,图形文件:bdf,文本文件:VHD,工程文件:qpfb.设计步骤:1新建文件夹,新建工程2文本输入、编译、仿真3管脚设定4全编译5下载c .2个可编程芯片:CPLD(基于逻辑门)FDGA(基于查找表)d.HDL的数据类型:二进制、八进制、十进制、十六进制e.状体机分类:Moore状态机(异步):输出只和状态有关而与输入无关,即输入变量改变,输出变量不会立即改变。

Mealy状态机(同步):输出不仅和状态有关而且和输入有关系f.循环语句(4种):repeat while for foreverg.块语句:支持顺序块{begin end} 和并列块{fork join}h.变量的位宽;赋值i.过程赋值:阻塞(顺序执行)与非阻塞(非顺序执行)的区别与特点(起点都一样)j.子程序:任务和函数k.分频器的程序:加法计数器的程序的两个ALW AYSl.模块的基本组成:四个部分,并非每个都必须模块名、端口设置、内部结点信息、功能说明二编程1循坏语句的编程(作业中的两道)P11213.使用while循环设计一个时钟信号发生器。

时钟信号的初值为0,周期为10个时间单位。

module clk_gen;integer i;reg clk;initialbegini=0;clk=0;while (i>=0)begin$display ("i=%d",i);#5 clk=~clk;i = i +1;endendendmodule14.使用for循环对一个长度为1024(地址从0到1023)、位宽为4的寄存器类型数组cache_var进行初始化,把所有单元都设置为0。

2012~2013年plc期末考试重点题还原回顾,60分问答和设计部分

1.设计一小车运行的控制线路,小车由异步电动机拖动,其动作程序如下:

①小车由原位开始前进,到终端后自动停止;

②在终端停留2min后自动返回原位停止;

③在前进或后退途中任意位置都能停止或启动。

2,用S、R和跳变指令设计满足下图所示波形的梯形图。

3, 三台电动机M1、M2、M3按下面的顺序启动和停车:启动时,M1、M2同时启动,此后10分钟M3才能启动;停车时,M3必须先停,M3停后5分钟M1、M2同时停。

按上述要求,提出所需控制电器元件,选择PLC机型,作I/O分配,画出PLC外部的接线图及电动机的主电路图,设计一个满足要求的梯形图程序。

4,电动机的起动电流很大,起动时热继电器应不应该动作?为什么?

5,用文字叙述TON的工作原理过程。

6,写出下列电器的作用、图形符号和文字符号:熔断器、接触器、低压断路器、行程开关、按钮、自动空气开关、热继电器、时间继电器、速度继电器;

7,写出下图所示梯形图的语句表程序.

8,指出下图中的错误.。

(完整版)集成电路设计复习题及解答

集成电路设计复习题绪论1.画出集成电路设计与制造的主要流程框架。

2.集成电路分类情况如何?集成电路设计1.层次化、结构化设计概念,集成电路设计域和设计层次2.什么是集成电路设计?集成电路设计流程。

(三个设计步骤:系统功能设计逻辑和电路设计版图设计)3.模拟电路和数字电路设计各自的特点和流程4.版图验证和检查包括哪些内容?如何实现?5.版图设计规则的概念,主要内容以及表示方法。

为什么需要指定版图设计规则?6.集成电路设计方法分类?(全定制、半定制、PLD)7.标准单元/门阵列的概念,优点/缺点,设计流程8.PLD设计方法的特点,FPGA/CPLD的概念9.试述门阵列和标准单元设计方法的概念和它们之间的异同点。

10.标准单元库中的单元的主要描述形式有哪些?分别在IC设计的什么阶段应用?11.集成电路的可测性设计是指什么?Soc设计复习题1.什么是SoC?2.SoC设计的发展趋势及面临的挑战?3.SoC设计的特点?4.SoC设计与传统的ASIC设计最大的不同是什么?5.什么是软硬件协同设计?6.常用的可测性设计方法有哪些?7. IP的基本概念和IP分类8.什么是可综合RTL代码?9.么是同步电路,什么是异步电路,各有什么特点?10.逻辑综合的概念。

11.什么是触发器的建立时间(Setup Time),试画图进行说明。

12.什么是触发器的保持时间(Hold Time),试画图进行说明。

13. 什么是验证,什么是测试,两者有何区别?14.试画图简要说明扫描测试原理。

绪论1、 画出集成电路设计与制造的主要流程框架。

2、集成电路分类情况如何?集成电路设计1. 层次化、结构化设计概念,集成电路设计域和设计层次分层分级设计和模块化设计.将一个复杂的集成电路系统的设计问题分解为复杂性较低的设计级别,⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎩⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎧⎪⎪⎪⎪⎩⎪⎪⎪⎪⎨⎧⎩⎨⎧⎩⎨⎧⎪⎪⎪⎪⎩⎪⎪⎪⎪⎨⎧⎪⎪⎪⎪⎪⎪⎩⎪⎪⎪⎪⎪⎪⎨⎧⎩⎨⎧⎪⎪⎪⎪⎩⎪⎪⎪⎪⎨⎧⎩⎨⎧⎪⎩⎪⎨⎧按应用领域分类数字模拟混合电路非线性电路线性电路模拟电路时序逻辑电路组合逻辑电路数字电路按功能分类GSI ULSI VLSI LSI MSI SSI 按规模分类薄膜混合集成电路厚膜混合集成电路混合集成电路B iCMOS B iMOS 型B iMOS CMOS NMOS PMOS 型MOS双极型单片集成电路按结构分类集成电路这个级别可以再分解到复杂性更低的设计级别;这样的分解一直继续到使最终的设计级别的复杂性足够低,也就是说,能相当容易地由这一级设计出的单元逐级组织起复杂的系统。

PLC期末考试复习题新

1。

PLC的数据单元也叫继电器。

2.PLC的输入口用来同意生产过程的各种参数。

输出口用来送出PLC运算后得出的操纵信息,并通过机外的执行机构完成工业现场的各类操纵.3。

输入继电器的线圈只能由机外信号驱动,在反映器件逻辑关系的梯形图中并不浮现。

4.PLC的两种基本工作状态是运行状态与停止状态。

5。

掉电保持的通用型继电器具有经历能力。

6。

使用计数器C201作加法计数时,特别辅助继电器M8201应处于断开或置0状态。

7。

使用一次MPS指令,便将当前运算结果送入堆栈的第一层,而将原有的数据移到堆栈的下一层。

8。

梯形图中,每一行的开始是触点群组成的工作条件,最右边是线圈表达的工作结果.9。

梯形图中触点应画在水平线上,不能画在垂直分支线上.10.状态转移图中的状态有驱动负载、指定转移目标和指定转移条件三个要素。

11.当变址寄存器V=6时,位组合元件K2X2V的实际地址为K2X10。

12。

存储器是PLC存放系统程序、用户程序和运算数据的单元。

13。

PLC存储器的存储区域按用途不同,可分为程序区和数据区.14.PLC输入输出接口有二个要紧要求,一是接口有良好的抗干扰能力,二是接口能满足工业现场各类信号的匹配要求.15.PLC按硬件的结构类型可分为单元式、模块式和叠装式三种.16.PLC中某个元件被选中,代表那个元件的存储单元1,失去选中条件,代表那个元件的存储单元0。

17。

在有几个串联回路并联时,应将触点最多的串联回路放大在梯形图的最上面.在有几个并联回路串联时,应将触点最多的并联回路放大在梯形图的最左面.18.功能指令助记符前标记(D)符号,表示该指令是32位指令。

19。

功能指令助记符后标记(P)符号,表示该指令是脉冲型指令。

系列PLC编程元件分为两个部分,第一部分是代表功能的字母,第二部分20.FX2是数字,代表该器件的序号。

21.在可编程操纵器内部要紧用于开关量信息的传递、变换及逻辑处理的编程元件,称为位元件。

数电复习题及图片

试题库(占80分)一、填空1.在十进制数中,其中低位和相邻高位之间的关系是。

2.只要条件具备了,结果便不会发生;而条件不具备时,结果一定发生,这种因果关系叫做。

3.(1101101)2=()16=()104.(10.00)16=()2=()105.MOS管的四种类型;;;。

6.54H、54S与74H、74S系列的区别仅在于与。

7.CMOS反相器的閾值电压为V TH= 。

8.根据逻辑功能的不同特点,可以把数字电路分成两大类,一类是;另一类是。

9.编码器的逻辑功能就是把输入的每一个高、低电平信号编成一个对应的代码。

10.我们把门电路两个输入信号同时向的逻辑电平跳变的现象叫做。

11.竞争现象是冒险现象的,而冒险现象并非竞争现象的。

12.触发器必须具备的条件之二是:根据不同的输入信号可以置成或状态。

13.同步RS触发器的特性方程是:。

14.任一时刻的输出信号不仅取决于当时的输入信号,而且还取决于电路,具备这种逻辑功能的电路叫做。

15.所谓移位寄存器,是指寄存器里存储的代码能在的作用下依次或。

16.按计数过程中计数器中的数字增减情况,可把计数器分为、、。

17. n+1位二进制计数器的容量等于。

18.D IR是移位寄存器的数据串行输入端,D IL为数据串行输入端。

19.Vm是脉冲电压的,q是脉冲电压的。

20.施密特触发器的负相閾值电压V T-= ,回差电压ΔV T=。

21.一个四位二进制加法计数器,由0000状态开始,经过45个输入脉冲后,此计数器的状态为。

22.时序逻辑电路任意时刻的稳定输出取决于,同时还和。

23.(-00101)2的反码;补码。

24.带符号位(最高位为符号位)(011011)2的反码;补码。

25.德.摩根定理(A+B)’= 。

26.MOS管的i D和u GS的关系为:。

27.TTL反相器的输入端噪声容限在输入为高电平时V NH= 。

28.T触发器的特性方程为:。

29.只读存储器在正常工作状态下从中读取数据,快速地随时修改或重新写数据。

PLD题目库 填空

13.

Mealy型状态机的输出是()和()的函数。

14.

()仿真,其过程不涉及任何具体器件的硬件特性,此时的仿真没有(

)或者系统添加的微小标准延时。

15.

JTAG接口使用四个I/0引脚和一个可选引脚TRST,其中四个I/O引脚分别是TDI、

()、()和()。

序号

题目

16.

Moore型状态机的输出仅为()的函数,而与()无关。

25.

在VHDL设计中,实体端口模式主要有输入、输出、()和()等四种。

26.

子程序可以在VHDL程序的三个不同的位置进行定义,即在()、()和()中定义。

ቤተ መጻሕፍቲ ባይዱ27.

若定义如下枚举类型:

type week is(Monday,Tuesday,Wednesday,Thursday,Friday,Saturday,Sunday);则:

计实体的()和外部设计实体()间的逻辑关系。

37.

VHDL语言标准定义了两个标准程序包,即()和(),

它们都被收入在STD库中。

38.

以Altera公司的Cyclone系列FPGA为例,其结构中主要包括()、EAB、

()和I/O控制块四部分。

39.

一般我们在区分CPLD和FPGA时,将以()结构方式构成逻辑行为的器

和变量。

7.

ifclk’eventandclk=‘1’then描述的是时钟的()边沿;ifrising_edge(clk)then

描述的是时钟的()边沿。

8.

VHDL中,16#EF#表示为()进制数;其二进制值为()。

9.

VHDL中,PROCESS为一无限循环语句;()发生()时

2012-2013-1_pld期末复习题试题

复习题(开卷)一、填空题(本大题共10小题,每空1分,共20 分)1.一般把EDA技术的发展分为MOS时代、MOS时代和ASIC三个阶段。

2.EDA设计流程包括设计输入、设计实现、实际设计检验和下载编程四个步骤。

3.EDA设计输入主要包括图形输入、HDL文本输入和状态机输入。

4.时序仿真是在设计输入完成之后,选择具体器件并完成布局、布线之后进行的时序关系仿真,因此又称为功能仿真。

5.VHDL的数据对象包括变量、常量和信号,它们是用来存放各种类型数据的容器。

6.图形文件设计结束后一定要通过仿真,检查设计文件是否正确。

7.以EDA方式设计实现的电路设计文件,最终可以编程下到FPGA和CPLD芯片中,完成硬件设计和验证。

8.MAX+PLUS的文本文件类型是(后缀名).VHD。

9.在PC上利用VHDL进行项目设计,不允许在根目录下进行,必须在根目录为设计建立一个工程目录。

10.VHDL源程序的文件名应与实体名相同,否则无法通过编译。

一、填空题与简答题1、ASIC的中文含义是:专用集成电路。

2、在VHDL中主要有哪三种重载现象参数类型的重载;参数数目的重载;函数返回类型的重载。

3、简单可编程逻辑器件的主要有PROM、PLA、PAL、GAL4、CPLD内部含有多个逻辑单元块,每个逻辑单元块相当于一个GAL器件:5、在设计中,常常采用的设计方法有直接设计方法、自顶向下和自底向上的设计方法。

6、CPLD的一般采用“与-或阵列”结构。

7、一个完整的VHDL程序包括库、程序包、实体、结构体和配置五个部分。

8、PLD的中文含义是:可编程逻辑器件。

9、“与-或”结构的可编程逻辑器件主要由四部分构成:输入电路、可编程“与”阵列、可编程或阵列、输出电路10、FPGA的一般采用“查找表”结构。

11.VHDL的全拼Very high speed integrated Hardware Description Language12.子程序有即过程(PROCEDURE)、函数〔FUNCTION〕两种类型。

数字电子技术复习题

A .32kHz;

B.2kHz;

C .128 kHz

D.256kHz

12.用 n 个触发器构成计数器,可得到的最大计数长度(模值)为 ____________。

A. n

B. 2n

C. n 2

D. 2 n 5V

84 13.由 555 定时器构成的施密特触发器6如图3所示,u该o 电路的回差电压

为

V。

ui

。

11、(43)10 =(

)2。

12、将逻辑函数 F=∑m(0,2,3,4,6,7,10,11,14,15),化

简为最简与或式结果为

。

13、三态门的输出状态除了高电平或低电平两种状态外,还有第三状

态是

。

14、若用二进制代码对 48 个字符进行编码,则至少需要

位

二进制。

15、JK 触发器的次态方程是 Q n1 =

D. A BC (A B )( A C )

3.如果要采用奇校验方式传送一个七位二进制代码 0011010,则其校

验位为

。

A. 0

.1

C

D. 其它

4. 三态门有一使能控制端,当使能端为无效电平时,正确的是

。

A. 输出端为高阻态

B . 输出端为高电平

C. 输出端为低电平

D. 输出与输入间有正常

的逻辑关系

2 15

4V

A.5

B.4

C.2

D.5/3

14.设 F=AB+C D ,则它的反函数是____________。

A. F =(A+B)(C D )

B. F =( A B )(C+D)

C. F = A B • C D

D.以上都不正确

《过程控制工程》期末复习题及答案

《过程控制工程》期末复习一、(每空1分)填空题:1、对于一个比例积分微分(PID)控制器来说,积分时间越小则积分作用越强;微分时间越小,则微分作用越弱。

2、三种常用的均匀控制方案包括简单均匀控制,串级均匀控制,双冲量均匀控制3、常规PID控制器中的P指比例作用、I指积分作用、 D指微分作用。

4、用于输送流体和提高流体压头的机械设备统称为流体输送设备,其中输送液体并提高其压头的机械称为泵,而输送气体并提高其压头的机械称为风机和压缩机5、工程上常用的几种整定PID控制器参数的方法是经验法、临界比例度法、衰减曲线法、响应曲线法。

6、请举出我们曾经学过的三种复杂控制系统:(串级)、(前馈)、(比值)。

7、比值系统控制系统从结构上可分为四种,分别是(开环比值控制系统)、(单闭环比值控制系统)、(双闭环比值控制系统)、(变比值控制系统)四种。

8、调节阀的固有流量特性主要有(线性型)、(等百分比(或对数)型)、(抛物线型)、)(快开型)9、比值系统控制系统从结构上可分为四种,分别是(开环比值控制系统)、(单闭环比值控制系统)、(双闭环比值控制系统)、(变比值控制系统)四种。

10、单回路控制系统一般由(控制器)、(控制阀)、(受控对象)、(测量变送器)四个环节组成。

11、常见的传热设备有(换热器)、(加热炉)、(锅炉)等。

12、要消除系统的稳态误差,通常选用(比例积分(PI)控制)控制器。

13、用来评价控制系统性能优劣的阶跃响应曲线性能指标分别是衰减比、超调量与最大动态偏差、余差、振荡频率和回复时间等。

14、工程上进行PID控制器参数整定时,随动系统的控制品质要求衰减比为 10 :1 ,定值系统中控制品质要求衰减比为 4:1 。

15、常见的传热设备有换热器、加热炉、锅炉、再沸器、冷凝器、加热器中任选三种等。

16、精馏装置一般由(精馏塔塔身)、(冷凝器)、(再沸器)、(回流罐)、等设备组成。

精馏塔产品质量指标选择有直接产品质量指标和间接产品质量指标两类。

《PLD原理与EDA技术》考试卷(B)

一、单选题(每题2分,共20分。

将答案填入右边括号)1.FPGA和CPLD通常也被称为专用IC。

( C )A.不可编程B.RAMC.可编程D.ROM2.将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

( B )A.程序B.综合C.编译D.汇编3.EDA技术采用自顶向下的设计方法,是在整个设计流程中各设计环节___的过程。

( B )A.分散处理B.逐步求精C.综合处理D.集中处理4.ASIC设计的全定制方法是一种基于晶体管级的,设计版图的制造方法。

( D )A.机器B.半自动C.自动D.手工5.IP核具有规范的接口协议,良好的可移植与性,为系统开发提供了可靠的保证。

( C )A.不可下载B.下载C.可测试D.不可测试6.GAL、CPLD之类都是基于乘积项的可编程结构;即包含有可编程与阵列和的PAL(可编程阵列逻辑)器件构成。

( B )A.不固定的或阵列B.固定的或阵列C.EEPROMD.SRAM7.FPGA可编程资源主要来自。

( B )A.EEPROMB.逻辑阵列块LABC.PLLD.LUT8.使用BST(边界扫描测试)规范测试,,可在器件正常工作时在系统捕获测量的功能数据。

( A )A.不必使用物理探针B.使用探针C.使用万用表D.使用示波器9.MAX II系列属CPLD类型的可编程逻辑器件;编程信息存于____________中。

( B )A.SRAMB.EEPROMC.LMP_RAMD.LMP_FIFO10.在VHDL语言中,用语句表示检测到时钟clk的上升沿。

( B )A. clk’eventB. clk’event and clk = ‘1’C. clk = ‘0’D. c lk’event and clk = ‘0’二、EDA名词解释,写出下列缩写的中文(或英文)含义(每个2分,共10分)1.VHDL:超高速集成电路硬件描述语言2、FPGA:现场可编程门阵列3、RTL:寄存器传输级4、JTAG:联合测试活动组织5、EAB:嵌入式阵列块三、简答题(每题5分,共15分)1.结构体的描述方式有几种,各有什么特点?答:结构体的描述方式有: Structure(结构)描述、 Date Flow (数据流)描述、Behavior Process(行为)描述。

放射生物学复习题

1、粒子的类型,要能区别粒子辐射、电磁辐射,放射医学关心的电磁辐射是什么?粒子辐射:通过消耗自己的能量传递给其它物质,主要有:α、β、负π介子和带电重离子。

电磁辐射:是以互相垂直的电场和磁场、随时间变化而交变震荡,形成向前运动的电磁波。

如:x、γ、微波、红外线波和紫外线都是电磁辐射。

放射医学关心是:生物学效应(此题不确定)2、辐射引起生物分子损伤,主要是通过形成什么?脂质过氧化物参考(脂质过氧化作用是由于氧自由基攻击了生物膜磷脂中的多不饱和脂肪酸引起,形成脂质过氧化物从而对细胞造成损伤(如LPO)。

3、辐射引起的DNA断裂的特点。

1)单链断裂与双链断裂的比值;DSB约为SSB的1/10~1/20;SSB由一个自由基攻击引起;DSB必须由两个以上自由基引起;一定能量的射线所产生的SSB和DSB有一个大致的比值,但比值不是恒定的。

2)LET对链断裂的影响:各种射线对链断裂效应的顺序:中子>γ射线、χ>紫外线;SSB与DSB的比值与LET的高低有关。

随着LET的升高,SSB减少,DSB增多。

3)氧效应对链断裂的影响:氧效应可增加链断裂的程度:主要原因是氧效应可增加羟自由基的产生;4)DNA链发的部位:剂量不同,DNA碱基发生断裂的概率亦不同。

当剂量<10Gy照射时,碱基断裂顺序G>A>T≥C。

当剂量>40~80Gy照射时,碱基断裂顺序T>G>A≥C。

5)DNA链断裂与细胞辐射敏感性;DNA的断裂程度与辐射敏感性有关;不同哺乳动物细胞对辐射的敏感性有很大差异,平均致死剂量(D0)亦不同。

4、DPC的特点DNA与蛋白质以共价键结合参考(DNA-蛋白质交联(DNA-protein cross- linking ,DPC):DNA与蛋白质以共价键结合)5、辐射的穿透性,会比较射线传能线密度大小的比较(1):软β射线、低能量X射线:穿透能力弱; (2):硬β射线、γ射线、高能量X射线,穿透能力强X-ray, Gamma < 3.5Electrons (Betas) < 3.5Alpha approx 175Neutrons- thermal approx 5- 0.01 MeV > 53- 0.1 MeV > 175- >0.1 - 2 MeV > 53- > 2 MeV - 20 MeV approx 23参考(软射线:能量低、电离密度高、穿透能力弱、皮肤浅层组织吸收,易引起表层组织损伤(软β射线、低能量X射线)硬射线:能量高、电离密度低、穿透能力强、达深层组织,最大剂量在皮肤3-5cm 深度,易引起深层组织损伤,而皮肤表面损伤所需要的剂量就较大。

2012-2013下学期期末考试机械工程控制基础试题

2012-2013下学期期末考试试题机械工程控制基础学号 ##成绩_____一、选择题〔每题2分,共计20分〕1、拉氏变换将时间函数变换成〔〕A .正弦函数B .单位阶跃函数C .单位脉冲函数D .复变函数2、微分环节的频率特性相位移θ<ω>= < >A. 90°B. -90°C. 0°D. -180°3、设系统的传递函数为G<s>=255252++s s ,则系统的阻尼比为〔 〕 A.25 B. 5 C. 21 D. 1 4、正弦函数sin t ω的拉氏变换是〔〕 A.ω+s 1 B.22s ω+ω C.22s s ω+ D. 22s 1ω+ 5、比例环节的频率特性相位移θ<ω>= < >A.90°B.-90°C.0°D.-180°6、一阶系统的阶跃响应, < > A.当时间常数T 较大时有振荡 B.当时间常数T 较小时有振荡C.有振荡D.无振荡7、系统特征方程式的所有根均在根平面的左半部分是系统稳定的 < >A.充分条件B.必要条件C.充分必要条件D.以上都不是8、时域分析法研究自动控制系统时最常用的典型输入信号是〔〕A .脉冲函数B .斜坡函数C .抛物线函数D .阶跃函数9、令线性定常系统传递函数的分母多项式为零,则可得到系统的 <>A .代数方程B .特征方程C .差分方程D .状态方程10、线性定常系统的传递函数,是在零初始条件下〔〕A .系统输出信号与输入信号之比B .系统输入信号与输出信号之比C .系统输入信号的拉氏变换与输出信号的拉氏变换之比D .系统输出信号的拉氏变换与输入信号的拉氏变换之比二、填空题〔每空2分,共计40分〕1、系统的稳态误差与输入信号的形式与、有关。

2、对于一个自动控制系统的性能要求可以概括为三个方面:、和。

第六章 数字PID算法习题及答案

第六章试题一、填空1. 在一般工业过程控制系统中常用的经典控制规律是PID 控制规律,即比例积分微分控制规律。

2. 采用类似于模拟调节规律的设计方法来设计数字调节规律的前提条件是采样周期足够短。

3. 位置式PID 调节规律的数学表达式为D 0I (){()()[()(1)]}n p j T T u n K e n e j e n e n T T==++--∑ 4. 增量式PID 调节规律的数学表达式为D I (){()(1)()[()2(1)(2)]}p T T u n K e n e n e n e n e n e n T T∆=--++--+- 5. 偏差平均型改进PID 算法可以提高数字PID 控制系统对偏差信号中混入的高频干扰信号的抑制能力。

6. 数字PID 算法参数整定的内容包括比例度、积分时间常数、微分时间常数和控制周期。

~二、选择1. 采用类似于模拟调节规律的设计方法来设计数字调节规律的前提条件是(A )。

(A )采样周期足够短 (B )采样周期足够长(C )用差分方程代替微分方程 (D )先将系统离散化三、判断。

1. 在利用临界比例度PID 参数整定法进行整定时,应使系统工作于开环状态。

(×)应使系统工作于闭环状态,以便产生临界振荡。

1. 在利用临界比例度PID 参数整定法进行整定时,应使系统工作于闭环状态。

(√)2. 在利用衰减曲线PID 参数整定法进行整定时,应使系统工作于开环状态。

(×) 衰减曲线PID 参数整定法进行整定时系统应处于闭环工作状态。

—2. 在利用衰减曲线PID 参数整定法进行整定时,应使系统工作于闭环状态。

(√)33. 在利用响应曲线法进行PID 参数整定时,应使系统工作于开环状态。

(√)3. 在利用响应曲线法进行PID 参数整定时,应使系统工作于闭环状态。

(×) 系统应处于开环。

4. 所谓积分饱和指的是数字PID 算法中,积分项的运算结果超出了计算机对数据的表示能力。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

复习题(开卷)一、填空题(本大题共10小题,每空1分,共20 分)1.一般把EDA技术的发展分为MOS时代、MOS时代和ASIC三个阶段。

2.EDA设计流程包括设计输入、设计实现、实际设计检验和下载编程四个步骤。

3.EDA设计输入主要包括图形输入、HDL文本输入和状态机输入。

4.时序仿真是在设计输入完成之后,选择具体器件并完成布局、布线之后进行的时序关系仿真,因此又称为功能仿真。

5.VHDL的数据对象包括变量、常量和信号,它们是用来存放各种类型数据的容器。

6.图形文件设计结束后一定要通过仿真,检查设计文件是否正确。

7.以EDA方式设计实现的电路设计文件,最终可以编程下到FPGA和CPLD芯片中,完成硬件设计和验证。

8.MAX+PLUS的文本文件类型是(后缀名).VHD。

9.在PC上利用VHDL进行项目设计,不允许在根目录下进行,必须在根目录为设计建立一个工程目录。

10.VHDL源程序的文件名应与实体名相同,否则无法通过编译。

一、填空题与简答题1、ASIC的中文含义是:专用集成电路。

2、在VHDL中主要有哪三种重载现象参数类型的重载;参数数目的重载;函数返回类型的重载。

3、简单可编程逻辑器件的主要有PROM、PLA、PAL、GAL4、CPLD内部含有多个逻辑单元块,每个逻辑单元块相当于一个GAL器件:5、在设计中,常常采用的设计方法有直接设计方法、自顶向下和自底向上的设计方法。

6、CPLD的一般采用“与-或阵列”结构。

7、一个完整的VHDL程序包括库、程序包、实体、结构体和配置五个部分。

8、PLD的中文含义是:可编程逻辑器件。

9、“与-或”结构的可编程逻辑器件主要由四部分构成:输入电路、可编程“与”阵列、可编程或阵列、输出电路10、FPGA的一般采用“查找表”结构。

11.VHDL的全拼Very high speed integrated Hardware Description Language12.子程序有即过程(PROCEDURE)、函数〔FUNCTION〕两种类型。

13、CPLD的中文含义是复杂可编程逻辑器件。

14、复杂可编程逻辑器件的主要有CPLD 和FPGA 。

15、FPGA的中文含义是现场可编程门阵列。

16.CPLD的基本结构看成由可编程逻辑宏单元可编程I/O控制模块和可编程内部连线组成。

17.FPGA由可编程逻辑块(CLB)、可编程互连单元(I/O)和可编程互连三种可编程电路和一个SRAM结构的配置存储单元组成。

18.EDA:电子设计自动化B:逻辑阵列块20.ESB:嵌入式系统块21.FAST TRACK:快速通道22.同步:各个逻辑单元共用一个时钟23.信号与变量使用时有何区别?答:(1)值的代入形式不同。

(2)变量值可以送给信号,信号值不能送给变量。

(3)信号是全局量,变量是局部量。

(4)操作过程不同。

24.VHDL语言在结构上分为哪几部分?答:VHDL语言在结构上一般分为实体(ENTITY)与结构体(ARCHITECTURE)两大部分。

25.说明端口模式INOUT和BUFFER有何异同点。

答:INOUT:双向端口;BUFFER:输出并向内部反馈。

INOUT是双向信号,既可输入又可输出。

BUFFER是输出并向内部反馈。

也是实体的输出信号,但作输入用时,信号不是由外部驱动,而是从反馈得到。

26.进程如何激活,敏感信号有何要求(注意事项)答:当一个进程的敏感信号值发生变化时,该进程被激活。

或当无敏感信号列表时,可通过满足条件的WAIT语句来启动进程语句进程的敏感信号A:是该进程描述的模块的输入信号。

B:使用了敏感信号表的进程中不能含有任何等待语句。

27、何为函数与过程重载?答:VHDL允许以相同的函数名定义函数,但要求函数中定义的操作数具有不同的数据类型,以便调用时用以分辨不同功能的同名函数。

同样名称的函数可以用不同的数据类型作为此函数的参数定义多次,此函数称为重载函数。

两个或两个以上具有相同的过程名和互不相同的参数及参数类型的过程称为重载过程。

28、什么是基于乘积项的可编程逻辑结构?什么是基于查找表的可编程逻辑结构?GAL、CPLD之类都是基于乘积项的可编程结构;即包含有可编程与阵列和固定的或阵列的PAL(可编程阵列逻辑)器件构成。

FPGA(现场可编程门阵列)是基于查找表的可编程逻辑结构。

FPGA(Cyclone/Cyclone II)系列器件主要由逻辑阵列块LAB、嵌入式存储器块(EAB)、I/O单元、嵌入式硬件乘法器和PLL等模块构成;二、解释与分析程序(注:些类题要求A、解释带有下划线的语句;B、说明该程序逻辑功能;C、回答部分问题,所以一定看懂程序每一句意思,弄清程序功能)1、程序如下:要求:1.解释带有下划线的语句。

2.画出该程序的原理图符号。

3.说明该程序逻辑功能。

Library ieee; 定义元件库Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Entity up_down is 实体说明Port(clk,rst,en,up: in std_logic;Sum: out std_logic_vector(2 downto 0);Cout: out std_logic);End up_down;Architecture a of up_down is 结构体说明Signal count: std_logic_vector(2 downto 0);BeginProcess(clk,rst) 进程,敏感信号为clk rstBeginIf rst=’0’thenCount<=(others=>’0’); 异步清零Elsif rising_edge(clk)then 上升沿If en=’1’then 计数控制端EN=1Case up isWhen ‘1’=> count<=count+1;UP=1加法计数When others =>count<=count-1; UP=0减法计数End case;End ifEnd if;End process;Sum<=count;Cout <=’1’when en=’1’and ((up=’1’and count=7) or (up=’0’and count=0)) else ‘0’;进位信号End a;程序功能:异步清零,同步计数的三位二进制可逆计数补题:3-5设计含有异步清零和计数使能的16位二进制加减可控计数器。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT16 ISPORT(CLK,RST,EN:IN STD_LOGIC;CHOOSE:IN BIT;SETDATA:BUFFER INTEGER RANCE 65535 DOWNTO 0;COUT: BUFFER INTEGER RANCE 65535 DOWNTO 0);END CNT16;ARCHITECTURE ONE OF CNT16 ISBEGINPROCESS(CLK,RST,SDATA)V ARIABLE QI:STD_LOGIC_VECTOR(65535 DOWNTO 0);BEGINIF RST='1' THEN --计数器异步复位QI:=(OTHERS=>'0');ELSIF SET=’1’THEN-计数器一步置位QI:=SETDATA;ELSIF CLK'EVENT AND CLK='1' THEN --检测时钟上升沿IF EN=’1’THEN –检测是否允许计数IF CHOOSE=’1’THEN --选择加法计数QI:=QI+1; --计数器加一ELSE QI=QI-1; --计数器加一END IF;END IF;END IF;COUT<=QI;--将计数值向端口输出END PROCESS;END ONE;3-6、图3—18是一个含有上升沿触发的D触发器的时序电路,试写出此电路的VHDL设计LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MULTI ISPORT(CL:IN STD_LOGIC; -- 输入选择信号CLK0:IN STD_LOGIC; -- 输入信号OUT1:OUT STD_LOGIC);-- 输出端END ENTITY;ARCHITECTURE ONE OF MULTI ISSIGNAL Q : STD_LOGIC;BEGINPR01: PROCESS(CLK0)BEGINIF CLK ‘EVENT AND CLK= ’1 ’THEN Q<=NOT(CL OR Q);ELSEEND IF;END PROCESS;PR02: PROCESS(CLK0)BEGINOUT1<=Q;END PROCESS; END ARCHITECTURE ONE; END PROCESS;(分3行写)5-13设计8位左移移位寄存器,给出时序仿真波形LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY SHFRT_L ISPORT (CLK,LOAD :IN STD_LOGIC;DIN :IN STD_LOGIC_VECTOR(7 DOWNTO 0);QB :OUT STD_LOGIC);END;ARCHITECTURE SHFRT_L OF SHFRT_L ISBEGINPROCESS(CLK,LOAD)V ARIABLE REG8 : STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINIF CLK'EVENT AND CLK='1' THENIF LOAD ='1' THEN REG8 :=DIN;ELSE REG8 (7 DOWNTO 1) :=REG8 (6 DOWNTO 0);END IF;END IF;QB<= REG8(0);END PROCESS;END SHFRT_L;2、参考第三、五、九、十章三、编程题四、程序题(简单,不提供2.用VHDL语言描述一个基本D触发器(6分)。

LIBRARYIEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITYdff2 ISPORT(d, clk: IN STD STD_LOGIC;q : OUT STD__LOGIC);END dffe2;ARCHITECTURE a OF dffe2 ISBEGINPROCESS(clk,d)BEGINIF clk’event AND clk=’1’THENq<=d;END IF;END PROCESS;END a;1、用VHDL语言对1 位全加器进行描述如图1位全加器是由二个一位半加器组成,其符号表示为右边的图即f_adder。