实验三 译码器、数据选择器及其应用

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验三译码器、数据选择器及其应用一、实验目的

1.熟练掌握集成译码器、数据选择器的工作原理、逻辑功能。2.熟练掌握集成译码器、数据选择器实现某些逻辑函数。

二、实验器件

1、3线-8线译码器74LS138×1

2、8选1数据选择器74LS151×1

3、4输入二与非门74LS20×1

4、六反相器74LS04×1

三、实验内容

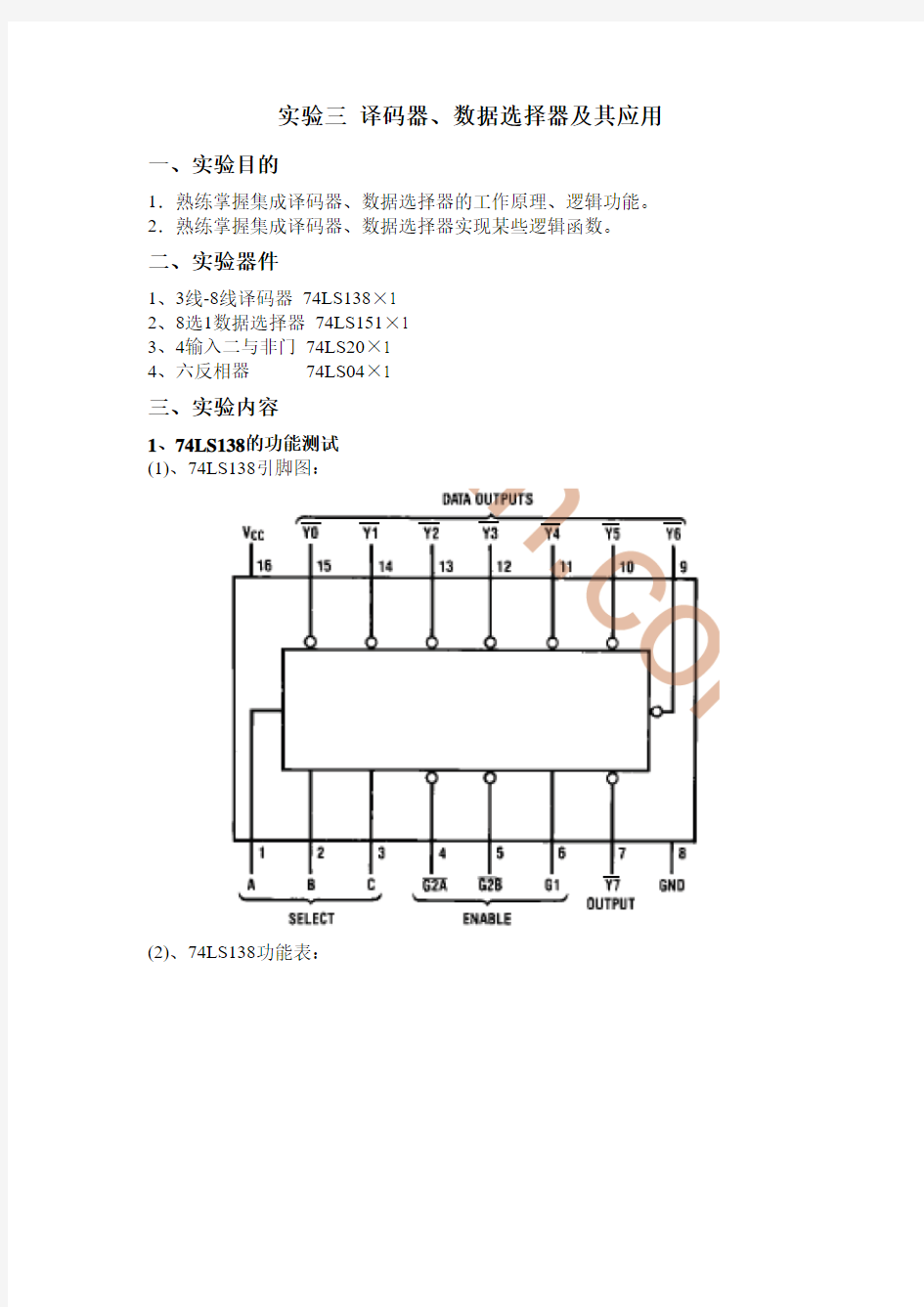

1、74LS138的功能测试

(1)、74LS138引脚图:

(2)、74LS138功能表:

注:2G =G 2A +G 2B

2、74LS138用作逻辑函数发生器

(1)、用74LS138和门电路实现逻辑函数 F=AB+AC+BC 实验步骤:

将逻辑函数转化为最小项逻辑表达式

画卡诺图:

由卡诺图得到:F=A BC+A B C+AB C +ABC=Σm (3,5,6,7) =7.6.5.3m m m m

=7.6.5.3Y Y Y Y

用一片74LS138和一片74LS20搭建电路:

(2)、用74LS138和门电路实现逻辑函数F=A BC+A B C+AB C(判偶电路)

(3)、用74LS138和门电路设计一个全加器

3、74LS151功能测试

(1)、74LS151引脚图:

(2)、74LS151功能表:

4、74LS151和门电路实现逻辑函数

(1)、用74LS151和门电路实现逻辑函数F=AB+AC+BC

实验步骤:

将逻辑函数转化为最小项逻辑表达式

画卡诺图:

由卡诺图得到:F=A BC+A B C+AB C+ABC=Σm(3,5,6,7)

=m0.0+m1.0+m2.0+m3.1+m4.0+m5.1+m6.1+m7.1

74LS151输出Y=m0.D0+m1.D1+m2.D2+m3.D3+m4.D4+m5.D5+m6.D6+m7.D7若令F=Y,A=C,B=B,C=A

则D0= D1= D2= D4=0

D3= D5= D6= D7=1

根据以上分析,画出电路图:

(2)、用数据选择器74LS151实现函数F=Σm (0,2,7,8,13)。

F=A B C D+A(B C D)+A(BCD)+A B C D+A(B C D)

=(A+A)B C D+ A(B C D)+A(BCD)+A(B C D)

=1.m0+A.m2+A. m5+A m7

74LS151输出Y=m0.D0+m1.D1+m2.D2+m3.D3+m4.D4+m5.D5+m6.D6+m7.D7若令F=Y,B=C,C=B,D=A

则D0=1,D2= D7=A,D5=A

D1= D3 =D4 =D6=0

根据以上分析,画出电路图:

四、实验报告

1、整理实验1、

2、

3、4的实验内容。