五段指令流水线kppt

计算机体系结构之流水线技术(ppt 125页)

张伟 计算机学院

大纲

1 概念定义 2 流水线分类 3 MIPS五级流水线 4 性能分析 5 流水线相关 6 高级流水线技术

1 概念定义

洗衣店的例子

A, B, C, D 均有一些衣物要 清洗,甩干,折叠

清洗要花30 分钟 甩干要用40 分钟 叠衣物也需要20 分钟

流水线输出端任务流出的顺序与输入端任务流 入的顺序相同。

异步流动流水线(乱序流水线):

流水线输出端任务流出的顺序与输入端任务流 入的顺序不同。

3 MIPS五级流水线

DLX(Dancing Links)

DLX 是一种简单的指令集(教学、简单芯片) 在不流水的情况下,如何实现DLX。

实现DLX指令的一种简单数据通路

4. 存储器访问周期MEM(Memory Access) 5. 写回周期WB(Write Back)

MIPS的简单实现

Instruction Fetch

Instr. Decode Reg. Fetch

Next PC

Next SEQ PC

4

RS1

RS2

Execute Addr. Calc

Zero?

RD

增加了向后传递IR和从MEM/WB.IR回送到通用寄存 器组的连接。

将对PC的修改移到了IF段,以便PC能及时地加 4,为取下一条指令做好准备。

2. 每一个流水段进行的操 作

IR[rs]=IR6..10 IR[rt]=IR11..15 IR[rd]=IR16..20

流水线的每个流水段的操作

将有效地址计算周期和执行周期合并为一个时钟周期,这

是因为MIPS指令集采用load/store结构,没有任何指令

需要同时进行数据有效地址的计算、转移目标地址的计算

计算机系统结构之流水线技术(205页)

入 求阶差

△t

对阶 △t

尾数相加 △t

出 规格化

△t

▲

31/206

1. 时空图 ➢ 时空图从时间和空间两个方面描述了流水线的工作 过程。时空图中,横坐标代表时间,纵坐标代表流 水线的各个段。 ➢ 4段指令流水线的时空图:

空间

存结果

123456

执行 译码

123456

5

123 45 6

取指令 1

2

3

4

k…+…1 k+j

已经由指令分析器预处理完成,存放在先行操作栈中的 RR*型指令,指令所需要的操作数已经读到先行读数栈中

k…+…j+1 k+j+n

已经由指令分析器预处理完成,存放在先行操作栈中,指 令所需要的操作数还没有读到先行读数栈中

k+j+n+1 正在指令分析器中进行分析和预处理的指令

k…+…j+n+2 已经从主存储器中预取到先行指令缓冲栈中的指令 k+j+n+m

1

2

3

…

1

2

3

…n

1

2

3

…

n

2

3

k

ti

i1

…n (n-1)t2

Tk 各段执行时间不相等的流水线及其时空图

n

时间

▲

33/206

2 流水线的基本概念

➢ 流水线每一个功能部件的后面都要有一个缓冲寄 存器(锁存器),称为流水寄存器。

站的某个存储单元(设其地址为j),同时用j替换原来指令

中的目标地址码字段。

✓ 立即数型指令:把指令中的立即数送入读数站(设为第l个 存储单元),同样也用l替换原来指令中的立即数字段。

计算机体系结构PPT教学课件-第三章流水线

• Can “launch(开始)” a new computation every 100ns in this structure • Can finish 107 computations per second

3-8

• Can launch a new computation every 20ns in pipelined structure • Can finish 5×107 computations per second

3-12

流水线的描述

• Spatio-temporal(时空的) chart

流水节拍

4+ n-1

Drain

n-1 n n-1 n n-1 n n-1 n tn tn+3 time

时间,以机器周期为单位

– Relation of pipeline and tasks in sequence

Fill balanced

流水线的洗衣 ----开始工作越快越好

6 PM 7 8 9

Time T a s k O r d e r

10

11 Midnight

30 40 40 40 40 20

A B C D

• Pipelined laundry takes 3.5 hours for 4 loads

3-6

Why pipelining : overlapped(重叠)

3-3

Why Pipelining: Its Nature(流水线的本质)

• Laundry(洗衣店)

A – Ann, Brian, Cathy, Dave each have one load of clothes to wash, dry, and fold B C D

常用五段流水线解释

DADD操作的结果在后面三条指令中都使用,这就产生了 数据冒险。

上述的数据冒险可以用一个简单的硬件技术— 直通(旁路)来解决。把DADD的结果从EX/MEM 寄存器移到DSUB需要的地方,即ALU输入锁存器 ,具体做法:

1.从EX/MEM流水线寄存器送入到ALU的结果总 是反馈到ALU的输入锁存器。

谢谢!

流水线可以减少指令的平均执行时间,可以认 为是减少了每条指令的CPI,也可以认为是减少了 时钟周期的长度。流水线是一种在连续指令流中 开发指令集并行性的技术,对编程者是透明的。

1.2 RISC指令系统的简单实现

执行每条指令最多只要5个时钟周期: 1.取指令周期(IF) 2.指令译码/读寄存器周期(ID) 3.执行/有效地址周期(EX) 4.访问存储器(MEM) 5.写回周期(WB)

在取指周期,根据PC指示的地址从存储器中取指令并装 入到IR中,同时PC+4以获取下一条指令地址。

在指令译码/读寄存器周期,对指令进行译码并访问寄存 器堆以读出寄存器中的内容,对寄存器中的内容进行比较, 判断是否是转移指令,计算下调指令的地址。

在执行/有效地址周期(EX),对上一周期准备好的操作 数进行运算,有三种指令:访问寄存器,寄存器-寄存器AL 指令,寄存器-立即数ALU指令。

2.如果直通硬件检测到前一次ALU操作写入的 寄存器正好是当前ALU操作的数据来源,那么控制 逻辑就选择直通结果作为ALU的输入。效果如下图

并不是所有的数据冒险都可以采用直通 技术来解决,下面指令:

LD

R1,0(R2)

DSUB

R4,R1,R5

AND

R6,R1,R7

OR

R8,R1,R9

指令流图如下图所示:

在访问存储器(MEM),load指令将根据上一周期得到 的有效地址从存储器中读取数据,store指令则根据有效地址 将第二个寄存器中的数据写入存储器。

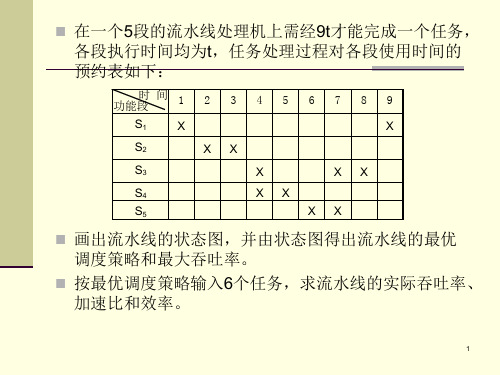

在一个5段的流水线处理机上需经9t才能完成一个任务参考课件

E X ( 执 行 ) R 1 X 2 B 2

D 2

3 1

“执行指令”执行由第二地址((X2)+(B2)+D2)决定的 主存数据区中的指令。

6

2.主存操作数相关

发生主存操作数相关的指令序列: n:OP A1,A2,A3 ;A1=(A2) OP (A3)

n+1:OP A1,A2,A3 ;A1=(A2) OP (A3) 出现下列情况之一,就发生主存操作数相关:

控制相关:由条件分支指令、转子程序指令、中断等引起的相 关。

解决数据相关的方法有两种: 推后处理 设置专用路径。

3

1.指令相关

发生指令相关的情况: n: STORE R1, n+1 n+1: …… 满足关系: 结果地址(n)=指令地址(n+1)

当第n条指令还没有把执行结果写到主存之前,取出 的第n+1条指令显然是错误的。

的入口处增设一个专门处理无条件转移指令的指令分析器 P270

8

解决通用寄存器数据相关的方法: 方法一:把读操作数、写运算结果与指令执行合在一

个节拍。 从数据从通用寄存器读出,在运算器中完成运算, 结果写回通用寄存器的整个回路中,只有通用寄存 器是时序逻辑。在通用寄存器到运算器之间建立直 接数据通路,即不设置缓冲寄存器或锁存器,则不 会发生通用寄存器数据相关。 这种情况下,实际上不需要分析周期,在一个节拍 中就可以完成从通用寄存器中通过两个多路选择器 分别读操作数到通用寄存器。

则发生LOAD数据相关。 • 解决方法:

11

K:

ADD读R1开始 LOAD写R1完成

IF

ID

EX

WR

K+1:

IF

计算机体系结构之流水线技术(ppt 125页)

EX/MEM.IR ← ID/EX.IR; EX/MEM.ALUo ←

ID/EX.NPC + ID/EX.Imm<<2;

EX/MEM.cond ←

ID/EX.A op ID/EX.Imm;

(ID/EX.A ==0);

(动画演示)

北京信息科技大学

(动画演示)

(动画演示)

流水段

流水线的每个流水段的操作 任何指令类型

按照数据表示来分 标量处理机:

不具有向量指令和向量数据表示,仅对标量进 行流水处理的处理机。

例如:IBM360/91, Amdahl 470V/6 等 向量处理机:

具有向量指令和向量数据表示的处理机。 例如:TI ASC, CRAY-I 等

北京信息科技大学

流水线的分类(6)

数据

M

存储器

U X

4

IR

北京信息科技大学

流水实现的数据通路

计算机体系结构

寄存器的命名形式为:x.y 所包含的字段的命名形式为:x.y[s]

其中:x:流水寄存器名称 y:具体寄存器名称 s:字段名称

例如: ID/EX.IR:流水寄存器ID/EX中的子寄存器IR IRID/EX.IR[op]:该寄存器的op字段(即操作码字

ID/EX.A ← Regs[IF/ID.IR[rs]];ID/EX.B ← Regs[IF/ID.IR[rt]];

ID

ID/EX.NPC ← IF/ID.NPC;ID/EX.IR ←IF/ID.IR; ID/EX.Imm ← (IF/ID.IR16)16##IF/ID.IR16..31;

(动画演示)

计算机体系结构

3 流水线技术

张伟 计算机学院

流水线技术ppt课件

◆ 线性流水线:流水线中的各段串行连接,没有反 馈回路。 ◆ 非线性流水线:流水线中的各段除有串行连接 外,还有反馈回路。

6. 按照流动是否可以乱序来分

◆ 顺序流动流水线:流水线输出端任务流出的顺 序 与输入端任务流入的顺序相同。

◆ 异步流动流水线(乱序流水线):流水线输出 端 任务流出的顺序与输入端任务流入的顺序不同。

(2) 编译器可以通过重新排列代码的顺序来消 除这种暂停,这种技术称为流水线调度或

指令调度;

(3) 举例: 例3.6 请为下列表达式生成没有暂停的DLX

指令序列: a=b+c ; d=e-f ;

假设载入延迟为1个时钟周期。

3.3.1 控制相关

(一)分支引起的暂停及减少分支开销的方法

1. 分支指令的执行结果

(4) 由于效率

E = 1─+─m1─-n─1 ─

而加速比

S = 1─+─mm─-n─1 ─

因此

E

=

─S─ m

说明效率和加速比成正比

又由于吞吐率:

因此 TP = (─1─+──m1─n-1─)△─t0 E =TP △t0 说明效率和吞吐率成正比

提高流水线效率所采取的措施对于提高 吞吐率也有好处。

例如:动态流水线。

3.2 流水线性能分析

1. 吞吐率

吞吐率是指单位时间内流水线所完成的任务 数或输出结果的数量。

(1) 最大吞吐率TPmax

最大吞吐率是指流水线在连续流动达到稳定状 态后所得到的吞吐率。

◆ 若流水线各段的时间相等,均为△t0 , 则: TPmax= 1 /△t0

◆ 若流水线各段的时间不等,则:

(“流水线气泡”或“气泡”) 引入暂停后的时空图 解决方法Ⅱ: 设置相互独立的指令存储器和数据 存储器或设置相互独立的指令Cache 和数据Cache。

五段式流水线CPU

五段式流⽔线CPU流⽔线CPU⼀、流⽔线CPU概述1、流⽔线CPU的原理流⽔线CPU是为提⾼吞吐量⽽创造的,五段式流⽔线CPU的吞吐量是单周期CPU的五倍,同⼀时间CPU上最多有五条指令在运⾏。

如何达到同⼀CPU上五条指令呢?答案就在于把每条指令都拆分成五个阶段,按照CPU硬件执⾏流来拆成五段:IF(instruction fetch)、DEC(decode)、EXE(execute)、ME(memory)、WB(write back),CPU上五段部分分别执⾏⼀条指令的⼀个阶段。

因为CPU上五段分别进⾏不同指令的不同阶段,每段都需要⾃⼰当前执⾏指令的数据:IF段所⽤数据为指令地址,可有pc寄存器提供;DE、EXE、ME、WB段所⽤数据包含但不限于指令内容,⼀定需要对应流⽔线寄存器保存。

2、流⽔线CPU设计的难点流⽔线CPU同时有多条指令运⾏,⼀个很重要的设计因素是解决冲突。

冲突包含硬件冲突、控制冲突和数据冲突。

硬件冲突硬件冲突是说同⼀时刻需要对同⼀互斥硬件(⼀次只允许⼀次读或写)进⾏访问,举例来说,D段需要从存储器中取出指令,M段需要对存储器写⼊数据,这两个操作同时进⾏就会带来冲突,在这⾥IM和DM是独⽴的两个存储器,因此不必考虑。

控制冲突控制冲突是分⽀指令和跳转指令带来的冲突。

分⽀指令的最终分⽀地址晚于下⼀周期到来,导致下⼀条指令的地址不能及时算出或者决定;跳转指令的跳转地址晚于下⼀周期到来,导致上述同样冲突。

解决这样的冲突主要是通过假设不跳转或者延迟槽。

假设不跳转是说先假设不跳转和分⽀,正常执⾏下⼀条指令,当计算出要跳转时清楚已执⾏的结果。

延迟槽是说跳转指令后⾯加空指令nop,即等待跳转地址计算出来再决定是继续下⼀条指令还是跳转。

数据冲突数据冲突是关于数据“新鲜性”的冲突。

指令的执⾏离不开寄存器,有的指令会利⽤寄存器数据,有的指令会写回寄存器,有的指令两者皆有,当前序执⾏的指令的⽬的寄存器(将要写回的寄存器)和后序执⾏的指令的源寄存器(利⽤其数据的寄存器)相同时,就存在数据关联。

计算机技术第6章超标量流水线ppt课件

CMP BYTE PTR [EBX+8], 1 或者只能在 U 流水线配对

; 不能配对,

CMP BYTE PTR [EBX], 1

; 可以配对

CMP BYTE PTR [EBX+8], AL ; 可以配对

10

(4) 带前缀(JCC指令的0F除外)的指令只能出现在U流水线中 例如: ①用段前缀对非缺省段寻址的指令。 ②在32位代码中使用16位的数据,或16位的代码中使用32

17

• Pentium浮点部件的“栈项瓶颈”是怎样形成的 ? 及如何解决?

• Pentium微处理机堆栈结构要求进行堆栈操作的所 有指令,在堆栈栈顶要有一个源操作数。因为绝大 多数指令总是希望用堆栈栈顶作为它们的目的操作 数。所以大多数指令看到的仿佛是一个“栈项瓶 颈”,在向栈顶发送一条算术运算指令之前,必须 先把源操作数传送至栈顶。

K+2 k+1

K

k-1

指令 指令 k-2 k-3

指令 指令 k-4 k-5

n+3周期

指令 指令 指令 指令

k+3

k+2 k+1 K

指令 指令 指令 指令

k-1 k-2 k-3

k-4

n+4周期

指令 指令 指令 指令 指令 指令

K+4 k+3

k+2 k+1 K

k-1

指令 指令 k-2 k-3

n+5周期

指令 指令 指令 指令 K+5 k+4 k+3 k+2

11

• 例6-1 程序段如下:

MOV AX,5 INC BX ADD AX,BX XOR CX,CX MOV DX,8 INC DX

五段指令流水线kPPT课件

五段流水线模拟

1、第一条指令的MEM阶段,第二条指令的EX阶段 ,第三台指令的ID阶段,第四条指令IF阶段。

4

五段流水线模拟

1、第一条指令的WB阶段,第二条指令的MEM阶 段,第三台指令的EX阶段,第四条指令ID阶段第五 条指令IF阶段。

5

五段流水线模拟

1、第一条指令的WB阶段,第二条指令的MEM阶 段,第三台指令的EX阶段,第四条指令ID阶段第五 条指令IF阶段。现:五段指令部分用链表来实现。定义 一个头结点*Head,中间节点共5个。用*next相连。 当到达最后一个阶段WB的NEXT,直接删除( delete this).同时用一个静态变量t来控制时钟。 设置成一个时钟函数。

7

五段流水线模拟

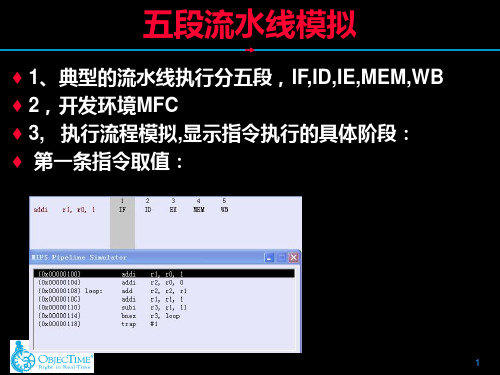

1、典型的流水线执行分五段,IF,ID,IE,MEM,WB 2,开发环境MFC 3, 执行流程模拟,显示指令执行的具体阶段: 第一条指令取值:

1

五段流水线模拟

1、第一条指令的ID阶段,第二条指令的IF阶段

2

五段流水线模拟

1、第一条指令的EX阶段,第二条指令的ID阶段,第 三台指令的IF阶段。

经典MIPS五级流水介绍

三种MIPS核心指令

1 算术逻辑运算指令(ALU instruction)

2 存储指令(load or store instruction) 3 分支指令(branch instruction)

三种指令格式:

R型 I型

J型

op rs rt rd shamt funct

Thanks~~

op

PC

address

..

字

通常,一条MIPS指令包含的五个处理步骤:

1) 从存储器中读取指令。 2) 指令译码的同时读取寄存器。MIPS的 指令格式允许指令译码和读取寄存器同时 进行。 3)执行操作或地址计算。 4)在数据存储器中读取操作数。 5)将结果写回寄存器堆。

利用流水线实现MIPS指令

五条指令对应的多时钟周期流水线图

传统表示方式下多周期流水线图

单周期数据通路图

引入流水线寄存器

从之前的流水线数据通路图可以看出,数 据通路需要的值都是从上一级寄存器中流 入下一级中。 我们用被这些寄存器分开的两个阶段来命 名它们,如IF和ID阶段之间的流水线寄存 器叫做IF/ID。

○

三种流水线冒险

数据冒险 一个操作必须等待另一个操作完成后才 能进行时,流水线必须停顿,我们称这种情况为 数据冒险。 转发(forward) 也叫旁路(bypass)。上一个 操作的结果产生以后不必写回寄存器,直接转发 给下一条指令。可以消除部分数据冒险。 阻塞(stall)当一条指令试图读取一个寄存器而 它前一条指令是load指令,并且该load指令写入 的是同一寄存器时,必须采用相应的机制阻塞流 水线。

五种MIPS寻址模式的图示:

1.立即数寻址

计算机组成原理 第15讲_流水线

m e0 n m t0 m m m T 若各段时间不等,则各段的效率也不等,整个流水线的效率

整个流水线的效率

i

e E

E

n t i

i 1

取指k 分析k 执行k 取指k+1 分析k+1 执行k+1 取指k+2 ……

顺序方式的优点是控制简单。 缺点是速度上不去,机器各部件的利用率不高。

6

2.重叠方式 Overlap 在解释第k条指令的操作完成之前,就可开始解释第k+1条指令。 例如,把解释一条机器指令分为:取指,执行,两个子过程。 取指k 执行k

4

§6.5 流水线工作原理

计算机的速度可以用每秒执行的指令条数来表示。 指令的解释 怎样加快一条指令的解释过程? 为了加快单条指令的解释过程可采用的方法有:

•选用更高速的器件

•减少解释过程所需拍数 •使解释过程的各个动作并行执行 指令的解释可以有三种控制方式:顺序,重叠,流水。

5

1.顺序方式 各条机器指令间顺序串行执行。一条指令执行完之后,才取 下条指令来执行。指令内的各条微指令也是顺序串行执行的。 例如,把解释一条机器指令分为:取指,分析,执行,3个 子过程。

10

时空图 Space-Time-Diagram 各功能段时间不等

空间 执行 (功能段)

1

2

3

4 4

取数

分析 取指

11 Βιβλιοθήκη 2 22 333 4

4

气泡 Bubble

时间

t0 t1 t2 t3 t4 t5 t6 t7 t8 t9 t10 t11 t12 t13 t14

第 3 章 流水线技术标量.ppt

浮点加

(b)定点乘法 22(c)浮点加法

浮点点积 (d)浮点点积

3. 按工作方式分

• ⑴ 静态流水线 • 在同一时间内,流水线只能以一种功能方式工作。

• 静态流水线可以是单功能的,也可以是多功能的。 当是多功能流水线时,则从一种功能方式变为另 一种功能方式时,必须先排空流水线,然后为另 一种功能设置初始条件后方可使用。

• 设完成一个任务需要的时间为T,则

•

∴

t

m↗

T 或m

Δt

↙T都pma可x 以增1t 加 流mT 水线的吞吐率。

加工。 • ⑶ 各流水段所需时间应尽量相等,以减少流水线

的瓶颈影响。 • ⑷ 流水线工作阶段可分为建立(装入)、满载和排

空三个阶段。 • ⑸在理想情况下,当流水线充满后,每隔Δ t时间

将会有一个结果流出流水线。

2020/1/16

17

3.2.2 标量流水分类(简述)

• 1.按处理级别分 • ⑴ 部件级——运算操作流水线 • 将复杂的算逻运算分段组成流水工作方式。 • 例:将浮点加法操作分成求阶差、对阶、尾数相

2020/1/16

27

非线性流水线

反馈回路

• 流水线的流动顺序: • S1→S2 →S3 →S2 →S3 →S4 →S1 →S2

2020/1/16

28

123456789

s1 1

1

s2

1

1

1

s3

1

1

s4

1

• 为了防止两条或两条以上的指令对同一功能段的 争用,非线性流水线需要对输入流水线的指令进 行比较复杂的控制。

n Tp Tm

• 流水线达到稳定状态后可获得的吞吐率。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

6

五段流水线模拟

部分代码实现:五段指令部分用链表来实现。定义 一个头结点*Head,中间节点共5个。用*next相连。 当到达最后一个阶段WB的NEXT,直接删除( delete this).同时用一个静态变量t来控制时钟。 设置成一个时钟函数。

7

五段流水线模拟

1、典型的流水线执行分五段,IF,ID,IE,MEM,WB 2,开发环境MFC 3, 执行流程模拟,显示指令执行的具体阶段: 第一条指令取值:

1

五段流水线模拟

1、第一条指令的ID阶段,第二条指令的IF阶段

Hale Waihona Puke 2五段流水线模拟 1、第一条指令的EX阶段,第二条指令的ID阶段,第 三台指令的IF阶段。

3

五段流水线模拟

1、第一条指令的MEM阶段,第二条指令的EX阶段 ,第三台指令的ID阶段,第四条指令IF阶段。

4

五段流水线模拟

1、第一条指令的WB阶段,第二条指令的MEM阶 段,第三台指令的EX阶段,第四条指令ID阶段第五 条指令IF阶段。

5

五段流水线模拟

1、第一条指令的WB阶段,第二条指令的MEM阶 段,第三台指令的EX阶段,第四条指令ID阶段第五 条指令IF阶段。