3-8自动循环计数器

任务三 三相异步电动机正反转循环运行的PLC控制

(二)设备与器材

表1-22 设备与器材

序号

名称

符号

型号规格

数量 备注

1

常用电工工具

十字起、一字起、尖嘴钳、剥线钳 等

1

2

计算机(安装GX Works3编程 软件)

3

三菱FX5U可编程控制器

PLC

FX5U-32MR/ES

4

三相异步电动机正反转循环运 行控制面板

5

三相异步电动机

6

以太网通信电缆

M

WDJ26,PN=40W,UN=380V, IN=0.2A,nN=1430r/min,f=50Hz

2)学会用三菱FX5U PLC的顺控程序指令编辑三相异步电动机正反转循 环运行控制的程序。

3)会绘制三相异步电动机正反转循环运行控制的I/O接线图。 4)掌握FX5U PLC I/O接线方法。 5)熟练掌握使用三菱GX Works3编程软件编辑梯形图程序,并写入 PLC进行调试运行。

11

项目一 任务三 三相异步电动机正反转运行运行的PLC控制

MPS

栈存储器的第一层, 之前存储的数据依次

下移一层

读取堆栈第一层的 MRD 数据且保存,堆栈内

的数据不移动

读取堆栈存储器第

MPP

一层的数据,同时该 数据消失,栈内的数

据依次上移一层

梯形图表示

FBD/LD表示

ST表示

目标元件

ENO:=MPS(EN);

ENO:=MRD(EN);

无

ENO:=MPP(EN);

对于FX5U PLC默认情况下,16位计数器的个数为256个,对应编号为C0 ~C255;32位超长计数器个数为64个,对应编号为LC0~LC63。

automa循环数组

automa循环数组【原创版】目录1.循环数组的概念2.自动循环数组的特点3.自动循环数组的实现方法4.自动循环数组在编程中的应用5.自动循环数组的优缺点正文循环数组是一种在程序设计中经常使用的数据结构,它可以让程序员在处理大量数据时更加方便快捷。

在众多的循环数组中,自动循环数组因其独特的特点而备受关注。

下面,我们将详细介绍自动循环数组的相关知识。

自动循环数组,顾名思义,是一种可以自动进行循环操作的数组。

它的主要特点在于,当数组中的元素达到最大值时,数组会自动回到数组的起始位置,并重新开始计数。

这种特性使得自动循环数组在处理循环任务时,具有更高的灵活性和效率。

实现自动循环数组的方法有很多,但其中最常用的方法是利用循环计数器。

循环计数器是一个可以记录数组当前位置的变量。

当数组中的元素达到最大值时,计数器会自动重置为零,从而使数组重新开始计数。

这样,程序员就可以通过循环计数器来实现自动循环数组的功能。

自动循环数组在编程中的应用非常广泛。

例如,在处理图形图像时,自动循环数组可以帮助程序员快速地实现图像的平移、缩放等操作。

在处理音频信号时,自动循环数组可以方便地实现音频信号的循环播放。

此外,自动循环数组还可以应用于数据加密、随机数生成等领域。

尽管自动循环数组具有很多优点,但它也存在一些不足之处。

首先,自动循环数组的实现相对复杂,需要程序员具备一定的编程技巧。

其次,自动循环数组在循环过程中,可能会出现数据溢出的现象,这需要程序员及时进行处理。

总的来说,自动循环数组作为一种高效的数据结构,可以帮助程序员在处理大量数据时,提高程序的运行效率。

3位十进制循环计数器

现代电子设计实验报告实验名称:3位十进制循环计数器的设计系(科):信息科学与技术系班级:学号:姓名:完成时间:2012年4月24日. 1 .一、实验内容(一)设计要求1.设计一个3位十进制循环计数器,从0加到999,再恢复到0,循环往复。

每秒计数器加1。

2.有复位功能,当复位端reset为高时,计数器清零,停止计数。

3.可以控制计数的开始start和停止stop。

当计数开始start信号有效时,计数器开始计数;当计数停止stop信号有效时,计数停止;当start信号再次有效时,继续计数。

4.计数器的计数值采用动态显示方式在数码管上显示出来。

5.进行设计,仿真并下载程序到实验箱的CPLD模块板进行验证。

(二)电路模块cyclecntsysclk reset startSE G[6. SCAN[7.★提示:reset信号可以使用拨动开关来产生。

start和stop信号使用按键来实现输入信号:sysclk:基准时钟,50MHz;reset:异步复位信号,高有效;start,stop:计数开始和计数停止信号输入;. 2 .输出信号:SEG[6..0]:段码信号输出。

SCAN[7..0]:位码信号输出。

二、实验原理此系统的核心为一个三位循环计数器,将此计数器的输出结果通过分位电路动态显示到三个数码管上面。

另外的辅助电路分别为四个不同频率的分频器和按键去抖电路。

三、设计方案四、原理图. 3 .. 4 .五、模块设计(一)分频电路1.设计原理分频器就是对较高频率的信号进行分频,得到较低频率的信号。

定义一个计数器对输入时钟进行计数,在计数的前一半时间里,输出高电平,在计数的后一半时间里,输出低电平,这样输出的信号就是占空比为50%的偶数分频信号。

例如,6分频,计数值为0~2输出高电平,计数值为3~5输出低电平。

2.VHDL程序代码输出为1HZ分频电路N=50MHZ/1HZ=50000000Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Use ieee.std_logic_arith.all;Entity fdiv1 isgeneric(N: integer:=50000000); --rate=N,N是偶数port(clkin: IN std_logic;clkout: OUT std_logic);End fdiv1;Architecture a of fdiv1 is. 5 .signal cnt: integer range 0 to n-1;Beginprocess(clkin) --计数beginif(clkin'event and clkin='1') thenif(cnt<n-1) thencnt <= cnt+1;elsecnt <= 0;end if;end if;end process;process(cnt) --根据计数值,控制输出时钟脉冲的高、低电平beginif(cnt<n/2) thenclkout <= '1';elseclkout <= '0';end if;end process;End a;输出为10HZ分频电路N=50MHZ/10HZ=5000000. 6 .Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Use ieee.std_logic_arith.all;Entity fdiv10 isgeneric(N: integer:=5000000); --rate=N,N是偶数port(clkin: IN std_logic;clkout: OUT std_logic);End fdiv10;Architecture a of fdiv10 issignal cnt: integer range 0 to n-1;Beginprocess(clkin) --计数beginif(clkin'event and clkin='1') thenif(cnt<n-1) thencnt <= cnt+1;elsecnt <= 0;end if;end if;end process;. 7 .process(cnt) --根据计数值,控制输出时钟脉冲的高、低电平beginif(cnt<n/2) thenclkout <= '1';elseclkout <= '0';end if;end process;End a;输出为200HZ分频电路N=50MHZ/200HZ=250000Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Use ieee.std_logic_arith.all;Entity fdiv10 isgeneric(N: integer:=250000); --rate=N,N是偶数port(clkin: IN std_logic;clkout: OUT std_logic);End fdiv10;Architecture a of fdiv10 is. 8 .signal cnt: integer range 0 to n-1;Beginprocess(clkin) --计数beginif(clkin'event and clkin='1') thenif(cnt<n-1) thencnt <= cnt+1;elsecnt <= 0;end if;end if;end process;process(cnt) --根据计数值,控制输出时钟脉冲的高、低电平beginif(cnt<n/2) thenclkout <= '1';elseclkout <= '0';end if;end process;End a;输出为1000HZ分频电路N=50MHZ/1000HZ=50000Library ieee;. 9 .Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Use ieee.std_logic_arith.all;Entity fdiv10 isgeneric(N: integer:=50000); --rate=N,N是偶数port(clkin: IN std_logic;clkout: OUT std_logic);End fdiv10;Architecture a of fdiv10 issignal cnt: integer range 0 to n-1;Beginprocess(clkin) --计数beginif(clkin'event and clkin='1') thenif(cnt<n-1) thencnt <= cnt+1;elsecnt <= 0;end if;end if;end process;process(cnt) --根据计数值,控制输出时钟脉冲的高、低电平. 10 .beginif(cnt<n/2) thenclkout <= '1';elseclkout <= '0';end if;end process;End a;(二)扫描电路1.设计原理当reset和stop信号起作用时,输出到计数器的信号为低电平,只有当start 和脉冲信号起作用时,输出才为高。

自动循环计数器

数字电子技术课程设计课题二:自动循环计数器一、设计目的1、熟练掌握计数器的应用。

2、加深对加减循环计数和显示电路的理解。

二、设计任务1、用集成计数器实行3~9自动循环计数。

2、电路能实现3~9加法和3~9减法循环计数。

3、输出用数码显示。

三、设计思想1、译码驱动显示部分:计数输出结果送至译码输出显示部分。

2、控制部分:实现加或减循环计数功能由控制部分完成。

3、计数部分:完成BCD码3~9的可逆加或减循环计数。

系统方框图如下:四、单元电路的设计、参数计算、器件介绍:(一)译码驱动显示部分1、采用74LS48 TTL BCD—7 段译码器/内部上拉输出驱动。

由于74LS48输出时高电平有效,所以显示数码管援用LTS547R共阴极数码管。

2、元器件型号的选择及参数的计算:数码管LTS547R,译码/驱动器74LS48;限流电阻的计算,数码管压降一般为1.8~2.2,工作电流10~20mA,经试验,静态显示时10mA,亮度客观,所以限流电阻R1~R7=(5V-2V)/10mA=300Ω。

3、译码驱动、显示电路的设计DBCA为8421BCD码输入端,a—g为7段译码器输出端。

LT灯测试输入使能端。

(二)控制部分及循环加减计数部分1、采用74LS191 TTL 4为同步加/减计数器。

2、控制部分及循环加减计数部分的设计74LS191功能管脚如图所示3、主要逻辑功能(1)同步指数功能当LD’=0时,CP来时,并行输入数据d3~d0被置入。

(2)计数功能取CT’=0 LD’=1当U’/D=0时,对应CP脉冲上升沿,十六进制加法计数。

当U’/D=1时,对应CP脉冲上升沿,十六进制减法计数。

(3)保持功能当CT’=LD’=1时,计数器保持原来的状态不变。

74LS138 TTL 三—8 线译码器状态图如下利用555定时器设计时钟脉冲如图五、总体电路设计图、工作原理及器件清单1、3~9可逆自动循环加或减计数器总体电路如图所示。

电气控制与PLC应用第8章习题与思考题参考解答

第5章S7-200 PLC的指令系统习题与思考题7-200指令参数所用的基本数据类型有哪些?:S7-200 PLC的指令参数所用的基本数据类型有1位布尔型(BOOL)、8位无符号字节型(BYTE)、8位有符号字节型(SIMATIC模式仅限用于SHRB指令)、16位无符号整数(WORD)、16位有符号整数(INT)、32位无符号双字整数(DWORD)、32位有符号双字整数(DINT)、32位实数型(REAL)。

实数型(REAL)是按照ANSI/IEEE 754-1985标准(单精度)的表示格式规定。

2~255字节的字符串型(STRING)即I/O指令有何特点?它应用于什么场合?:立即指令允许对输入和输出点进行快速和直接存取。

当用立即指令读取输入点的状态时,相应的输入映像寄存器中的值并未发生更新;用立即指令访问输出点时,访问的同时,相应的输出映像寄存器的内容也被刷新。

由于立即操作指令针对的是I/O端口的数字输入和数字输出信号,所以它们的位操作数地址只能是物理输入端口地址Ix.x和物理输出端口地址Qx.x。

辑堆栈指令有哪些?各用于什么场合?:复杂逻辑指令,西门子称为逻辑堆栈指令。

主要用来描述对触点进行的复杂连接,并可以实现对逻辑堆栈复杂的操作。

杂逻辑指令包括:ALD、OLD、LPS、LRD、LPP和LDS。

这些指令中除LDS外,其余指令都无操作数。

这些指令都是位逻辑指令。

装载与指令ALD用于将并联子网络串联起来。

装载或指令OLD用于将串联子网络并联起来。

辑推入栈指令LPS,在梯形图中的分支结构中,用于生成一条新的母线,左侧为主控逻辑块时,第一个完整的从逻辑行从此处开始。

辑读栈指令LRD,在梯形图中的分支结构中,当左侧为主控逻辑块时,该指令用于开始第二个和后边更多的从逻辑块。

辑栈弹出指令LPP,在梯形图中的分支结构中,用于恢复LPS指令生成的新母线。

入堆栈指令LDS,复制堆栈中的第n级值,并将该值置于栈顶。

PLC工作台自动往返课程设计

《PLC 》课程设计说明书专业名称:电气工程及其自动化班级:学号:姓名:指导教师:《PLC课程设计》评阅书摘要中型企业普遍采用了先进的自动化系统对生产过程进行控制,但绝大部分小型企业尚未应用自动化系统和产品对生产过程进行控制。

因此,PLC在我国的应用潜力远没有得到充分发挥。

我国工业企业的自动化程度普遍较低,PLC产品有很大的应用空间,如机械行业80%以上的设备仍采用传统的继电器和接触器进行控制。

随着竞争的日益加剧,越来越多的小型企业将采用经济、实用的自动化产品对生产过程进行控制,以提高企业的经济效益和竞争实力。

在自动化生产线上,有些生产机械的工作台需要按一定的顺序实现自动往返运动,并且有的还要求在某些位置有一定的时间停留,以满足生产工艺要求。

用PLC程序实现运料工作台自动往返顺序控制,不仅具有程序设计简易、方便、可靠性高等特点,而且程序设计方法多样,便于不同层次设计人员的理解和掌握。

关键词:PLC,自动化,顺序控制,工作台目录摘要 (I)1设计任务 (1)1.1总体要求 (1)1.2 操作要求 (1)2硬件选取与电气线路图设计 (3)2.1 硬件选取与地址的分配 (3)2.2 电气主线路的设计 (3)2.3 控制线路的设计 (4)3 PLC软件的设计 (5)4组态的设计 (8)4.1 主画面 (8)4.2 主电路画面 (8)4.3 运行画面 (9)5 调试结果实现 (10)5.1 软件调试 (10)5.2 组态调试 (10)6 总结 (12)7 参考文献 (13)1设计任务1.1总体要求使用PLC实现工作台往返循环工作的控制。

工作台前进及后退由步进电动机通过丝杠拖动。

点动控制:能分别实现工作台前进和后退的点动控制。

自动循环控制:单循环运行即工作台前进及后退一次循环后停止在原位,碰到换向行程开光时不掩饰);6次循环计数控制(即工作台前进及后退1次1个循环,每碰到换向行程开关时停止3秒后再运行,循环6次后停止在原位,原位在SQ2处。

计数器说明书2

WSD-ZH-09A计数器使用说明手册杭州威士德喷码技术有限公司服务电话:400-685-2815杭州威士德喷码技术有限公司是专门经销和生产喷码设备和耗材的一家优秀企业,从事喷码行业多年,有着非常丰富的经验。

为了适应广大用户的生产需求,特为水泥行业开发WSD-ZH-09 型计数器,该计数器使用简单,计数准确,使用方便,可以用一台主机最多连接12个计数器窗口,可在不同的地方随时观察计数数值,子窗口链接距离1000米。

可减少人工计数人员的工作量,降低误差,以一个年产100万吨的水泥厂为例,0.5%的误差是(1000000吨*20包/吨*0.5%)=100000包,这样的误差对于水泥企业来说无疑是巨大的,还容易造成企业利益流失及客户信任度下降。

设备面板显示:上面7位数码管为计数总和,总计数为9999999,可自动循环计数。

下面一行为单次车装量,最大值为59999。

使用方法:开机显示:月份日期星期以及时间1.时间的设定:当时间不准确时请按累加数/时间键,机器将显示年二位。

月二位,日二位,星期一位,空一位,小时二位,分钟二位。

如:2009年2月27号星期五9:55分,将显示成:按正确的数字键将修改闪烁那位的数字并前进一位,如有错误可按取消键退格。

最后按确认修改保存,回到初时时间界面。

如不保存只能关电源。

2.计包学习:本产品可以适应任何长度、任何流水线速度的包装产品的计数,主要是通过计包学习来完成的,通过对水泥厂的流水线进行速度和包长的综合检测,当设备安装完成(即接近开关和红外感应检测都正常)后,先必须进行计包长度学习。

按清零/学习键,屏幕将出现表示第一次学习(按取消可退出),开动流水线,让包过红外对管,此时屏幕下行会出现一数字,如:07 08。

07表示接近开关的计数值,08表示光电开关的计数基值。

此数字表示一包在红外对管接收到信号时接近开关翻转次数,建议此数据要大于5小于16,按确认完成,这时候会出现表示第二学习,共学习四次,每次按确认完成。

环形计数器

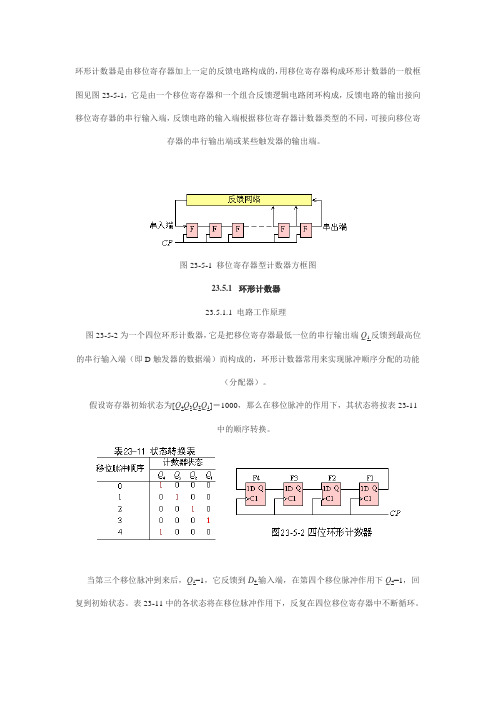

环形计数器是由移位寄存器加上一定的反馈电路构成的,用移位寄存器构成环形计数器的一般框图见图23-5-1,它是由一个移位寄存器和一个组合反馈逻辑电路闭环构成,反馈电路的输出接向移位寄存器的串行输入端,反馈电路的输入端根据移位寄存器计数器类型的不同,可接向移位寄存器的串行输出端或某些触发器的输出端。

图23-5-1 移位寄存器型计数器方框图23.5.1 环形计数器23.5.1.1 电路工作原理图23-5-2为一个四位环形计数器,它是把移位寄存器最低一位的串行输出端Q1反馈到最高位的串行输入端(即D触发器的数据端)而构成的,环形计数器常用来实现脉冲顺序分配的功能(分配器)。

假设寄存器初始状态为[Q4Q3Q2Q1]=1000,那么在移位脉冲的作用下,其状态将按表23-11中的顺序转换。

当第三个移位脉冲到来后,Q1=1,它反馈到D4输入端,在第四个移位脉冲作用下Q4=1,回复到初始状态。

表23-11中的各状态将在移位脉冲作用下,反复在四位移位寄存器中不断循环。

由上述讲讨论可知,该环形计数的计数长度为N=n。

和二进制计数器相比,它有2n-n个状态没有利用,它利用的有效状态是少的。

23.5.1.2 状态转换图和工作时序表23-11中是以1000为初始状态的,它所对应的状态转换图见图23-5-3。

如果移位寄存器中的初始状态不同,就会有不同的状态转换图。

图23-5-4给出了四位环形计数器可能有的其它几种状态转换图。

图23-5-3 状态转换图(a) (b) (c) (d)图23-5-4 四位环行计数器其它的状态转换图图23-5-4(a)、(b)、(c)三个状态转换图中各状态是闭合的,相应的时序为循环时序。

当计数器处于图23-5-4(d)所示的状态0000或1111时,计数器的状态将不发生变化。

这两个状态称为悬态或死态。

四位环形计数器可能有这么多不同的循环时序,是我们不希望的,只能从这些循环时序中选出一个来工作,这就是工作时序,或称为正常时序,或有效时序。

循环计时器的解法原理

循环计时器的解法原理循环计时器是一种常见的计时器类型,它能够实现定时循环启动和停止的功能。

循环计时器的原理是通过设置计时器的初始值、周期时间以及循环次数,实现定时循环计数的功能,并在计数完成后执行特定的操作。

下面将详细介绍循环计时器的解法原理。

1. 计时器基本原理计时器是一种能够根据外部输入信号或内部时钟信号对时间进行计数的装置。

在计时器中,一般会有一个计数器寄存器和一个时钟源。

计时器会根据时钟源提供的脉冲信号进行计数,当计数器的值达到设定的目标值时,就会触发计时器的输出信号。

2. 循环计时器的基本特点循环计时器是在计时器的基础上进行改进,它可以实现定时循环启动和停止的功能。

循环计时器的基本特点包括以下几点:- 可设置循环次数:循环计时器可以设置循环的次数,一般用于指定一个需要重复执行的任务。

- 可设置周期时间:循环计时器可以设置每次循环的周期时间,即每次计数完成所需的时间。

- 可设置初始值:循环计时器可以设置计时器的初始值,即从哪个数值开始计数。

- 具备计数功能:循环计时器具备计数的功能,即根据设置的周期时间和初始值,进行计数。

- 循环启动和停止功能:循环计时器可以通过外部输入信号或内部设置控制器的命令,实现循环的启动和停止。

3. 循环计时器的解法原理循环计时器的解法原理即是根据上述的基本特点,结合控制器和计时器的协同工作,实现定时循环启动和停止的功能。

其具体步骤如下:- 步骤一:设置循环计时器的初始值、周期时间和循环次数。

初始值可以是0或者任意一个合适的值,周期时间可以根据具体需求设置,循环次数表示需要循环的次数。

- 步骤二:启动循环计时器。

通过控制器发送启动命令,控制器会将计时器的初始值写入计数器寄存器中,并开始计数。

- 步骤三:计数。

计时器开始计数,每次计数完成后,会将计数器的值与设定的周期时间进行比较。

如果计数器的值小于周期时间,计时器继续计数;如果计数器的值等于周期时间,计数器将清零,并触发输出信号。

电子电路中的计数问题解析

电子电路中的计数问题解析计数问题在电子电路中是一个非常重要的概念。

无论是数字电路还是模拟电路都需要计数器来实现各种计数功能。

本文将对电子电路中的计数问题展开详细解析,包括计数器的基本原理、计数器的类型以及计数器的应用。

一、计数器的基本原理计数器是一种常见的数字电路元件,用于记录和表示电路的计数状态。

它由触发器或者锁存器以及各种逻辑门构成。

计数器的基本原理是通过时钟信号的触发,使得计数器按照一定规律改变其输出状态,从而实现计数功能。

二、计数器的类型基于实现方式的不同,计数器可以分为同步计数器和异步计数器。

同步计数器是指计数器各个触发器的输出同时改变的计数器,它具有运算速度快、稳定可靠等特点。

异步计数器是指在计数过程中,各个触发器的输出存在时间差,具有灵活性强的特点。

根据计数器的位数,计数器又可以分为4位计数器、8位计数器等等。

不同位数的计数器适用于不同的场景,可以根据具体需求选择合适的计数器类型。

三、计数器的应用1. 时钟频率分频:计数器可以通过设置初始值和重载值实现时钟频率的分频。

通过改变计数器的位数,可以实现不同的分频比。

2. 自动计数:计数器可以用于自动记录、统计和计算数据,提高工作效率。

例如,物流行业中的包裹计数器能够自动记录出入库的货物数量。

3. 数字显示:计数器可以用于驱动数码管显示数字。

通过改变计数器的输出状态,可以实现数字的自动循环显示。

4. 时序控制:计数器可以用于控制电子系统的时序。

通过改变计数器的输出状态,可以按照预设的时序顺序触发各种操作。

5. 频率测量:计数器可以用于测量信号的频率。

通过记录计数器在一定时间内的计数值,可以根据公式计算出信号的频率。

四、总结电子电路中的计数问题是一项重要的研究内容,计数器是实现计数功能的基本元件。

本文对计数器的基本原理、类型以及应用进行了详细解析。

希望通过本文的介绍,读者能够更好地理解电子电路中的计数问题,并且能够灵活应用计数器解决实际问题。

设计计数器的原理

设计计数器的原理

计数器是一种用于实现计数功能的电子电路或者设备。

它能够记录和显示特定事件或者操作的次数。

计数器的原理是基于触发器的工作原理。

触发器是一种存储器件,能够在时钟信号的控制下切换输出状态。

计数器通常是由多个触发器连接在一起组成的,每个触发器代表一个比特(位)的计数。

计数器的计数方式一般分为两种:二进制计数和十进制计数。

在二进制计数中,每个触发器代表一位二进制数,计数器的输出依次为000、001、010、011、100……。

在十进制计数中,

每个触发器代表一位十进制数,计数器的输出依次为0、1、2、3、4……。

计数器通常采用时钟信号来控制计数的速度。

每当时钟信号上升沿到来时,计数器就会增加一个计数。

当计数器达到其最大计数值时,会产生一个溢出信号,同时计数器会从零重新开始计数。

这种计数方式称为自动循环计数。

计数器还可以实现其他功能,如计数器的清零、计数器的预置值、计数器的方向控制等。

通过增加逻辑门或者引入控制信号,可以灵活地扩展计数器的功能。

总的来说,计数器是一种基于触发器工作原理的电子电路或者设备,用于记录和显示特定事件或者操作的次数。

通过时钟信号的控制,计数器可以实现自动循环计数和其他附加功能。

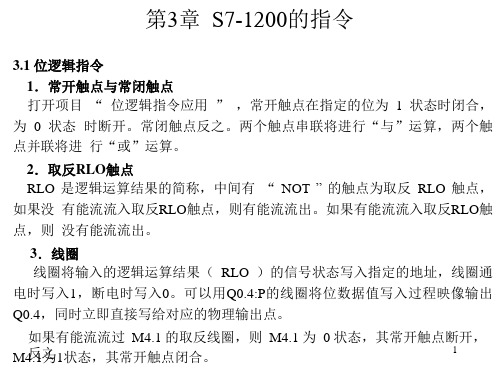

S7-1200-PLC编程及应用第三版--ppt课件-第3章

8.在信号边沿置位操作数的指令 中间有 P 的线圈是 “ 在信号上升沿置位操作数 ” 指令,仅在流进该线圈 的能流 的上升沿,该指令的输出位M6.1为1状态。其他情况下M6.1均为0状态, M6.2 为保存P线圈输入端的RLO的边沿存储位。 中间有 N 的线圈是 “ 在信号下降沿置位操作数 ” 指令,仅在流进该线圈 的能流 的下降沿,该指令的输出位M6.3为1状态。其他情况下M6.3均为0状态, M6.4 为边沿存储位。 上述两条线圈格式的指令对能流是畅通无阻的,这两条指令可以放置在程序 段的中间或最右边。在运行时改变I0.7的状态,可以使M6.6置位和复位。

2Leabharlann 5.置位位域指令与复位位域指令 “ 置位位域 ” 指令 SET_BF 将指定的地址开始的连续的若干个位地址置位, “ 复 位位域”指令RESET_BF将指定的地址开始的连续的若干个位地址复位。

7.扫描操作数信号边沿的指令 中间有P的触点的名称为 “ 扫描操作数的信号上升沿”,在I0.6 的上升沿, 该触 点接通一个扫描周期。M4.3为边沿存储位,用来存储上一次扫描循环时 I0.6的 状态。通过比较I0.6前后两次循环的状态,来检测信号的边沿。边沿存 储位的 地址只能在程序中使用一次。不能用代码块的临时局部数据或I/O变量 来作边 沿存储位。 中间有 N 的触点的名称为 “ 扫描操作数的信号下降沿 ” ,在 M4.4 的下降 RES沿E,T_BF的线圈“通电”一个扫描周期。该触点下面的M4.5为边沿存储位。

12

3.关断延时定时器指令 关断延时定时器( TOF )用于将 Q 输出的复位操作延时 PT 指定的一段时间 IN输入电路接通时,输出Q为1状态,当前时间被清零。在IN的下降沿开始定 时,ET从0逐渐增大。ET等于预设值时,输出Q变为0状态,当前时间保持不 变,直到IN输入电路接通(见波形A)。关断延时定时器可以用于设备停机 后 的延时。 如果 ET 未达到 PT 预设的值, IN 输入信号就变为 1 状态, ET 被清 0 , 输出 Q 保 持1状态不变(见波形B)。复位线圈RT通电时,如果IN输入信号 为0状态, 则定时器被复位,当前时间被清零,输出Q变为0状态(见波形C)。 如果复 位时IN输入信号为1状态,则复位信号不起作用(见波形D)。

DSP技术及应用--陈金鹰(第三章)

用来修 改存储 器映象 寄存器

7.堆栈寻址

功能 特点

PSHD *AR2 POPD *AR3

用来在中断和 子程序调用时 自动保存程序 计数器(PC) 中的数值,也 能用来保护现 场或传送参数

从高地址向低地址方向生长, SP用来管理堆栈,SP始终指向 堆栈中所存放的最后一个数 据,即SP指针始终指向栈顶。 在 压 入 操 作 时 , 先 减 小 SP 的 值,再将数据压入堆栈;在弹 出操作时,先从堆栈弹出数 据,再增加SP的值。 23

第二节

程序地址 生成器 (PAGEN) 构成 核心

程序地址的生成

程序计数器(PC) 重复计数器(RC) 块重复计数器(BRC) 块重复起始地址寄存器(RSA) 块重复结束地址寄存器(REA) 地址内容为: 即将取指的某条指令; 某个16位立即操作数; 系数表。 24 在程序存储器中的地址

16位程序计数器(PC) 内中保存某个内部或外 部程序存储器的地址。

ARx是数据存储器地址 访问后,ARx中的地址减1 访问后,ARx中的地址加1 访问后,AR0以循环寻址的 方式加到ARx中 21

6.存储器映象寄存器寻址

功能 方法 高9位数据 存储器地址 被置0,利 用指令中的 低7位地址 访问MMR。 LDM PRD,A

22

举例

特点 0页寻址。 不影响当前 DP或SP 值 。用于 直接寻址和 间接寻址

操作码语 法 *ARx *ARx*ARx+ *ARx+0%

辅助寄存器 AR2 AR3 AR4 AR5

双数据存储器操作数寻址的类型

Xmod或 Ymod 00 01 10 11 功 能 说 明

addr=ARx addr=ARx ARx=ARx-1 addr=ARx ARx=ARx+1 addr=ARx ARx=circ( ARx+AR0)

Techcon TS 点胶机使用手册

Techcon泰康TS350点胶机使用手册安全注意事项:1.操作此设备时切勿超过最大额定功率/设置2.务必穿上适当的个人防护衣3.仅可使用以下电源适配器型号:PSA15R-240P(ZJ) 或PW118RA2403B01、PW118RA2403H01、PW118RA2403M01、PW118RA2403G014.务必小心防止入口处的腐蚀性或易燃液体回流入设备。

如果使用腐蚀性或易燃液体,则在点胶机上必须要安装进气管过滤器 (881-000-000),防止液体倒吸入设备5.点胶液可能是有毒和/或危险物质。

请仔细阅读用“材料安全数据表”和安全注意事项6.如果活塞没有配合针筒使用,则在接收器磁头上必须要安装进气管过滤器(881-000-000),防止液体倒吸入设备。

切勿将该针筒装得太满并且要以其侧面放置7.使用易燃液料点胶时,切勿吸烟或使用明火8.该设备仅可在室内使用Techocn代理亚普德科技0755 299 555 2431 35 10 26 05 68Q 25 57 998 620手动/排胶点胶循环设置:1. 按“电源”按钮 (1) 打开设备。

2. 按“模式”按钮 (2) 直到显示器上出现“PURGE 排胶”。

3. 通过旋转压力调节旋钮(5)直至所需要的点胶压力显示出来4. 填充针筒或使用预封装的胶合剂后,将注射器附在接收器磁头组件上。

确保注射器固定于恰当的位置。

5. 将接收器磁头组件的插入端连接到其中一个气式点胶出口 (6)。

6. 如果需要真空抽吸,逆时针旋转真空压力旋钮(7),所需要的真空压力可以显示出来。

7. 压住“脚踏开关”以激活点胶循环。

(此刻手动/排胶模式即被激活)自动点胶循环设置程序选择1.按下设置按钮(3)直到“P:”开始闪烁2.旋转程序选择按钮(8)选择所需要的程序时间设置1.按下模式按钮 (2)选择需要的时间模式2.按下并释放设置按钮 (3)直到时间里 (:) 开始闪烁.3.旋转时间旋钮 (8)选择需要的点胶时间4.压下踩脚踏开关启动点胶周期培训模式设置在培训模式下,只要脚踏开关处于压下状态,设备就会累计时间。

自动循环计数器(精)

目录一、设计目的…………………………………………………………… ..二、内容及要求………………………………………………………… .三、设计思想…………………………………………………………… .四、单元电路的设计、参数计算、器件选择及介绍………………… .(一、电源部分………………………………………………………………… .(二、单脉冲产生部分………………………………………………………… .(三、译码驱动显示部分…………………………………………………………(四、控制部分及循环加减计数部分……………………………………………五、总体电路设计图、工作原理及元器件清单………………………六、硬件电路安装、调试测试结果,出现的问题、原因及解决方法七、总结设计电路的特点和方案的优缺点……………………………八、收获、体会…………………………………………………………九、参考文献…………………………………………………………… ..设计题目:自动循环计数器一、设计目的:1. 熟练掌握计数器的应用。

2. 加深对加减循环计数和显示电路的理解。

二、内容及要求:1. 用集成计数器实行 3~9自动循环计数。

2. 电路能实现 3~9加法和 3~9减法循环计数。

3. 输出用数码显示。

根据功能要求构建总体设计思想,比较和选定设计的系统方案,确定整个电路的组成以及各单元电路完成的功能,画出系统框图。

三、设计思想 :根据功能要求构建总体设计思想,按照题目要求,系统可以划分为以下各单元部分;基本思想如下:1、电源部分,由它向整个系统提供 +5V电源。

2、单脉冲产生部分:功能是由它产生单个脉冲,为循环计数部分提供计数脉冲。

3、译码驱动显示部分:计数输出结果送至译码驱动显示部分。

4、控制部分:实现加或减循环计数功能由控制部分完成。

5、计数部分:完成 BCD 码 3~9的可逆加或减循环计数。

系统方框图如图 1所示。

图 1 3~9加 /减可逆自动循环计数器系统方框图四、单元电路的设计、参数计算、器件选择及介绍:(一、电源部分直流稳压电源主要由变压器、整流电路、滤波电路、稳压电路组成。

数电课程设计题目

1001、1002班数电课程设计题目:要求:1、学生分组,每组限6人,特殊情况需说明2、查阅资料,器件选型,提供元器件清单,本周五(11月9日)前需完成3、后续待课程设计时候再做具体要求!一、汽车尾灯控制电路1、设计任务设计一个汽车尾灯控制电路,要求汽车尾部左右两侧各有3个指示灯(用发光二极管模拟),当在汽车正常运行时指示灯全灭;在右转弯时,右侧3个指示灯按右循环顺序点亮;在左转弯时,左侧3个指示灯按左循环顺序点亮;在临时刹车时,所有指示灯同时点亮。

2、参考设计方案分析以上设计任务,由于汽车左转弯或右转弯时,3个指示灯循环点亮,所以用三进制计数器控制译码器电路顺序输出低电平,从而控制尾灯按要求点亮。

由此得出在每种运行状态下,各指示灯与给定条件间的关系,即逻辑功能表1-1所示。

汽车尾灯控制电路设计总体框图如图1-1所示。

汽车尾灯和汽车运行状态表1-1开关控制汽车运行状态右转尾灯左转尾灯S1 S2D1D2D3D4D5D60 0 正常运行灯灭灯灭0 1 右转弯按D1D2D3顺序循环点亮灯灭1 0 左转弯灯灭按D4D5D6顺序循环点亮1 1 临时刹车所有尾灯同时点亮图1-1汽车尾灯控制电路设计总体框图二、自动循环计数器1、设计任务①用集成计数器实行3~9自动循环计数。

②电路能实现3~9加法和3~9减法循环计数。

③输出用数码显示。

2、参考设计方案分析设计任务,该系统由加减控制模块、可逆计数器、译码显示模块构成。

完成由加法计数自动转向减法计数。

可逆计数器实现加法、减法计数功能。

加减控制模块可由门电路组成的基本RS触发器和其它控制门电路构成。

译码显示模块完成该结果的数字显示。

自动循环计数器设计框图如图2-1所示。

图2-1 自动循环计数器设计框图三、篮球竞赛30秒计时器1、设计任务①30秒计时器具有显示30秒的计时功能。

②系统设置外部操作开关,控制计时器的直接清零、启动和暂停/连续功能。

③计时器为30秒递减计时时,其计时间隔为1秒。

定时器 计数器的基本结构及工作原理

定时器计数器的基本结构及工作原理80C51单片机内部设有两个16位的可编程定时器/计数器。

可编程的意思是指其功能(如工作方式、定时时间、量程、启动方式等)均可由指令来确定和改变。

在定时器/计数器中除了有两个16位的计数器之外,还有两个特殊功能寄存器(控制寄存器和方式寄存器)。

定时器/计数器的结构:从上面定时器/计数器的结构图中我们可以看出,16位的定时/计数器分别由两个8位专用寄存器组成,即:T0由TH0和TL0构成;T1由TH1和TL1构成。

其访问地址依次为8AH-8DH。

每个寄存器均可单独访问。

这些寄存器是用于存放定时或计数初值的。

此外,其内部还有一个8位的定时器方式寄存器TMOD和一个8位的定时控制寄存器TCON。

这些寄存器之间是通过内部总线和控制逻辑电路连接起来的。

TMOD主要是用于选定定时器的工作方式;TCON主要是用于控制定时器的启动停止,此外TCON还可以保存T0、T1的溢出和中断标志。

当定时器工作在计数方式时,外部事件通过引脚T0(P3.4)和T1(P3.5)输入。

定时计数器的原理:16位的定时器/计数器实质上就是一个加1计数器,其控制电路受软件控制、切换。

当定时器/计数器为定时工作方式时,计数器的加1信号由振荡器的12分频信号产生,即每过一个机器周期,计数器加1,直至计满溢出为止。

显然,定时器的定时时间与系统的振荡频率有关。

因一个机器周期等于12个振荡周期,所以计数频率fcount=1/12osc。

如果晶振为12MHz,则计数周期为:T=1/(12×106)Hz×1/12=1μs这是最短的定时周期。

若要延长定时时间,则需要改变定时器的初值,并要适当选择定时器的长度(如8位、13位、16位等)。

当定时器/计数器为计数工作方式时,通过引脚T0和T1对外部信号计数,外部脉冲的下降沿将触发计数。

计数器在每个机器周期的S5P2期间采样引脚输入电平。

若一个机器周期采样值为1,下一个机器周期采样值为0,则计数器加1。

jdk8的safepoint参数

jdk8的safepoint参数JDK8的Safepoint参数JDK(Java Development Kit)是Java语言的软件开发工具包。

JDK8是Java SE(Standard Edition)的第8个版本,于2014年3月发布。

在JDK8中,Safepoint参数被引入,用于控制Java虚拟机(JVM)的Safepoint机制。

Safepoint是JVM中的一种同步机制,用于确保在某个特定的时间点,所有执行中的线程都停在一个安全点上。

在Safepoint上,JVM可以进行一些特殊的操作,比如垃圾回收、线程栈的安全检查等。

在JDK8中,可以通过一些参数来调整Safepoint的行为。

下面将介绍几个常用的Safepoint参数。

1. -XX:+PrintSafepointStatistics这个参数用于打印Safepoint的统计信息。

通过这些统计信息,可以了解Safepoint的触发频率、停顿时间等相关信息。

对于性能调优和故障排查非常有帮助。

2. -XX:PrintSafepointStatisticsCount这个参数用于设置打印Safepoint统计信息的触发次数。

默认值为20,表示打印前20次的统计信息。

可以通过修改这个参数的值来控制打印的次数。

3. -XX:GuaranteedSafepointInterval这个参数用于设置两次Safepoint之间的最小时间间隔。

默认值为500ms。

可以通过增大这个值来减少Safepoint的触发频率,从而减少应用程序的停顿时间。

但是如果设置得太大,可能会导致垃圾回收等操作的延迟。

4. -XX:+UseCountedLoopSafepoints这个参数用于启用循环计数器安全点机制。

在JDK8之前,循环计数器是一个全局的计数器,当计数器的值达到某个阈值时,会触发Safepoint。

而在JDK8中,循环计数器被改为线程局部的计数器,每个线程都有自己的计数器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《自动循环计数器》

——课程设计报告

学院:信息科学与技术学院

专业:电子信息工程

班级:2010级(2)班

姓名:梁亚龙沈纪军

学号:2010508123 2010508136

20 12年7 月5 日

目录

1、设计目的………………………………………………………………………..

2、实验器材………………………………………………………………………..

3、设计思路………………………………………………………………………..

4、功能模块………………………………………………………………………..

5、设计电路图…………………………………………………………………….

6、工作原理…………………………………………………………………………

7、仿真截图…………………………………………………………………………

8、报告总结…………………………………………………………………………

9、参考文献…………………………………………………………………….

一:设计目的

1、熟练掌握计数器、编码器、译码器的原理和应用。

2、加深对加减循环计数和显示电路的理解。

二:实验器材

74LS191计数器、74LS48 TTL BCD—7 段译码器、74LS298D数据选择器,74LS48D 译码器、7个电阻,一个函数信号发生器

三、设计思路

1、译码驱动显示部分:计数输出结果送至译码输出显示部分。

2、控制部分:实现加或减循环计数功能由控制部分完成。

3、计数部分:完成BCD码3~9的可逆加或减循环计数。

系统方框图如下:

四、功能模块

1. 74LS191计数器、

74LS191 为可预置的四位二进制加/减法计数器,其管脚图如下图所示:

RCO 进位/借位输出端

MAX /MIN 进位/借位输出端

CTEN 计数控制端

QA-QD 计数输出端

U/D 计数控制端

CLK 时钟输入端

LOAD 异步并行置入端(低电平有效)。

其功能表如下所示:

2.74LS48 TTL BCD—7 段译码器、

7段显示译码器74LS48是输出高电平有效的译码器,

74LS48/SN74LS48 引脚功能图

74LS48除了有实现7段显示译码器基本功能的输入(DCBA )和输出(Ya ~Yg )端外,74LS48还引入了灯测试输入端(LT )和动态灭零输入端(RBI ),以及既有输入功能又有输出功能的消隐输入/动态灭零输出(BI/RBO )端。

74LS48所具有的逻辑功能: (1)7段译码功能(LT=1,RBI=1)

在灯测试输入端(LT )和动态灭零输入端(RBI )都接无效电平时,输入DCBA 经74LS48译码,输出高电平有效的7段字符显示器的驱动信号,显示相应字符。

除DCBA = 0000外,RBI 也可以接低电平 (2)消隐功能(BI=0) (3)灯测试功能(LT = 0) (4)动态灭零功能(LT=1,RBI=1)

U6

74LS138D

Y015Y114Y213Y312Y411Y510Y69Y77

A

1

B 2

C 3G1

6~G2A 4~G2B 5GND 8VCC

16

引脚图

74LS138 为3 线-8 线译码器,共有 54/74S138和 54/74LS138

两种线路结构型式。

其工作原理如下:

当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A 、B 、C )的二进制编码在一个对应的输出端以低电平译出。

利用 G1、/(G2A)和/(G2B)可级联扩展成 24 线译码器;若外接一个反 相器还可级联扩展成 32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器。

4.74LS298D

U1

74LS298D

A13

B21A22B14C19C25D17WS 10D26CLK 11QA 15QB 14QC 13QD

12

GND

8

VCC 16

74LS298为带储存的四组2选1 数据选择器,数据选择端S 可选择两个4位数据(A1-D1),(A2-D2)中的一个,在时钟CLK 脉冲下降沿作用下被选取的数据传

送到输出端QA-QD. 引出端符号:

WS 选择输入端

CLK 时钟输入端(下降沿有效) A1-D1,A2-D2 数据输入端 QA-QD 输出端

5. XFG1(函数信号发生器)

其工作原理如下图所示,其波动的频率都可自己调节,为了方便,故选择了频率为60Hz 。

五、电路设计图

六、工作原理

由函数信号发生器产生的脉冲送至74LS191的CLK端,做加法时,191的D/U’端需接地,通过手动开关实现。

加法减法计数时按题目要求,9加1变成10,3减1应该变成9,在此利用74LS298双4位2选一数据选择器将预置数3(0011)或9(1001)选择一个数据送给191的预置数据端DCBA,实现的方法是,将加到10或减到2由138译码得到的负脉冲送到298的CLK端,CLK将与之的无论

加或减的预置数0011或1001数据送至191的预置端,298的WS端为数据选择端,即WS=1选0011加法预置数,WS=0选1001减法预置数。

七、仿真截图

加法截图

2.减法截图

八.报告总结

通过这次的课程设计,收益很大,初步掌握电子电路的计算,掌握了数字电路设计的一般方法,具备初步的电路设计能力。

熟悉了常用元器件的类型和特性。

初步学会电子电路的安装、布线、调试的基本技能,同时也提高独立解决问题和团队合作的能力,也认识到了团队合作重要性。

九.参考文献

1.《模拟电子技术基础》(第四版)童诗白华成英高等教育出版社

2.《数字电子技术基础》(第五版)阎石高等教育出版社

3.姚福安《电子电路设计》山东科学技术出版社2001年10月。