印制电路板设计(工艺性要求)检查表单

PCB板设计规范检查表

3

工艺边一般以整板(即含拼板)的长边为工艺边,当短边与长边的比≤80%时, 必须以长边为工艺边。

4

工艺边宽度:双面或多层板5mm(MARK点不在工艺边上),双面或多层板10mm± 2mm(MARK点在工艺边上);单面板10mm±2mm;

检查问题点确认描述

第 2 页,共 5 页

对策

责任人

完成 时间

效果 验证

NO

检查项 目

检查内容及参考标准

自检 他检 检查问题点确认描述

4 导锡点的位置是否合理,导锡点与PCB板过炉方向相反,大小合适。 5 过回流焊的IC和排插的焊盘不允许有加拖锡点。

6

过回流焊的与大面积铺铜连接的小电流SMT焊盘应为网状(梅花形)连接(例如: 连接铺铜地线的焊盘),线宽0.3mm,连线数3条。

17 同一个元件的两个焊盘大小必须一致。

18 引脚间距<2mm插件焊盘非焊接面用绿油覆盖,特殊要求除外

19 焊盘不能被丝印覆盖。

20 烧录IC最好设计元件升级的焊盘或可植针的焊点。

1 PCB的拼板尺寸控制在宽100~200mm ×长200~310mm的面积范围内。

2

两面都有SMT元件的而且面积较小的PCB(比如KB板),4拼板,两正两反或正 反正反,一定要对称,正看和镜像都一样。

1 MARK点的直径为1mm。

2 MARK点的外环直径为3mm。

3 MARK点的边缘到PCB板边距离大于5mm。

4

MARK点与周围的元件距离大于4mm,四周5mm范围内不能有元器件、焊盘或测 试点。

5 一块PCB要有4个以上的MARK点,最好是对角,但是不能对称。

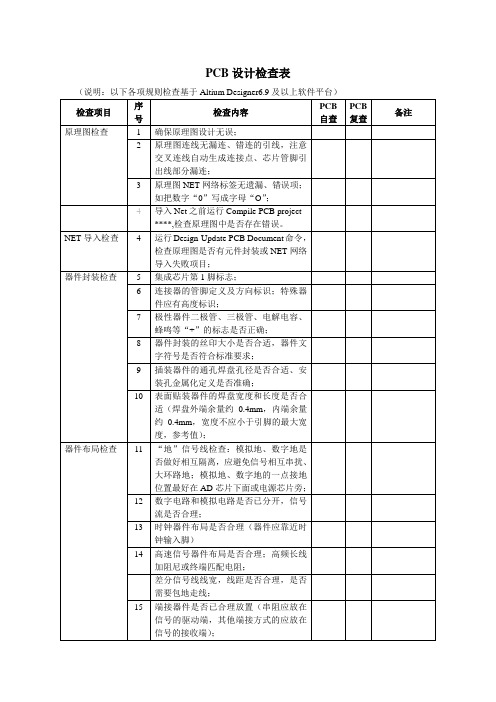

PCB设计检查表

PCB设计检查表

○13W规则:

为了减少线间串扰,应保证线间距足够大,当线中心间距不少于3倍线宽时,则可保持70%的电场不互相干扰,称为3W规则。

如要达到98%的电场不互相干扰,可使用10W的间距。

○220H规则:

由于电源层与地层之间的电场是变化的,在板的边缘会向外辐射电磁干扰。

称为边沿效应。

解决的办法是将电源层内缩,使得电场只在接地层的范围内传导。

以一个H(电源和地之间的介质厚度)为单位,若内缩20H则可以将70%的电场限制在接地层边沿内;内缩100H则可以将98%的电场限制在内。

○3信号电流和线宽的关系:

铜箔厚度=0.65mil(0.01651mm)

电流密度:5A/mm^2

单位线宽电流:0.01651mm*5A/mm^2=0.08255A/mm=2.09677A/inch=2.1mA/mil;

○4印制板加工技术指标:

最小线宽:0.12mm(4.7mil),常规推荐:0.20mm(8mil);

最小线距:0.12mm(4.7mil),常规推荐:0.20mm(8mil);

最小孔径:0.30mm(11mil),对应焊盘:0.64mm(25mil);

pcb板厚:1.0mm,1.2mm,1.6mm,2.0mm,2.5mm,常规1.6mm;。

印制板(PCB)自查与审核列表(EMC版本)

时钟线、高速信号线、控制线、复位线是否加跟随地线或包地

同层或相邻布线层的数字信号布线是否没有穿越模拟部分,反之亦然

分 层

主电源平面(板上功率最大的那种电源)是否与地平面相邻★

元件面下面(第二层或倒数第二层)是否有相对完整的参考平面★

时钟发生器是否靠近用到该时钟的器件★

逻辑电路(时钟驱动、缓存等)与晶体相连,是否扩大敷铜地平面包围住这些时钟附属电路★

时钟产生电路附近是否有与底板、机壳搭接的焊盘

电 源

电源线,尤其地线是否粗、短★

单层板的电源线、地线是否就近平行布线★

电源的输入输出线是否隔离,是否避免交叉★

隔离变压器、光电耦合器下面的电源层、地层是否挖空

PCB上的敷铜、局部接地面等接地过孔之间的物理距离是否小于最高频率波长的1/20

连 接 器

连接器是否避免跨越平面层的开槽★

金属外壳连接器,其周围15mm以内的地方,是否没有布置敏感器件★

是否选用具有更多地针的连接器,是否每根信号针都有相应的地针

审核意见及建议

EMC设计师(签名):年月日

印制板自查与审核列表

表单编号:NO:

产品名称

产品代号

设计师

印制板名称

版本号

图号

填表日期

本表使用说明:

1.设计师开始设计印制板之前,先应当熟悉公司《印制电路板电磁兼容设计规范》相关内容,当印制板设计完成后,

设计师首先应按照本检查表核对设计结果,进行设计师自查,最后提交审核;

2.“设计自查”及“EMC审核”分别由设计师本人和电磁兼容设计师在需要检查的项目填写“Y”、“N”或空白,

EDA-PCB设计工艺性检查表

是 是 是 否 否 否 否 否 否 否 是 是 否 否 是 是 是 是 否

无此类器件 布线审核时再确认 布线审核时再确认 布线审核时再确认 布线审核时再确认 无此类器件 无此类器件 无此类器件 无此类器件 OK 无此类器件 无此类器件 OK OK OK 按新的规范设计 按新的规范设计 布线审核时再确认 布线审核时再确认 / / / / / / / / / / /

是 是 否 是 是 是 否 否 否 否 否 否 否 否 否 是 否 是 是 是 否 否 是 是

OK OK OK OK OK 该板为系统板 该板为系统板 该板为系统板 该板为系统板 该板为系统板 该板为系统板 该板为系统板 该板为系统板 该板为系统板 该板为系统板 OK OK 无此类器件 无此类器件 无此类器件 无此类器件 无此类器件 OK 布线审核时再确认

/ / / / / / / / / / / / / / / / / / / / / / / / /

107 108 109 110 111 112

线宽线距

基材圈大小

□确认无“密度低,但线宽线距要求较高且不合理”现 象 ★确认无“基材圈太小,易造成内层短路”现象(一般 情况下线离孔应大于或等于28mil) ★确认无“基材圈太大,造成内层某区域隔绝”现象

否 是 是 是 是 否 否 是 是 否 否 否 否 否 是 否 是 否 否 否 否 否 否

★确认过孔焊盘满足PCB制造工艺要求(一般单边≥ 6mil) ★确认采用回流焊工艺的单板,焊盘上没有导通孔 ★确认采用波峰焊面工艺的单板,导通孔没有设计在点 胶位置上 ★确认无阻焊导通孔离SMT元件焊盘大于0.5mm ★确认在波峰焊面排成一列的无阻焊导通孔焊盘的间隔 大于0.5mm(20mil) ★确认背板的A面(TOP面)已有插座位号和丝印外形 ★确认背板的电源插座插入方向已标识出位号、外形、 引脚信号 ★确认焊接元件引脚伸出背板足够的长度 ★确认PCB连接器的引脚号顺序已统一(应自上而下) ★确认线缆连接器的插装方向已统一(同一背板要求统 一) ★确认衬板对压接支撑面贴片,插件元件有作避让开孔 处理 ★确认衬板的厚度为背板厚度向上取整后再加1mm所得 ★确认衬板的压接元件孔径已处理为非金属化孔且放大 0.4mm ★确认衬板的安装定位孔为非金属化孔且孔径没有放大 0.4mm ★确认衬板没有丝印及铜箔 ★确认无器件超过元件面和焊接面元件高度限制,并有 余量 ★确认金属壳体的元器件,已特别注意不与别的元器件 或印制导线相碰,且已留有足够的空间位置 ★确认压接元件周围5mm范围内没有高度超过其高度 的元件 ★确认压接元件焊接面引脚外5mm范围内没有器件 ★确认高尺寸器件(如连接器)能进行手工焊接和检查 ☆确认需要用胶加固的元器件已经留出注胶位置 ☆确认每一种单板上只使用一种推荐的铆钉 ★确认子卡安装后子卡上最高器件不超过元件高度限制 ★确认无“线宽线距太小,无法加工”现象

PCB点检表(增加工艺审查)

PCB点检表设计规范的附录A兀器件种类及名称文字符号兀器件种类及名称文字符号变压器T 接触器KM测试点(焊盘) TP 晶体振荡器、谐振器Y插头、插座J 开关S电池GB 滤波器Z电感器、磁珠L 模块电源MP电容器 C 熔断器FU电阻器R 三极管Q电位器RP 二极管、稳压二极管 D排阻RR 发光二极管DL热敏电阻RT 指示灯HL压敏电阻RV 继电器K蜂鸣器VD 集成电路、三端稳压块U光耦ISO TVS管TVS跳线器、拨码开关JUMP 数码管LVDS电流互感器CT 电压互感器PT设计规范的附录B器件间距要求PLCG QFR SOP各自之间和相互之间间隙》2.5mm( 100mil )。

PLCC QFP SOP与 Chip、SOT之间间隙 >1.5mm (60mil )回流焊:Chip、SOT各自之间和相互之间的间隙可以小至0.3mm(12mil)。

波峰焊:Chip、SOT相互之间的间隙 R8mm(32mil )和 1.2mm (47mil ),钽电容在前面时,间隙应 >2.5mm (100mil )。

见下图:BGA外形与其他元器件的间隙 >5mm(200mil )PLCC表面贴转接插座与其他元器件的间隙>3mrm( 120mil )。

表面贴片连接器与连接器之间应该确保能够检查和返修。

一般连接器引线侧应该留有比连接器高度大的空间。

元件到喷锡铜带(屏蔽罩焊接用)应该 2mm(80mil)以上。

元件到拼板分离边需大于1mm(40mil)以上。

如果B面(焊接面)上贴片元件很多、很密、很小,而插件焊点又不多,建议插件引脚离开贴片元件焊盘 5mm 以上,以便可以采用掩模夹具进行局部波峰焊。

注:其中间隙一般指不同元器件焊盘间的间隙,器件体大于焊盘时,指器件体的间隙)设计规范的附录C丝印字符大小参考值)设计规范的附录F 器件封装制作要求器件封装制作要求:。

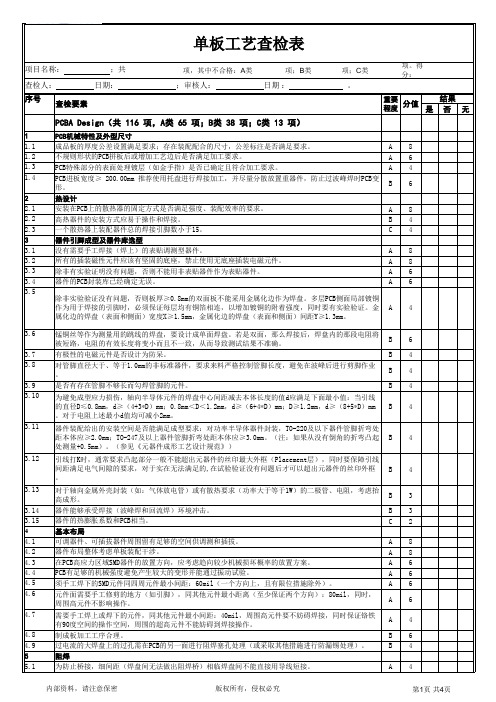

单板工艺查检表

项,其中不合格:A 类项;B 类项;C 类是否无11.1A 81.2A 61.3A 41.4B622.1A 82.2B 42.3C 433.1A 83.2A 83.3A 63.4A63.5A 43.6B 63.7B 43.8B 43.9B 43.10B43.11B 43.12B 43.13B 33.14B 33.15C 244.1A 84.2A 84.3A 64.4A 64.5A 64.6A 64.7A 44.8B 64.9B 455.1A4制成板加工工序合理。

过电流的大焊盘上的过孔需在PCB的另一面进行阻焊塞孔处理(或采取其他措施进行防漏锡处理)。

阻焊为防止桥接,细间距(焊盘间无法做出阻焊桥)相临焊盘间不能直接用导线短接。

PCB有足够的机械强度避免产生较大的变形并能通过振动试验。

须手工焊下的SMD元件同四周元件最小间距:60mil(一个方向上,且有限位措施除外)。

元件面需要手工修剪的地方(如引脚),同其他元件最小距离(至少保证两个方向):80mil,同时,周围高元件不影响操作。

需要手工焊上或焊下的元件,同其他元件最小间距:40mil,周围高元件要不妨碍焊接,同时保证铬铁有90度空间的操作空间,周围的超高元件不能妨碍到焊接操作。

基本布局可调器件、可插拔器件周围留有足够的空间供调测和插拔。

器件布局整体考虑单板装配干涉。

在PCB高应力区域SMD器件的放置方向,应考虑趋向较少机械损坏概率的放置方案。

引线打K时,通常要求凸起部分一般不能超出元器件的丝印最大外框(Placement层),同时要保障引线间距满足电气间隙的要求,对于实在无法满足的,在试验验证没有问题后才可以超出元器件的丝印外框。

对于轴向金属外壳封装(如:气体放电管)或有散热要求(功率大于等于1W)的二极管、电阻,考虑抬高成形。

器件能够承受焊接(波峰焊和回流焊)环境冲击。

器件的热膨胀系数和PCB相当。

对管脚直径大于、等于1.0mm的非标准器件,要求来料严格控制管脚长度,避免在波峰后进行剪脚作业。

PCB设计检查表

2.10

普通板有大于3mm工艺边

18

2.11

器件布局间距,IC大于2mm、BGA大于5mm;特殊情况可适当调整。但保证IC大于1mm,BGA大于3mm

19

2.12

压接件距其他器件大于5mm,焊接面压接件贯通区域无任何器件

20

2.13

有极性插装器件第一脚为方焊盘

21

2.14

坐标原点为板框左、下延伸线交点

149

PAD与PAD的SPACING:最小要8mil

150

4.4.13

BGA SOCKET(Through Hole TYPE)

151

Hole size:1.27mm pitch 用0.5mm(20mil)

152

1.00mm pitch 用0.35mm(14mil)

153

4.4.14

BGA SOCKET(Through Hole TYPE)

139

4.4.8

螺丝及COUNTERSINK

140

请参考螺丝与孔对照表,表上列出为孔的大小

141

4.4.9

VIA 孔的ANNULAR RING 每边为5mil

142

4.4.10

螺丝孔的ANNULAR RING,PAD的大小为孔的两倍

143

4.4.11

BGA SOCKET(POGO PAD TYPE)

158

4.4.

15

其他SOCKET

159

HOLE SOZE:按照图纸做

160

Annular Ring:最小要0.010”,如不能达至要求就长圆PAD

161

长圆PAD的ANNULAR RING:长的一边做15mil,短的一边做6mil

PCB设计对照检查表(制版前检查)

浪涌抑制器件对应的信号走线是否在表层短且粗?

E1、以太网、串口等接口信号是否已满足要求 时钟线、高速信号线、敏感的信号线不能出现跨越参 考平面而形成大的信号回路 电源、地是否能承载足够的电流 (估算方法:外层 铜厚1oz时1A/mm线宽,内层0.5A/mm线宽,短线电流 加倍)

PCB上的角部是否留有至少3个定位孔 测试点的位置,大小,形状是否合理,是否符合生产 要求及夹具制作要求

检查禁止布局区是否有元器件

布局是否模块化,功能化

打印1∶1布局图,检查布局和封装 数字电路和模拟电路的走线是否已分开,信号流是否 合理 高速差分信号线和类似信号线,是否等长、对称、就 近平行地走线? 时钟线以及高速信号线是否避免穿越密集通孔过孔区 域或器件引脚间走线? 布通率是否100%

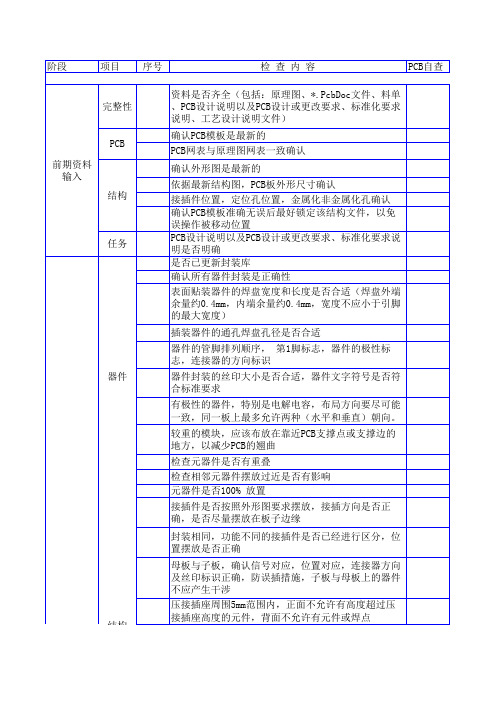

阶段

项目 序号

检查内容

PCB自查

完整性

前期资料 输入

PCB 结构

任务

器件

结构

资料是否齐全(包括:原理图、*.PcbDoc文件、料单 、PCB设计说明以及PCB设计或更改要求、标准化要求 说明、工艺设计说明文件)

确认PCB模板是最新的

PCB网表与原理图网表一致确认

确认外形图是最新的

依据最新结构图,PCB板外形尺寸确认 接插件位置,定位孔位置,金属化非金属化孔确认 确认PCB模板准确无误后最好锁定该结构文件,以免 误操作被移动位置 PCB设计说明以及PCB设计或更改要求、标准化要求说 明是否明确 是否已更新封装库 确认所有器件封装是正确性 表面贴装器件的焊盘宽度和长度是否合适(焊盘外端 余量约0.4mm,内端余量约0.4mm,宽度不应小于引脚 的最大宽度)

PCB设计规范验证表

PCB板工艺设计验证表客户/车型:东旭机型名:作成部门:作成日期:拟制:审核: 批准:深圳市东旭电子科技有限公司工程部(A/0)检验·要点参考数据①是否谋求用保护膜(resist)等防止印制导线的腐蚀?·印制导线应无外露。

(壳体地线用的印制导线除外)检验·要点参考数据①风冷条件下,热敏器件距热源是否良好差检验·要点参考数据检验·要点参考数据①插装器件管脚应与通孔公差配合是否良通孔直径大于管脚直径②元件孔直径是否符合要求a) 横插元件孔直径为检验·要点D1=D2检验·要点参考数据判定①间距a、b是否符合要求·基准:a≥3.58mm……a)b≥3.58mm……b)检验·要点参考数据①焊盘是否符合元件标准库参见元件标准库②不规则元件焊盘设计是否参见工艺设计要求图33-检验·要点参考数据判定①单面板线宽、线间距是否符≥0.3mm,≥0.3mm检验·要点参考数据①布线方向是否符合要求水平或垂直②走线拐角是否符合要求直转入水平拐角应在45º以下进入检验·要点参考数据判定检验·要点参考数据①接地印制线路是否是最短?检验·要点参考数据GND与壳体GND的尽可能在接近接线端子的地方进行连接。

(与印刷底板的铜膜的阻抗相比,金属地线的阻抗要小。

)检验·要点参考数据判定①接线柱一端的无线电噪声、电波障碍对策用的电容器的GND印制线路作为良接地,要确实连接壳体GND、电路GND。

检验·要点参考数据①过孔、半过孔是否必要?检验·要点参考数据①阻焊层与焊盘的间隔适当吗?·作为基准,a≤0.15mm左右最好。

不良检验·要点参考数据①是否因残留的印制线路或突出引起参考数据为了提高耐断线性能,希望有复数个。

检验·要点参考数据在波峰焊工艺的方向45度5—11—2。

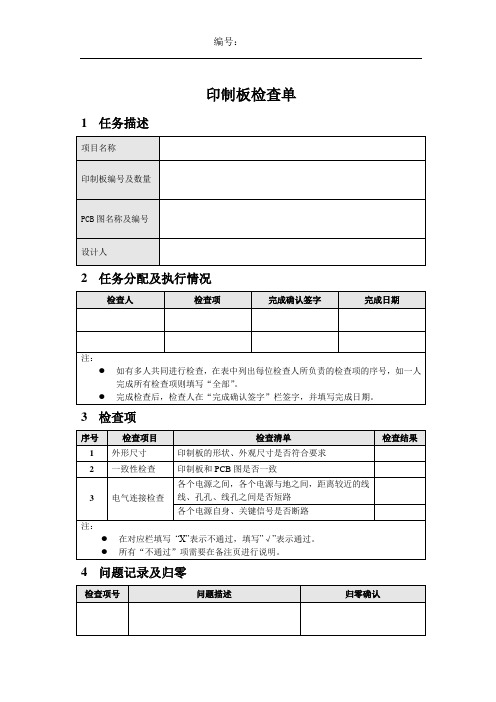

10-06印制板检查单

检查结果

1

外形尺寸

印制板的形状、外观尺寸是否符合要求

2

一致性检查

印制板和PCB图是否一致

3

电气连接检查

各个电源之间,各个电源与地之间,距离较近的线线、孔孔、线孔之间是否短路

各个电源自身、关键信号是否断路

注:

在对应栏填写“X”表示不通过,填写”√”表示通过。

所有“不通过”项需要在备注页进行说明。

印制板检查单

1任务描述

项目名称

印制板编号及数量

PCB图名称及编号

设计人

2任务分配及执行情况

检查人检查项Leabharlann 完成确认签字完成日期

注:

如有多人共同进行检查,在表中列出每位检查人所负责的检查项的序号,如一人完成所有检查项则填写“全部”。

完成检查后,检查人在“完成确认签字”栏签字,并填写完成日期。

3检查项

序号

检查项目

4问题记录及归零

检查项号

问题描述

归零确认

注:如发现有问题,检查人将检查单返给检查对象负责人,要求其修改,修改后检查人必须对修改结果进行归零确认。

印制板(PCB)自查与审核列表(可生产性、结构)

印制板设计自查与审核列表

——可生产性、结构版本表单编号:NO: 202101

【注解】

1.印制板性能等级

1级一一普通军用电子设备

主要用于地面和一般军用设备。

要求印制板组装后有完整的功能,一定的工作寿命和可靠性,允许有一些不影响电气和机械性能的外观缺陷。

2级一一专用军用电子设备

主要用于军用通信设备、复杂的军用电子设备等。

要求印制板组装后有完整的功能,较长的工作寿命及较高的可靠性,允许有不影响使用性能的轻微外观缺陷。

3级一一高可靠军用电子设备

主要用于车载、机载、舰载、航天等军用电子设备。

要求印制板组装后有完整的功能,长的工作寿命,连续工作和高的可靠性,在使用中不允许发生任何故障。

2.印制板可生产性等级

根据印制板的设计、公差、组装、生产工艺和成本,印制板可生产性等级可分为如下三级:A级一一复杂性较低,可生产性好(推荐使用);

B级一一复杂性中等,可生产性较好(一般使用);

C级一一复杂性高,生产难度大(特殊使用)。

PCB设计规范检查表DFM完整版

PCB设计规范检查表DFM完整版产品系列产品型号PCB 编码PCB 描述全部通过条件通过BQ-C10_3.3_BAS50-108V_V1.0PCB DFM\DFT ChecklistDatasheet for PCB Check ApprovalXXXXX 科技有限公司研发部产品工程部12拼板设计3456789111215161720212223242526布线时应无直角及锐角PCB 安全间距检查是否符合要求(特别是初次级变压器与pattern 的间距)PCB 上要有高压安全标识丝印应清晰,不能重复,不能被过孔打掉部品位置标记丝印不能放在部品下面,在部品丝印的内部不能标记部品位置丝印.SMD 器件与插件器件距离SMD 器件与PCB 边的距离过孔与走线距离插件与芯片距离SMD 器件与芯片距离要有器件极性标识及方向标识芯片的1脚标识应在外部明显地方器件丝印符号的规范性(参照丝印对照表格)定位孔设计(孔径及位置)Mark 点设计(反光点及位置)PCB 上制造公司信息PCB 上有产品名称及版本信息大小与实物封装是否一致间距设计焊盘位置设计是否合理关健覆盖点PCB 上应有符合要求的条码位置PCB DFM ChecklistNO检查项目检查结果检查人日期备注器件布局设计插件孔测试点工艺边及裁缝线等常规设计重器件布局经常插拔件布局过波峰焊接器件方向布局(如插件电阻及二极管等)工艺边设计是否符合要求(3-5mm)V-CUT 设计(角度45及深度插件器件孔径符合相关的规范插件与PCB 边距离邮票孔设计(孔径,间距等)拼板设计是否合理晶振接地及防短路插件孔的形状与实物封装要匹配丝印设计PCB 布线设计手工测试点大小针床测试点大小器件丝印的归属性(要求每个器件都有明确的丝印与之对应)器件丝印的完整性(所有的器件都要有丝印)过孔与焊盘距离SMD 器件与SMD 器件距离过孔与过孔距离插件器件与插件距离焊盘与布线是否匹配PC 焊盘的耐压值能否满足要求(尤其是线束结口的焊盘间距)过孔焊盘设计光耦、强电布线绝缘距离272829晶振,时钟芯片以及变压器下避免通过高速信号线。

PCB工艺检查一览表

10

10

布 局 的 工 艺 要 求

14.大功率器件必须考虑散热器的位置和足够的散热空间以及可靠的固定方式, 15.大功率器件周围不应布置热敏元件并要留有足够的距离 16.大质量的器件应考虑加装器件固定架或固定盘 17.所有不绝缘的金属外壳元件,当它们跨越印制导线时,应当有加强的绝缘措施 18.轴向插装元件立式安装时的插孔跨距是否大小合适 19.径向插装元件插孔跨距是否与元件引线中心距一致 20.相邻插装元件之间的间距是否利于手工插装作业 21.每个插装元件安装空间是否足够 22.PCB的元件标识符是否易于看到,有极向元件极性是否标出,比第一脚位置是否标出 23.PCB上接插件位置是否利于布线和插拔 24.元器件布局与机构安装是否有相互干涉的部位 1.SMD零件的焊盘上不能有任何样式的过孔 2.SMD零件的焊盘上不能有任何丝印图形或阻焊油墨,标志符号离焊盘边缘距离应≥0.5mm 3.凡是对称的SMD零件,其焊盘大小形状设置必须保持其全面的对称性 4.SMD零件的焊盘不允许直接设置于大面积的铜箔上 5.SMD零件的相邻焊盘若需短路连接,不允许直接不允许直接以铜箔连接而形成大焊盘 6.SMD零件的阻焊膜的厚度不得大于焊盘的厚度 7.SMD零件的焊盘的阻焊膜的开口尺寸,其宽度和长度分别应比焊盘尺寸大0.05~0.25mm 8.无外引线和倒装器件的焊盘之间不允许有通孔,以保证清洗质量 9.有极性或方向要求的器件必须标示易于识别的标识 10.波峰焊接的QFP等四边封装的器件应与PCB的传送方向呈45°排列 11.波峰焊接的SOIC、OFP零件必须在锡流的末端设置导锡用的工艺焊盘(前一焊盘的2倍大小) 12.呈直线排列的THT焊盘必须在锡流的末端设置导锡用的工艺焊盘(前一焊盘直径的2倍大小)

11

元 器 件 焊 盘 和 图 形 字

PCB板检验记录表格模板

厂商

适用机种

签收日期:__年__月__日检测日期__年__月__日

品名规格 使用仪器和工具:光标卡尺或直尺,万用表、标准冲针、负载机、示波器、千分尺、chroma、酒精灯等

检验项目

规格标准

判定

备注

铜箔

外形尺寸 AI 定位孔尺寸 基板供货商 文字印刷 基板厚度 外观

孔加工

材质 切割/V-CUT 表面处理 防火等级 过锡测试 防焊状况

□合格□不合格

防焊符合要求与 LAYOUT 图面一致

□合格□不合格

实例 长(mm) 宽(mm) 1 2 3 4 5

结果判定 □合格□不合格

板厚(mm)

实例 6 7 8 9 10

长(mm) 宽(mm)

板厚(mm)

单重(G)

核准

审阅

经办

冲孔类型□电钻/CNC,□模具冲孔/PUNCH,孔径测试用标准冲针测量 □合格□不合格

冲孔不可偏位.短路.断路

□合格□不合格

与 BOM 要求一致□22F□CEM-1□CEM-2□CEM-3□XPC□FR-1□FR-4 □合格□不合格

□1.0mm 板厚切(0.5+0.005)mm,□1.2mm 板厚切(0.8+0.15)mm,□玻纤系列切除 2/3

覆铜箔厚度:□1OZ:35um,□2OZ:70um

□合格□不合格

面铜:□单面,□双面,□多层

□合格□不合格

不可有氧化、翘铜、起泡现象

□合格□不合格

不可有短路断路现象

□合格□不合格

_____*______mm,8mm 以下±0.1mm,(8-25)mm±0.15mm,(25-80)mm ±0.2mm,(80-250)mm±0.3mm,250mm 以上±0.5mm

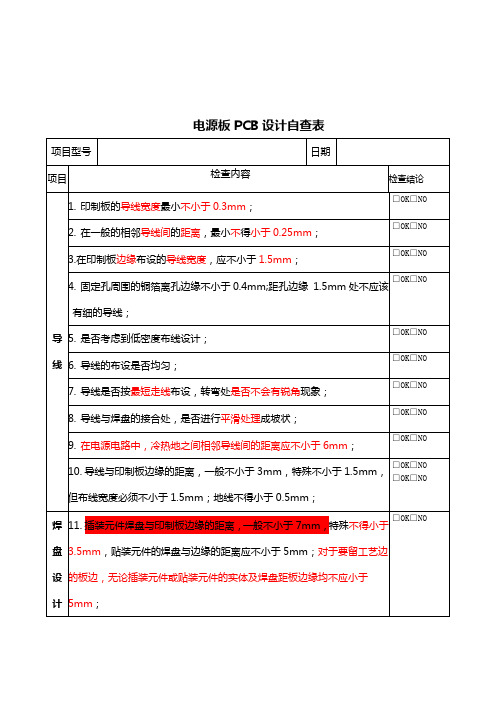

电源板PCB设计自查表

51.印制板边缘是否有易上锡的焊盘和铜箔,使得装配比较困难;

□OK□NO

52.竖板是否考虑了固定方式;

□OK□NO

53.固定在散热片上的元器件是否留有不拆卸散热器即可拆卸的空间;

□OK□NO

54.排插的周围是否有高大密集的元器件或者比较尖锐的散热器边角;

□OK□NO

55.输入输出排插放置位置是否满足与整机其它板连接的便利性;

□OK□NO

□OK□NO

焊盘设计

11.插装元件焊盘与印制板边缘的距离,一般不小于7mm,特殊不得小于3.5mm,贴装元件的焊盘与边缘的距离应不小于5mm;对于要留工艺边的板边,无论插装元件或贴装元件的实体及焊盘距板边缘均不应小于5mm;

□OK□NO

12.引脚间距1.78mm的IC其连接(焊盘)的间距应该不小于0.3mm;

电源板PCB设计自查表

项目型号

日期

项目

检查内容

检查结论

导线

1.印制板的导线宽度最小不小于0.3mm;

□OK□NO

2.在一般的相邻导线间的距离,最小不得小于0.25mm;

□OK□NO

3.在印制板边缘布设的导线宽度,应不小于1.5mm;

□OK□NO

4.固定孔周围的铜箔离孔边缘不小于0.4mm;距孔边缘1.5mm处不应该有细的导线;

29.不规则的PCB板是否有工艺边;

□OK□NO

30.工艺夹持边是否满足5mm的要求;

□OK□NO

31.是否需要增加工艺边来保证夹持位置;

□OK□NO

32.工艺边范围内不允许有焊盘、管脚、元件实体;

□OK□NO

33.距板边垂直水平5mm边角处需要留不少于三个孔径为4.0mm的工艺孔;

PCB检查表

PCB检查表文件名称:设计人员:NO:7322-RD-一.布局方面□ 1. 单块线路板外形尺寸,安装孔的尺寸和位置及其它有结构定位要求的尺寸和位置应符合产品设计要求。

□ 2. 用插件机的线路板长宽尺寸符合要求,长:150 mm~330mm,宽:80 mm~250mm,最佳宽度为140mm~180mm。

□ 3. MARK点的放置符合要求。

即在板的对角上放置MARK点,两MARK点位置:距非传输边15mm 以上;距传输边4mm以上。

□ 4. 元器件本体距印制板传输边不得小于5mm。

□ 5. 机插定位孔周围11*11mm盲区及上下5mm的边框,不得有机插元器件。

□ 6. 大功率发热元器件和相邻塑料件及其他温度敏感器件之间的间距至少为5mm。

□ 7. 对于吸热大的器件,在整板布局时要考虑焊接时热均衡原则,不要把吸热多的器件集中放在一处,以免造成局部供热不足,而另一处过热现象。

□ 8. 相邻贴片器件的焊盘最少相距0.5mm。

□ 9. 以机插元器件被弯脚的引脚为圆心0°~90°(象限角度为与器件弯脚方向一致)半径为3mm 的范围内焊点面不能放置贴片器件。

□ 10. 插件IC的摆放要与生产时PCB的夹送方向平行。

□ 11. 贴片IC(SOIC)与PCB夹送方向平行,并在末端设置偷锡焊盘。

□ 12. 贴片QFP或LQFP的焊盘排列方向要与生产时PCB的夹送方向成45度角,同时在末端设置偷锡焊盘。

偷锡焊盘其宽度一般为焊盘的2-3倍。

□ 13. 贴片电阻、电容、二极管、三极管在线路板上的放置方向要与过波峰焊方向垂直。

□ 14. SOP器件轴向需与波峰焊方向一致。

□ 15. 原则上同块线路板的器件全为插件或全为贴片。

瓷片电容、三极管等径向元件应尽量设计成贴片,以提高生产效率;若该产品已含有贴片工序,则瓷片电容、三极管径向元件一定设计为贴片。

□ 16.机插电容设计5mm跨距;跳线、1/4w以下电阻、玻璃封装的二极管设计成10mm跨距。

PCB工艺设计CheckList

6 7 8 9 10 11 12

BGA、CSP器件的贴装面的背面是否有其它 BGA、CSP器件的背面不允许贴装器件,以防止其影响到BGA、CSP器件的X-RAY检测。 器件贴装? 大型器件四周是否留有一定的维修空隙? 应留出SMD返修设备加热透能够进行操作的尺寸,较矮小的器件不应被高大的器件围住。 密脚器件(引脚间距≤0.5mm)布局是否合 1.不能布置在离板边10mm范围内; 理? 2.钢网需局部加厚的器件8mm范围内禁布密脚器件。 器件兼容设计是否符合要求? 焊盘设计是否符合要求? 器件高度是否满足要求? 1.不允许两个器件共用一个焊盘; 2.不允许两个表面贴装的异型引脚器件重叠。 PCB焊盘与器件封装要一致,具体参考IPC-SM-782A。 除结构有特殊要求之外,THD器件都必须放置在正面;背面贴片器件高度≦5mm。

丝印方向

TOP面上,优先水平放置。

丝印外形

丝印位号 丝印批号 丝印过板方向 留空间

锡焊盘、阴影效应。

m二维码空间。

局部Mark点

路丝印处,放置完器件后应可见。

整板Mark点数为3

整板Mark点数为2

刷设备的能力。太小刮刀无法板自动刷

钢网的尺寸厚度

测试点设置 四个角倒45°R角

PCB下流。

炉等过程中碰损元器件。

引脚阻焊是否有做桥位?

ist

评审日期

评审结果 回流焊≤255℃ 波峰焊≤265℃

不符合说明

改善建议

℃,3s(一般235~255℃); 良(浮起、立碑等);过波峰焊时不能

优先SMD件 编带 异性器件带吸附面

吸附面的封装;

绿油覆盖

般是≤0.4pitch; 加阻焊漆

间距为2.54mm。

直径一般≥1.4mm

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

图1 a

Mi

检查项目

V

PCB尺寸(最大)

图2

图3

允收标准

长L≤350*宽M≤300(mm) 若 长L>350mm,宽M>300mm,須知会工艺 最小板子长L≥50mm,宽≥50mm

V

工艺边

工艺边L≥5mm,若无工艺边,则要设置相应 的禁布区M≥5mm

图4

图例

SMT M

L L L

使其轴线和波峰焊方向平行

v THC布局

较轻的器件如二级管和1/4W 电阻等,布局 时应使其轴线和波峰焊方向垂直

v

V V V

对PCB上轴向插装等较长、高的元件,应该 考虑卧式安装

a) IC的第一脚。

b) 各种插槽(包括:IDE、DB15、VGA、

有极性的 connector 防呆 USB、SOCKET等等)的第一脚。

PIN 设计

c) CONNECTOR的第一脚。

d) JUMPER的第一脚。

以上的第一脚焊盘设计成方形焊盘

電池的使用

電池不能使用一体式的

需使用载具制程

在BOOTOM面THC因脚周围5mm范围内不 能布器件

L1 L

DIP

L 过板方向

第 6 页,共 8 页

V

电解电容极性”+”及 在正极端须标示白色”+”标示,并标示零

图5

NG料号/位置

判定

OK

NG

无法达到标准之 风险评估 建议其修改之方式

原因(说明)

(说明)

(说明)

M M

v

PCB倒角

如果板子不需要拼板,要求板子4个角圆角

r

。如果板子需要拼板,要求拼板后的板子4

个角为圆角,圆角的最小尺寸半径为r=5mm

拼板

单板

PCB在SMT生产方向为短边过回焊炉

PCB过板方向定义 (Reflow), PCB长边为SMT传送帶夹持边。 v

无铅板要加入无铅标识

V

DIP电容与BGA边缘距 离

≧200mil (5mm)

V

散热器与电容距离( TOP面 )

≧80mil(2mm)

V

电解电容彼此间的外框 L≧20mil (0.5mm) 间距

V

DIP电容极件请统一两 个方向

正极端统一朝上或下,朝左或 右

多个引脚在同一直线上的器件象连接器、

V

DIP 封装器件、T220 封装器件,布局时应

v

v v

v v v v v v

BGA 器件周围须留有L≥3mm 禁布区,最佳 为5mm禁布区,且BGA 不允许放置BOTTOM面

L

L

INTEL BGA

L

L

TOP面

SMD元件布局(2) SMD元件布局(3)

BOTTOM面(reflow)SMD布局的重量限制如 下:

A=器件重量/引脚与焊盘接触面 积 片式器件:A≦0.075g/mm2 翼形引脚器件:A≦0.300g/mm2 J 形引脚器件:A≦0.200g/mm2 面阵列器件:A≦0.100g/mm2 如必须放在BOTTOM要通知工艺并须要有实 验证明其可靠性 PCB I/O port 板边的螺丝孔(星月孔)PAD 至PCB板边, 禁布SMD或DIP零件(如右图黃 色区).

度 与较宽印制线连接的焊盘,中间最好通过

一段窄的印制线过渡,这一段窄的印制线 通常被称为“隔热路径”,

大面积电源区和接地区的元件连接焊盘, 应设计成花焊盘

零件Pad尺寸L1需>零件Pin脚尺寸L

L

L1

TOP面的焊盘间距(见表11-1) 线路与SOIC、PLCC、QFP、SOT等器件的 焊盘连接时,一般建议从焊盘两端引出

文字面

件位置

V 电解电容标示

负极端之半圆形框內,需填满白色实线。

EC1 EC2

V DIP 波峰焊流向文字面 PCB须标示DIP流向

v

V

V V

v v

V V

V V V

有I/O Port的PCB传送 方向

PCB在DIP生产方向为I/O Port朝前过波 焊炉(Wave Solder), PCB与I/O垂直的两边 为DIP传送帶夹持边。

I/O DIP過板

DIP器件本体与器件丝 印框

丝印框≥器件本体

丝印框 器件本

PTH铜箔设计

BGA区域内的导通孔 阻焊设计

为因为无铅制程,新增之项目(有铅及无铅均适用)

无论哪一层接大铜箔时,均需以Thermal relief方式衔接

作测试点,导通孔塞孔,焊接面开满窗; 不作测试点,绿油塞孔

塞孔

开满窗

BGA区域外的导通孔 作测试点:在TOP面开小窗,在BOTTOM面开

要 求 Mark 点 标 记 为 实 心 圆 , 除 局 部 MARK 点外要加上金属保护圈。基准点的材料是 裸铜或覆铜。

MARK 点 直 径 r = 1mm , 阻 焊 开 窗 直 径 R = 2mm,金属保护圈的中心距L=3mm,金属保 护圈的环宽M=6mil,

MARK点下PCB内层要铺设铜箔

局部MARK L

PCB传送方向

第 8 页,共 8 页

IC器件一般要表示出1号脚位置,用小圆圈 或数字表示

V

对BGA器件用英语字母和阿拉伯数字构成

字符图(2)

的矩阵方式表示

V

极性元件要表示出正极,用“+”表示;二极

V

管采用元件的图形符号表示,并表示出“+” 极;转接插座有时为了调试和连接方便,

也需要标出针脚号。

焊盘 缺口

第 5 页,共 8 页

v

字符图(3)

机种:

版

本:

检查人员:

印制电路板设计(工艺性要求)检查表单

工艺路线 单面全SMD(图1) 双面全SMD(图2) 单面元件混装(图3) TOP面元件混装BOTTOM面仅贴简单SMD(图4) TOP面插件BOTTOM面仅贴简单SMD(图5) 注:简单SMD-----CHIP、SOT、引线中心距大于1 mm的SOP, 图4是公司常用的组装形式,图2是最理想的组装形式,建议推广。

R PTH

丝印框 邮票孔

BGA器件布局时,与过板方向成90°或0°

INTEL BGA

过板方向

布线要求(1)

内 、 层 线 路 及 铜 箔 距 板 边 L ≥ 0.5mm (20mil)

L

插拔式单板:内层线路及铜箔距板边L2≥ 1mm(40mil);外层线路及铜箔距板边L≥ 导轨深度L1+2mm(80mil)。

阻焊设计

满窗;

开小

不作测试点:开窗

BGA丝印设计

BGA文字框外缘标示W 有一定宽度的实心 框, 以利维修时对位置件;

BGA极性以三角形实心框标示.

BGA实体

INTEL

BGA

L

PCB设计

L

W

L

L

PTH thermal relief切 割为十字形

PCB厚度

最大 3mm, 最小 0.8mm

RLC晶体避免使用共用 Pad(如右图示)

mil)的QFP、中心距≤0.8 mm(31 mil) BGA 的BGA等器件,应在该元件中心点对角线附

近的对角设置MARK点;如果几个SOP器件比

较靠近(<100mm)形成阵列,可看作整体, 在其对角位置设计两个MARK点。

QFP SOP阵列

传送边SMD距板边L≥200mil (5mm)内禁布

L

传送方 v

排成一列的无阻焊导通孔焊盘,波峰焊盘 的间隔大于0.5 mm(20 mil) v

导通孔焊盘

排成一列的无阻焊导通孔焊盘,回流焊盘

的间隔大于0.2 mm(8 mil) v

第 4 页,共 8 页

V 螺丝孔设计

采用星月孔进行设计 螺丝孔范围內,禁止置放零件。

当表面组装元件焊盘间隙≥0.25mm(10mil) 时,采用单焊盘式窗口设计;间隙<0.25 mm(10mil)时,采用群焊盘式窗口设计

L

拼板时SMD距V-CUT槽L≥40mil (1mm)内禁

布

v

SMD元件布局(1)

V-CUT

LL

插拔器件或板边连接器周围在TOP面L=2mm

v

范围内禁止布置SMD及L1=2.5mm范围内禁止 布置3mm高的SMD;在BOTTOM面3mm范围内禁

L L1

L

止布置SMD

TOP面

BOTTOM

第 2 页,共 8 页

R L

L4m间m的,连槽接长桥LL42为为255

mm~80 mm,槽与槽之 mm~7 mm,小圆孔的孔

D

L

径 D 为 Ф 0.8mm ~ 1 mm , 孔 中 心 距 L3 为

D L

D+0.4 mm~0.5 mm,板厚取较小值,板薄

取较大的值。

L1 L2

L L2

第 1 页,共 8 页

v

MARK点设计

L 外层铜

内层铜

L2

内层铜

L L

L1 L 外层铜 导槽

第 3 页,共 8 页

V v

v

布线要求(2)

拼板分离边: 1.V-Cut:内、外层线路及铜箔距板边L≥1mm

(40mil); 2.邮票孔:内、外层线路及铜箔距板边L1≥

0.5mm(20mil);

线宽L≥5mil,线距L1≥4mil

L

L L

内层铜 外层铜

片式器 J形引脚器件

翼形引脚器 面阵列器件 PAD

V-Cut或邮票孔须距正上方垂直板边的SMD

丝印

器件丝印框外缘L≧2mm(80 mil)。

L

L

V-Cut

丝印 邮票孔

V-Cut或邮票孔须距正上方平行板边的SMD