基于工具软件的直接数字频率合成器设计方法

基于FPGA平台的数字频率合成器的设计和实现

基于FPGA平台的数字频率合成器的设计和实现数字频率合成技术是一种实现高精度频率合成的方法,具有广泛应用价值。

在数字频率合成中,FPGA是一种非常重要的平台,能够实现高速、高精度、可编程的数字频率合成。

本文将介绍基于FPGA平台的数字频率合成器的设计和实现。

一、FPGA简介FPGA是一种可以编程的数字集成电路,具有非常灵活的可编程性。

FPGA中包含了大量的逻辑单元、存储单元和输入输出接口,可以通过编程实现各种数字电路功能。

FPGA具有高速、高度集成、低功耗等优点,在数字电路的设计和实现中得到了广泛应用。

二、数字频率合成的基本原理数字频率合成是通过一组特定的频率合成器和相位加法器来合成所需要的频率。

首先,将参考频率和相位加法器连接起来,形成一个频率合成器。

然后,将输出频率与参考频率的比例进行数字控制,并将输出频率的相位与参考频率相位进行加法计算,最终输出要求的频率。

三、数字频率合成器的设计1. 参考频率生成模块参考频率生成模块是数字频率合成器的核心模块。

参考频率一般使用晶振作为输入信号,并通过频率除和锁相环等技术来产生高精度的参考频率。

在FPGA中,可以使用PLL、DCM等IP核来实现参考频率的生成。

2. 分频器分频器是将参考频率转化为所需的输出频率的模块,一般使用计数器实现。

在FPGA中,可以使用计数器IP核或使用Verilog等HDL语言来实现。

3. 相位加法器相位加法器用于将输出频率的相位和参考频率的相位相加。

在FPGA中,可以使用LUT(查找表)实现相位加法器。

4. 控制单元控制单元用于控制数字频率合成器的各个模块,并实现与外部设备的接口。

在FPGA中,可以使用微处理器或FPGA内部逻辑来实现控制单元。

四、数字频率合成器的实现数字频率合成器的实现需要进行数字电路设计和FPGA编程。

一般来说,可以采用Verilog或VHDL等硬件描述语言进行FPGA编程,实现各个模块的功能。

数字电路设计过程中,需要考虑到功耗、面积和时序等问题,同时需要进行仿真和验证。

直接数字频率合成信号的软件设计

( rp i U e It fc , 称 G I, 整 参 数 k 1 ≤1 0 可 以 产 生 1 10Hz 意频 率 的 时 域 和 频 域 波 形 , 够 产 G ahc sr ne ae 简 r U )调 (≤ 0) —0 任 能

生 直 接 数 字频 率 合 成 信 号 . 到 设 计 要 求 。 达

3 结束 语

根 据 以 上设 计 , 作 了智 能 拐 杖 样 机 。 通 过 对 样 机 的 测 制 试 , 要实现了如下功能 : 主 1卫 星定 位 功 能 , ) 监护 人 可 随 时确 定使 用者 的 具体 位 置 ; 2 偏 离提 示 和 求 助 功 能 , 使 用 者 偏 离 预 定 路 线 时 给 予 ) 在 主 动 提 示 , 要 时 呼 叫 监 护 人 , 出求 助信 息 ; 必 发 3 拐 杖 倾 倒 自动 呼 救 功 能 , 使 用 者 摔 倒 , 杖 随 之 倾 ) 在 拐 倒 超 过 一 定 时 间 , 动 向 监 护 人 发送 求 救 信 息 ; 主 4 监 护 人 可 以通 过 微 机 监 控 使 用 者 的 活动 轨 迹 , 现 连 ) 实 续实时定位 。 本 项 目推 广 应 用 后 . 以 解 决 老 年 人 、 疾 人 和 智 障 人 可 残 士 因 种 种 原 因在 迷 路 、 失 时 . 使 用 者 和 监 护 人 等 提 供 有 走 给 效 帮 助 , 助 监 护 人 迅 速 找 到 使 用 者 , 免 进 一 步 的 意 外 发 帮 避 生 。随 着 社会 的发 展 和 生 活 水 平 的 提 高 , 心 和 改 善 老 年 人 、 关 残 疾 人 和 智 障 人 士 的 生 活 质 量 是 大 势 所 趋 , 项 目有 广 阔 的 该 应用 前景 。 有 很好 的经 济 意 义 和 社 会 意 义 。 具

DDS实验报告

电子线路课程设计 --直接数字频率合成器(DDS)2014 年 11 月摘要本实验通过使用 QuartusⅡ软件,并结合数字逻辑电路的知识设计,使用DDS 的方法设计一个任意频率的正弦信号发生器,要求具有频率控制、相位控制、以及使能开关等功能。

在此基础上,本实验还设计了扩展功能,包括测频、切换波形,动态显示。

在控制电路的作用下能实现保持、清零功能,另外还能同时显示输出频率、相位控制字、频率控制字。

在利用 QuartusⅡ进行相应的设计、仿真、调试后下载到SmartSOPC实验实现 D/A转换,验证实验的准确性,并用示波器观察输出波形。

关键词:SmartSOPC实验箱 QUARTUSⅡ数字频率合成仿真AbstractThis experiment is based on QuartusⅡ,with the help of knowledge relating to the digital logic circuits and system design,to design a sine signal generator which generates any frequency by the method of DDS. This generator is provided with the functions of frequency control,phase control and switch control. Based on the basic design,I also design extra functions,including frequency measurement,changes of wave forms and dynamic display.The control circuit can be maintained time clearing and time keeping functions,and also shows the output frequency,phase control characters,frequency control word. All the designing and simulating work are based on QuartusⅡ. After all the work finished on computer, I downloaded the final circuit to SmartSOPC experiment system to realize the transformation of D/A ,and then test the accuracy of the design by means of oscilloscope observing the wave forms.Key words: SmartSOPC QUARTUSⅡ DDS Simulation目录摘要 (1)目录 (2)一、设计要求 (3)二、方案论证 (3)三、直接数字频率合成器总电路图 (4)四、各子模块设计原理及分析说明 (5)4.1、脉冲发生电路 (5)4.2、频率相位预置与调节电路 (9)4.3、累加器电路 (10)4.4、相位控制电路 (11)4.5、波形存储器ROM电路 (12)4.6、测频电路 (14)4.7、不同波形选择电路 (15)4.8、动态译码显示电路 (16)五、程序下载、仿真与调试 (17)六、实验结果 (18)七、实验总结与感想 (23)八、参考文献 (23)一、设计要求1、利用QuartusII软件和SmartSOPC实验箱实现直接数字频率合成器(DDS)的设计;2、DDS中的波形存储器模块用Altera公司的Cyclone系列FPGA芯片中的RAM 实现,RAM结构配置成212×10类型;3、具体参数要求:频率控制字K取4位;基准频率fc=1MHz,由实验板上的系统时钟分频得到;4、系统具有使能功能;5、利用实验箱上的D/A转换器件将ROM输出的数字信号转换为模拟信号,能够通过示波器观察到正弦波形;6、通过开关(实验箱上的Ki)输入DDS的频率和相位控制字,并能用示波器观察加以验证;7、可适当添加其他功能二、方案论证直接数字频率合成器(Direct Digital Frequency Synthesizer)是一种基于全数字技术,从相位概念出发直接合成所需波形的一种频率合成技术。

proteus frequency用法

Proteus频率是一种用于频率合成和仿真的软件工具,广泛应用于电子设计和通信系统的研发中。

Proteus频率可以帮助工程师们快速准确地设计和测试各种类型的频率合成器和信号处理器。

在本文中,我们将介绍Proteus频率的基本用法,包括频率合成器的设计、仿真和测试等。

一、Proteus频率的基本概念1. 什么是Proteus频率Proteus频率是由Labcenter Electronics公司开发的一款用于频率合成和仿真的软件工具。

它包括了多种模拟和数字信号处理器,能够进行快速准确地频率合成和仿真。

2. Proteus频率的应用范围Proteus频率广泛应用于通信系统、雷达系统、无线电频率合成器、射频电路设计等领域,也可用于教育和研究。

二、Proteus频率的设计和仿真1. 频率合成器的设计Proteus频率可以帮助工程师们设计各种类型的频率合成器,包括PLL 频率合成器、直接数字频率合成器、混频器等。

用户可以根据需求选择合适的器件、参数和电路拓扑,通过Proteus频率实现快速的设计。

2. 信号处理器的仿真Proteus频率包括了各种模拟和数字信号处理器,用户可以通过Proteus频率对频率合成器进行仿真和性能测试。

通过仿真,工程师们可以快速准确地评估频率合成器的性能指标,如相位噪声、频率偏移等。

三、Proteus频率的测试和验证1. 软件模拟器的测试Proteus频率提供了软件模拟器,可以快速方便地对频率合成器进行测试。

用户可以通过软件模拟器观察频率合成器的输出波形、频谱特性等,评估其性能指标。

2. 硬件实现的验证Proteus频率还支持用户将设计好的频率合成器连接到硬件评台上进行测试和验证。

用户可以通过Proteus频率导出相应的电路图和PCB 布局,方便在实际硬件评台上实现和验证设计的频率合成器。

四、Proteus频率的优势特点1. 方便快捷Proteus频率集成了多种工具和模块,可以帮助工程师们进行频率合成和信号处理工作,使得设计、仿真和测试变得更加方便快捷。

基于MC145151-2PPL频率合成器的设计

一

频 率 合 成 器 的 频 率分 辨 率 。 改 变 R数值 的 大 小 ,

准 频率源相组合 ,就能产生与标准信号源有相 同的频率稳定度、准确度的众多频率点。

可改变频率合成器的分辨率。由以上可以看 出 当环路锁定后,压控振荡器的输出频率严格 与 输入 频率 行相等 。同时在 一定 范围 内跟踪 输 入信号频率变化 ,具有 良好 的跟踪特性 。只要 L P F通频带设计合理,整个环路就具有 良好的

窄带滤波特性。

1 M C 1 4 5 1 5 1 - 2 锁相环 简介

MC1 4 5 1 5 1 - 2是 一 块 双 列 直 插 式 C M OS大 规 模 集 成 电路 , 由 4位 总 线 输 入 、 锁 存 器 选 通

个 高 稳 定度 的 标 准 频 率 f s , 经 参 考 分 频 器 进

:

R A 2 R A 1 R A o M c 1 4 5 1 5 1 — 2

: : M A X 3 0 8

;

随 着 移 动 通 信 、雷 达 技 术 以及 遥 测 、 遥

感测控技术不断发展 ,各种 系统对频 率源 的要 求越来越高 , 不但 要求频率稳定度和准确度高, 而且还要求能方便 的改变 收发频率。特别是无

图一 1 基 本锁相 环 频率合 成 器组 成框 图

【 关键词 】频率合成 V C O 锁相环 频率 源 分

频 器

广 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 1 广 一 一 一 一 一 一 一 一 一 一 一 一 一 一 一 1

最新-实现直接数字频率合成器的三种技术方案 精品

实现直接数字频率合成器的三种技术方案摘要讨论了的工作原理及性能性点,介绍了目前实现常用的三种技术方案,并对各方案的特点作了简单的说明。

关键词直接数字频率合成器相位累加器信号源现场可编程门限列1971年,美国学者等人撰写的-文首次提出了以全数字技术,从相位概念出发直接合成所需波形的一种新给成原理。

限于当时的技术和器件产,它的性牟指标尚不能与已有的技术盯比,故未受到重视。

近1年间,随着微电子技术的迅速发展,直接数字频率合成器简称或得到了飞速的发展,它以有别于其它频率合成方法的优越性能和特点成为现代频率合成技术中的姣姣者。

具体体现在相对带宽宽、频率转换时间短、频率分辨率高、输出相位连续、可产生宽带正交信号及其他多种调制信号、可编程和全数字化、控制灵活方便等方面,并具有极高的性价比。

1基本原理及性能特点的基本大批量是利用采样定量,通过查表法产生波形。

的结构有很多种,其基本的电路原理可用图1来表示。

相位累加器由位加法器与位累加寄存器级联构成。

每来一个时钟脉冲,加法器将控制字与累加寄存器输出的累加相位数据相加,把相加后的结果送到累加寄存器的数据输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。

这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位加累加。

由此可以看出,相位累加器在每一个中输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位,相位累加器的出频率就是输出的信号频率。

用相位累加器输出的数据作为波形存储器的相位取样地址。

这样就可把存储在波形存储器内的波形抽样值二进制编码经查找表查出,完成相位到幅值转换。

波形存储器的输出送到转换器,转换器将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号。

低通滤波器用于滤除不需要的取样分量,以便输出频谱纯净的正弦波信号。

在相对带宽、频率转换时间、高分头放力、相位连续性、正交输出以及集成化等一系列性能指标方面远远超过了传统频率合成技术所能达到的水平,为系统提供了优于模拟信号源的性能。

直接数字频率合成技术DDS

幅

位

度

码

码

数模变换器 DAC

时 钟

低通滤波器 LPF 输出

图3-11 相位/幅度变换装置

假设DAC的输入幅度码是四位,则它的输出幅度与输 入幅度码之间的关系是按线性变化的,如表3-1所示。

二进制幅度码 0000 0001 0010 0011 0100 0101 0110 0111

表 3-1

十进制幅度 二进制幅度码

0.1875

0 +1.1875

续表 3 - 4

8 1000 17π/16 -0.1951 0011 0.1875 1 9 1001 19π/16 - 0.5556 1001 0.5625 1 10 1010 21π/16 - 0.8316 1101 0.8125 1 11 1011 23π/16 -0.9808 1111 0.9375 1 12 1100 25π/16 -0.9808 1111 0.9375 1 13 1101 27π/16 -0.8316 1101 0.8125 1 14 1110 29π/16 -0.5556 1001 0.5625 1 15 1111 31π/16 -0.1951 0011 0.8175 1

② 将模2π的累加相位变换成相应的正弦函数值的幅度, 这里幅度可先用代码表示,这可以用一只读存储器ROM来 存储一个正弦函数表的幅值代码;

③ 用幅度代码变换成模拟电压,这可由数模变换器 DAC来完成;

④ 相位累加器输出的累加相位在两次采样的间隔时间 内是保持的,最终从DAC输出的电压是经保持的阶梯波。

2. 相位与幅度的变换

累加器输出的相位码,需先经过一个相位码/幅度码变换 装置之后,再经数/模变换生成阶梯波,最后通过低通滤波 器才能得到所需的模拟电压。

《基于FPGA的PLL+DDS的频率合成器》范文

《基于FPGA的PLL+DDS的频率合成器》篇一一、引言随着通信技术的飞速发展,频率合成器作为电子系统中的关键部件,其性能和稳定性直接影响到整个系统的性能。

本文将详细介绍一种基于FPGA(现场可编程门阵列)的PLL(锁相环)+DDS(直接数字合成器)的频率合成器,并对其设计原理、实现方法及性能优势进行深入探讨。

二、PLL+DDS频率合成器的工作原理PLL+DDS频率合成器通过将PLL与DDS结合,利用两者的优势来达到高精度、高稳定性的频率输出。

PLL模块主要负责跟踪和生成参考频率,而DDS模块则能够快速生成多种频率的波形。

FPGA作为核心控制器,负责协调PLL和DDS模块的工作,实现频率的合成和输出。

三、设计实现1. 硬件设计在硬件设计方面,PLL+DDS频率合成器主要包含FPGA、PLL模块、DDS模块以及输出电路等部分。

其中,FPGA作为核心控制器,负责协调整个系统的运行。

PLL模块采用高精度的锁相环电路,以实现稳定的参考频率输出。

DDS模块则采用数字方式生成多种频率的波形。

2. 软件设计在软件设计方面,需要编写FPGA的程序代码来实现对PLL 和DDS模块的控制。

通过配置FPGA的IO口,实现对PLL和DDS模块的驱动和控制。

同时,还需要编写相应的算法程序,以实现频率的合成和输出。

四、性能优势基于FPGA的PLL+DDS频率合成器具有以下优势:1. 高精度:PLL和DDS的结合使得频率合成器具有高精度的频率输出。

2. 高稳定性:通过PLL模块的锁相环电路,可以实现稳定的参考频率输出,从而提高整个系统的稳定性。

3. 快速响应:DDS模块采用数字方式生成波形,具有快速响应的特点,可以快速调整输出频率。

4. 灵活性:FPGA的可编程性使得频率合成器具有很高的灵活性,可以方便地实现多种功能的扩展和升级。

五、应用领域基于FPGA的PLL+DDS频率合成器在通信、雷达、电子测量等领域具有广泛的应用。

例如,在通信系统中,它可以为基站提供稳定的射频信号;在雷达系统中,它可以为雷达提供精确的扫描频率;在电子测量领域,它可以用于信号源的生成和测试等。

基于FPGA直接数字频率合成器DDS的设计

量, 相位增加量 的大d E频率控制字确定 。信号波形 的数据 表包 含待 , h 产生信号一个周期 的幅度一相位信息 。 从数据表中读出相位累加器输 出相位信号值对应 的幅度 数据 .通过 D C 该数据转换成所需 的模 A 将 拟信号波形输 出。相位累加器 的相位 累加 为循 环迭加 . 这样使得输 出 信号 的相位是 连续的 直接数字合 成器 D S D 就是 根据上述原理 而设 计的数字控制频率合成器

k y p r ft u la e ato hen ce rDDS ,DDS d sg e u la ,b h h s c u ltra d te wa eol aatbe ta a e rt btaywa eoi O e in d n ce r y t ep a e a c muao n h v fYn d t a l h tc n gneaea irr v frlt r T

生任意波形。F G P A器件 作为 系统控制 的核 心 , 其灵活的现 场可更改性 , 可再配置能力 , 系统的各种改进非常方便 , 对 在不更改硬件 电路的基础 上进一步提 高系统的性能 【 关键词 】 直接数字频率合成 ; 相位 累加器 ;P A FG

Di e tDi i e u nc y t e sg Be s d o r c g t Fr q e y S n h  ̄s De i n a e n FPGA al

F PGA e iea h o esse c nr 1Ta lofrh ri rv h efr n e o es se d vc stec r ytm o to. nas u te mp o etep roma c ft y tm. h

【 e od] icdgaFeuny ytesF G Pae cu u t K yw rsDr t it rqec n s ;P A;hs acm lo e il s hi ar

基于FPGA的DDS直接数字频率合成器设计与实现

图 5

期只采样 2点,难 以保证输出精度 。为了保证输 出精度 ,规 定最低每 周期采样 8 点,此时 K 2/ = 2 ,则 :f = = 8 18 … K×

f/ 1 . 2 H c2= 6 5 M z 5

( )最 小步长的正弦波 ( 6 1 图 )

频 率 控 制 字 : 00 0 0 0 00001 相 位 控 制 字 : 00 0 0 0 00000

r — V v\ 1 / 厂 八 八八 / / ^厂 r u 厂 九 \ ^\ 、

图7

仿 真测得正弦波频率为:2 2 . 8 8 7 s2 .6 s /( 0 3 76 u 一 0 2 u )≈ 1. 4 3 H ,与计算参 数相 近,误差来 自于仿真测量时的显 5 6 1M z

2 波形存储 .

本设计 中波形存储 为连续存储 ,对正 弦波进行采样 利用 O a ts制造 一个 R M ,进 行 查值 操 作 , 波 形 的 存 储 方 法 ur u O表 在 上可 以有两种 方案 ,一个是对正弦波从 0到 2 进行采样 ,在 兀 这 次 设计 和 以上 的 参 数 选 取 上 均 基 于 这 种 方 案 ,这 个 方 案 的

示 误差 。

正弦波幅值的获得 ,可通过 C语言编程得到,将 C程序

所 得 结 果 导 出 到一 个 文 件 中 便 可 得 到 正 弦波 幅 值 。 3 系 统 设计 . 由波 形 存 储 模 式 ,设 计 系统 模 型 框 图 4 :

( )最 大 步 长 的 正 弦波 ( 7 2 图 ) 频 率 控 制 字 : 0 10 0 0 00000 相 位 控 制 字 :0 0 0 0 0 0 0 0 00

优 点 是 实现 简 单 ,思 路 清 晰 ;另一 种 方 案 是 对 正 弦波 从 0到

EDA课程设计直接数字频率合成器(DDS)

,a click to unlimited possibilities

汇报人:

目录

01 添 加 目 录 项 标 题

02 D D S 的 原 理

03 D D S 的 硬 件 实 现

04 D D S 的 应 用

05 D D S 的 软 件 仿 真 与实现

06 D D S 的 优 化 与 改 进

医疗领域:用于 医疗设备的信号 处理和传输

军事领域:用于 雷达、通信、电 子对抗等设备的 信号处理

工业领域:用于 工业自动化设备 的信号处理和控 制

Part Five

DDS的软件仿真与 实现

软件仿真工具介绍

MATL AB:强大的数学计算和图形处理 能力,适合进行信号处理和仿真

Simulink:MATL AB的扩展工具,可以 进行系统级仿真,支持DDS模块

DDS的动态范围扩展

动态范围扩展原理:通过调整DDS的输出电压和频率,实现动态范围的 扩展 动态范围扩展方法:采用数字信号处理技术,如滤波、放大、压缩等

动态范围扩展效果:提高DDS的输出信号质量,降低噪声和失真

动态范围扩展应用:在通信、雷达、电子对抗等领域具有广泛应用

THANKS

汇报人:

DDS的频率分辨率优化

频率分辨率定义:衡 量DDS性能的重要参 数,表示输出信号的 频率精度和稳定度。

优化方法1:采用高 精度的参考时钟源, 提高时钟频率,减小 DDS的相位截断误差。

优化方法2:增加相 位累加器的位数,扩 大频率调制的范围, 提高频率分辨率。

优化方法3:采用数 字滤波技术,对DDS 输出信号进行滤波处 理,减小杂散分量, 提高频率分辨率。

实际应用:通过对DDS的相位噪声 进行降低,可以提高信号的纯度, 减小干扰和失真,从而提高通信、 雷达、电子对抗等系统的性能。

基于FGA的直接数字频率合成器的优化设计

基于FGA的直接数字频率合成器的优化设计作者:彭昭胡进峰来源:《电子世界》2012年第18期【摘要】介绍了DDS的基本工作原理,针对传统DDS存在的主要问题,提出了基于流水线结构的累加器和基于波形对称的ROM优化设计,并在开发软件Quartus II上仿真,验证了优化设计的正确性。

不仅提高了系统的运算速度,而且也节省了硬件资源。

【关键词】FPGA;DDS;流水线结构;仿真1.引言随着科技的飞速发展,对信号发生器的要求越来越高,传统分立式模拟电路来难满足[1]。

直接数字频率合成法(Direct Digital Frequency Synthesis简称DDFS或DDS)具有频率稳定度高、分辨率高、切换时间短、相位变化连续、易于实现各种数字调制、集成度高等特点,能很好的满足各种需求[2]。

因此,DDS技术在通信、雷达、电子对抗、仪器测试等领域都有广泛的应用。

专用DDS 芯片在控制方式、频率控制等方面不灵活,很多时候不能满足系统的要求,利用FPGA来设计符合自己需要的DDS系统就是一个很好的解决方法。

2.DDS的工作原理DDS是利用数字相位累加产生线性变化的数字相位输出信号,通过波形数据查找表,获得对应于相位信号的数字化幅度信号,再通过数模转换器(DAC)获得模拟信号输出[3]。

一个基本的DDS系统由基准时钟fclk、相位累加器、相位/幅值查找表(ROM)、数模转换器(DAC)及低通滤波器(LPF)组成,如图1所示。

工作原理:预先在ROM中存入所需波形的幅度编码,每来一个时钟信号,N位的相位累加器将频率控制字K累加,同时累加器输出序列的高M位去寻址相位/幅值查找表,得到一系列离散的幅度编码(Y位)。

该幅码经数模转换后得到模拟的阶梯电压,再经低通滤波器平滑后,就可得到所需要的波形信号。

DDS的输出信号频率fout=K·fclk/2N,频率分辨率为Δfout=foutmin/2N,实际最高输出频率取foutmax=fclk×40%,相对带宽为foutmax/foutmin=2N×40%。

直接数字频率合成技术及其设计方案

直接数字 频率合成技 术( DDS 最初是在 ) 1 7 由美 国学者 J T e y等人提出的 , 91 .i me 它是 继直接 频率合成和 间接 频率 合成之后 , 随着数 字集成 电路和微电子技 术的迅速发展起来的第 三 代 频 率 合 成技 术 。 由于 它 在 频率 转 换 时 间、相 位连续性等方面 的优 点 , 现在 已经广泛 应 用 干 通 信 、雷 达 、 电子 战 等 设备 中 。

3实现 D S O 的两种技术方案

3 1采用高性能 D S 片的解决方案 . D芯

随着徽电子技 术和集成 电路技术的飞速发 展 , 前市场上有不少 l能优 良的D S 目 生 D 产品 , 生 产 D S芯片的公 司主要有 Q ac mm、AD、 D ul o S i g和 Sa fr 公司。其 中 AD公司的 ce t tnod等 DS D 系列产品以其较高的性价 比取得 了广泛 的 应用 。下面仅对 AD 公司的 A 9 4 D9 5 芯片做 简 单 介绍 。 A 9 5 是采用先进的 D S D 94 D 技术开发 的高 集成度的 D S器件 。它 内置高速 、高性能 D D / A 转换器及超高速 比较 器 , 可作为数字 编程 控 制的频率合成 器 , 能产生 2 0 0 MHz 的模 拟正 弦 波 。AD 9 4内含 12 2 态 RAM , 95 0 4X3 静 利 用该 RA 可实现高速调制 , 支持几种扫频 M 并 模式 。A 9 5 可提供 自定义的线性扫频操作 D 94 模式 , 通过 AD 94的串行 IO 口输入控制字 95 / 可实现快速 变频 并且具有 良好的频率分辨率 。 其 应 用范 围包括 灵敏频 率合 成器 、可 编程时 钟 发生器、雷达和扫描 系统的 F 调制源以及 M 测试和测量装置等 。AD 94 内部结构如 图 95 的 2 所示 , 其主要特性 : 内置 4 0 P 时钟 ;内含 0 MS s l 位 DA 相位 、幅度可编程 ;2 4 C; 3 位频率转换 字; 可用串行 I /O控制 ; 内置超高速模拟 比较 器可 自 动线性和非线性扫频内部集成有 12 04x 3 2位 RAM ; 采用 1 8 . V电源供电 ; 4 0倍倍 可 2 频; 支持大多数数字输入 中的 5 V输 入电平 ; 可 实现 多片 同步 。 3 2基于 FG . P A技术实现 D S D 的方案 D DS技术 的实现依赖 干高速 、高性能的 数 字器件 。随 着 电子技 术和 大规模 集成 电路 的发展 , 一种新型的数字器件—— F G P A得到 了飞速 的发展 。 它不仅具 有 很高 的速度 和可 靠性 , 而且具有用户可重复编程的特点 , 它的时 钟频率 已达 几百 兆赫兹 , 常适 合干实现 D S 非 D 的数字部分。 Xni il x公司是最大的 F GA/C L P P D生产商 之 一 , 多年 来 一 直 占据 行 业 领 先 的 地 位 。 X ni F G / P D具 有高性 能、高集成 il x的 P A C L 度和 高性价 比的优 点, 而且 它还 提供 了功能全 面的开发工具和丰富的 I 、宏功能 等。IE P核 S

实现直接数字频率合成器的种技术方案

实现直接数字频率合成器的种技术方案数字频率合成器是指一种非常重要的电子技术设备,其可以将高精度的数字信号转化为高质量的模拟信号,并通过模拟电路将这些信号输出,使得它们可以被人类感知。

实现直接数字频率合成器的技术方案有很多,本文将会详细介绍其中几种方案。

首先,最基本的方案是采用数字锁相环(,简称PLL)来实现直接数字频率合成器。

PLL技术已经被广泛应用于数字电路中,不仅可以实现同步,还可以通过比较、过滤和放大的方式将输入信号与参照信号进行比较,从而实现频率合成。

在此方法中,数字信号由一个ARB(任意波形发生器)产生,然后通过一个分频器进行分频,得到一个低频数字信号。

然后,这个低频数字信号以作为输入信号,通过两个锁相环(一个主锁相环,一个辅助锁相环)进行比较和过滤,最终输出高质量的数字信号。

这种方案非常简单,低成本、功耗低,适用于低频合成,但缺点是精度较低。

第二种方案是数字信号处理器(DSP)。

为了实现更高精度和更高的频率合成,可以采用DSP来实现。

首先,数字信号由一个ARB产生,并通过高速ADC进行采样。

然后,DSP通过数字滤波器等技术将这些数字信号进行处理,最终输出精度高、频率高的数字信号。

这种方案的优点是可以实现高精度、高频率的数字信号合成,但缺点是复杂度高、功耗大。

第三种方案是FPGA(现场可编程门阵列)。

FPGA相当于一个可编程的芯片,在硬件上实现数字信号处理和频率合成这两个功能。

这种方案的优点是高度灵活、可修改、功耗低,可实现多路复用,缺点是工程量大、难度较高。

总的来说,实现直接数字频率合成器的技术方案有很多,具体的方案应根据具体的应用场景和需要来确定。

如果需要实现低成本、低功耗的低频率合成,则可以采用PLL技术的方案。

如果需要实现高精度、高频率的数字信号合成,则可以采用DSP的方案。

如果需要更高的灵活性和可修改性,则可以采用FPGA的方案。

基于VHDL的直接数字频率合成器设计与实现

基于VHDL的直接数字频率合成器设计与实现作者:赵林军来源:《现代电子技术》2008年第17期摘要:从直接数字频率合成器(DDS)的基本原理出发,详细讨论了相位量化字长对DDS性能的影响,并给出了相位控制字与振幅控制字长度与量化信噪比的关系。

结合相位量化字长为24 b、振幅量化字长为10 b的正弦波DDS设计过程,给出了查表法实现的一个DDS设计实例。

文中所附代码均通过Max+Plus Ⅱ编译通过,可直接应用,同时,指出了改进查表法实现的DDS性能的几个基本途径。

关键词:DDS;VHDL;Max+Plus Ⅱ;流水线中图分类号:TN391.9 文献标识码:B 文章编号:1004373X(2008)1709603Design and Realization of Direct Digital Frequency Synthesizer Based on VHDLZHAO Linjun1,2(1.Xidian University,Xi′an,710071,China;2.Shaanxi U niversity ofTechnology,Hanzhong,723003,China)Abstract:From the principle of DDS,the quantization word length to DDS performance influence is discussed,and the relations of quantification signal-to-noise ratio to phase word length and amplitude word length is given.A detailed DDS design example,which phase quantization word length is 24 b and amplitude quantification word length is 10 b.Finally,the essential way to improve the DDS performance is pointed out.Keywords:DDS;VHDL;Max+Plus Ⅱ;pipeline20世纪60年代末,伴随数字集成电路与微电子技术的发展出现了直接数字频率合成器(DDS),它与传统的频率合成技术相比较,具有极高的频率分辨率与稳定度、转换时间短、输出信号的频率、相位、幅度可控等诸多优点,易于实现调频、调相、调幅等多种信号,因而得到广泛应用。

直接数字式频率合成器设计

大 众 科 技

DA ZHO NG KE J

No 6, 0 0 . 2 1

( muai l N .3 ) Cu lt ey o1 0 v

直 接 数 字 式 频 率 合成 器 设 计

i本 君

( 电子科技 大学 电子工程 学院 ,四川 成都 6 0 5 1 04)

【 摘 要 】直 接 数 字频 率合 成 ( ) 上 世 纪 7 代 初 提 出的 一 种 新 的 频 率 合 成 技 术 ,其 数 字 结 构 满足 了现 代 电 子 系统 的 DDs是 0年 许 多要 求 。因而得 到 了迅 速 地 发 展 。 文 基 于 A tr 公 司的 Cyln E 1 Q20 论 l a e c e P C6 4 ,完 成 了一 个 直 接 数 字 频 率 合 成 器的 硬 件 电路 , o 并 给 出其 电路 原 理 图 。 【 键 词 】 直接 数 字频 率 合 成 ;F GA;硬 件 关 P 【 中图 分 类 号 】T 4 . N7 21. 【 献 标 识 码 】A 文 【 章编 号 】 10 - 1 1 000 — 0 1 0 文 0 8 15 ( 1)6 0 4 - 2 2

( )直接 数 字频 率 合成 器原 理简 介 一

直 接 数 字 频 率 合 成 技 术 (ie t i ia F e u n y D r c D g t l r q e c S n h s s 即 D F ,一 般 简 称 D S , 是 从 相 位 概 念 出发 直 y te i , DS D) 接 合 成 所 需 要 波 形 的一 种 新 的 频 率 合 成 技 术 。一 个 直 接 数 字 频 率 合 成 器 由相 位 累 加 器 、加 法 器 、波 形存 储 RM / O 、D A转 换

基于Verilog语言的DDS设计与仿真

基于Verilog语言的DDS设计与仿真一、本文概述随着数字信号处理技术的快速发展,直接数字频率合成器(DDS)在现代通信、雷达、电子对抗等领域的应用越来越广泛。

DDS技术以其高精度、高速度、高稳定性等优点,成为了现代电子设备中实现频率合成的首选方法。

Verilog语言作为一种高效、灵活的硬件描述语言,为DDS的设计与实现提供了强大的支持。

本文旨在探讨基于Verilog语言的DDS设计与仿真方法。

我们将简要介绍DDS的基本原理和关键技术,包括相位累加器、波形存储器、D/A转换器等核心组件的作用与实现方式。

我们将详细阐述如何使用Verilog语言实现DDS的各个模块,包括相位累加器、波形存储器等关键部分的设计思路和代码实现。

我们将通过仿真实验验证设计的正确性,分析DDS的性能指标,如频率分辨率、相位连续性等,并探讨优化设计的方法。

通过本文的研究,读者可以深入了解DDS的设计原理和实现方法,掌握基于Verilog语言的DDS设计与仿真技术,为实际应用中的DDS 设计提供参考和借鉴。

本文的研究成果也可以为其他数字信号处理系统的设计和实现提供有益的启示和借鉴。

二、DDS基本原理直接数字频率合成(Direct Digital Synthesizer,简称DDS)是一种先进的频率合成技术,它使用数字信号处理技术生成所需频率的模拟信号。

DDS主要由相位累加器、正弦查找表(ROM)、D/A转换器和低通滤波器(LPF)组成。

DDS的基本工作原理是:在相位累加器中,每一步都会将频率控制字(Frequency Control Word,FCW)与相位寄存器中的值相加,生成新的相位值。

这个相位值随后被用作查找表(通常是正弦查找表)的地址,从而得到对应相位值的正弦波幅度。

查找表输出的数字信号然后被D/A转换器转换为模拟信号。

通过低通滤波器滤除高频分量,得到平滑的模拟正弦波。

DDS的频率分辨率和频率转换时间主要由查找表的大小和相位累加器的位数决定。

基于FPGA的直接数字频率合成器的设计和实现

能够提 供 高达 20 5 MHz的 双 向 IO 功 能 , 全 支 持 / 完

3 MHz 6 MHz的 P I 部 总线 标 准 。 3 和 6 C 局 快速 连 续式 延 时 可 预测 具

的 快 速 通 道 互 连 ( a tT ak ; 提 供 实 现 快 速 加 法 F s r c ) 能 器 、 数 器 、 法器 和 比较 器 等 算术 功 能 的专 用 进位 链 计 乘 和 实 现 高速 多 扇入 逻辑 功 能 的专 用级 连链 。

西安交通大孥电子物理与器件 国家重点实验 室 ( 西安 704) 109

周俊峰 陈 涛

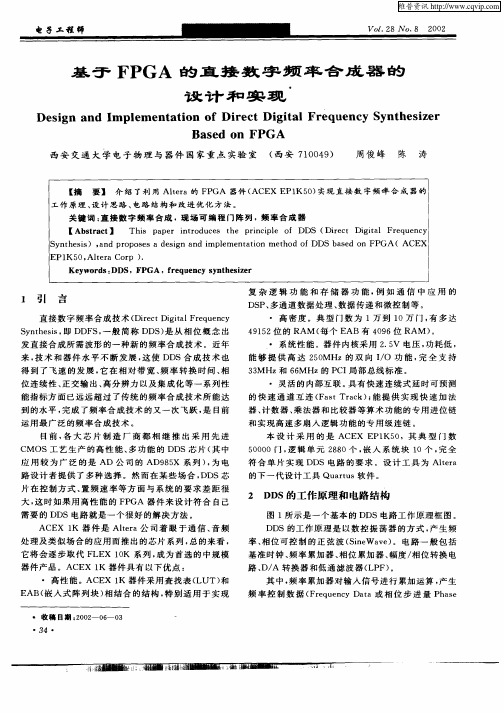

【 摘 要 】 介 绍 了 利 用 Al r t a的 F GA 器 件 ( E P K5 ) e P AC X E 1 0 实现 直 接 数 字 频 率 合 成 器 的 工作 原 理 、 计 思路 、 路 结 构 和 改进优 化 方 法 。 设 电

路 设计 者 提供 了多 种 选 择 。然 而 在 某 些 场 合 , DS芯 D

片 在 控 制 方 式 、 频 速 率 等方 面 与 系 统 的 要 求 差 距 很 置 大 , 时 如 果用 高 性 能 的 F GA 器 件来 设 计 符 合 自己 这 P 需要 的 DD S电路 就 是一 个 很 好 的解 决 方法 。 AC X 1 器 件 是 Al r E K t a公 司 着 眼 于 通 信 、 频 e 音

路 、 A 转换 器 和低 通 滤波 器 ( P 。 D/ L F)

处理 及 类 似场 合 的应用 而 推 出 的芯 片 系列 , 的来 看 , 总

它将 会 逐 步 取 代 F E 0 系 列 , 为 首选 的 中规 模 L X 1K 成 器件 产 品 。AC X 1 器 件具 有 以下优 点 : E K

DDS_直接数字频率合成器

南京理工大学直接数字频率合成器实验报告作者: 学号:学院(系):专业:指导老师:实验日期:2013年11月直接数字频率合成器(DDS)摘要本次课程设计的主要目的是学习使用FPGA设计直接数字频率合成器(DDS)。

实验的主要容是使用DDS的方法设计一个具有清零、使能频率相位控制、输出多种波形等功能任意频率的信号发生器,在设计之余,还完成了ROM空间的节省、提高等设计,并设计了一个基于DDS的AM调制电路。

利用Quartus II完成设计、仿真等工作,并下载至smart SOPC实验平台进行硬件测试,通过示波器观察输出信号波形。

实验结果与理论值相符,证明了DDS技术是一项非常实用的技术,它可以广泛应用于数字通信系统。

关键词:DDS ROM 正弦波AM调制AbstractThe main purpose of this curriculum design is encouraging us to learn to design a direct digital frequency synthesizer by using FPGA. The report mainly talks about how to design a direct digital frequency synthesizer with the function of resetting, frequency and phase controlling , multiple waves output . In addition, I also complete the design of ROM space saving ,and I design an AM modeling circuit based on DDS . The design and simulation work is completed with the help of QuartusII. The final system circuit is downloaded to the smart SOPC platform to undergo hardware test. And the output wave can be seen through oscilloscope. The experiment result is close to the theoretical result. DDS is proved to be a quite useful technology which can be widely applied in digital communication system.Keywords:Direct digital synthesizer ROM Sine wave AM module目录一、实验目的 (1)二、实验容和设计要求 (1)2.1实验容 (1)2.2设计要求 (1)三、直接频率合成器(DDS) (2)3.1实验原理 (2)3.2脉冲发生电路 (3)3.3消颤电路 (4)3.4频率和相位调节电路 (5)3.5累加器 (6)3.6波形存储器(ROM表)设计 (8)3.7测频电路 (11)3.8显示电路 (13)3.9总电路图(1) (14)四、节省ROM空间 (17)4.1设计思路 (17)4.2正弦波的计算 (18)4.3三角波计算 (20)4.4锯齿波计算 (20)4.5方波计算 (22)4.6四种计算波形合并 (22)4.7总电路图(2) (23)五、基于DDS的AM调制器的设计 (24)5.1AM调制原理 (24)5.2调制信号与载波信号的产生 (25)5.3波形存储器(ROM表)设计 (29)5.4调制度的确立 (30)5.5加法器与乘法器 (30)5.6显示电路 (30)5.7AM调制电路总图 (31)六、节省电路的改进 (32)七、实验中遇到的问题及解决办法 (33)八、实验收获和感受 (33)九、致 (34)十、参考文献 (34)十一、附录 (35)一、实验目的1.学习使用QuartusII软件做复杂逻辑电路的设计。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

p o rm o lx c d . u tb sn h P b i e , e in r o l n etk h e eo me t r t h r g a c mpe o e J s y u ig teDS ul r d sg e sc udu d ra et ed v lp n d wo kwi t e h

第 3卷 第 6 3 期

21 0 1年 l 月 2

探 测 与 控 制 学 报

J u n l fD tc in & C n r l o r a ee t o o o to

Vo. 3No 6 I3 .

De . 01 c2 1

基 于工具 软件 的直 接数 字 频 率 合成 器 设 计 方 法

a v n a e fs r n t r c in a d smp e u a e d a t g s o to g i e a t n i l s g . n o

2 Xi n I s i t fElc r m e h n c l n o ma in Te h oo y。 ' 1 0 5 Ch n ) . ' n t u e o e to c a ia f r t c n l g Xi n 7 0 6 , ia a t I o a

Ab ta t De ino sr c : s f g DDS sg a o reb sdo P b i e s al s st emeh do o iig h r waed — in l u c a e nDS ul ru u l u e h t o f mbnn a d r e s d y c

卢一拮h , 蒙美海 张 峰 张 珂 , ,

(. 电动态 控制 重点 实验 室 , 1机 陕西 西 安 70 6 ;. 安机 电信 息研 究所 , 10 52 西 陕西 西 安 7 06 ) 105

摘 要 : 利用 F G P A设计直接数字频率合成器( D )通常是采用硬件描述语言与原理图输入相结合的方法。 D S,

界面下的建模 、 真和系统集成 。设计实 例表 明: 仿 通过 系统 参数 的设置 可方便地 对信号 的频 率及相 位进行 修

改, 继而缩短 了研制周期 , D 为 DS设计 提供 了一种新 的设计方法 。该方法无需编制复 杂的程序代码 , 利用 D P S B i e 软件友好 的图形开发界面就可进行系统设计 , ul r d 且开发 环境与 Quru I软件交互 性强 , atsI 便于修 改, 具有

s r t n ln u g t c e tce ty I sv r a df rd s n r , ea s h ymu tfm ia t ad r c i i a g a ewih sh ma i n r . ti ey h r o ei es b cu et e s a l rwi h r wa e p o g i h fu d t n a dh r wa ed sg a g a e To s ligt i p o lm ,hsp p rp ee tdan w ein meh do o n ai n ad r e in ln u g . ovn hs rbe ti a e r sn e e d sg to f o d rc ii l rq e c y te i DDS b s dO P b i e. emeh dc ud f iht ed s n o h d e ie t gt e u n y s n h ss( d a f ) a e DDS ul r Th to o l i s h e i ft emo l d n g i P ule , n o peemo eig, i lto s se n e rto n Smu ik Thsmeh o l ra l nDS b i r a d c m lt d l d n smuain, y tm itg ain i i l . i n t o c ud g ety d s o tn t ed sg e id b df ig sg a rq e c h o g y tm aa trs tig a d i dd n tn e o h re h ein p ro ymo i n in l e u n yt ru hs se p rmee et , n i o e dt y f n t

对 设计者的硬件基础要求较高 , 且要求熟悉硬件 电路设计语 言 , 性较强 。提 出一种 基于 D PB i e 的直 综合 S udr l

接数字频率合成 的设计方法 , D PB i e 软件中完 成 F GA D S的模型设计 , Smuik软件中完成图形 在 S ul r d P D 在 i l n

良好的可重配性 。

关键 词 : 直接数字频率合成( D )现场可编程门阵列(P A ; S ul r D S; F G )D PB ie 软件 d

ቤተ መጻሕፍቲ ባይዱ

中图分类号 :N 1.2 文献 标志 码 : 文章 编号 :0819 (010- 4- T 917 A 10—1421 ) 0 20 60 4

FPGA DDS De in Ba e n DS Bu l e sg s d o P id r

L z e , ENG eh i, H ANG e g , ANG U Yih M M ia Z F n ZH Ke

( . ce c n c n lg n Elcrm eh nc l n mi C to a o ao y Xin7 0 6 Chn ; 1 S in ea dTeh oo yo e to c a i a Dy a c onr lL b r tr , ' 1 0 5, ia a