DSP第五章

DSP原理与应用2011-第五章TMS320F28335片(精)

DSP 原理与应用The Technology & Applications of DSPs第五章: TMS320F28335片内外设北京交通大学电气工程学院夏明超郝瑞祥万庆祝***************.cn**************.cn**************.cn:TMS320F28335第五讲: TMS320F28335片内外设教学目标:掌握TMS320F28335内核结构,例如A/D转换、串行通信接口、串行外设接口。

外设接重点:TMS320F28335A/DCS308335内部/C 的正确使用,串行通信接口应用。

难点:TMS320F28335的ADC 寄存器操作和串行通信寄存器操作。

教学内容分两部分51§5.1:TMS320F28335内模拟/数字转换§5.2 :TMS320F28335系列串行通信接口SCI 和Modbus 协议介绍DSP 原理与应用2DSP原理与应用3 ADC 有关引脚§5.1 TMS320F28335内模拟/数字转换§5.1 .1Features and functions of ADC module:◆core with built-in dual sample-and-hold◆Simultaneous sampling or sequential sampling modesp g q p g ◆Analog input: ◆Fast conversion time runs at ADC clock orFast conversion time runs at , ADC clock, or 6.25 MSPSmultiplexed inputs◆, multiplexed inputs◆capability provides up to 16 " t i " i i l i E h i "autoconversions" in a single session. Each conversioncan be to select any 1 of 16 input channels.DSP 原理与应用4Sequencer can be operated as two independent 8-state ◆Sequencer can be operated as two independent 8-state sequencers or as one large 16-state sequencer (i.e., two cascaded 8-state sequencerstwo cascaded 8state sequencers.◆(individually addressable to store conversion values store conversion valuesA/DC digital value:DSP 原理与应用2012年9月3日5◆for the start-of-conversion sequence–S/W -software immediate start–ePWM 1-6–GPIO XINT2◆allows interrupt request on every end-of-sequence (EOS or every other EOSy q ( y◆Sequencer can operate in mode, allowing multiple "time-sequenced triggers" to synchronize p q gg yconversions.Sample-and-hold (S/Hacquisition time window has ◆Sample and hold (S/H acquisition time window has separateA/DC模块框图(Block diagram of A/DC Module)§5.1. 2ADC 有关的寄存器控制寄存器通道顺序选择寄存器结果寄存器ADC有关的寄存器(序)控制寄存器状态寄存器参考电压选择寄存器偏移电压调整寄存器§5.1.3 ADC操作模式1 顺序采样模式(Sequential Sampling Mode)根据采样模式划分,包括顺序采样和同步采样2同步采样模式(Simultaneous Sampling Mode)DSP 原理与应用2012年9月3日11根据转换模式划分,包括:级联模式转换和和双序列模式转换1)级联模式转换DSP 原理与应用2012年9月3日122)双序列模式转换DSP 原理与应用2012年9月3日13 单序列模式和级联模式对比DSP 原理与应用2012年9月3日14§5.1.4 ADC电压参考默为使用内部电压参考也以使用外部电压参考允许值为●默认为使用内部电压参考,也可以使用外部电压参考,允许值为2.048V ,1.5V 和1.024V 。

DSP原理及应用第五章

4 MBytes SDRAM

10

PC

C64x 入门套件: C6416 DSK

X

11

第5章 汇编语言程序开发工具

2. ’C54x的开发工具

(2)代码调试工具:

可扩展的开发系统仿真器(XDS510):可用来 进行系统级的集成调试,是进行DSP芯片软硬件开发 的最佳工具。 评价模块EVM板:是一种低成本的开发板,可 进行DSP芯片评价、性能评估和有限的系统调试。

X

29

第5章 汇编语言程序开发工具

5.4 链接器的使用

链接器的主要任务是根据链接命令文件(.cmd), 将一个或多个COFF目标文件链接起来,生成存储器映 像文件(.map)和可执行的输出文件(.out)。

X

12

C6701 评估板

X

13

第5章 汇编语言程序开发工具

5.2 汇编语言程序的编辑、汇编和链接过程

汇编语言源程序可以在任何一种文本编辑器中进行

。如笔记本、WORD、EDIT、TC等。

当汇编语言源程序编写完成后,还必须经过汇编和

链接后才能运行。

X

14

第5章 汇编语言程序开发工具

5.2 汇编语言程序的编辑、汇编和链接过程

① 将一个或多个COFF目标文件中的各种段作为

链接器的输入段,经链接后在一个执行的COFF输出

模块中建立各个输出段;

② 在程序装入时对其重新定位,为各个输出段

选定存储器地址。

X

23

第5章 汇编语言程序开发工具

5.3.3 链接器对段的处理 链接器有2条伪指令支持上述任务:

● MEMORY伪指令——用来定义目标系统的存储 器配置空间,包括对存储器各部分命名,以及规定 它们的起始地址和长度。 ● SECTIONS伪指令——用来指定链接器将输入 段组合成输出段方式,以及输出段在存储器中的位 置,也可用于指定子段。 若未使用伪指令,则链接器将使用目标处理器 默认的方法将段放入存储空间。

DSP5第五章IIRDF的设计方法

其中:Ha(s)是模拟滤波器的系统函数。 • 假 设p1, z1为Ha(s) 的一个零点和一个极点,则-p1, -z1

必为Ha(-s)的一个零点和极点,Ha(s)、Ha(-s)的零极点 成象限对称分布。所以必然有如下形式: zpA 11 2 ( * ) *H a --( zps 11) H a ( s )s j k 2 ( ( 2 2 z p 1 2 1 ) 2 ) 2 ( 2 ( z 2 2 p ) 2 2 ) ( ( 2 2 z N 2 p ) m 2 )

1、低通滤波器的性能指标

|H(ejw)|或|H(f)

1

Ap

1-δ1

δ2 fp fs wp ws

δ1:通带的容限

δ2:阻带容限

通带截止频率:fp(wp)又称 为通带上限频率。

通带衰减:Ap

As f

阻带截止频率:fp(ws)又称 阻带下限截止频率。

w

阻带衰减:As

2、高通滤波器的性能指标

|H(ejw)|或|H(f) Ap 1

• 根 据 给 定 设 计 要 求, 把 数 字 滤 波 器的 性能指标变成模拟滤波器的 性 能 指 标。

2、模拟滤波器设计

• 设计出符合要求的模拟滤波器的 系 统 函 数。可以选择多种类型的滤波器。 如Butterworth,Chebyshev,Elliptic,Bessel等。

3、 映 射 实 现

二、IIR DF频率特性

• 它是由三个参量来表征: 1.幅度平方响应 2.相位响应 3.群延时

第五章 DSP系统设计

随着大规模集成芯片和可编程逻辑芯片的发展,使硬

件原理设计的难度得以降低,但它依然是DSP系统集成 中关键的一步。原理图设计的成功与否是DSP系统能否

正常工作的最重要的一个因素。

16/39

第五章

DSP系统设计

5.1 系统设计— DSP系统硬件设计

第四步:PCB设计

PCB图的设计要求DSP系统的设计人员既要熟悉系

流之间留有一定余量,因为峰值电流会更大,余量至少

是20%。 现有的电源模块分AC/DC型和DC/DC型。DSP设计中常用 DC/DC型。 DC/DC型中又分开关型和线性低压降型(LDO)。开关型效

率高,但体积大、纹波大。线性LDO型体积小巧,但效率

低,其效率相当于输出电压和输入电压之比,例如5V转 1.8V的效率仅32%,只适用于电流较小的场合。

的电流消耗。 以AD6P21060/ADSP 21062为例,其进行FFT运算时,需 要的电源电流最大,这一峰值电流约是700 mA,但这是 在最“坏”情况下,真正的电流消耗比这小很多。

19/39

第五章

DSP系统设计

5.2 电路设计— 电源设计

因此在设计电源时,必须考虑在电源电流和实际需用电

出现问题时,一般采用修改软件的方法,如果软件修改

无法解决问题,则必须调整硬件,这时问题就严重了。

18/39

第五章

DSP系统设计

5.2 电路设计— 电源设计

DSP使用的电源是数字电源,这些电源必须满足一定要 求,一般要求纹波不超过10%;还应准确估算出DSP及

其外围器件的功耗。DSP数据手册给出了各种情况下DSP

电路设计时有必要采用多层印刷板,一般建议其中 一层是地层。优点:减少干扰;布线时省去了大量 器件管脚接地的工作量。注意:现在DSP等元件广泛 采用表贴封装,在器件布线时,将尽可能多的网络

DSP原理与应用2011-第五章 TMS320F28335片内外设_ad转换SCI

掌握TMS320F28335内核结构,例如A/D转换、串行通信接口、 串行 外设接口。

重点:

TMS320F28335内部A/DC的正确使用,串行通信接口应用。

难点:

TMS320F28335的ADC寄存器操作和串行通信寄存器操作。

教学内容分两部分

§5.1:TMS320F28335内模拟/数字转换 §5.2 :TMS320F28335系列串行通信接口SCI和Modbus协议介绍

7

§5.1 .2 ADC有关的寄存器

控制寄存器

通道顺序选 择寄存器

结 果 寄 存 器

DSP原理与应用

2012年9月3日

8

ADC有关的寄存器(序)

控制寄存器 状态寄存器

参考电压选择寄存器 偏移电压调整寄存器

DSP原理与应用

2012年9月3日

9

§5.1.3 ADC 操作模式

根据采样模式划分,包括顺序采样和同步采样 1) 顺序采样模式(Sequential Sampling Mode)

DSP原理与应用

2012年9月3日

10

2) 同步采样模式(Simultaneous Sampling Mode)

DSP原理与应用

2012年9月3日

11

根据转换模式划分,包括: 级联模式转换和和双序列模式转换 1) 级联模式转换

DSP原理与应用

2012年9月3日

12

2) 双序列模式转换

DSP原理与应用

DSP原理与应用

4

Sequencer can be operated as two independent 8-state sequencers or as one large 16-state sequencer (i.e., two cascaded 8-state sequencers).

DSP-5

IIR的并联型

将因式分解的H(Z)展开成部分分式的形式,就可 得到IIR的并联型滤波器。

H ( z) H1 ( z) H2 ( z) H k ( z)

Hi(z)通常为一阶网络和二阶网络,网络系统均 为实数。 0i 1i z 1 Hi ( z) 1 a1i z 1 a2i z 2 输出Y(z)表示为

IIR 直接型

IIR 直接I型和IIR 直接II型,之所以称为“直接 型”,是因为它们的结构是直接从系统函数中得 到的,没有对系统函数做任何的重排。

遗憾的是:这样的结构对参数量化十分敏感。当 N较大时,数字滤波器会因参数量化(有限字长) 的微小变化,导致系统的零、极点位置出现重大 的变化。故通常不推荐使用在实际应用中。

引言

时域离散系统或网络可以用差分方程、单 位脉冲响应以及系统函数进行描述。

y (n ) bi x (n i ) ai y (n i )

i 0 i 1 M N

系统函数H(z)为

Y ( z) H ( z) X ( z)

M

1 ai z i

i 1

i 0 N

因为含有输出延时部分,它是反馈网络。IIR直接I型结 构 由下图可以看出,该网络是两部分的级联。第一网络对 应系统函数的分子,全零点系统;第二网络对应与系统 函数的分母,意味着这是系统函数的全极点系统。

IIR 直接 I型

该结构需要N+M级延时单元。

直接I型特点:直观、速度慢、不经济(需要N+M) 个延时器

b c

L L

k 流图特征余子式; 中除去与第k个前向通道接触的回

路后的剩余部分;

dsp-第5章

IIR_DF网络结构小结:

我们这里考虑的系统函数H(z)为标准形式:

y (n) ai x(n i ) bi y (n i )

i 0 i 1

N

N

H ( z)

i 1 N i 1

N

ai z

i

1 bi z

i

若

H ( z)

i 1

N

ai z i

N

b0 bi z i

i 1 i 0 N

上式为I I R滤波器形式,但当{ a i}=0时就是一个FIR滤波器。

对于这样一个系统,也可用差分方程来表示:

y (n) bi x(n i ) ai y (n i )

i 0 i 1

N

N

5.2 数字滤波器的结构

一、数字网络的信号流图表示 差分方程中数字滤波器的基本操作:①加法②乘法③延迟。 为了表示简单,通常用信号流图来表示其运算结构。对于加 法、乘法及延迟这三种基本运算。

y(n) a0 x(n) a1 x(n 1) b1 y(n 1)

两个变量相加,用一个圆点表示(称为网络节点) 只有输出支路的节点称为输入节点或源点; 只有输入支路的节点称为输出节点或阱点; 既有输入支路又有输出支路的节点叫做混合节点。 通路是指从源点到阱点之间沿着箭头方向的连续的 一串支路,通路的增益是该通路上各支路增益的乘 积。 回路是指从一个节点出发沿着支路箭头方向到达同 一个节点的闭合通路,它象征着系统中的反馈回路。 组成回路的所有支路增益的乘积通常叫做回路增益。

j

) 1 e

N ) 2 sin( ) 2

A类线性相位即h(n)为偶对称 h(n)=h(N-1-n) B类线性相位即h(n)为奇对称 h(n)=-h(N-1-n)

DSP第五章

⑬I/O端口寻址(PA) :

用一个符号或一个常数来确定外部I/O口地址。 例如,把一个数从端口地址为FIFO的I/O口 中的一个字复制到AR5指向的数据存储器单元: PORTR FIFO,*AR5 FIFO所标注的地址为端口地址。

⑭ *(lk)寻址:

用一个符号或一个常数来确定数据存储器中 的一个地址,这种寻址的语法允许所有使用 Smem寻址的指令去访问数据空间的任意单元而 不改变数据页指针(DP)的值,也不用对AR进行 初始化。 例如,把地址为BUFFER的数据单元中的数 装到累加器A: LD *(BUFFER),A 这里的BUFFER是一个16位的符号常数。

DST B,*AR3表 示 把 源 累 加 器 B 中 的 内 容 00 4AB2 CC22存放到AR3寄存器所指向的长数据存 储器单元中,然后AR3寄存器的内容减2。 本例中,数据存储器单元的地址为0101, 第1个字处在奇地址0101h,故第2个字就 处在前一个(较低的)地址0100h。执行后, 第 1 个 字 0101h 的 内 容 为 4AB2 , 第 2 个 字 0100h的内容为CC22。

ห้องสมุดไป่ตู้

在以SP为基准的直接寻址中,指 令寄存器中的7位dma作为一个正偏移 与SP相加得到有效有16位数据存储器地 址。 SP可指向存储器中的任意一个地 址。 dma可指向当前页中一个明确的单 元,从而允许访问存储器任意基地址中 连续128个字。

例: SSBX CPL 对状态寄存器ST1的CPL置位,CPL=1; LD @X1,A SP指针加X1形成的地址中的内容送累加器A; ADD @Y2,A SP指针加Y2形成的地址中的内容与累加器A中 的值相加。

例如指令: LD #93h,A 把立即数93h送入累加器A LD 93h,A 把地址为93h单元中的数装到累加器A, 而不是把93h送入累加器A。

DSP原理及应用第五章

STACK

table:

start:

;从程序存储器传送到数据存储器中

;从数据存储器传送到数据存储器中

end:

10

MEMORY { PAGE 0: EPROM : org = 0E000H len = 0100H VECS: org = 0FF80H len = 0004H PAGE 1: SPRAM : org = 0060H len = 0020H DARAM : org = 0080H len = 0100H } SECTIONS { .text :>EPROM PAGE 0 .data :>EPROM PAGE 0 .bss :>SPRAM PAGE 1 STK :>DARAM PAGE 1 .vectors:>VECS PAGE 0 }

16

特 点

对于Xmem和Ymem,只能用以下辅助寄存器及寻址方式:

辅助 寄存器 选择

Xar或Yar 00 01 10 11

操作码语 法 *ARx *ARx*ARx+ *ARx+0%

辅助寄存器 AR2 AR3 AR4 AR5

双数据存储器操作数寻址的类型

Xmod或 Ymod 00 01 10 11 功 能 说 明

第五章 汇编语言编程举例

第一节 汇编语言编程的基本方法

第三节

第四节

DSP在信号发生器上的应用

用DSP实现FIR滤波器

第五节

用DSP实现IIR滤波器

1

第一节 汇编语言编程的基本方法

1.堆栈的使用

要 点

1.压入数据时,堆栈从高地址向低地址 增长。 2.压栈时指针先减,SP-1,再压入数据; 3.出栈时,先弹出数据后,再SP+1。 4.如要用堆栈,必须先设置,后使用。

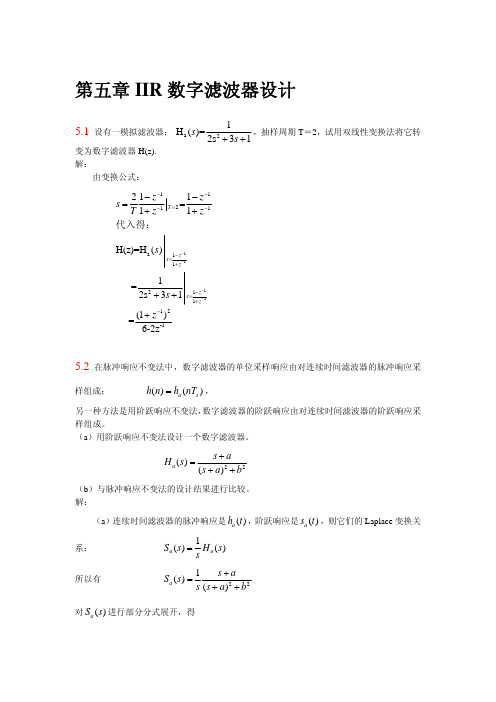

DSP第五章课后答案

(b)用脉冲响应不变法, 所以

H ( z)

1 e ( a jb )Ts z 1 1 e ( a jb )Ts z 1 1 cos(bTs )e aTs z 1 1 2 cos(bTs )e aTs z 1 e 2 aTs z 2

1 2

butterworth 低通滤波器阶次 N:

lg 100.301 1 / 101.5 1 1.941 N 2 lg 2 / 4.828

所以选 N=2 滤波器的截止频率 c

2.000

10

0.301

1

1/ 4

2

再查表可求得模拟滤波器的系统函数为

所以有

对 S a ( s ) 进行部分分式展开,得

Sa ( s)

由

1 a a jb a jb 2 2 2 2 2 s a b 2(a b )( s a jb) 2(a b 2 )( s a jb)

1 1 得 Ts 1 1 e z s 1 a a jb 1 a jb 1 S ( z) ( a jb )Ts 1 ( a jb )Ts 1 1 2 2 2 2 2 2 1 z a b 2(a b ) 1 e z 2(a b ) 1 e z

Ap

H z

i 1

N

1 e siT z 1

5.6

试用双线性变换法(T=1)设计一低通数字滤波器,并满足技术指标如下:

(1)通带和阻带都是频率的单调下降函数,而且没有起伏 (2)频率在 0.5 处的衰减为-3.01db (3)频率在 0.75 处的衰减至少为 15db。 解: 根据题意,显然要先设计一个原型 butterworth 低通滤波器。 (1) 利用 T=1 对技术要求频率先进行反畸变: 因为 wp 0.5 , ws 0.75 所以 p

DSP第五章 DSP的汇编指令

展和移位操作都以第31比特为准。

M40=1时,D单元按40位运算模式,因此累加器溢出,进位,符号扩

展和移位操作都以第39比特为准。

BCLR M40

; Clear M40

BSET M40

; Set M40

第五章 TMS320C55x系列DSP的汇编指令

2、累加器溢出状态(ACOVx)

当AC0~AC3寄存器溢出时,目的累加器的溢出状态位ACOV0~3被置1。 以下情况会清零ACOVx位

复位; CPU执行一个跳转,条件调用,条件返回或执行一条测试ACOVx的指令; 通过BCLR指令清除; 溢出位检测受ST1_55中的M40位影响,即:

第五章 TMS320C55x系列DSP的汇编指令

(3)内置并行指令与用户自定义并行指令的混合形式 在不引起资源冲突的情况下,将隐含并行的指令按用户自定义 方式与另一条指令并行执行。例:

MPY *AR0, *CDP, AC0 ;隐含的或内置的并行指令 :: MPY *AR1, *CDP, AC1 ||MOV #5, AR1

பைடு நூலகம்

在实际编程时,只要指令满足这三条基本规则,即可写成并行

方式,然后进行编译。如果编译有错,则可参照书上详细规则进 行检测。

第五章 TMS320C55x系列DSP的汇编指令 5.4 TMS320C55x DSP的汇编指令

TMS320C55x DSP的汇编指令按操作分为以下6类 算术运算指令 比特操作指令 一条指令的属性包括: 语法(Syntax) 执行的操作 操作数 相关的状态位 是否有并行使能位 长度(Size) 执行周期(Cycles) 在流水线(Pipeline)上的执行阶段 在哪个功能单元执行(Executed) 是否可以重复执行等

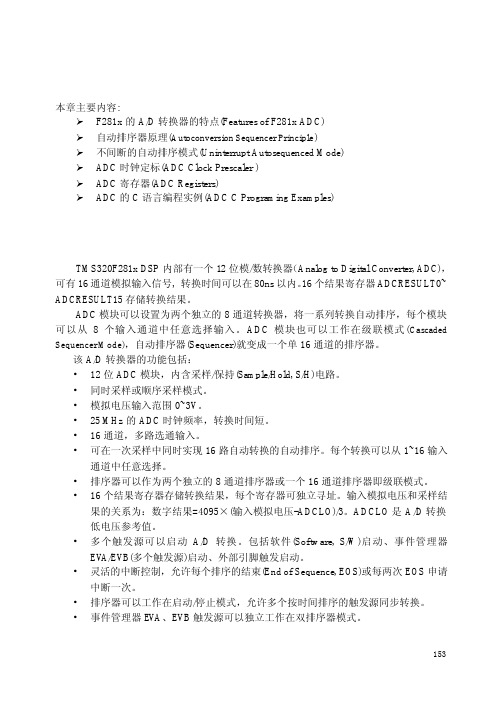

第5章DSP的AD转换器

第5章 DSP的A/D转换器 本章主要内容:Ø F281x的A/D转换器的特点(Features of F281x ADC)Ø 自动排序器原理(Autoconversion Sequencer Principle)Ø 不间断的自动排序模式(Uninterrupt Autosequenced Mode)Ø ADC时钟定标(ADC Clock Prescaler )Ø ADC寄存器(ADC Registers)Ø ADC的C语言编程实例(ADC C Programing Examples)5.1 F281x的A/D转换器的特点 TMS320F281x DSP内部有一个12位模/数转换器(Analog to Digital Converter, ADC),可有16通道模拟输入信号, 转换时间可以在80ns以内。

16个结果寄存器ADCRESULT0~ ADCRESULT15存储转换结果。

ADC模块可以设置为两个独立的8通道转换器,将一系列转换自动排序,每个模块可以从8个输入通道中任意选择输入。

ADC模块也可以工作在级联模式(Cascaded Sequencer Mode),自动排序器(Sequencer)就变成一个单16通道的排序器。

该A/D转换器的功能包括:•12位ADC模块,内含采样/保持(Sample/Hold, S/H)电路。

•同时采样或顺序采样模式。

•模拟电压输入范围0~3V。

•25 MHz的ADC时钟频率,转换时间短。

•16通道,多路选通输入。

•可在一次采样中同时实现16路自动转换的自动排序。

每个转换可以从1~16输入通道中任意选择。

•排序器可以作为两个独立的8通道排序器或一个16通道排序器即级联模式。

•16个结果寄存器存储转换结果,每个寄存器可独立寻址。

输入模拟电压和采样结果的关系为:数字结果=4095×(输入模拟电压-ADCLO)/3。

DSP第五章

说明:程序跳转到pma指定的地址,并根据指令修 改当前AR和ARP。Pma可以为符号或者数字。例 如: B 191, *+, AR1

(10)BACC 跳转到累加器指定的地址

语法: BACC

说明:程序跳转到累加器低16位所确定的地址。

例如:

(11)BANZ 辅助寄存器非0跳转

语法:

说明:如当前AR不为0,则程序跳转到pma指定的 地址,否则执行下一条指令。根据指令修改当前 AR和ARP。缺省时,当前AR减1。该指令常用来 控制循环体的执行,如要使循环体执行N次,则可 在循环体执行前将用于计数的AR初始化为N-1

(18)CALL 无条件调用

语法:

说明:首先将返回地址压入栈顶保存,然后将pma值赋给 PC实现子程序调用。根据要求修改ARP和当前AR值。例 如:

(19)CC 条件调用

语法:

说明:若条件满足,则将返回地址压入栈顶,把pma值赋 给PC实现子程序调用。若不满足则PC加2,按顺序执行 例如:

如果ACC小于或等于0 且进位位C=1,则调用 PGM191,否则按顺序执行。

MAR *, AR1 LT *+, AR2 ;AR1成为当前AR ;AR2成为当前AR

MPY *

4. 位反转寻址

位反转寻址主要用于FFT算法中,这种寻址方 式可以大大提高程序的执行速度和存储器的利用 效率。使用时,AR0存放的整数值为FFT点数的一 半,当前辅助寄存器AR指向存放数据的单元。位 反转寻址将AR0加到辅助寄存器中,地址以位反转 方式产生。也就是说,两者相加时,进位是从左 向右传递的,而不是通常加法中的从右到左。例 如,1010与1100的位反转相加结果为0001:

说明 当前AR包含数据存储器地址 访问完成后,当前AR+1

DSP完整课件第5章

退出

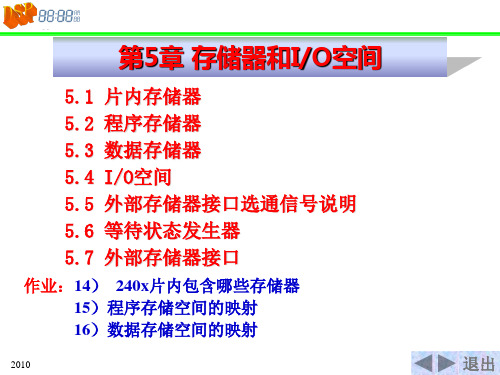

5.4 I/O空间 I/O空间

I/O空间都可以用IN和OUT指 I/O空间都可以用IN和OUT指 空间都可以用IN 令访问。 令访问。 执行IN或OUT指令时, 执行IN或OUT指令时,信 IN 指令时 将变成有效, 号 IS 将变成有效,因此可用 作为外围I/O I/O端口的 信号 IS 作为外围I/O端口的 片选信号。 片选信号。

(DON=1) 外部(DON=0 ) 0FFFh 外部 非法 1000h 1000h 7000h 外设映射寄存器 系 外设映射寄存器(系 统、WD、ADC等) 、 等 8000h 外部

DSP对数据存储器空间的寻址方式 DSP对数据存储器空间的寻址方式 有两种:一种寻址方式为全16位地址的 有两种:一种寻址方式为全16位地址的 寻址;另一种寻址为按页寻址的方式。 按页寻址的方式 寻址;另一种寻址为按页寻址的方式。 按页寻址时,DP(ST0.8 0) 0)为数据页指 按页寻址时,DP(ST0.8~0)为数据页指 其值为16位地址线的高9 16位地址线的高 针,其值为16位地址线的高9位,将64KB 的数据空间划分成512个数据页。 512个数据页 的数据空间划分成512个数据页。 每个数据页有128个字单元, 每个数据页有128个字单元,变量在 128个字单元 数据页中的具体位置是由指令中的偏移量 确定(对应16位地址中的低7 16位地址中的低 确定(对应16位地址中的低7位)。 寻址时首先找到变量的基地址(DP值 寻址时首先找到变量的基地址(DP值), (DP 然后再加上地址偏移量即可。 然后再加上地址偏移量即可。

2)CNF,决定片内DARAM(B0)是否映射到程序空间,=1映射; CNF,决定片内DARAM(B0)是否映射到程序空间,=1映射; 决定片内DARAM(B0)是否映射到程序空间 映射 PON,决定片内SARAM是否映射到程序存储空间 =1映射 决定片内SARAM是否映射到程序存储空间, 映射。 3)PON,决定片内SARAM是否映射到程序存储空间,=1映射。

DSP第五章3

修正频率抽样结构

将零极点移至半径为r的圆上:r 1

r N zN

)

1 N

N 1 Hr (k ) k0 1 rWNk z1

极点:

zk

j 2 k

re N

k 0,1,..., N 1

5.3 FIR数字滤波器的基本结构

FIR数字滤波器的特点:

系统函数:

N 1

H (z) h(n)zn n0

有N-1个零点分布于z平面 z=0处 是N-1阶极点

1)系统的单位抽样响应 h(n)有限长,设N点 2)系统函数H(z)在 z 0 处收敛,有限z平面只有

零点,全部极点在 z = 0 处(因果系统) 3)无输出到输入的反馈,一般为非递归型结构

四、快速卷积结构

五、线性相位FIR滤波器的结构

FIR滤波器单位抽样响应h(n)为实数,0 n N 1 且满足:

偶对称: h(n) h(N 1 n) 或奇对称: h(n) h(N 1 n) 即对称中心在 (N-1) / 2处 则这种FIR滤波器具有严格线性相位。

N为奇数时

z

)

k 0

1.子系统: Hc (z) 1 zN

在单位圆上有N个等间隔角度的零点:

j 2 k

zk e N k 0,1,..., N 1

频率响应:

Hc (e j ) 1 e jN

jN

e 2

jN e 2

jN

e 2

2

je

jN 2

sin

M

H (z)

Y (z) X (z)

bk zk

DSP课件第五章TMS320LF240x汇编指令系统

ZLVC ZLVC 两个4位字段,每位表示以下条件:

ACC=0---Z;ACC<0---L;溢出---V;进位---C

+1word 双字操作码的第2个字。包含16位常数。根据指令不同该

常数可能是长立即数、程序存储器地址、I/O端口或I/O映

射的寄存器地址。

2021/3/5

5

4.2 指令句法描述

例8:ADDS 6 例9:ADDS *

;设DP=5,则数据存储器地址为280h~2FFh, (ACC)+(数据存储器286h)→ ACC

2021/3/5

17

5、加法指令ADDT 句法: ADDT dma

ADDT ind[,ARn] 功能:将被寻址的数据存储器单元的内容左移0~15位后与累加器的内容相

2021/3/5

14

例6:ADDC DAT300 例7:ADDC *-,AR4 ;(设OVM=0),将当前AR指定的数据存储

单元的内容与累加器的内容及进位位相加 后送累加器,并将当前AR的内容减1,然 后将AR4指定为下次的辅助寄存器。

2021/3/5

15

4、加法指令ADDS 句法: ADDS dma

ADDC ind[,ARn] 功能:将被寻址的数据存储器单元的内容与累加器的内容及进位位相 加,

结果送至累加器。

操作: ①(PC)+1→PC; ② (ACC) +(数据存储器地址)+(C)→ ACC

状态位:影响C和OV位,受OVM状态位影响,不受SXM影响。若相加结果产 生进位,则C=1,否则C=0。

令要求修改当前辅助寄存器和ARP的内容. 操作: ①pma→PC (pma可以是符号地址或数值地址);

②按指令要求修改当前AR和ARP。 例17: B 16

DSP第五章 数字信号处理课件

,为N阶FIR系统的横向结构

, 时,为全极点IIR格型结构

(3) 上半部分对应全极点系统

下半部分对应全零点系统 按全极点系统的方法求出 而上半部分对下半部分有影响,故需求

令

为由

到

之间的系统函数

整个系统的系统函数

由

两边同次幂系数相等,得

解法一:

解法二 :

全极点IIR滤波器的系统函数

其中

表示M 阶全极点系统的第 i 个系数, 的关系

讨论与格型结构

全极点格型结构基本单元:

M=1

M=2

格型同全零点系数与

的递推关系完全一样。

3、零极点系统(IIR系统)的格型结构

在有限 z 平面 的IIR系统 上既有极点又有零点

(1) 当

差分方程:

需N+M个 延时单元

2、直接Ⅱ型(典范型)

只需实现N阶滤波器所需的最少的N个延时单元, 故称典范型。( )

直接型的共同缺点:

系数

, 对滤波器的性能控制作用不明显

极点对系数的变化过于灵敏,易出现不稳定或

较大误差

运算的累积误差较大

3、级联型

将系统函数按零极点因式分解:

将共轭成对的复数组合成二阶多项式,系数即为实数。 为采用相同结构的子网络,也将两个实零点/极点组合成二 阶多项式

导致系统不稳定

系数多为复数,增加了复数乘法和存储量

修正频率抽样结构

将零极点移至半径为r的圆上:

为使系数为实数,将共轭根合并

由对称性:

又h(n)为实数,则

将第k个和第(N-k)个谐振器合并成一个实系数的二阶网络:

当N为偶数时,还有一对实数根

k=0, N / 2处:

DSP原理与实训指导第五章 数字信号处理(DSP)基础知识

5.2

一、时钟电路

2

DSP电路的硬件结构

锁相环PLL

⑤ 倍频切换 若要改变PLL的倍频,必须先将PLL的工作方式从倍频方 式(PLL方式)切换到分频方式(DIV方式),然后再切换到新的倍 频方式。 实现倍频切换的步骤: 1:复位PLLNDIV,选择DIV方式; 2:检测PLL的状态,读PLLSTATUS位; 3:根据所要切换的倍频,确定乘系数; 4:由所需要的牵引时间,设置PLLCOUNT的当前值; 5:设定CLKMD寄存器。 注意:2分频与4分频之间也不能直接切换。

1

0

工作

1

1

工作

5.2

一、时钟电路

2

DSP电路的硬件结构

锁相环PLL

② 软件PLL的工作方式 通过软件编程,可以使软件PLL实现两种工作方式: PLL方式,即倍频方式。芯片的工作频率等于输入时钟 CLKIN乘以PLL的乘系数,共有31个乘系数,取值范围为 0.25~15。 DIV方式,即分频方式。对输入时钟CLKIN进行2分频 或4分频。

5.2

一、时钟电路

2

DSP电路的硬件结构

锁相环PLL

(2) 软件配置的PLL 软件配置的PLL具有高度的灵活性,它是利用编程对时钟 方式寄存器CLKMD的设定,来定义PLL时钟模块中的时钟配 置。 软件PLL的时钟定时器提供各种时钟乘法器系数,并能直 接接通和关断PLL。软件PLL的锁定定时器可以用于延迟转换 PLL的时钟方式,直到锁定为止。

PLL工作 状 态位

PLLSTA TUS

PLL PLLCO ON/ PLLDIV UNT OFF

PLLNDIV

5.2

一、时钟电路

2

DSP电路的硬件结构

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

§5.6

全通滤波器

∑a z

k =0 N k k =0 k

N

− N +k

∑a z

−k

= z−N

∑a z ∑a z

k =0 k k =0 N k

N

k

−k

= −z−N

D ( z −1 ) D( z)

z −2 + a1i z −1 + a2i 写成二阶滤波器形式:H ( z ) = Π i =1 a z −2 + a z −1 + 1 1i 2i

§5.8

一、梳状滤波器的构成:

梳状滤波器

假设系统函数是H(z),传输函数为H(ejw ),H(ejw )以2π 为 周期。如果将H(z)的变量z用z 代替,得到H(z ),传输函数 为H(ejwN ),H(ejwN )以2π / N为周期, 相当于将原来的H(ejw )压 缩到0 ∼ 2π / N区间, 而且N 个周期中的波形一样。 1-z-1 例5.8.1 已知H(z)= ,0 < a < 1, 利用该系统函数构成 -1 1-az N = 8的梳状滤波器。 1-z 的变量z用z 代替,得:H(z )= 1-az-N

(2)最大相位滤波器:滤波器的全部零点都位于单位圆外。

(2)对同一系统函数幅频特性相同的所有因果稳定系统中

(3)最小相位系统保证它的逆系统因果稳定。 B(z) 因果稳定系统H(z)= ,定义它的逆系统为 A(z) 1 A(z) -1 H (z)= = H(z) B(z) 原系统的极点变成了逆系统的零点,原系统的零点 变成了逆系统的极点。 故只有当因果稳定系统H(z)是最小相位系统时,它的 逆系统H -1(z)才是因果稳定的,也是一个最小相位系统。

非常靠近单位圆,则wr ≈ w0 ,3dB带宽为Δw ≈ 2 (1 − r ) 2、两个零点放在z = 1和z = −1,一对共轭极点为p1,2 = re ± jw0 其系统函数:H ( z ) = b0 (1 − z

−1

(

1 − re jw0 z −1

)(1 + z ) )(1 − re z )

−1 − jw0 −1

β ( jω ) 为相频特性:反映各频率成分通过滤波器

后在时间上的延时情况。

◆假设有一个信号x(n),它的频率分量分布在频率范围 w1<w<w2中,该信号通过一个理想滤波器 ⎧Ce − jwn0 , w1 < w < w2 H (e jω ) = ⎨ 0, 其他w值 ⎩ C和n0是常数,滤波器的幅度特性 H (e jω ) = C 滤波器的相位特性: ϕ ( w ) = − wn0 相位特性是频率w的线性函数,称为线性相位。 dϕ ( w ) 群时延: τ g ( w) = − = n0 dw ★群时延为常数:表示输入信号中的所有频率分量的延迟 时间相同。

§5.1

数字滤波器的基本概念

1、数字滤波器与数字滤波: 将输入信号的某些频率成分或某个频带进行压缩、 放大、从而改变输入信号的频谱结构---频率选择器。还 包括对信号进行检测和参数估计。数字滤波器是通过对 输入信号进行数值运算的方法来实现滤波的,模拟滤波 器则用电阻、电容、电感及有源器件等构成滤波器对信 号进行滤波。

§5.3.3 二阶数字滤波器 二阶数字滤波器:极点有2个,零点有1个、2个或没有。 但滤波器的零点和极点都是成对出现。 ( z − b1 )( z − b2 ) 二阶数字滤波器的系统函数:H ( z ) = G ( z − p1 )( z − p2 )

G是常数,p1 , p2为共轭极点;b1 , b2为共轭零点。

4、数字滤波器的种类:

◆经典滤波器:一般经典滤波器指的是用线性系统构成的 滤波器。 ◆现代滤波器:建立在随机信号处理的理论基础上,利用 随机信号内部的统计特性对信号进行滤波、检测或估值 等。例如维纳滤波器、卡尔曼滤波器、自适应滤波器等。

◆经典滤波器的分类:

(1)从滤波特性方面考虑:低通、高通、带通、带阻、全通滤波器 注意: 幅度特性 以2π为 周期

理想数字滤波器

理想数字滤波器的特点和分类

◆理想滤波器有三个重要特点(1)在滤波器的通带内, 幅度为常数(非零),在阻带内幅度为零;(2)具有 线性相位;(3)单位脉冲响应是非因果无限长序列。 ◆频率响应: H (e jω ) = H (e jω ) e jβ ( jω )

H (e jω ) 为幅频特性:表示信号通过该滤波器后 各频率成分的衰减情况。

(2)从实现方法上考虑:

无限脉冲响应滤波器---IIR滤波器(N阶)

bk z − k ∑ 1 − ∑ ak z

k =1 k =0 N −k M

H ( z) =

有限长单位脉冲响应滤波器--- FIR滤波器(N-1阶)

H ( z ) = ∑ h( n) z

n =0 N −1 −n

§5.2

§5.2.1

( ) = 10 H ( e )

jw p jw p

2

⎛ 2a ⎞ = 10 ≈ 0.5 ⇒ wp = arccos ⎜ 得: e H ⎟ 1 + a2 ⎠ ⎝ 当极点很靠近单位圆时,wp ≈ β = 1 − a,β 称为3dB带宽,

jw p 2 −3 10

( )

用β 计算的带宽和精确带宽很近似,见P119表5.3.1。

§5.3.2 一阶低通数字滤波器带宽的计算 1 − a 1 + z −1 一阶低通数字滤波器: H2 ( z ) = 2 1 − az −1

0 < a <1

w = 0时幅度最大, H ( e j 0 ) = 1, 幅度为0dB,设w = wp时幅度 降到 − 3dB,有: 3 = 20lg H e −

2、数字滤波器的实现方法: (1)用软件在计算机上实现。 (2)用专用的数字信号处理芯片完成。 (3)用硬件(加法器、乘法器和延时器的组合)完成。 3、数字滤波器的可实现性: 数字滤波器是一个LTI系统。实现一个LTI系统要考虑 系统的可实现性,即要求系统因果稳定---要求设计出的 系统极点全部集中在单位圆内。硬件乘法器只能完成实 数乘法,要求系统的差分方程的系数或者系统函数的系 数为实数,即要求系统的零极点必须共轭成对出现,或 者是实数。

( )( ) 其系统函数:H ( z ) = ( z − ae )( z − ae )

z − e jw0

jw0

z − e − jw0

− jw0

陷波器的3dB带宽为2 β = 2 (1 − a ),说明a越大,即极点越 靠近零点(越靠近单位圆),陷波器的3dB带宽越窄。

全通滤波器:滤波器的幅度特性在整个频带 [0,2π ] H 0 上均等于常数,或者等于1,即: ( e jw ) = 1,, ≤ w ≤ 2π 信号通过全通滤波器后,其输出的幅度特性保持不变, 仅相位发生变化,故全通滤波器也称纯相位滤波器。 其系统函数:H ( z ) =

第五章

数字滤波器的基本概念及一些特 殊滤波器

学习目标:

理解数字滤波器的基本概念。 理解理想数字滤波器的特点、分类及如何近似实现。 会用零极点放置法来设计简单的滤波器:一阶数字滤波 器、二阶数字滤波器。掌握低通到高通的简单变换。 理解掌握数字谐振器的概念及两种类型。 理解掌握数字陷波器、全通滤波器、最小相位滤波器、 梳状滤波器和正弦波发生器的概念。

L

它的零点和极点互成倒数关系。

§5.7

最小相位滤波器

一、因果稳定的滤波器的全部极点必须位于单位圆内, 但零点可以位于任意位置:

(1)最小相位滤波器:滤波器的全部零点都位于单位圆内。 (3)混合相位滤波器:在单位圆内、外均有零点。 二、最小相位滤波器的重要性质: (1)任何一个因果稳定的滤波器H(z)均可以用一个最小 相位滤波器和一个全通滤波器H ap(z)级联构成。 最小相位系统的延迟最小。

§5.5

数字陷波器

数字陷波器:二阶滤波器,它的幅度特性在w = ± w0处为零, 设零点为z=e ± jw0,使幅度特性在w = ± w0处为零,为使幅度 离开w = ± w0后迅速上升到一个常数,将两个极点放在很靠 近零点的地方,极点为z = ae ± jw0,

在其他频率上接近于常数,是一个滤除单频干扰的滤波器。

P118图5.3.1(a):一个极点,没有零点 1− a 0 < a <1 H1 ( z ) = z−a P118图5.3.1(b):一个极点,一个零点。 1 − a 1 + z −1 H2 ( z ) = −1 0 < a <1 2 1 − az 结论: ◆设计单极点、单零点低通滤波器应该让零点远离极点--滤波器幅频特性最好。

H hp ( e jw ) = H lp e hhp ( n ) = e

jπn

(

j ( w−π )

)

相当于将低通滤波器传输函数的w用w − π 代替。 hlp ( n ) = ( −1) hlp ( n )

n

相当于将低通滤波器的单位脉冲响应的奇数项加一个负号。

§5.4

数字谐振器

数字谐振器:二阶滤波器,特殊的双极点带通滤波器, 一对共轭极点re ± jw0,r接近于1,幅度特性在w0附近最大, 相当于在该频率发生了谐振。 数字谐振器的零点有两种放置法: (1)放置在原点; (2)两个零点分别放置在z = 1和z = −1。 1、零点在原点,一对共轭极点为p1,2 = re ± jw0 b0 其系统函数:H ( z ) = 1 − re jw0 z −1 1 − re − jw0 z −1

见P121例5.3.2和例5.3.3

§5.3.4 低通到高通的简单变换 ◆设计高通滤波器:首先设计一个低通滤波器,再将低通 滤波器转换成高通滤波器。 低通滤波器的通带在w=0附近,阻带在w=π附近;高通 滤波器的通带在w=π附近,阻带在 w=0附近 ◆简单的转换方法:将低通滤波器的频率响应旋转π弧 度,可得高通滤波器。