集成电路封装知识简介

干货|集成电路封装全,封装图片封装名称,拿走不谢,建议收藏

干货|集成电路封装全,封装图片封装名称,拿走不谢,建议

收藏

依旧自我介绍,张工,NPI 工程师,如果还不知道我具体是干什么的,欢迎看我的第一篇文章(主页点进去即可)。

万变不离其宗,作为NPI 工程师,DFM 可制造性分析涉及的范围非常广,今天是关于:集成电路封装大全,实物+名称。

一、什么是PCB封装?

封装是指将硅芯片上的电路引脚连接到外部连接器上,以便与其他设备连接,或者是指用于安装半导体集成电路芯片的外壳。

它不仅起到安装、固定、密封、保护芯片和增强电热性能的作用,而且通过芯片上的接点通过导线连接到封装外壳的管脚上,这些管脚又连接到其他的管脚上。

器件通过印刷电路板上的导线将内部芯片与外部电路结合起来。

这都是因为芯片必须与外界隔离,以防止芯片电路因接触空气杂质而腐蚀和性能下降。

另一方面,封装后的芯片也更易于安装和运输,这是很重要的,因为封装的质量直接影响芯片本身的性能以及与其连接的PCB(印刷电路板)的设计和制造。

衡量一个芯片封装技术先进性的一个重要指标是芯片面积与封装面积的比值,这个比值越接近1越好。

二、集成电路封装大全

集成电路封装

集成电路封装

集成电路封装

集成电路封装

集成电路封装

集成电路封装

集成电路封装

集成电路封装

集成电路封装集成电路封装。

集成电路封装基础知识

集成电路封装基础知识教材集成电路封装基础知识第一章集成电路的概述第一■节序言第二节集成电路的产生第三节集成电路的定义第四节集成电路的前道和后道的定义第五节集成电路的分类第二章集成电路的构成第一节集成电路的主要构成第二节各组成部分的作用第三章集成电路的封装类型第一节国外集成电路的封装类型第二节国内集成电路的命名第三节本公司内部的集成电路的封装类型第四节集成电路未来发展的趋势第四章集成电路的一脚(INDEX)识别第一节集成电路的一脚构成第二节集成电路的一脚识别第五章集成电路封装的主要材料第一节集成电路的主要原材料第二节各原材料的组成、保管、主要参数第六章集成电路封装工艺流程第一节集成电路封装的主要工艺流程第二节集成电路封装的详细工艺流程第三节封装中工艺流程的变化第七章集成电路封装设备的主要结构第一节封装设备的通用结构第二节设备各部分的作用第三节各工序各部分的结构不同第四节设备操作面板上常用英文和日文单词注释第八章集成电路封装设备的主要控制原理第一节PLC的概念第二节PLC的控制原理第三节设备的控制原理第九章集成电路封装中的常用单位换算第一节长度单位换算表第二节质量单位换算表第三节体积和容积单位换算表第四节力单位换算表第五节力矩和转矩单位换算表第六节压力和应力单位换算表第七节密度单位换算表第一节序言从本世纪50年代末开始,经历了半个多世纪的无线电电子技术正酝酿着一场新的革命.这场革命掀起的缘由是微电子学和微电子技术的兴起•而这场革命的旋涡中心则是集成电路和以其为基础的微型电子计算机.集成电路的问世,开辟了电子技术发展的新天地,而其后大规模和超大规模集成电路的出现,则迎来了世界新技术革命的曙光•由于集成电路的兴起和发展,创造了在一块小指甲般大小的硅片上集中数千万个晶体管的奇迹;使过去占住整幢大楼的复杂电子设备缩小到能放入人们的口袋,从而为人类社会迈向电子化,自动化,智能化和信息化奠定了最重要的物质基础•无怪乎有人将集成电路和微电子技术的兴起看成是跟火和蒸汽机的发明具有同等重要意义的大事1 •集成电路的产生5•集成电路的分类:TTL集成电路;(定义)集成运算放大器;COMS集成电路;接口集成电路; ECL集成电路;集成稳压器与非线性模拟集成电路微型计算机集成电路;HTL集成电路.2•集成电路的构成:.集成电路的封装类型1. 国外集成电路封装类型的命名及分类SIP ---------------------------------------------- (SINGLE IN -INE PACKAGE) ZIP ---------------------------------------- (ZIG-ZAG IN-LINE PACKAGE)DIP-------------------------------------------- (DUAL IN-LINE PACKAGE) SHDIP -------------------------- (SHRINK DUAL IN-LINE PACKAGE)WDIP ------------------ (WINDOW TYPE DUAL IN-LINE PACKAGE)PGA -------------------------------------- (PIN GRID ALLEY PACKAGE)SVP---------------------------------- (SURFACE VERTICAL PACKAGE) SOP ----------------------- (SMALL OUTLINE L-LEADED PACGAGE) TSOP1 ------------ (THIN SMALL OUTLINE L-LEADED PACKAGE)LSSOP -------------------------------------- (LOW PRO SMALL OUTLINE PACKAGE)TSSOP -------------------------------------- (THIN PRO SMALL OUTLINE PACKAGE)UTSOP ------------------------------------ (ULTRA THIN SMALL OUTLINE L-LEADED PACKAGE)QFP ------------------------------------------------------------------ (QUAD FLAT L-LEADED PACKAGE)LQFP -------------------------------------------- (LOW PRO FLAT L-LEADED PACKAGE)TQFP --------------------------------------------------------- (THIN QUAD FLAT L-LEADED PACKAGE)UTQFP ------------------------------------------ (ULTRA THIN QUAD FLAT L-LEADED PACKAGE)HQFP -------------------------------------------------------------------------------- (QFP WITH HEAT SINK)TPQFP ------------------------------------------------- (TEST PAD QUAD FLAT L-LEADED PACKAGE)SON ---------------------------------------------------- (SMALL OUTLINE NON-LEADED PACKAGE)QFN ----------------------------------------------------------- (QUAD FLAT NON-LEADED PACKAGE)SOJ ----------------------------------------------------------- (SMALL OUTLINE J-LEADED PACKAGE)QFJ ------------------------------------------------------------------- (QUAD FLAT J-LEADED PACKAGE)BGA ------------------------------------------------------------------------------------ (BALL GRID ARRAY)SPGA ------------------------------------------------------------- (SHRINK PIN GRID ALLEY PACKAGE)LGA ------------------------------------------------------------------------ (LEAD GRID ALLEY PACKAGE)DTP ------------------------------------------------------------------- (DUAL TAPE CARRIER PACKAGE)QTP ------------------------------------------------------------------- (QUAD TAPE CARRIER PACKAGE)SIMM ------------------------------------------------------------- (SINGLE INLINE MEMORY MODULE)DIMM ---------------------------------------------------------------- (DUAL INLINE MEMORY MODULE)SOCKET TYPE3. 国内外封装名称对照:SIP ----------- S INGLE IN LINE PACKAGE ------------------ 单列封装SIPT --------- S INGLE IN LINE PACKAGE WITH TAB----- 带散热片的单列封装DIP ----------- D UAL IN LINE PACKAGE ----------------------- 双列封装DIPT --------- D UAL IN LINE PACKAGE WITH TAB -------- 带散热片的双列封装SDIP --------- S HRINK DUAL IN LINE PACKAGE ----------- 纵向收缩型双列封装2. 国内集成电路的名称和代号:玻璃陶瓷扁平封装 W 陶瓷四面引线扁平封装 Q 塑料双列弯引线封装O 陶瓷熔封扁平封装 H 塑料双列封装 P 陶瓷熔封双列封装 J 金属菱形封装 K 塑料片式载体封装 E 陶瓷扁平封装 F 塑料扁平封装 B 塑料四面引线扁平封装 N 陶瓷双列封装 D 塑料单列封装 S 金属圆形封装 T 陶瓷无引线片式载体封装 --------------- C陶瓷针栅阵列封装 ---------------------- GSWDIP ----- SKINNY DIP OR SHRINK WIDTH DUAL IN LINE PACKAGE----------- 横向收缩型双列封装QIP ---------- QUAD IN LINE PACKAGE ----------------------- 四列封装ZIP ----------- ZIGZAG IN LINE PACKAGE -------------------- 引线交叉排列封装CERDIP ——CERAMIC DUAL IIN LINE PACKAGE ------- 陶瓷熔封双列式封装CDIP -------- CERAMIC DUAL IN LINE PACKAGE (SIDE BRAZED )----------- 陶瓷双列式封装(通常指侧面钎焊的)PGA --------- PIN GRID ARRAY --------------------------------- 针栅阵列封装SOP --------- SMALL OUT LINE PACKAGE ------------------ 微型封装(两面出腿)SOJ --------- SMALL OUTLINE PACKAGE WITH J LEAD----J 形弓 I 线微型封装PLCC -------- PLASTIC LEADED CHIP CARRIER ----------- CLCC/LCC--CERAMIC LEADLESS CHIP CAEEIER ------ 陶瓷片式载体 QFP --------- QUAD FLAT PACKGE ---------------------------- 四面引线扁平封装 薄的微型封装(两面出腿)塑封有引线的片式封装TSOP ------- THIN SMALL OUTLINE PACKAGE ------------4.本公司内现有的封装类型SIP、SIPTDIP、DIPT、SDIP、SKDIPDIP24、DIP28、DIPT14、SDIP42、SDIP52、SDIP64、SKDIP22、SKDIP24SOP8、SOP14 SOP16 SOP20、SOP24 SOP28 SOL8SOJ26QFP48、QFP64、QFP80、QFP100.集成电路的一脚(INDEX)识别印记正对人的位置,产品最左下角的起脚为一脚,然后按逆时针方向旋转,以次列数.DIP8、DIP14、DIP16、DIP18、DIP20、 SOP 、SOL SOJQFP5.本公司内现有的圭寸装品种.集成电路封装的主要材料1. 引线框架:LEAD FRAME(IC的载体,连接芯片和PCB板)(框架的一脚标记与芯片的一脚在装片时,要保持一致)2•银浆Ag:用以粘接芯片和L/F的PAD.3. 金丝:用以连接芯片和L/F.4. 树脂(塑封料):用以包封以键合好的半成品,以达到保护芯片的目的5. 油墨:用以标识集成电路.四.集成电路封装工艺流程1. 主要工艺流程:(磨片)-----划片-----装片-----键合——塑封——去飞边——电镀-----打印-----切筋打弯-------- 外观-----(测试)----包装2. 工艺流程的细化:贴片----磨片----贴片----划片----超声清洗----UV照射----崩片----装片----银浆固化----键合----塑封前烘----塑封----后固化----切筋----去飞边----电镀----打印----油墨固化----成形----外观----测试----包装七.设备的结构和控制原理1. 磨片(减薄):在使用大直径的硅片制造集成电路芯片时,由于其厚度较大,不能满足划片,装片和键合的工艺要求,因此需要对圆片的背面进行处理和减薄,除去其背面的氧化层,才能保证在装片和键合时有良好的浸润性,并改善装片后芯片与中岛之间的欧姆接触,减小串联附加电阻和提高散热性能.1.)研磨法:是利用大量硬度较大,颗粒较细并具有复杂棱角的磨料,在外力的推动下对被加工表面进行磨削作用的一种机械加工方法•研磨料:可采用天然或人造金刚砂,如a -AL2O3;a -SiC 磨料与水的比例为:1:52. )磨削法:是将机械平面磨削方法应用到半导体器件的加工中.磨削圆片时,砂轮和转盘各自以相反方向旋转,借助于它们的相对运动将圆片磨削减薄.(例:MPS2R30C减薄机)结构:由磨头,转盘(吸盘),磨头垂直和水平进给机构和冷却装置等部分组成.2. 划片:把已制有电路图形的集成电路圆片切割分离成具有单个图形(单元功能)的芯片,常用的方法有金刚刀划片,砂轮划片和激光划片等几种.而我们通常使用的是砂轮划片.砂轮划片机的砂轮转速为30000r/min左右,切割速度通常在50-150mm/min之间.圆片的固定方法是采用真空吸盘,并且工作台面是气垫式的,因此可以保证切割深度完全一致.同时利用监视图象或显微镜来进行定位.全自动划片机工艺步骤包括:圆片上料,对准,划片,清洗,烘干,进圆片盒等工步. 划片的切割方法:通常我们采用的是切割留深法.划片的切割方式:A模式(用于非FJ产品) C 模式(用于富士通产品)3. 装片:是把集成电路芯片粘接到引线框架中岛上的指定位置,为丝状引线的连接提供条件的工艺,称之为装片.3.1 装片的方法有:导电胶粘接法,银浆,低温玻璃烧结法和低熔点合金的共晶熔接法等.3.2 导电胶粘接法由于具有工艺简单.成本低,易采用自动化专用设备,同时在胶粘剂中增加一定比例的金属粉粒,以改善胶粘剂的导电和导热性能,有利于改善芯片的散热条件,因此目前广为应用的就是导电胶粘接法.3.3导电胶:是利用高分子有机化合物所制成的胶粘剂,是以环氧树脂为主体并加有银粉或铝粉等金属粉粒,再配置少量的固化剂和溶剂而成,其具体要求是:粘接牢固,固化时间短,在经受一定的温度后仍能保持其固化状态不变,并在固化期间不产生过多的挥发气体而污染芯片和具有较高的导电散热能力.3.4装片机:由承片台,真空吸嘴,芯片传送机构,加热系统,工件传送机构几个主要部分组成. 承片台:主要作用是将已经分离的但仍与塑料薄膜保持粘贴的芯片,连同贴片环进入承片台后,可由步进电机驱动承片台,作X和丫方向的移动,并通过图形识别装置,挑选出合格与合格芯片.对缺角,破裂和注有不合格标志的芯片,将有反馈信号加至步进电机,使承片台迅速移动,不将其剔除不用;而对合格芯片,则也有反馈信号输至步进电机,使承片台移动,将其送入到规定的位置上.真空吸嘴:作用是将到达规定位置的芯片,为了保护芯片不受损伤,采用真空吸力键芯片吸起,并送到引线框架的中岛上进行装片.真空吸嘴分为:平面吸嘴,斜面吸嘴和角锥吸嘴等. 根据材料的不同可分为:金属吸嘴和海绵吸嘴等.芯片的传送机构:通常采用悬臂式结构•主要作用是将由真空吸嘴吸取的芯片直接送到规定位置去进行装片,也可经过中途修正台修正位置后再送到规定位置上•加热系统:由内热式电阻加热,体积小但功率可达150-200W,并附有调温装置和预热设备,但仅限于共晶焊接装片使用.工件传送机构:对于塑料封装引线框架,可根据引线的尺寸来调整其轨道的宽度,并由步进电机按规定程序使之准确就位•4. 键合:将芯片的电极用金丝与引线框架的内引线连接起来,这一工艺过程称之为键合•4.1集成电路的芯片与封装外壳的连接方式可分为:有引线键合结构和无引线键合结构两大类有引线键合结构就是通常所说的丝焊法,即用金丝或铝丝实行金-金键合,金-铝键合或铝- 铝键合•由于都是在一定压力下进行的焊接,故又称为压焊•4.2目前塑料封装的集成电路通常使用有引线键合的金丝焊接.金丝焊接又分为:热压楔焊,热压球焊,超声热压焊,超声焊.4.3热压焊键合:就是在加热和加压的同时,对其芯片金属化层的压点(一般是铝层)以及外壳或引线框架的外引线引出端头,用金属丝引线(一般是金丝)通过焊接连接起来.由于金属丝和芯片上的铝层同时受热受压,其接触面产生了塑性变形,并破坏了界面的氧化膜,使两者接触面几乎接近原子引力的范围;又因为金丝和焊接层(铝层,镀金层或镀银层)表面存在的不平整现象,加压后其高低不平处相互填充而产生弹性嵌合作用,使两者紧密结合在一起,从而达到键合的目的.键合时,外壳或引线框架应预先加热到310-350 C°,金丝通过陶瓷,碳化钨或碳化钛硬质合金所做成的劈刀,并加热至200C°左右.当金丝由劈刀毛细孔中伸出时,利用氢气或电火花在其端头进行加热,使其熔化成球状,并立即通过50-160g的压力压焊在芯片金属化层的压点上.外焊点则仍采用楔形焊,,即金丝与外壳或引线框架的外引线引出端头实行金-金的热压焊接.4.4超声焊键合:是利用超声波的能量将金属丝(通常是用铝丝)在不加热的情况下,实行内外焊点的键合.其工作原理是由超声波发生器产生的几十千周的(通常为50-60kHz)超声波振荡电能,通过磁致伸缩换能器,在超声频磁场感应下迅速伸缩而产生弹性振动,再经变幅杆传给劈刀,并同时在劈刀上施加一定的压力.劈刀就在这两种力的作用下,带动金属丝在芯片金属层的压点和外壳或引线框架的外引出端头的表面迅速摩擦振动.这样不仅破坏了两者焊接界面的氧化膜,同时也使两者产生塑性变形,使两种纯净的金属面紧密接触,形成牢固的键合.超声焊接的内外焊点都是成楔形的,不需要对芯片和外壳加热,压点是实行铝-铝键合.键合状态主要由以下三个工艺参数所决定的:功率,时间,压力.4.5超声热压焊键合:在热压焊的基础上再加增加超声的能量所实现的键合,称之为超声热压超声热压焊同时具有热压和超声压焊两者的优点,可以降低热压焊的温度(从单纯的热压焊温度---300 C°以上下降至200-260 C°),使一些耐温不高的外壳货基片也能应用金丝作互连•对于引线框架较厚的和带有散热片的塑料封装集成电路,因为它们的散热好,温度梯度大,也可采用超声热压焊•超声热压焊机分为:手动式,半自动式,全自动式.操作步骤:(1)位置复原:确定芯片一金属化层压点为第一个焊接点,并调整其位置,使之置于对位光点之下;11/15(2) 按下开动钮:劈刀降落并进行第一点的焊接.当金球与芯片压点接触时,劈刀端头的内凹面在热能的作用下将金球压成钉头状的焊点,此时超声波发生器同步启动,并产生超声能量,以加速焊接的进行;(3) 劈刀自动提升到一定高度,丝夹张开,使金丝自动送出;(4) 把引线框架外引线一相应的引出端头作为第二焊点,并调整其位置,使之置于对位光点之下,按下开动钮,劈刀降落,以第二点的焊接,并用劈刀端头的外侧把金丝压成楔形的焊点,此时超声波发生器同步启动,并产生超声能量,以加速焊接的进行;(5) 劈刀自动升起时丝夹夹紧金丝,把金丝从楔形焊点的端头拉断,成为一个无丝尾的焊点;(6) 劈刀自动停在复原位置上,丝夹仍然夹紧金丝,电子烧球器产生高压电火花,把金丝端部烧成金球;(7) 丝夹松开,靠金丝的张力把金球升起到劈刀端部,准备进行下一个程序的循环.全自动式金丝球焊机:当对其第一个产品进行光点对位或采用自教程序进行焊接后,则所有的动作程序全部存储在微处理机中,通过自动传输机构,对以后的同类产品进行连续作业作业人员只需用料盒将已经装片的引线框架放到送料台上,并取走已焊接好的产品.如果个别芯片装片位置不当或有其他差错时,则设备上图形识别装置将会自动报警停机,以待作业人员处理.同时,当金丝使用完毕后,设备也会自动给出信号,告诉作业人员添加金丝.图形识别装置的作用:就是对芯片的焊接位置进行寻找和检测,其工作原理是采用相关法技术,即用工业视频摄像机摄取芯片表面的图形,并将摄取图象转换为二进制数码,然后和预先存储的标准的二进制数码图象进行比较.当发现差异时,可由步进电机按给定信号驱动工作台,作X和丫方向的移动,直至对位准确为止.校准范围一般在X= ± 0.2mm,Y= ± 0.2mm 0 =±5°.4.6 球焊劈刀:适用于金丝球焊键合,都是空心管状轴对称型,其端头的锥角有30 ° ,20 ° ,15° ,10° 等.劈刀常用材料有:陶瓷,碳化钨和碳化钛等.由于陶瓷能耐王水(3HCL+HNO3)的腐蚀,当金丝阻塞劈刀通孔而不能取出时,可用王水浸泡而将残存的金丝溶解出来,因此陶瓷劈刀应用较多.4.7金丝要求:(1)丝材的表面应光滑,清洁,不应有任何有机物如油脂,指印等的污染;(2) 不应有大于直径四分之一的影响丝材横截面的缺凹,划伤,裂痕,凸块和附着物⑶丝材应卷绕在特定的绕线轴上,不应有小于30°的死弯和小于0.76mm直径的结存在,且卷绕紧密整齐,不能杂乱松动;(4) 任意长的丝材卷绕在绕线轴上时,只能单层上绕式密绕,且每轴只绕一根,并在首尾注有标记;(5) 每轴丝材都应有严格的包装,以防止受损或污染,并应有规定的标志.⑹金丝纯度要求在99.99%以上,经制成细丝后还需进行退火处理,以保证其拉力强度和延伸率都能符合键合工艺要求.金丝成分表:金丝的选用:应根据集成电路的工作电流来加以选择.一般金丝的熔断电流与金丝的直径成线性关系.5.塑封:即塑料封装,是一种非气密性封装.它是将键合后的半成品用塑料封装起来,以达到保护作用以适应一定的环境.5.1塑料封装从50年代开始,70年代推广,到今天九十年代已广为使用.之所以塑料封装能发展到目前的水平,因其存在诸多的优点:(1) 塑料封装在集成电路的组装过程中一次加工完毕,不同与其他形式的气密性封装,需要事先作成封装外壳,大大简化了工艺流程;(2) 生产工艺简便.一次成型几百只,节省时间,提高工效,易于实现自动化,便于大批量生产;(3) 成本低.所用材料少,除了在初建初期需要对设备和模具投资外,以后的维护费用很低,是气密性封装的1/3-1/5;(4) 重量轻,抗冲击,振动和加速运动等机械性能都比较优越;(5) 环氧和硅酮树脂的抗辐射性能好;(6) 绝缘性能好,寄生参数小;(7) 抗化学腐蚀能力强;(8) 塑料封装中铀,钍的含量少,适于VLSI存储器的封装. 缺点:(1) 抗潮性能差;(2) 热性能差;(3) 抗盐雾腐蚀性能差;(4) 电屏蔽性能差;(5) 易老化.5.2塑封树脂:是一种热固性塑料,以高分子化合物合成的树脂为基体,加入固化剂仮应促进剂(催化剂),填充剂,阻燃剂,脱模剂和着色剂等组成.常用树脂有:环氧树脂,硅酮树脂等.目前我们使用的是环氧树脂. 树脂发展趋势:高纯度,低应力,低a射线等.树脂的保管:5C°以下.5.3塑料封装的成型方法有滴涂敷法,填充法,浇铸法和递模成型法.目前我们使用的是递模成型法. 递模成型法:是将塑料包封机上油缸压力,通过注塑头,传递到被预热的塑料上,使塑料经浇道,浇口缓慢挤入型腔,并充满整个型体,把芯片包封起来,该成型法称之为递模成型法.也就是通常称的塑封.5.4塑圭寸的工艺条件:⑴塑封模的温度:175土5C°(2) 合模压力:根据塑封模的大小,重量,型腔数,以下框架材料,成品外形尺寸和注塑压力等条件选定的.(3) 注塑压力:也称为递模压力和传递压力,其作用是传递塑料,使塑料能充满型腔.一般30-100Kg/cm2.⑷预热温度:塑料(塑封料)的预热温度取决于塑料的凝胶时间和流动性,一般为80-100C。

集成电路封装技术

集成电路封装技术一、概述集成电路封装技术是指将芯片封装成实际可用的器件的过程,其重要性不言而喻。

封装技术不仅仅是保护芯片,还可以通过封装形式的不同来满足不同应用领域的需求。

本文将介绍集成电路封装技术的基本概念、发展历程、主要封装类型以及未来发展趋势等内容。

二、发展历程集成电路封装技术随着集成电路行业的发展逐渐成熟。

最早的集成电路封装形式是引脚直插式封装,随着技术的不断进步,出现了芯片级、无尘室级封装技术。

如今,随着3D封装、CSP、SiP等新技术的出现,集成电路封装技术正朝着更加高密度、高性能、多功能的方向发展。

三、主要封装类型1.BGA封装:球栅阵列封装,是一种常见的封装形式,具有焊接可靠性高、散热性好等优点。

2.QFN封装:裸露焊盘封装,具有体积小、重量轻、成本低等优点,适用于尺寸要求严格的应用场合。

3.CSP封装:芯片级封装,在尺寸更小、功耗更低的应用场合有着广泛的应用。

4.3D封装:通过将多个芯片垂直堆叠,实现更高的集成度和性能。

5.SiP封装:系统级封装,将多个不同功能的芯片封装在一起,实现更复杂的功能。

四、未来发展趋势随着物联网、人工智能等领域的兴起,集成电路封装技术也将迎来新的挑战和机遇。

未来,集成电路封装技术将朝着更高密度、更低功耗、更可靠、更环保的方向发展。

同时,新材料、新工艺和新技术的应用将为集成电路封装技术带来更多可能性。

五、结语集成电路封装技术是集成电路产业链中至关重要的一环,其发展水平直接关系到整个集成电路的性能和应用范围。

随着技术的不断进步,集成电路封装技术也在不断演进,为各个领域的技术发展提供了强有力的支撑。

希望本文能够帮助读者更好地了解集成电路封装技术的基本概念和发展趋势,为相关领域的研究和应用提供一定的参考价值。

集成电路封装制程知识

集成电路封装制程知识

集成电路的制造包括芯片制造、芯片封装、测试三个制程。

目前本公司只进行芯片封装和测试两个制程,封装的制程如下:

1.划片

这道工序是将晶圆贴在蓝膜上,并将晶圆切割成芯粒。

2.粘片

这道工序是为了使芯片和框架之间形成一个良好的欧姆接触。

3.压焊

这道工序是为了将粘片完成后的芯片,使其芯片内引线和框架外引线用金丝键合在一起,从而使内外引脚连接起来。

4.塑封

这道工序是为了将压焊完成后的芯片进行包装,确保芯片和外界保持清洁、无干扰。

5.打印

这道工序是为了将塑封好的产品进行打印标识,使人明白这电路的型号和规格。

6.冲溢料

这道工序是为了除去管脚之间的塑封溢料及连筋,使电路更美观整洁。

7.喷砂

这道工序是为了将产品表面的油渣、生刺和溢料去除,以达到电镀的技术要求。

8.电镀

这道工序是将产品的引脚表面镀上一层纯锡,以提高其抗氧化性并增加其导电性。

9.冲切

这道工序是电镀好的产品冲切成单个的成形品。

10.测试

这道工序是测试产品的电性参数,将合格品和不合格品分开,防止电性不良产品出货。

其它还有:外检、编带、包装等辅助工序。

了解电子信息工程中的集成电路封装技术

了解电子信息工程中的集成电路封装技术随着科技的不断发展,电子信息工程已经成为现代社会中不可或缺的一部分。

而在电子信息工程中,集成电路封装技术则扮演着非常重要的角色。

本文将介绍集成电路封装技术的概念、发展历程以及未来的发展趋势。

一、集成电路封装技术的概念集成电路封装技术是指将电子元器件封装在一个外壳内,以保护电子元器件并方便其安装和使用的技术。

封装技术的主要目标是提高集成电路的可靠性、稳定性和性能。

封装技术的发展与集成电路技术的进步密不可分,两者相互促进,共同推动了电子信息工程的发展。

二、集成电路封装技术的发展历程集成电路封装技术的发展可以追溯到上世纪五六十年代。

当时,集成电路的封装主要采用插入式封装,即将芯片插入到插座中,这种封装方式简单粗暴,但存在许多问题,如连接不牢固、易受外界干扰等。

随着电子信息工程的快速发展,人们对集成电路封装技术提出了更高的要求。

于是,表面贴装封装技术应运而生。

表面贴装技术将芯片直接粘贴在印刷电路板上,通过焊接连接芯片和电路板,大大提高了封装的可靠性和稳定性。

这种封装方式成为了当今电子信息工程中最常见的封装技术。

随着电子产品的不断迭代和升级,封装技术也在不断创新。

目前,三维封装技术成为了研究的热点。

三维封装技术通过将多个芯片垂直叠加,从而实现更高密度的封装,提高电子产品的性能和功能。

此外,柔性封装技术也逐渐崭露头角,它可以将芯片封装在柔性基板上,使电子产品更加轻薄和便携。

三、集成电路封装技术的未来发展趋势随着电子信息工程的快速发展,集成电路封装技术也将迎来更大的挑战和机遇。

未来,集成电路封装技术的发展趋势主要体现在以下几个方面:1. 进一步提高封装密度:随着电子产品的不断迭代和升级,对集成电路封装的密度要求越来越高。

未来的封装技术将更加注重提高封装的密度,实现更小尺寸、更高性能的电子产品。

2. 加强封装与散热的结合:随着电子产品功耗的增加,散热问题成为了制约电子产品性能提升的重要因素。

24.IC封装基本知识介绍

4.3.3 MCM应用领域 作为一个完整的电子系统,常常由许多功能块组成, 如复杂的运算单元像MCU和DSP、小信号放大、射频 电路、低频功放和光电器件等。这些功能电路往往用 不同的工艺实现,如要用同一工艺制在一片芯片上是 十分困难的,有时甚至是不可能的。 ——多芯片封装的集成电路组件

4.3.4 MCM的基板 多芯片封装的基板主要有以下一些类型 L(Laminate)型,即叠层型 C(Ceramic)型即原膜陶瓷型 D(Deposited Thin Film)型即淀积薄膜型 Si (Silicon)型,即硅型

SOP封装外形图

(3) QFP(Quad Flat Package) 四边引脚扁平封装

QFP封装结构 QFP的分类: QFP的分类:塑(Plastic)封 QFP(PQFP) 薄型QFP(TQFP) 窄(Fine)节距 QFP(FQFP)

4.3 集成电路多芯片组件(MCM)封装技术 集成电路多芯片组件( )

一种六芯片MCM

4.3.2 多芯片封装的好处 多芯片封装的好处是可将不同工艺的芯片组合在 一起在单片集成电路上实现较为完整的系统功能。还 在于可以利用现有成熟而较为复杂的芯片附加自己设 计的较简单的ASIC组成应用系统,降低产品开发风险, 提高芯片性能和经济效益。多芯片封装提高系统的保 密性和可靠性也是很显然的。多芯片封装是21世纪新 型封装的一个重要方向。

6. 按芯片功能分类 模拟集成电路(Analog IC):它是指处理模拟信号 (连续变化的信号)的集成电路 线性集成电路:又叫做放大集成电路,如运算 放大器、电压比较器、跟随器等 非线性集成电路:如振荡器、定时器等电路 数模混合集成电路(Digital - Analog IC) :例如数 模(D/A)转换器和模数(A/D)转换器等

集成电路芯片封装的概念

集成电路芯片封装的概念集成电路芯片封装的概念1. 引言集成电路芯片封装是现代电子技术中非常重要的一环。

它是将微小的芯片封装在保护性外壳中,以便保护芯片免受损坏,并提供电气连接和散热功能。

本文将深入探讨集成电路芯片封装的概念,从封装形式、封装材料、封装技术以及封装的发展趋势等多个方面展开,帮助读者更全面、深刻地了解这一关键电子技术。

2. 集成电路芯片封装的形式集成电路芯片封装有多种形式,每种形式都有不同的特点和适用范围。

常见的封装形式包括:2.1 芯片级封装(Chip-scale Package,CSP):CSP封装将芯片直接封装在微小的外壳中,尺寸比传统封装更小。

它适用于高密度集成电路和轻薄移动设备等应用。

2.2 简单封装(Dual in-line Package,DIP):DIP封装是最早的一种封装形式。

芯片被封装在具有导脚的塑料外壳中,易于插拔和焊接。

但该封装形式占用空间较大,适用于较低密度的应用。

2.3 小型封装(Small Outline Package,SOP):SOP封装是一种相对较小的封装形式,兼具DIP封装的插拔性和CSP封装的高密度特点。

2.4 超薄封装(Thin Small Outline Package,TSOP):TSOP封装比SOP封装更薄,适用于具有高密度布局的应用。

2.5 高温封装(High-Temperature Package,HTP):HTP封装在高温环境下依然能够保持电性能,适用于高温工作环境中的电子设备。

3. 集成电路芯片封装的材料3.1 塑料封装材料塑料封装材料是集成电路芯片封装中最常见的材料之一。

它具有廉价、轻便、隔热、防潮的特点,适用于大规模生产。

常见的塑料封装材料有聚酰亚胺(Polyimides)、环氧树脂(Epoxy Resin)等。

3.2 陶瓷封装材料陶瓷封装材料的热导率较高,能够较好地散热,适用于高性能和高功率的集成电路芯片。

常见的陶瓷封装材料有氧化铝(Alumina)和氮化铝(Aluminium Nitrite)等。

集成电路芯片封装

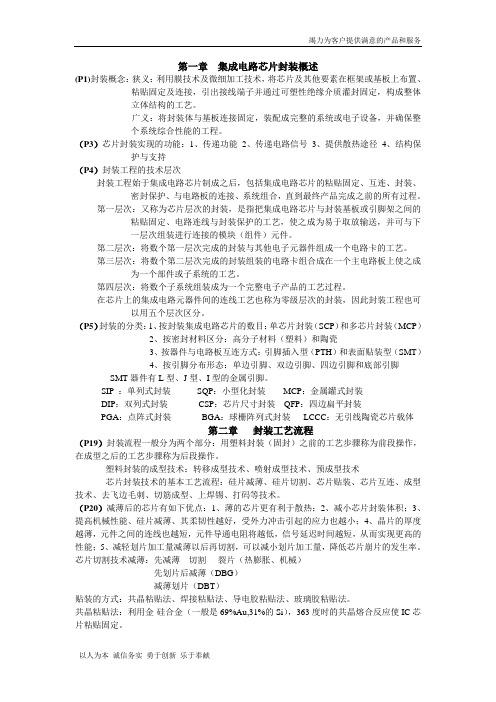

第一章集成电路芯片封装概述(P1)封装概念:狭义:利用膜技术及微细加工技术,将芯片及其他要素在框架或基板上布置、粘贴固定及连接,引出接线端子并通过可塑性绝缘介质灌封固定,构成整体立体结构的工艺。

广义:将封装体与基板连接固定,装配成完整的系统或电子设备,并确保整个系统综合性能的工程。

(P3)芯片封装实现的功能:1、传递功能2、传递电路信号3、提供散热途径4、结构保护与支持(P4)封装工程的技术层次封装工程始于集成电路芯片制成之后,包括集成电路芯片的粘贴固定、互连、封装、密封保护、与电路板的连接、系统组合,直到最终产品完成之前的所有过程。

第一层次:又称为芯片层次的封装,是指把集成电路芯片与封装基板或引脚架之间的粘贴固定、电路连线与封装保护的工艺,使之成为易于取放输送,并可与下一层次组装进行连接的模块(组件)元件。

第二层次:将数个第一层次完成的封装与其他电子元器件组成一个电路卡的工艺。

第三层次:将数个第二层次完成的封装组装的电路卡组合成在一个主电路板上使之成为一个部件或子系统的工艺。

第四层次:将数个子系统组装成为一个完整电子产品的工艺过程。

在芯片上的集成电路元器件间的连线工艺也称为零级层次的封装,因此封装工程也可以用五个层次区分。

(P5)封装的分类:1、按封装集成电路芯片的数目:单芯片封装(SCP)和多芯片封装(MCP)2、按密封材料区分:高分子材料(塑料)和陶瓷3、按器件与电路板互连方式:引脚插入型(PTH)和表面贴装型(SMT)4、按引脚分布形态:单边引脚、双边引脚、四边引脚和底部引脚SMT器件有L型、J型、I型的金属引脚。

SIP:单列式封装SQP:小型化封装MCP:金属鑵式封装DIP:双列式封装CSP:芯片尺寸封装QFP:四边扁平封装PGA:点阵式封装BGA:球栅阵列式封装LCCC:无引线陶瓷芯片载体第二章封装工艺流程(P19)封装流程一般分为两个部分:用塑料封装(固封)之前的工艺步骤称为前段操作,在成型之后的工艺步骤称为后段操作。

集成电路封装

集成电路封装

集成电路封装,又称芯片封装,是指将集成电路芯片进行封装,以提供保护、连接和连接外部电路的功能。

常见的集成电路封装有以下几种类型:

1. 对顶焊接(DIP)封装:这是最早也是最常见的封装形式之一,通常用于较低密度和较低频率的应用。

它采用两排引脚,可以直接插入插座或焊接到电路板上。

2. 表面贴装技术(SMT)封装:这是目前最常用的封装技术,广泛应用于各种电子设备中。

SMT封装可以有效提高集成度和组装效率,减小封装体积和重量。

3. 高级封装:随着技术的发展,出现了一些更高级的封装形式,例如球形阵列封装(BGA)、无引脚封装(LGA)和封装在柔性基板上的芯片(COF)等。

这些封装形式主要用于高密度、高速和复杂电路的应用。

封装的选择会根据应用需求、电路复杂性、可靠性和成本

等因素进行评估和决策。

不同的封装形式有各自的优缺点,需要根据具体的设计要求和制造工艺选择适合的封装。

集成电路封装介绍

SO 小外形 Small outline SOJ J形引线的SOP Small outline J lead SOP 小外形封装 Sop outline package SOT 小外形晶体管 SSOP 缩小的小外形封装 Shrink small outline package SOIC 小外形IC Small outline IC TAB 载带自动焊 Metric TAB TCE 热膨胀系数 TCM 导热模块 TQFP 薄形四边引线扁平封装 Thin quad flat pack TSOP 薄形小外形封装 Thin small outline package TSSOP 薄形缩小的小外形封装 Thin shrink small outline package VLSI 超大规模集成 ZIF 零插入力 ZIP 单边交叉双列直插封装 Zig-zag in-line package

高密度封装中的关键技术

从技术发展观点来看 ,作为高密度封装的关键技术主要 有 :TCP , BGA, FCT ,CSP ,MCM和三维封装

载带封装 它可以提供超窄的引线间距和很薄的封装外形 ,

且在PCB板上占据很小的面积 ,可用于高I/O数的

ASIC和微处理器 ,东芝公司1 996年问世的笔记

半导体后封装的发展趋势

向表面安装技术 (SMT)发展 1988年SMT技术约占封装市场份额的17.5% , 1 993年占 44% , 1 998年占 75%。传统的双列直插 封装所占份额越来越小 ,取而代之的是表面安装类 型的封装 ,如有引线塑料片式载体 ,无引线陶瓷片 式载体 ,四边引线塑料扁平封装 ,塑料球栅阵列封 装 (PBGA)和陶瓷球栅阵列封装 (CBGA)等 , 尤其是PQFP和BGA两种类型最具典型.

集成电路封装概述

返回

集成电路封装概述

3.1根据材料分类,根据所用的材料来划分半导体器 件封装形式有金属封装、陶瓷封装、金属-陶瓷封 装和塑料封装 3.2根据密封性分类,按封装密封性方式可分为气密 性封装和树脂封装两类 3.3根据外形、尺寸、结构分类,按封装的外形、尺 寸、结构分类可分为引脚插入型、表面贴装型和 高级封装

返回

集成电路封装概述

4.SiP(system in a package,封装内系统, 或称系统封装)是指将不同种类的元件,通 过不同技术,混载于同一封装之内,由此 构成系统集成封装形式。该定义是经过不 断演变,逐渐形成的,开始是在单芯片封 装中加入无源元件,再到单个封装中加入 多个芯片、叠层芯片以及无源器件,最后 封装构成一个体系,即SiP 返回

集成电路封装概述

1.封装形式主要有:DIP、SOP、QPF、PGA、 BGA到CSP再到现在的SIP

返回

集成电路封装概述

2.1利用膜技术及微细连接技术将半导体芯片(chip) 和框架(Lead-Frame)或基板(Substrate)或 塑料薄片(Film)或印刷线路板中的导体部分连 接以便引出接线引脚,并通过可塑性绝缘介质灌 封固定,构成整体立体结构的工艺技术。

集成电路封装概述

5.1.封面积比增大 5.2.在物理尺寸变小 5.3.有很好的兼容性 5.4. SIP可提供低功耗和低期 5.7.有良好的抗机械和化学侵害的能力以及高可靠 性 返回

集成电路封装概述

6. SIP综合运用现有的芯片资源及多种先进封装技术的优势, 有机结合起来由几个芯片组成的系统构筑而成的封装,开 拓了一种低成本系统集成的可行思路与方法,较好地解决 了SOC中诸如工艺兼容、信号混合、电磁干扰EMI、芯片 体积、开发成本等问题,在移动通信、蓝牙模块、网络设 备、计算机及外设、数码产品、图像传感器等方面有很大 的市场需求量。所Semico公司报道,世界SIP营销收入将 从2002年的8200万美元增长到2007年的7.48亿美元, 年均增长率达55.6%。日本新近预测,2007年世界有关 应用SIP技术的LSI市场可望达1.2万亿日元,这是根据同 期系统LSI的1/5可利用SIP技术计算而得的。

集成电路封测简介介绍

深入研究失效机理,找出失效原因,为改进设计 提供依据。

失效预防

根据失效分析结果,采取相应的预防措施,提高 集成电路的可靠性和稳定性。

03

集成电路封测流程

封装设计

封装设计是集成电路封测流程的起始 阶段,主要任务是根据集成电路的规 格和性能要求,设计出合适的封装结 构和尺寸。

封装设计通常使用专业设计软件进行 ,设计过程中需要进行仿真和优化, 以确保设计的可行性和可靠性。

测试技术

功能测试

通过模拟输入信号,检测 集成电路的输出信号是否 符合预期,以判断其功能 是否正常。

性能测试

在特定条件下测试集成电 路的各项性能指标,如功 耗、频率、延迟等,以评 估其性能优劣。

可靠性测试

通过长时间、高强度的使 用或模拟恶劣环境条件下 的测试,评估集成电路的 可靠性。

可靠性分析

环境适应性

分析集成电路在不同温度、湿度 、气压等环境条件下的性能表现

和稳定性。

寿命预测

通过加速老化试验等方法预测集 成电路的使用寿命,为产品设计

提供依据。

可靠性评估

根据测试数据和实际使用情况, 评估集成电路的可靠性水平,为

产品可靠性设计提供依据。

失效分析

失效模式识别

通过外观检查、电性能测试等手段,识别出集成 电路的各种失效模式。

集成电路封测技术对于飞行控制系统至关重要,确保飞机在 各种环境和条件下都能够安全、稳定地飞行。

05

集成电路封测的挑战与解决方 案

技术更新换代

总结词

随着集成电路技术的不断进步,封测 技术需要不断更新换代,以满足更高 的性能和可靠性要求。

详细描述

随着芯片制程技术的不断缩小,封测 技术需要不断改进和升级,以满足更 精细的封装和测试需求。这涉及到新 的封装材料、更先进的测试设备和方 法等方面的研发和应用。

集成电路封装举例说明

集成电路封装举例说明

集成电路封装是将多个电子元件集中在一起,通过封装形成一个完整的功能模块。

它在电子设备中起到连接、保护和提供电气连接的作用。

下面举例说明几种常见的集成电路封装类型:

1. 双列直插封装(DIP):这种封装形式是早期集成电路常见的一种封装方式。

其特点是具有两列金属引脚,通过插入到插座或焊接到电路板上进行连接。

它广泛应用于诸如存储芯片、逻辑芯片和模拟电路的集成电路。

2. 表面贴装技术(SMT):SMT是一种现代的集成电路封装技术,通过焊接

贴装到印刷电路板(PCB)上。

SMT封装常常以薄片形式存在,可以有效地提高

电路板的布局密度。

常见的SMT封装类型有QFP(方形扁平封装)、BGA(球栅

阵列封装)和SOP(小外形封装)等。

3. 裸片封装(Wafer-level Packaging):裸片封装是一种先进的集成电路封装技术,其封装过程发生在硅片被锯开之前。

在这种封装技术中,集成电路芯片直接在硅片上封装,有效提高了尺寸和成本的优势。

裸片封装被广泛应用于移动设备、计算机芯片和图像传感器等。

4. 三维封装(3D Packaging):三维封装是指将多个集成电路堆叠在一起,实

现更高的集成度和性能。

这种封装技术通过垂直堆叠多个封装层,可以在占地面积相同的情况下实现更多的功能。

三维封装适用于高性能计算、通信和互联网 of Things (IoT) 等领域。

总之,集成电路的封装类型多种多样,各有其适用的场景和特点。

通过选择合

适的封装方式,可以有效提高电子设备的性能、可靠性和布局密度。

集成电路封装与测试技术

集成电路封装与测试技术随着信息技术的快速发展和应用的广泛普及,集成电路在现代社会中扮演着重要的角色。

而集成电路封装与测试技术作为集成电路制造的重要环节,对于电子产品的性能、可靠性和稳定性起着至关重要的作用。

本文将介绍集成电路封装与测试技术的基本概念、重要性以及相关的发展趋势。

一、集成电路封装技术1.1 封装技术的定义与作用集成电路封装技术是将裸片芯片进行外包装,以提供对芯片的保护、连接和便于插拔。

其主要目标是保证芯片的电性能、机械可靠性和环境适应性,同时满足产品的体积、功耗和成本要求。

1.2 封装技术的分类根据不同的封装方式和结构,集成电路封装技术可以分为裸片封装、芯片级封装和模块级封装等多种形式。

其中,裸片封装是指将芯片直接粘贴在PCB板上,不进行封装的方式;芯片级封装是将芯片封装成单芯片或多芯片封装;模块级封装是将集成电路芯片与其他元器件进行封装。

1.3 封装技术的发展趋势随着集成电路的功能不断增强和尺寸不断缩小,封装技术也在不断创新与发展。

目前,多芯片封装、三维封装、无线封装等是集成电路封装技术的研究热点与发展方向。

这些新技术的应用将进一步提高集成电路的性能和可靠性。

二、集成电路测试技术2.1 测试技术的定义与作用集成电路测试技术是对封装好的集成电路芯片进行功能、电性能和可靠性等方面的验证和测试。

通过测试可以确保芯片的质量和性能符合设计要求,提高产品的可靠性和稳定性。

2.2 测试技术的分类根据不同的测试目的和方法,集成电路测试技术可以分为芯片测试、模块测试和系统测试等多种形式。

其中,芯片测试是对单个芯片进行测试,模块测试是对芯片封装后的模块进行测试,系统测试是对整个集成电路系统进行测试。

2.3 测试技术的发展趋势随着集成电路的复杂度不断提高,传统的测试技术已经无法满足需求。

因此,新型测试技术如板级测试、全片测试、MEMS测试等正在逐渐发展起来。

这些新技术的应用将提高测试效率、降低测试成本,并能同时满足不同级别的测试需求。

集成电路封装介绍

集成电路封装介绍

封装集成电路

封装集成电路(Package Integrated Circuit,简称PIC),是将集

成电路(Integrated Circuit,简称IC)封装成有形的组件,它可以安

装在微机或其他电子设备上,从而发挥其功能的一种电子元件。

封装集成

电路是在技术发展中发挥着不可替代的作用,特别在早期的示波器、计算

机中,它都发挥着重要的功能。

封装集成电路可以分为三类:平板封装集成电路,模块封装集成电路

和板上封装集成电路。

1、平板封装集成电路

平板封装集成电路是最常用的封装方式,它采用矩形底座,上面安装

引脚,除此之外还有抗表面电容、抗表面电阻等组件,芯片直接安装在底

座上,然后将相关的接线组件安装在底座上,使其具有可靠性和耐用性。

2、模块封装集成电路

模块封装集成电路采用整体结构,底座和芯片及其相关部件,如滤波器、电容器、变频器、电感器等,均采用封装的方式,整体结构更加紧凑,而且安装方法更加方便,因此,模块封装集成电路在技术上具有良好的性能,已经大量地应用于各种设备中。

3、板上封装集成电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

封装外观尺寸

TSOP II 54LD内部构造 内部构造

A6 A2 DS A5 A7

A5

Items

Thickness (mm) Nominal 1.000 0.127 Alloy 42 0.279 0.100 0.050 0.210 0.254 0.238

Thickness (mils) 39.37 5 A42 11 4 2 8 10 9.37

Die(Chip)

俯视图

Gold Wire L/F Pad Epoxy Inner Lead Die

正视图

工艺流程(前道工艺) 工艺流程(前道工艺)

打线结合(Wire Bonding)

主要工艺参数: • ball shear test • wire pull test • ball bond size • Ball placement • Pad Cractering Test • Loop Height Test • Reject(see PBI reject criteria) 见下页图示 打线后图片 设备与材料: 1. 打线机 2. 金线 3. 劈刀 主要机器参数: 1. 超声波功率 2. 焊接压力 3. 焊接持续的时间 4. 焊接温度

银胶

框架

胶带

固化 传统银胶粘结工艺

加热 固化 胶带粘结工艺

工艺流程(前道工艺) 工艺流程(前道工艺)

晶片粘结(Die Bonding) 银胶 芯片

框架焊盘

Fillet height BLT

Die Tilt

Y2

芯片

主要工艺参数: 1. BLT 2. Die tilt 3. Fillet height 4. Wetting 5. Die placement 6. Die shear

Marking (打字)

Testing (測試)

製造完成

三種不同的連接方式

Wire Bonding

TAB Bonding

Flip Chip Bonding

封 裝 之 目 的

傳統之構裝 1. 保護元件 2. 連接 3. 散熱 4. 協助測試 從現在起 1. 電子連接與隔離 2. I/O 位置標準化 3. 散熱 4. 協助測試 5. 保護元件

什么是电子封裝

电子封装乃是将前制程加工完成后所提供晶圆中之每一顆IC晶粒独立分离, 并外接信号线至导线架上而予以包覆,使其最終形成與外界電源相連之通路。

名詞簡釋

Wafer(晶圓):外觀為一圓薄盤,底材為Si,一面長有微細電路 Die, Chip(晶粒): 呈方形,附於wafer上互相連接,每個之間均隔 有寬線(切割道),排列如下

Prepared by:Peng xu dong

主要内容

内容: 内容:

封装外观尺寸 TSOP II 54LD的内部构造 工艺流程 前道工艺 贴膜 WTP 研磨 GRD 抛光 Polish 上片 W-M 揭膜 WDP 目检 V-I 切割 SAW 清洗 DWC 紫外线照射 U-V 切割后检查 PSI 晶片粘结 DBD 银胶固化 CRG 打线结合 WBD 打线后检查 PBI 后道工艺 塑封 MLD 塑封后固化 PMC 背印 BMK 正印 PTP 切筋 TRM 电镀 SDP 电镀后烘烤 APB 切筋成型 T-F 引脚检查 LSI 烘烤(去湿) UBK 最终目检 FVI 包装 P-K 出货检查 OQC 入库 W-H

封装制程简介

IC产业体系

设备仪器 資金人力資源

CAD

逻辑设计

光罩设计 光罩设计

晶粒测试及切割 晶粒测试及切割 测试

封 裝

成品测试 成品测试

服务支援

CAE

设计

光罩

制造

封裝

测试

货运 海关 材料

长 晶 晶圆切割

导线架 导线架 化学品

晶圆

科学圆区 • • •

Wire, Solder, Tape, Underfill Material

工艺流程(前道工艺) 工艺流程(前道工艺)

*选项: 晶圆背面抛光(POLISHING)

抛光轮 背面

设备与材料: 1. 抛光机 2. 抛光轮 3. 抛光剂 4. 去离子水 主要控制参数: 1. 主轴转速 2. 吸盘转速 3. 抛光步骤 4. 抛光压力 5. 抛光时间 6. 抛光剂流量

晶圆

真空吸盘

定义:抛光研磨过的晶圆背面 目的:减少晶圆研磨时产生的加工应力。 主要失效: 1. 晶圆碎裂 (wafer broken) 2. 边缘破损(edge chipping) 收集数据: 1. 表面粗糙度 2. 表面平整度 3. 最终厚度

• 低成本/高可靠度 • 小而薄之塑膠構裝

• 元件至最後系統 • 模擬與評估 • 給與最佳之封裝組合

封 裝

型

式

資料來源:Michael Pecht, “Integrated Circuit, Hybrid, and Multichip Module Package Design Guidelines,” pp. 50-51

工艺流程(前道工艺) 工艺流程(前道工艺)

打线结合(Wire Bonding)

Loop Height 拉力 Wire pull test

推力

Ball shear test Y2 X2 Y1 X1

Ball placement X=(X2-X1)/2 Ball placement Y=(Y2-Y1)/2

X1

银胶 所有兰色区 域为 Wetting

X2

Die placement X=(X2-X1)/2 Die placement Y=(Y2-Y1)/2

Y1

工艺流程(前道工艺) 工艺流程(前道工艺)

打线结合(Wire Bonding)

Tie Bar Wb Simulation Bonding Pad

Microsoft PowerPoint 演示文演

工艺流程(前道工艺) 工艺流程(前道工艺)

目检(V-I)

定义:研磨后检查 目的:检查研磨质量 检查主要内容: 1. 晶圆厚度 2. 研磨(抛光)后晶圆粗糙度 3. 废品 设备与材料: 1. 厚度测量仪 2. 粗糙度测量仪 3. 显微镜 主要控制参数: NA

工艺流程(前道工艺) 工艺流程(前道工艺)

Ball placement test

工艺流程(前道工艺) 工艺流程(前道工艺)

工艺流程(前道工艺) 工艺流程(前道工艺)

切割后检查(PSI)

检查主要内容: 1. 晶圆mount方向是否与键合图一致 2. 芯片名称,芯片ID是否与键合图所示相符 3. 废品 1. 刮痕 Scratch 2. 腐蚀 Pad Corrosion 3. 金属镀层的短路 Metallization bridging 4. 刮划 Scribe 5. 裂纹 Crack 6. 碎片 Chipping 7. 金属镀层的附着 Metallization adherence 8. 金属镀层的气孔 Metallization void 9. 玻璃钝化保护层失效 Glassivation defect 10. 外来物质Foreign material 设备与材料: 1. 高倍显微镜 主要控制参数: NA

工艺流程(前道工艺) 工艺流程(前道工艺)

晶圆表面贴膜(WTP)

背面 晶圆

设备与材料: 1. 贴膜机:待定 2. 胶带:待定 主要控制参数: 1. 贴膜压力 2. 贴膜速度 3. 贴膜温度

保护膜

正面

定义:在晶圆的表面贴上一层保护膜 目的:在晶圆背部研磨过程中,对晶圆表面电路提供保护 主要失效: 1. 切割毛边 (cut burr) 2. 双层胶带(double tape) 3. 胶带脱落(tape peeling) 4. 外来物(F/M under protective tape ) 5. 气泡(Bubble )

工艺流程(前道工艺) 工艺流程(前道工艺)

晶片粘结(Die Bonding)

设备与材料: 1. 粘片机 DBD Simulation 2. 银胶/胶带 Microsoft PowerPoint 演示文演 3. 框架 4. 吸嘴 5. 顶针 主要机器参数: 1. 拣片力 2. 粘结力 3. 粘结时间 4. 拣片时间 5. 粘结温度 6. 点胶压力 7. 顶针速度 8. 顶针高度

工艺流程背面研磨(GRD)

研磨轮 背面

设备与材料: 1. 研磨机 2. 研磨轮 3. 去离子水 主要控制参数: 1. 主轴转速 2. 吸盘转速 3. 进给速度 4. 晶圆初始厚度 5. 晶圆目标厚度 6. 粗磨量 7. 精磨量

晶圆

真空吸盘

定义:研磨晶圆的背面,减薄晶圆厚度 目的:根据封装尺寸要求,减薄晶圆厚度到芯片 规定厚度 主要失效: 1. 晶圆碎裂 (wafer broken) 2. 边缘破损(edge chipping) 收集数据: 1. 表面粗糙度 2. 表面平整度 3. 最终厚度

工艺流程(前道工艺) 工艺流程(前道工艺)

上片(W-M)

晶圆框架 晶圆

背面 晶圆 晶圆框架 真空吸盘 侧面图(示意图) 正面图 晶圆框架

设备与材料: 1. 上片机 2. 滚轮 3. 胶带 主要控制参数: 1. 上片压力 2. 上片速度 3. 上片温度 上片后图片

定义:在晶圆背面贴一层膜把晶圆固定在晶圆框 架上。 目的:便于芯片切割和芯片焊接。 主要失效: 1. 气泡 (bubble) 2. 外来物(F/M under protective tape )

Figure. Packaging Evolution

Packaging Evolution

Figure. Single-Chip Packaging Evolution leading to Multichip Packaging

IC 元 件 和 封 裝 趨 勢

TSOP封装流程介绍 封装流程介绍

A5 A3