半导体量测设备及应用介绍_201309

半导体和测试设备介绍

半导体和测试设备介绍半导体是一种电子材料,通常由硅、锗等元素组成,具有导电性能介于导体和绝缘体之间。

它的特点是可以在特定条件下控制电流的流动,主要应用在电子器件如晶体管、集成电路等中。

半导体的发展可以追溯到20世纪50年代开始的晶体管时代,随后发展为20世纪60年代的集成电路时代,再到21世纪的芯片时代。

半导体技术的进步使得电子产品变得更小、更快、更强大,成为现代科技和信息技术发展的关键驱动力。

半导体的制造过程非常复杂,需要经过多个步骤,包括晶圆制备、掩膜制造、曝光、蚀刻、沉积、刻蚀、清洗等。

这些步骤需要精密的设备和工艺控制,以保证半导体器件的质量和性能。

为了确保半导体器件的质量和性能,需要进行严格的测试。

测试设备是用于对半导体器件进行电性能、可靠性和参数测试的设备。

测试设备可以分为芯片测试设备和封装测试设备两类。

芯片测试设备用于测试独立芯片的电性能和参数。

它通常由测试头和测试座椅组成,测试头用于与芯片的测试接点连接,而测试座椅则用于稳定测试头和芯片的相对位置。

芯片测试设备可以通过高精度的测试仪器对芯片进行电流、电压、频率等多种电性能和参数进行测试,以验证芯片的质量和性能。

封装测试设备用于测试封装后的芯片或电子器件的电性能和可靠性。

这些封装测试设备通常包括测试座椅、测试引脚、测试仪器等。

测试座椅用于固定测试引脚和电子器件,测试引脚用于连接测试仪器和电子器件的引脚,测试仪器则用于测量电流、电压、功率等电性能和参数。

封装测试设备可以对整个芯片或电子器件进行全面的电性能和可靠性测试,以保证它们能够正常工作和长时间稳定运行。

除了芯片和封装测试设备,还有一些其他的测试设备也非常重要。

例如,绝缘测试设备用于测试半导体器件的绝缘性能,温度测试设备用于测试半导体器件在不同温度下的电性能,可靠性测试设备用于测试半导体器件的可靠性和寿命等。

这些测试设备能够对半导体器件进行全方位的测试,为其在不同应用场景中提供可靠的性能和质量保证。

半导体探测器应用场景

半导体探测器应用场景

半导体探测器是一种能够探测并测量辐射的设备,其应用场景

非常广泛。

从医疗影像到科学研究,从安全检测到空间探索,半导

体探测器都发挥着重要的作用。

在医疗领域,半导体探测器被广泛应用于放射性药物的诊断和

治疗。

例如,PET(正电子发射断层扫描)技术利用半导体探测器来

探测放射性同位素的发射,从而为医生提供了非常精确的身体组织

影像。

此外,X射线和γ射线探测器也是医院常见的设备,用于检

测骨折、肿瘤和其他疾病的诊断。

在科学研究领域,半导体探测器被广泛用于粒子物理实验、核

物理实验和天体物理实验。

例如,大型强子对撞机(LHC)实验中使

用的探测器就包括半导体探测器,用于测量高能粒子的轨迹和能量。

在安全检测领域,半导体探测器被用于辐射监测和核材料检测。

例如,在核电站和辐射治疗设施中,半导体探测器被用于监测辐射

水平,确保工作人员和公众的安全。

在空间探索领域,半导体探测器也发挥着重要作用。

例如,火

星探测器和卫星上携带的探测器用于测量太阳辐射、宇宙射线和行星表面的辐射情况,为科学家提供了宝贵的数据。

总的来说,半导体探测器在医疗、科学研究、安全检测和空间探索等领域都有着重要的应用场景,为人类社会的发展和进步做出了重要贡献。

随着技术的不断进步,相信半导体探测器的应用范围还会不断扩大,为人类带来更多的福祉和进步。

半导体行业对外测试设备介绍

半导体行业对外测试设备介绍首先,半导体行业对外测试设备中最常见的是测试工作站。

测试工作站是一个高度集成的自动化系统,用于对芯片和集成电路进行功能测试、可靠性测试和质量控制。

测试工作站通常由测试座、设备接口、测试探针、测量设备和自动控制系统等组成。

它能够通过电子探针或射频传感器对芯片进行信号采集和分析,以验证芯片的工作性能和电气特性。

其次,多功能测试系统也是半导体行业常用的对外测试设备之一、多功能测试系统集成了多个测试功能,并具备高度自动化和灵活性。

它可以进行芯片的功能测试、温度测试、电流测试、功耗测试、射频测试等多种测试。

多功能测试系统通常由测试仪器、测试软件和设备控制系统组成,可以在高速度和高精度下进行测试。

除了测试工作站和多功能测试系统,还有其他一些对外测试设备也被广泛应用于半导体行业。

例如,测试机械臂是一种能够对芯片进行自动加载和卸载的设备,可以提高测试效率和减少人工操作。

测试探针站是一种用于安装和更换测试探针的设备,它能够快速准确地完成测试探针的组装和拆卸。

测试封装设备是一种用于对芯片进行封装测试的设备,可以测试芯片的机械强度、封装完整性和封装结构等性能。

除了这些设备,还有一些专门用于特定测试的设备在半导体行业中应用广泛。

例如,红外热像仪用于测试芯片的温度分布和热特性;X射线检测仪用于检测芯片的封装完整性和焊点接触性能;电子显微镜用于对芯片表面和细微结构进行检查和分析。

总之,半导体行业对外测试设备是进行芯片和集成电路测试的重要工具。

这些设备的应用可以提高测试效率和测试精度,保证产品质量和可靠性。

随着半导体技术的不断进步,对外测试设备也将继续发展和创新,以适应半导体行业的需求。

教你认识半导体与测试设备(doc 14页)

教你认识半导体与测试设备(doc 14页)更多企业学院:《中小企业管理全能版》183套讲座+89700份资料《总经理、高层管理》49套讲座+16388份资料《中层管理学院》46套讲座+6020份资料《国学智慧、易经》46套讲座《人力资源学院》56套讲座+27123份资料《各阶段员工培训学院》77套讲座+ 324份资料《员工管理企业学院》67套讲座+ 8720份资料《工厂生产管理学院》52套讲座+ 13920份资料《财务管理学院》53套讲座+ 17945份资料《销售经理学院》56套讲座+ 14350份资料《销售人员培训学院》72套讲座+ 4879份资料第一章.认识半导体和测试设备(1)本章节包括以下内容,●晶圆(Wafers)、晶片(Dice)和封装(Packages)●自动测试设备(ATE)的总体认识●模拟、数字和存储器测试等系统的介绍●负载板(Loadboards)、探测机(Probers)、机械手(Handlers)和温度控制单元(Temperature units)一、晶圆、晶片和封装1947年,第一只晶体管的诞生标志着半导体工业的开始,从那时起,半导体生产和制造技术变得越来越重要。

以前许多单个的晶体管现在可以互联加工成一种复杂的集成的电路形式,这就是半导体工业目前正在制造的称之为"超大规模"(VLSI,Very Large Scale Integration)的集成电路,通常包含上百万甚至上千万门晶体管。

半导体电路最初是以晶圆形式制造出来的。

晶圆是一个圆形的硅片,在这个半导体的基础之上,建立了许多独立的单个的电路;一片晶圆上这种单个的电路被称为die(我前面翻译成"晶片",不一定准确,大家还是称之为die好了),它的复数形式是dice.每个die都是一第一章.认识半导体和测试设备(3)二、自动测试设备随着集成电路复杂度的提高,其测试的复杂度也随之水涨船高,一些器件的测试成本甚至占到了芯片成本的大部分。

半导体晶圆量检测设备行业_概述及解释说明

半导体晶圆量检测设备行业概述及解释说明1. 引言1.1 概述半导体晶圆量检测设备是半导体制造过程中至关重要的工具,用于对晶圆进行质量检测和性能评估。

随着半导体技术的快速发展和需求的不断增长,半导体晶圆量检测设备行业也得到了迅猛发展。

该行业主要涉及各种技术和设备,主要用于监测和分析晶圆表面的特征、缺陷、杂质等,并帮助生产商控制生产过程、提高产品可靠性以及改进产品设计。

这些设备可以通过非接触式或接触式方式对晶圆进行扫描和测试,然后生成相应的评估报告或数据。

1.2 文章结构本文将全面介绍半导体晶圆量检测设备行业,并深入探讨其原理、分类以及作用。

文章共分为以下几个部分:- 引言:对本文的目的和内容进行简要介绍。

- 半导体晶圆量检测设备行业概述:介绍该行业的背景、技术发展趋势以及市场规模与增长预测。

- 半导体晶圆量检测设备原理与分类:详细讨论该设备的基本原理、主要组成部分以及各种分类和应用领域。

- 半导体晶圆量检测设备的重要性和作用:探讨该设备在质量控制、成本降低和技术竞争力增强等方面的重要性和作用。

- 结论:总结研究内容,展望半导体晶圆量检测设备行业未来发展,并提出进一步研究或改进的建议。

1.3 目的本文旨在全面了解半导体晶圆量检测设备行业,在介绍其概况、原理、分类以及作用的同时,探讨其对半导体制造过程中产品质量控制、生产效率提高以及创新能力提升等方面的重要意义。

通过全面了解该行业,我们可以更好地认识到半导体晶圆量检测设备对于整个半导体产业链的重大贡献,并为未来的研究和发展提供有益参考。

2. 半导体晶圆量检测设备行业概述:2.1 行业背景半导体晶圆量检测设备行业是半导体制造过程中的关键领域之一。

随着科技的不断进步和信息产业的高速发展,半导体行业的需求不断增加,使得晶圆量检测设备市场逐渐兴起。

这些设备广泛应用于芯片制造工艺中,帮助提高产品质量、降低生产成本以及增加生产效率。

2.2 技术发展趋势半导体晶圆量检测设备行业面临着快速变化的技术发展趋势。

半导体式检测仪使用方法

半导体式检测仪使用方法全文共四篇示例,供读者参考第一篇示例:半导体式检测仪使用方法在现代科技的发展和应用中,半导体式检测仪起着举足轻重的作用。

它能够帮助我们准确、高效地检测各种材料的性能、结构和组分,为科学研究、医学诊断、环境监测等领域提供重要支持。

对于初次使用半导体式检测仪的人来说,可能会觉得操作复杂,不知从何入手。

下面将介绍一下关于半导体式检测仪的使用方法,希望对大家有所帮助。

一、准备工作在使用半导体式检测仪之前,首先需要对仪器本身进行一些准备工作。

确认仪器的电源已经连接,并处于正常工作状态。

然后,检查仪器的探头是否安装牢固,探头外部是否有损坏,以及连接线是否完好。

打开仪器的开关,等待仪器进行自检,确保一切正常后再进行操作。

二、调整参数在使用半导体式检测仪时,需要根据实际需要调整一些参数,以确保检测结果的准确性和可靠性。

首先是选择合适的检测模式,根据被测物质的性质和检测目的选择合适的检测模式。

其次是设置检测范围和灵敏度,根据被测物质的浓度和要求,选择合适的检测范围和灵敏度。

最后是校准仪器,根据需要对仪器进行校准,确保检测结果的准确性。

三、实施检测在调整参数完成后,就可以进行实际的检测工作了。

将仪器的探头对准被测物质,确保探头和被测物质的接触良好。

然后,按下检测按钮,开始进行检测。

在检测过程中,注意观察仪器的显示,根据显示结果进行分析和判断。

注意检测过程中可能出现的异常情况,如高温、湿度等,及时处理。

四、分析结果在检测完成后,需要对检测结果进行分析和判断。

首先是对检测数据进行处理,根据需求对数据进行整理和分析。

然后是对检测结果进行解读,根据实际情况进行判断,并做出相应的处理和决策。

最后是将检测结果记录下来,保存在合适的地方,方便日后查阅和对比。

五、维护保养在使用半导体式检测仪过程中,需要注意对仪器的维护保养工作。

首先是定期清洁仪器,保持仪器的清洁和干燥。

其次是定期校准仪器,确保仪器的稳定性和准确性。

半导体测试仪

• 半导体产业链包括设计、制造、封装、测试等环节 • 测试仪在测试环节中对器件性能进行全面评估 • 合格的半导体器件对整个电子产业的正常运行至关重要

半导体测试仪的发展历程

20世纪50年代,半导体测试仪开始 出现

20世纪80年代,半导 体测试仪进入数字化时

代

21世纪初,半导体测 试仪向高精度、高速、

交流测试仪器的应用领域

• 变压器、电感、电容等器件的测试 • 电动机、发电机、变频器等设备的测试 • 电力系统、通信设备的测试

射频测试仪器的特点与应用

射频测试仪器主要用于测试半导体器件的射频性能

• 射频性能包括频率、功率、增益等参数 • 射频测试仪器具有较高的精度和稳定性,适用于对性能要求较高的场景

半导体测试仪的性能和水平直接影响半导体产品的质量

• 高性能的测试仪可以更准确地评估器件性能,筛选出不良品 • 低性能的测试仪可能导致不合格产品流入市场,影响电子产品质量 • 因此,半导体测试仪在半导体产业链中具有举足轻重的地位

02

半导体测试仪的分类及特点

直流测试仪器的特点与应用

直流测试仪器主要用于测试半导体器件的直流性能

• 直流性能包括电压、电流、电阻等参数 • 直流测试仪器具有较高的精度和稳定性,适用于对性能要求较高的场景

直流测试仪器的应用领域

• 集成电路的测试 • 晶体管、二极管的测试 • 电池、电源模块的测试

交流测试仪器的特点与应用

交流测试仪器主要用于测试半导体器件的交流性能

• 交流性能包括电压、电流、功率等参数 • 交流测试仪器具有较高的精度和稳定性,适用于对性能要求较高的场景

半导体测试仪器行业的发展机遇

半导体和测试设备介绍

半导体和测试设备介绍1. 引言半导体是一种电子材料,具有不同于导体和绝缘体的特性。

它具有介于导体和绝缘体之间的电导率,因为它的导电性依赖于温度、外界控制和掺杂等因素。

而测试设备是用于测试半导体器件的工具和设备,旨在确保半导体器件在生产过程中的可靠性和质量。

本文将介绍半导体的基本原理和分类,并详细介绍常见的测试设备及其作用。

2. 半导体基本原理半导体是由p型(正型)和n型(负型)材料组成的。

p型半导体中的杂质含有能够捕获自由电子的不足电子,而n型材料中的杂质含有能够提供额外电子的不足电子。

当p型和n型的半导体材料接触时,电子将从n型材料中流向p型材料,从而形成结。

这种结构被称为pn结,是半导体器件的核心组成部分。

3. 半导体分类半导体可以分为两类:元素半导体和化合物半导体。

元素半导体是由单一的化学元素组成,如硅(Si)和锗(Ge)。

化合物半导体则由两种或更多的化学元素组成,如砷化镓(GaAs)和砷化铟(InAs)。

除了按照成分分类,半导体还可以根据其电导性分类。

根据电子在半导体中的运动方式,半导体可分为p型半导体和n型半导体。

p型半导体中的电导主要由空穴(缺少电子的位置)贡献,而n型半导体中的电导则主要由自由电子贡献。

4. 测试设备介绍4.1. 电测设备电测设备用于测试半导体器件的电性能,其中包括电流、电压、电阻等参数。

常见的电测设备包括万用表、示波器和信号发生器。

•万用表:用于测量电流、电压、电阻、电容等参数。

它是一种便携式的测试仪器,常用于检测电路中的问题和验证电子元件的参数。

•示波器:用于显示电信号的波形,可以帮助分析和测量电路中的信号特性。

示波器通常具有高速、高分辨率和多通道功能,适用于复杂的电子设备测试。

•信号发生器:用于产生不同波形和频率的信号,在半导体器件测试中用于模拟各种输入信号。

4.2. 热测设备热测设备用于测试半导体器件的热性能,包括温度、热导率等参数。

常见的热测设备包括热电偶、热像仪和热电池。

半导体行业对外测试设备介绍

半导体行业对外测试设备介绍半导体行业是指从事半导体材料、半导体器件制造、集成电路设计和制造等相关领域的产业链。

在半导体制造过程中,对外测试设备起到了至关重要的作用,能够对半导体产品进行全面、稳定的测试和评估。

本文将对半导体行业中常用的对外测试设备进行介绍。

1.IC测试设备IC测试设备主要用于对集成电路芯片的功能、可靠性等进行测试。

这些设备通常由测试主机、探针卡/测试卡以及相关软件组成。

测试主机负责与芯片的输入输出接口进行连接,并通过控制信号和数据进行测试。

探针卡/测试卡则用于实现对芯片引脚的电气连接和信号采集。

相关软件用于设置测试参数、记录测试结果并进行数据分析。

常见的IC测试设备包括:逻辑分析仪、信号发生器、频谱分析仪等。

2.半导体分析仪半导体分析仪用于对半导体材料、晶片进行结构表征和性能测试。

主要功能包括电学特性测试、光学特性测试、热学特性测试、显微镜观察等。

常见的半导体分析仪有扫描电子显微镜(SEM)、透射电子显微镜(TEM)、拉曼光谱仪、X射线衍射仪等。

3.封装测试设备封装测试设备主要用于对已封装好的芯片进行功能测试和可靠性评估。

封装测试设备通常包括测试针床、测试插座、电路板、探针接头以及相关软件。

测试针床和测试插座用于与芯片的引脚进行连接,电路板负责控制信号和数据的输入输出。

探针接头则用于将测试信号传输到芯片引脚上。

常见的封装测试设备包括:引导测试设备、无线通信测试设备、高速串行测试设备等。

4.温度测试设备温度测试设备主要用于对半导体产品在不同温度下的性能进行测试。

温度测试设备通常由温度控制器、温度传感器、测试夹具等组成。

温度控制器用于控制测试环境的温度,温度传感器用于实时检测温度变化,测试夹具则用于固定和连接被测试器件。

常见的温度测试设备包括:快速热冷温度循环测试仪、高低温试验箱等。

5.故障分析设备故障分析设备主要用于对半导体产品出现的故障进行定位和分析。

故障分析设备通常由故障分析仪、探针仪、电子显微镜等组成。

半导体测试设备简介演示

通过对半导体器件进行测试,可 以确保其性能和质量符合设计要 求,为半导体产业的发展提供有 力支持。

半导体测试设备的重要性

确保产品质量

半导体测试设备能够准确检测半导体 器件的性能和质量,及时发现并处理 问题,确保产品的可靠性和稳定性。

提高生产效率

促进产业发展

半导体测试设备是半导体产业发展的 重要支撑,其技术的不断进步和创新 为半导体产业的发展提供了有力保障 。

THANKS

谢谢您的观看

要点三

主要厂商分析

应用材料公司、泛林集团、东京电子 等大型半导体设备厂商在市场上具有 较高的市场份额和影响力。这些厂商 在技术研发、产品创新、市场营销等 方面具有优势,能够为客户提供全面 的半导体测试解决方案。

未来展望

市场规模预测

技术发展趋势预测

市场机遇与挑战分析

随着半导体产业的持续发展,未来几 年半导体测试设备市场规模将继续保 持增长态势。同时,随着5G、物联网 、人工智能等新兴技术的快速发展, 半导体测试设备市场将迎来新的发展 机遇。

多样化

随着不同类型和规格的半导体器件 不断涌现,半导体测试设备需要具 备更强的适应性和可扩展性,以满 足不同应用场景的需求。

02

半导体测试设备分类与特点

静态参数测试设备

01

02

03

电压降测试

测量半导体器件的电压降 ,判断其性能。

电阻测试

测量半导体器件的电阻值 ,判断其导电性能。

电流测试

测量半导体器件的电流值 ,判断其导电性能。

业提供优质的测试服务。

04

半导体测试设备技术发展趋势 与挑战

技术发展趋势:高精度、高效率、高可靠性

高精度测试

半导体和测试设备介绍推荐文档

半导体和测试设备介绍(可以直接使用,可编辑优质资料,欢迎下载)第一章.认识半导体和测试设备(1)本章节包括以下内容,●晶圆(Wafers)、晶片(Dice)和封装(Packages)●自动测试设备(ATE)的总体认识●模拟、数字和存储器测试等系统的介绍●负载板(Loadboards)、探测机(Probers)、机械手(Handlers)和温度控制单元(Temperature units)一、晶圆、晶片和封装1947年,第一只晶体管的诞生标志着半导体工业的开始,从那时起,半导体生产和制造技术变得越来越重要。

以前许多单个的晶体管现在可以互联加工成一种复杂的集成的电路形式,这就是半导体工业目前正在制造的称之为"超大规模"(VLSI,Very Large Scale Integration)的集成电路,通常包含上百万甚至上千万门晶体管。

半导体电路最初是以晶圆形式制造出来的。

晶圆是一个圆形的硅片,在这个半导体的基础之上,建立了许多独立的单个的电路;一片晶圆上这种单个的电路被称为die(我前面翻译成"晶片",不一定准确,大家还是称之为die好了),它的复数形式是dice.每个die都是一个完整的电路,和其他的dice没有电路上的联系。

当制造过程完成,每个die都必须经过测试。

测试一片晶圆称为"Circuit probing"(即我们常说的CP测试)、"Wafer porbing"或者"Die sort"。

在这个过程中,每个die都被测试以确保它能基本满足器件的特征或设计规格书(Specification),通常包括电压、电流、时序和功能的验证。

如果某个die不符合规格书,那么它会被测试过程判为失效(fail),通常会用墨点将其标示出来(当然现在也可以通过Maping图来区分)。

在所有的die都被探测(Probed)之后,晶圆被切割成独立的dice,这就是常说的晶圆锯解,所有被标示为失效的die都报废(扔掉)。

半导体光电探测器的原理及其应用

半导体光电探测器摘要:本文介绍了光电与系统的组成、一些半导体光电探测器的工作原理及其特性,最后阐述了光电导探测器与光伏探测器的区别。

关键词:半导体光电探测器,光电系统,光电导探测器,光伏探测器引言光电探测器是一种受光器件,具有光电变换功能。

光敏器件的种类繁多,有光敏电阻、光电二极管、光电三极管、光晶闸管、集成光敏器件等;有雪崩型的及非雪崩型的;有PN结型、PIN结型及异质结型的等。

由于光电探测器的响应速度快,体积小,暗电流小,使之在光纤通讯系统、光纤测试系统、光纤传感器、光隔离器、彩电光纤传输、电视图象传输、快速光源的光探测器、微弱光信号的探测、激光测距仪的接收器件、高压电路中的光电测量及光电互感器、计算机数据传输、光电自动控制及光测量等方面得到了广泛应用。

半导体光电探测器是用半导体材料制作的能接收和探测光辐射的器件。

光照射到器件的光敏区时,它就能将光信号转变成电信号,是一种光电转换功能的测光元件。

它在国防和工农业生产中有着重要和广泛的应用。

半导体光电探测器可分为光电导型和光伏型两种。

光电导型是指各种半导体光电导管,即光敏电阻;光伏型包括光电池、P-N结光电二极管、PIN光电二级管、雪崩光电二极管、光电三级管等。

本文首先介绍了光电系统的组成,然后分别介绍其工作原理及其特性,最后将这两类探测器进行比较。

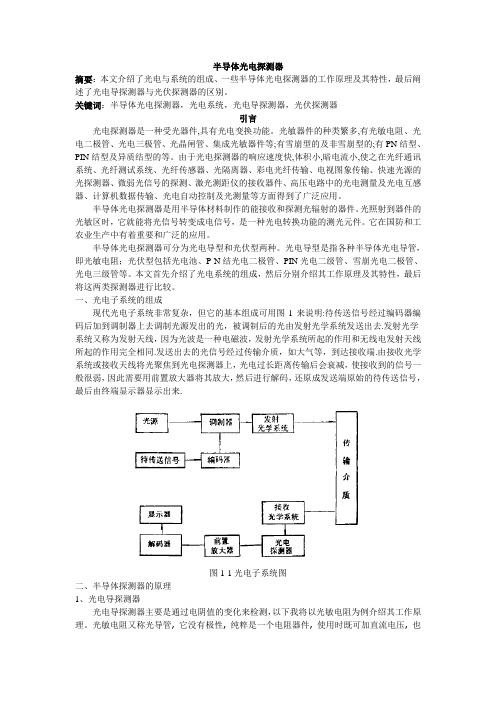

一、光电子系统的组成现代光电子系统非常复杂,但它的基本组成可用图l来说明:待传送信号经过编码器编码后加到调制器上去调制光源发出的光,被调制后的光由发射光学系统发送出去.发射光学系统又称为发射天线,因为光波是一种电磁波,发射光学系统所起的作用和无线电发射天线所起的作用完全相同.发送出去的光信号经过传输介质,如大气等,到达接收端.由接收光学系统或接收天线将光聚焦到光电探测器上,光电过长距离传输后会衰减,使接收到的信号一般很弱,因此需要用前置放大器将其放大,然后进行解码,还原成发送端原始的待传送信号,最后由终端显示器显示出来.图1-1光电子系统图二、半导体探测器的原理1、光电导探测器光电导探测器主要是通过电阴值的变化来检测,以下我将以光敏电阻为例介绍其工作原理。

半导体测试设备简介介绍

产业链协同发展

半导体测试设备与半导体产业链密切相关 ,随着整个产业链的协同发展,半导体测

试设备也将迎来更大的发展空间。

市场需求驱动发展

随着半导体市场的不断扩大,半导体测试 设备的需求也将不断增加,进一步推动其 发展。

国际化趋势

随着全球化的加速发展,半导体测试设备 也将逐渐走向国际化,与全球市场接轨, 为全球半导体产业提供更优质的服务。

测试流程

操作人员将待测芯片放置在探针台上,通过探针卡与测试主 机连接,然后运行测试程序,对芯片进行性能和功能测试。 测试完成后,测试结果会显示在显示模块上,操作人员可以 根据结果判断芯片是否合格。

04

半导体测试设备的选型与使用 注意事项

选型原则与依据

测试需求

根据产品特性、生产流程和测试要求,选择 适合的测试设备。

作用

通过对半导体器件进行测试,可 以确保其性能和质量符合设计要 求,为半导体产业的发展提供有 力支持。

半导体测试设备的重要性

确保产品质量

半导体测试设备能够准确检测半 导体器件的性能参数,及时发现 并处理潜在的问题,确保产品的

质量和可靠性。

提高生产效率

通过自动化测试和数据分析,半导 体测试设备可以大幅提高生产效率 ,降低生产成本。

推动产业发展

半导体测试设备在半导体产业的发 展中具有重要地位,为新产品的研 发、生产和应用提供了有力支持。

半导体测试设备的发展趋势

智能化

随着人工智能、机器学习等技术的发 展,半导体测试设备将越来越智能化 ,实现更高效、更精准的测试和分析 。

模块化与集成化

为了满足不同应用场景的需求,半导 体测试设备将更加模块化和集成化, 便于用户根据实际需求进行定制和扩 展。

教你认识半导体与测试设备

半导体测试设备行业将迎来更多的创 新和变革,推动整个行业的发展

添加标题

添加标题

添加标题

人工智能、大数据等技术在半导体测 试设备中的应用逐渐普及

未来半导体 增长的趋势

市场需求趋势

半导体测试设备市场需求持 续增长

高端产品需求不断扩大

行业技术水平不断提高

测试机

体

试机等

等

降

探针台原理与功能

探针台定义:一种用于测试半导体器件的设备,通过探针接触芯片上的电极,实现对芯片性能的测试

探针台原理:利用X、Y、Z三轴运动系统,将探针精准定位到芯片上的电极位置,通过探针与芯片 实现对芯片性能的测试。

探针台功能:可以对芯片进行快速、准确的测试,提高生产效率;同时,可以检测芯片的缺陷和故 产品质量。

分选机原理与功能

分选机的工作原理 分选机的功能特点 分选机在半导体测试中的应用

• 05

半导体测试设备应用领域

集成电路测试

集成电路测试设备概述

集成电路测试设备应用领域

集成电路测试设备分类及特点

微电子器件测试

测试目的:验证器件性能是否满足设计要求 测试方法:采用专业的测试设备对器件进行测试 测试内容:包括直流参数测试、交流参数测试、噪声测试等

化合物半导体测试

化合物半导体材料类型:GaAs、GaN、SiC等 化合物半导体测试设备应用领域:通信、电力电子、光电子等 化合物半导体测试设备特点:高精度、高稳定性、高可靠性

• 06

半导体测试设备市场现状与发展趋势

市场现状及竞争格局

市场规模及增长趋势

主要厂商及市场份额

竞争格局及合作模式

半导体温度计的原理和应用

半导体温度计的原理和应用1. 引言半导体温度计作为一种常见的温度测量设备,广泛应用于许多领域,如工业生产、医疗设备、电子产品等。

本文将介绍半导体温度计的工作原理和应用。

2. 半导体温度计的工作原理半导体温度计利用材料在温度变化时导电特性变化的原理来测量温度。

其工作原理可以简单描述如下:•负温度系数材料: 半导体温度计常使用负温度系数材料作为敏感元件。

在这些材料中,电阻值会随温度的升高而降低。

常见的负温度系数材料有硅(Si) 和锗 (Ge)。

•PN 结构: 半导体温度计采用PN结构。

当温度升高时,半导体材料中导电带的电子浓度增加,使半导体材料的电阻降低。

•电阻测量: 半导体温度计通过测量材料的电阻值来反映温度的变化。

一般通过建立一个电桥电路或利用差动放大电路来测量电阻值。

3. 半导体温度计的应用半导体温度计在各行各业都有广泛的应用。

以下列举了几个常见的应用领域:3.1 工业控制在工业控制系统中,半导体温度计常被用于监测和控制温度,例如炉温、热水器、空调等。

由于半导体温度计具有响应速度快、体积小、精确度高等优点,因此被广泛应用于各种工业控制环境中。

3.2 医疗设备半导体温度计也被广泛应用于医疗设备中,例如体温计和血液透析机。

相比传统的玻璃温度计或者RTD温度计,半导体温度计无需预热,响应时间快,能够提供更准确的温度测量结果。

3.3 电子产品在电子产品中,半导体温度计可以用来监测电子元器件的温度,以确保电路运行的稳定性和可靠性。

例如,计算机、手机、笔记本电脑等设备中常常会使用半导体温度计来监测CPU的温度,以避免过热引起的故障。

3.4 环境监测半导体温度计也可以用于环境监测领域,对空气、水、土壤等的温度进行测量。

通过收集和分析温度数据,可以提供环境监测和气候研究所需的信息。

3.5 汽车工业半导体温度计在汽车工业中具有重要的应用。

它们可以被用于测量发动机冷却剂的温度、车内温度等。

通过监测温度,可以提高汽车发动机的效能,保护车内乘客的安全与舒适。

半导体和测试设备介绍

半导体和测试设备介绍概述:半导体是一种在电子行业中广泛应用的材料,它具有介于导体和绝缘体之间的导电性能。

半导体能通过控制电流流动来实现各种电子设备的功能。

为了保证半导体产品的质量和性能,测试设备在半导体制造工艺中起着至关重要的作用。

测试设备可用于检测和评估半导体产品的特性和可靠性,以确保其符合规格和标准。

半导体:半导体材料基于其电传导性能和电阻特性可分为P型和N型半导体。

P型半导体具有正电荷的杂质,被称为“施主”,而N型半导体具有负电荷的杂质,被称为“受体”。

通过合并P型和N型半导体,可以创建PN 结构,形成二极管和其他半导体器件。

在半导体工艺中,使用化学气相沉积、物理气相沉积、离子注入和蒸发等技术进行材料的制备。

制造的半导体材料还需要经过切割、刻蚀、掺杂、清洗和涂层等工艺步骤,以形成最终的半导体器件。

半导体测试设备:1.测试仪器和设备:半导体测试仪器和设备用于检测和量化半导体器件的性能参数,如电流、电压、频率、容量等。

常见的测试仪器包括示波器、信号发生器、频谱仪、多用途测试设备等。

2.自动测试设备(ATE):自动测试设备是用于高速自动测试和分析半导体器件的设备。

它可以同时测试多个芯片,提高测试效率。

ATE可以执行各种测试,如直流、交流和混合信号测试,适用于集成电路、存储器和其他半导体器件。

3.封装测试设备:封装测试设备用于测试和验证封装后的半导体芯片。

这些设备可以检测封装的功能和可靠性,如引脚连通性、操作温度范围、应力测试等。

4.温度测试设备:温度测试设备用于评估半导体器件在不同温度条件下的工作特性和可靠性。

这些设备可以模拟各种温度环境,如高温、低温和温度循环,以评估器件的稳定性和寿命。

5.电子显微镜:电子显微镜用于观察和分析半导体器件的微观结构。

它可以提供高分辨率的图像,并帮助发现器件中的缺陷和故障。

6.系统级测试设备:系统级测试设备用于对整个电子系统进行测试和验证。

这些设备可以模拟实际使用条件下的工作环境,以评估系统的性能和可靠性。

半导体探测器课件

根据材料类型,半导体探测器可分为 元素半导体探测器和化合物半导体探 测器;根据工作温度,可分为常温探 测器和高温探测器。

应用领域

光电探测器在光通信 、光谱分析、激光雷 达等领域有广泛应用 ;

压阻式探测器在压力 、振动等测量领域有 广泛应用。

热探测器在红外成像 、环境监测等领域有 广泛应用;

02

制造工艺

01

02

03

薄膜沉积

通过物理或化学方法在衬 底上沉积所需的半导体薄 膜,是制造探测器的重要 步骤。

光刻与刻蚀

利用光刻技术将设计好的 电路图案转移到衬底上, 然后通过刻蚀技术将不需 要的材料去除。

掺杂与离子注入

通过掺杂或离子注入改变 半导体的导电性能,以实 现器件的功能。

封装技术

芯片级封装

半导体探测器技术

材料技术

硅材料

硅是最常用的半导体材料,具有 高纯度、高稳定性、低成本等优

点,广泛应用于探测器制造。

化合物半导体

化合物半导体材料如砷化镓、磷化 铟等具有较高的电子迁移率和光学 特性,常用于制造高性能探测器。

宽禁带半导体

如硅碳化物和氮化镓等宽禁带半导 体材料具有高热导率和大禁带宽度 等特点,适用于高功率和高频率探 测器。

响应信号的变化。

高灵敏度

由于其独特的材料特性和结构 设计,半导体探测器通常具有 很高的灵敏度,能够检测微弱 的信号。

小型化

随着技术的进步,半导体探测 器的尺寸越来越小,便于集成 和携带。

稳定性好

经过特殊处理和工艺制造,半 导体探测器具有较好的稳定性

,不易受环境因素的影响。

缺点

温度影响

某些半导体探测器会受到温度的影响 ,导致性能下降或漂移。

半导体量测设备应用流程

半导体量测设备应用流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!半导体量测设备应用流程主要包括以下几个步骤:1. 样品制备选择合适的半导体材料,并进行切割、研磨、抛光等处理,以获得平整、光滑的表面。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

M50

La se r

M50 I/O

Object

Driver

Encoder Stage

Slit Scanner

• Slit scanners are a direction extension of the basic triangulation principle

非接触三角法探头原理

Wafer Scanner

Features

High speed measurement of the height for solder bumps with high accuracy (±0.25µm @ aveó). Measuring range from 10 ~ 130µm height.

High-speed inspection by AOD (Acousto Optical Deflector), laser scanning, and triangulation. Input and processing height and brughtness informations at 7 megapoint/sec.

Realtine display for inspection results per chip.

Wafer Bump 3D Inspection System

• Wafer Bump 3D Inspection System Vi-Z800【Wafer Auto Handler】

Wafer Bump 3D Measurement

The 3D profiling technique is based on a newly developed optical interferometry, which has the world fastest measurement speed with sub-micron accuracy of height measurement.

Toray's Automatic Bump Inspection System Series

Specifications

ห้องสมุดไป่ตู้

Test Results

August Technology

Designed for highspeed bump and wafer inspection, the system incorporates the Company's patentpending threedimensional (3D) Rapid Confocal Sensor™, with proprietary twodimensional (2D) bump and active die inspection technologies to provide bump manufacturers with high-speed and high accuracy combined in a single bump inspection solution.

• Wafer Bump 3D Measurement

• Wafer Gold Bump Measurement Inspection / MEM-5296D

2D、3D、SD for Bumping检测设备

主要用途 ・具有高速及高精度测试Wafer Bump的功能 ・测试分辨力为0.1μm ・世界领先地位的生产能力 产品应用 ・缺陷检测功能 ・高精度Bump Height检测能力及再生产的功能 产品特色 1.高速的检测能力 2.提供有效的Off- Line Review功能 3.对客户端提供简易的操作使用系统 4.用独有的高精度激光变位传感器来实现高精度 的测试 ・采用微细激光线的排列 ・用PSD排列来达到高速测试 ・对高度和缺陷进行高精度的检测,实现了先进 的运算法则。 5.先进的信号处理系统 ・采用高速的A/D转换机板 ・运用DMA技术来实现先进的高速信号处理 ・测试画面清晰

半导体量测设备及应用介绍

陈贵荣 2013/09/11 E_mail : chen.kueijun@

芯片凸块制程检验

• 雷射扫瞄仍是目前凸块检测最广为使用的 三维量测技术

Failure Analysis_1

Failure Analysis_2

Examples of solder bump defect

ASE

Measuring Method: Triangulation by laser scanning.

IS-100 is high-speed inspection developed for area array bump inspection

Inspection object: Solder bump on the wafer. Handling: Cassette to cassette inspection. Result output: Realtime display per chip and also can be recorder on MO.

• Explain

高阶封装技术

• 300mm晶圆

高阶封装技术

• Wafer Bump

3D Bump Inspection using Laser Triangulation

• 3D and 2D bump inspection is a critical component in manufacturing of bumped wafers. Continuous miniaturization and use of through silicon via (TSV) in 3D packages are pushing bump sizes smaller and smaller. The small bump size, small pitch and high number of bumps are challenging inspection technologies, requiring high accuracies and high throughput. • Laser triangulationis the dominant technology for 3D characterization of solder and pillar bumps used in conventional packaging techniques.The technology is a line scan laser with the ability to collect hundreds of 3D data points along one scan line in a fraction of a second.These data points can then be used to build a 3D model of the top of the bump and surface of the wafer for local height inspection. As bump size and pitch continue to decrease and bump numbers head towards tens of millions per wafer, the speed and accuracy of laser triangulation technology gives 3DIC manufacturers the ability to tightly control bump processes and detect bump defects.

8"~12" Wafer高阶Solder Bump检查机

高Repepeatability(3δ) : 1 um 以下 业界的最快检查能力 对应8"~12" Wafer FOUP自动 机器 提供多种多样化的讯息报告

WVI-6000α

Falcon 800

Camtek开发的Falcon 800系列先进的 测量系统用于凸起封装晶圆,并保 证凸点达到他们严格的公差。 CTS,Camtek三角测量系统(专利申 请中)应用了比已知的三角测量原 理更新的方式,提高了一系列凸起 技术的精度与可重复性。更宽的角 度范围创造了更多种类凸起形状与 材料更强和更稳定的反射,支持凸 起的真3D几何重建。 Falcon 800更是特别设计用于最精细 的金板的测量。

• For both standard and flip chip wafers, the Wafer Scanner™ Inspection Series provides superior yield management for 3D/2D bump and RDL metrology, bump and RDL defect and macro defect inspection throughout post-fab processes. • Defects created in the post-fab area between wafer processing, bump processing and final manufacturing can negatively impact product yields and time-to-market. • The Wafer Scanner quickly and reliably locates bump and wafer defects, reducing process costs and improving yield.

Basic Geometry of Laser Triangulation

雷射三角几何示意图

此雷射三维系统之量测精度,主要受限于传感器之分辨 率及投射之雷射光线宽,越细的雷射线宽及高分辨率传 感器,可获得较高之量测精度。

雷射三角法系统架构图