cpld数字时钟设计程序

应用CPLD的数字光端机的设计与实现

A D变换 /

采集 模块

R 一8 S 4 5信号

远 程控制

文 献标志码 :A

Ab tac : To v r o te ia v na e o n lg pia tr n l e ., p o q ai o r n miso sr t o ec me h ds d a tg s f a ao o t l emia , .g c o r u ly f ta s sin, sg a dso t n a s d y t in l itri c u e b o

应 用 C L 的数 字光 端 机 的设 计 与 实 P D的数 字光 端机 的设 计 与实 现

De i ig a d Re l i g o h gi l t a er ia y Usn sgnn n ai n ft e Di t z a Op i l c T m n l ig CPL b D

̄e ue c i s o e s mpig  ̄e u n y t mpe n i s rn n e sn pia b rc a n 1 Th o g x e me s a d tmig q n y4 tme ft a ln h q e c o i lme tt me ha g a d r u ig o tc lf e h n e. i i ru h e p r nt n i n i smuain。te c re te s a d fa ii t o e s se ae v rfe . T sse i lt o h or cn s n e sbl y f t y tm r ei d i h i he y tm as e tr s smpl sr cu e, lw c s 。 a d tbe n lo f au e i e tu t r o ot n sa l i p ro a c e r n e。d fntl twi e te d v lpn rn fdgt pia em ias f m e i yi i e l b e eo ig te d o iia o tc ltr n l. l h l

cpld 实验报告

C P L D及电子C A D实验报告学生姓名:梁鹏同组同学:沈金锁在短短的八个周里,我们学习了CPLD及电子CAD的应用方法。

在老师的悉心辅导下我们接触了很有意思的软件——MAX+PLUSII和DesignExplorer99。

我们重点学习了软件MAX+PLUSII,学会使用MAX+PLUSII 软件设计我们曾经学过的一些简单时序逻辑电路,如:3-8译码器的设计,十进制计数器的设计,六十进制计数器的设计以及我们最后自己动手设计的综合实验:基于CPLD的数字电子钟设计。

该软件方便了我们设计电路,它提供了从多种方法输入、编译、仿真、下载等一系列配套功能,同时,我们还可以通过该软件将我们所设计的电路的功能下载到EPIK30TC144-1器件,利用我们所学的理论知识来检验设计电路的正误。

其次,我们还简单学习了软件DesignExplorer99,利用DesignExplorer99设计555振荡器的原理图和PCB设计。

实验内容:实验一:3-8译码器的设计一、实验目的:1.通过一个简单的3-8译码器的设计,让学生掌握组合逻辑电路的设计方法。

2.初步了解CPLD设计的全过程,初步了解软件的使用。

3.掌握组合逻辑电路的静态测试方法。

二、实验内容:(一)进入Windows操作系统,打开MAX+PLUS II的设计软件。

1.指定设计的项目名称用MAX+PLUS II编译一个项目前,必须确定一个设计文件作为当前项目。

对于每个新的项目应该建立一个单独的子目录,当指定了保存该设计项目的子目录名。

其步骤为:(1)启动File----Project Name菜单,将出现Project Name 对话框。

(2)在Project Name对话框内,键入你的设计项目名。

(3)选择OK。

这时,MAX+PLUS II的标题条将显示新的项目名字。

2.选择器件点击Assign----Device菜单,选择器件(本设计一律选用EPIK30TC144-1)。

cpld报告

CPLD课程学习报告学生姓名:钟琦同组姓名:王晓娟在没有接触cpld这门课程之前,可以说对Max+plusⅡ这个软件一窍不通,第一节课时,黄老师用投影仪为我们仔细演示了一遍这个软件的操作过程,通过这节课的学习,我了解到Max+plusⅡ编译一个项目前,必须确定一个设计文件作为当前项目。

对于每个新的项目应该建立一个单独的子目录,当指定设计项目名称时,也就同时指定了保存该设计项目的子目录名实验步骤如下:实验步骤1)新建文件后,输入项目文件名(File/Project/Name)(此时save as名称如果是程序则需要用vhd结尾保存文件)2)输入源文件(图形、VHDL、波形输入方式)(Max+plusⅡ/graphic Editor;Max+plusⅡ/Text Editor;Max+plusⅡ/Waveform Editor)3)指定CPLD型号,选择器件(Assign/Device)(应选择EP1K 30TC144-1)4)设置管脚、下载方式和逻辑综合的方式(Assign/Global Project Device Option,Assign/Global Logic Synthesis) 5)保存并检查源文件(File/project/Save & Check)6)指定管脚(Max+plusⅡ/Floorplan Editor)(具体的管脚应该参考CPLD管脚资源表格)7)保存和编译源文件(File/project/Save & Compile)8)生成波形文件(Max+plusⅡ/Waveform Editor)9)仿真(Max+plusⅡ/Simulator)10)下载配置(Max+plusⅡ/Programmer)一分别做10,24,60进制的计数器因为是第一次接触CPLD的编程,所以对它所用的语言不清楚,第一次写10进制计数器程序时基本是照着老师写的程序生搬硬套上去的,后面写24和60进制计数器时才基本弄懂有些程序的意思。

实验九 复杂可编程逻辑器件CPLD的使用

d 选择目标板元件பைடு நூலகம்

点击(图 9-1a)中的 Next 进入设置工程名称和保存位置(图 9-1b)对话框,在设置 好工程名称和保存路径后点击 Next 进入源文件加载对话框(图 9-1c) ,用户如果有需要加 载的源文件可以点击“add”进行加载,没有可直接点击“Next”进入目标器件选择对话 框(图 9-1d) ,在该对话框中用户应该选择目标器件,在“Family(器件系列) ”中选择 “MAX7000s”系列,在“Available device”列表中选择“EPM7128STC100-15” ,然后点

LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY halfadder2 IS PORT ( a,b : IN bit; s,c : OUT bit); END halfadder2; ARCHITECTURE behave OF halfadder2 IS BEGIN s<=((not a)and b) or (a and not(b)); c<=a and b; END behave;

就像其他宏功能器件符号一样,可以被高层设计或被其他原理图设计文件调用。 3.利用 VHDL 创建一个半加器 ①新建 VHDL 文件:与原理图输入法类似,选择菜单【File】 【New…】 ,打开新建文 件对话框如图 9-2 所示。在该对话框中选中“VHDL File” ,点击“OK” 。 ②输入 VHDL 源代码:在 Quartus II 的文本编辑输入界面中输入以下代码

S i Ai Bi C i 1 S a C i 1 C i Ai Bi ( Ai Bi )C i 1 C a S a C i 1 C a C b

【CPLD EPM570】Verilog实现数码管电子时钟

Verilog实现数码管电子时钟1 原理图8位8段LED数码管,实现时钟的秒、分、小时、日期年月日的显示,其中主显示月、日、小时和分,按住按键S1显示年和秒;8x8的LED阵列显示秒的跳变,每一分钟点亮一圈,8位LED的跑马灯以1秒的频率移动;S1~S4按键实现时钟的设置,S1显示年和秒,S2选择设置的时钟段,S3实现设置数据的增加,S4跳出设置;4x4的矩阵按键,用了K1~K10共10个键,实现数据1~9、0的输入,可用于设置时钟(参考实例图)。

数码管显示的原理图如下,2个4位的8段数码管,组成的8位8段数码管,每个4位数码管的数据线独立,其实是可以以总线形式连接在一起的,可以减少IO。

共阳极的供电端用了三极管增加驱动,否则IO供电驱动多个数码管时有困难。

按键检测及跑马灯原理图如下,共5个按键,其中一个作为Reset按键(设计未加电容,可以考虑优化),每个按键采用一个IO检测,低电平表示有按键按下。

共8个LED灯,每个灯采用一个IO驱动,高电平点亮。

8x8的矩阵LED,行H1-H8为共阳,采用三极管增加驱动,但此实验板采用5V供电,因此无论行控制信号输出高电平或是低电平,都会导致LED有供电,只是供电强弱不一样,但都可能点亮LED,所以实现时需要将不供电时输出高阻z,同理对数据信号V1-V8。

此矩阵显示原理也是分时显示每一列数据,轮流显示速率较快,让人眼无法反映识别出来,避免闪烁。

4x4的矩阵按键,8个IO,检测原理是IO63、66、67、68作为输出信号,轮流赋值高电平,IO59、60、61、62作为输入信号,检测对应的按键按下。

比如,在IO68赋值高电平时,检测到IO59信号为高电平,则表示按键K1被按下,本时钟只用了10个按键,K1~K10。

2 CPLD代码module clock (clk_24m, //24M时钟reset_n, //全局异步复位/******************************************* 8位8段数码管显示接口信号*******************************************/ Bit_line,Data_line_h,Data_line_l,/******************************************* 8位跑马灯接口信号*******************************************/ led_Bit_line,/******************************************* S1-S5按键信号*******************************************/Key_line,/*******************************************8x8 LED数码管矩阵接口信号*******************************************/Hline,Vline,/*******************************************按键阵列接口信号*******************************************/Keyarray_Vline,Keyarray_Hline);input wire clk_24m;input wire reset_n;output wire [7:0] Hline;output wire [7:0] Vline;output wire [7:0] Bit_line;output wire [0:7] Data_line_h;output wire [0:7] Data_line_l;output wire [7:0] led_Bit_line;input wire [3:0] Key_line;input wire [3:0] Keyarray_Vline;output wire [2:0] Keyarray_Hline;/*************************************************************** 内部分频时钟,便于计数。

CPLD控制数字时钟

宁波技师学院课程设计设计题目数字时钟专业班级07电气(六)1学生姓名姚珊珊学号35号学生姓名蒋佳娜学号16号指导教师刘军指导教师陈弢起止日期 2011 年9月3日到 2010 年10月9 日宁波技师学院电气技术系二零一一年九月目录1引言 (3)2总体设计方案 (4)2.1设计要求 (4)2.2设计目的 (4)2.3系统框图 (5)3硬件设计 (7)3.1 CPLD 的简介 (7)3.2电源部分 (8)3.3CPLD外部原理图 (9)4 CPLD内部原理图设计 (10)4.1CPLD内部原理总图 (15)4.2 CPLD写入 (16)5元件清单 (18)6 制作和调试 (19)6. 1制作步骤 (19)6. 2 调试步骤 (19)7结论 (20)8致谢 (21)9参考文献 (22)附录1 仿真图 (23)附录2 CPLD内部原理图 (24)附录3 PCB图 (25)附录4 实物图 (26)1引言有关钟表的发展过程,大致可以分为三个演变阶段,那就是:一、从大型钟向小型钟演变。

二、从小型钟向袋表过渡。

三、从袋表向腕表发展。

每一阶段的发展都是和当时的技术发明分不开的。

时钟的功能也是越来越多,从一开始的简单计时,到现在的定时,闹钟等等。

单片机被广泛运用在工业自动化控制、以其仪器仪表、数据采集、通讯及家用电器等领域。

单片机,以其与通用微机完全不同的发展模式,不断满足工业测控、恶劣环境下可靠运行的要求。

单片机已成为现代领域中不可缺少的重要角色。

单片机发展速度十分迅速,速度更快、功能更强的16位、32位单片机已陆续问世,但8位机,特别是新一代高档8位机具有优异的性能,已能满足大部分单片机应用领域的需要,另外,它还具有可靠性、外围芯片配套、系统构成简单、应用软件丰富、技术成熟、开发运用方便等优点,单片机运用中仍有一定的市场。

在这次的课程设计中我们用51单片机设计了一个数字时钟,其包括计时和校正。

我们通过共阴德数码管来显示,时,分,秒。

cpld时钟

CPLD课程学习报告CPLD 课程是一门实践性非常强的课程,它要求我们运用基本的VHDL硬件描述语言编程得到我们想要的器件以实现我们所预期的功能。

这次CPLD课程学习的主要任务就是灵活地运用CPLD相关知识来设计一个数字电子钟,其基本要求是时、分、秒在数码管上的显示和小时、分钟的校准,扩展要求包括以下几点:1、整点报时:55,56,57,58,59低音响,正点高音,间断振铃(嘟--嘟--嘟--嘟--嘟--嘀)2、跑表:最大计时99分59秒999毫秒。

独立的跑表功能,不影响数字钟正常工作。

3、定时闹钟:可在00:00到23:59之间由用户设定任一时间,到时报警。

4、定时闹钟花样:前10s一般振铃,其后13秒较急促,再其后17秒急促,最后20秒特急促振铃。

并可随时关断。

5、其他(加减调时调分、音乐铃声等,越新奇越好)。

下面我就整个数字电子钟功能的实现过程做一一讲解。

首先,要完成一个最基本的时钟,首要任务就是编写两个计数器(24进制和60进制)。

60进制计数器的VHDL描述如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;ENTITY dl21_cnt60 isport(clk,reset,en:in bit;q0,q1:out std_logic_vector(3 downto 0); carry:out std_logic);end;architecture one of dl21_cnt60 issignal m0,m1:std_logic_vector(3 downto 0); beginprocess(clk,reset,en)beginif reset='1'then m0<="0000";m1<="0000"; elsif clk'event and clk='1' thenif en='0'thenif m0="1001" and m1="0101" thenm1<="0000";m0<="0000";carry<='1';elsif m0="1001" then m1<=m1+1;m0<="0000"; else m0<=m0+1;carry<='0';end if;end if;end if;end process;q0<=m0;q1<=m1;end;通过对程序的保存、创建项目、编译之后,我们可以得到下图所示的实体器件:60进制计数器到底我们做的这个60进制计数器对不对呢,它能不能达到我们想要的效果呢,下面让我们来用波形仿真试一试就知道了。

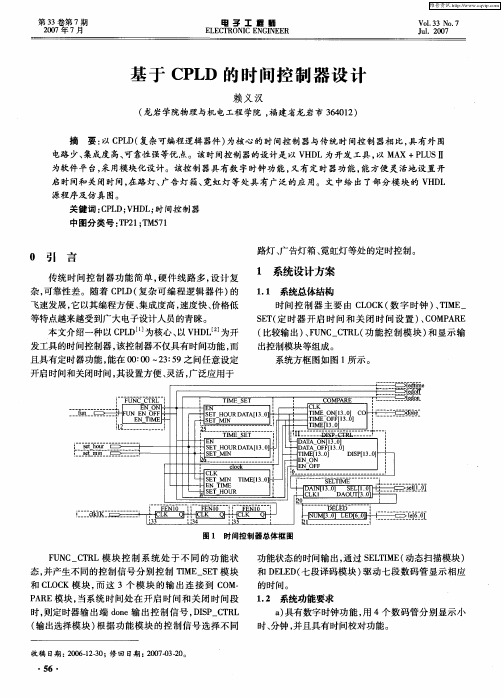

基于CPLD的时间控制器设计

… … 一 面 f … … 一 … … … … 一 西 1 _ _ f 厂 厨 可 H= = j = 0 l

—

J Kl CL

DAOUT3 O 『 仆—}——]

- : 硇K: I: : 三 ; 三 三三

二

l

霉

_

甄

图 1 时间控制器总体框 图

F UNC

第3 3卷第 7期

赖义汉 : 于 C L 基 P D的时间控制器设计

・ 计算机与 自动化技术 ・

b 能 方便地设 定 定 时器 的 开启 时 间 和关 闭 时 间 , )

通过 比较器输出时间控制信号。 e 具 有 4种 功能状态 : ) 系统 时 间校对状 态 、 开启 时

间设 定状 态 、 闭时 间设 定 状 态 、 关 时钟 正 常 显示 状 态 ,

关 键词 : P D; H L 时间控制 器 CL V D ;

中图分 类号 : F 1 T 5 1 T 2 ; M 7

幄

路灯、 广告灯箱、 霓虹灯等处的定时控制。

0 引 言

传 统 时 间 控 制 器 功 能 简单 , 件 线 路 多 , 计 复 硬 设 杂 , 性 差 。随 着 C L 复杂 可 编 程 逻辑 器 件 ) 可靠 P D( 的

_ _

D

【 。 一

量பைடு நூலகம் !

… … … … … … …

l :

.

O [3 0 N 1 . 】 O F1 0 F[ 】 3 TME 1 】 I [ 0 3 D S [3 0 IP 1 】

D n A DA=A r

— —

!

EN ON

—

E OF N F

实验11-用FPGA器件和EDA技术设计多功能数字钟

用FPGA器件和EDA技术

实现多功能数字钟的设计

已知条件

MAX+Plus II软件 FPGA实验开发装置

扩展功能 仿电台报时;

报整点时数。

基本功能

以数字形式显示时、分、 秒的时间;

小时为同步24进制; 要求手动校时、校分; 定时闹钟 。

1

二、实验的步骤与要求

19

b. 添加连线到器件的管脚上 把鼠标移到元件引脚附近,则鼠标光标自动由箭头

变为十字,按住鼠标右键拖动,即可画出连线。 删除一根连接线,单击这根连接线并按 Del 键。

20

c. 标记输入/输出断口属性

双击输入端口的 “PIN-NAME”,当变成黑色时,即可输 入标记符并回车确认。输出端口标记方法类似。对 n 位宽的 总线 A 命名时,你可以采用 A[n-1..0] 形式,其中单个信号用 A[0], A[1], A[2], ….., A[n-1] 形式 。半加器的输入端分别标记 为 A、B ,输出端分别为 S、C 。

“..\maxplus2\max2lib\ mega_lpm”自定义,带 参数

指定您将输入 文件中的符号 名称。

双击一个符号 库,在 Symbol Files 对话框中将出 现它的所有符 号

显示当前路径下的所有符号

18

半加器所需元件和端口包括:输入端口INPUT、 与门AND、异或门XOR、输出端口OUTPUT,它们都 在 Prim 库中。下图为半加器元件安放结果。

5

时、分、秒计数器的设计

分和秒计数器都是模M=60的计数器 其计数规律为00—01—…—58—59—00…

时计数器是一个24进制计数器 其计数规律为00—01—…—22—23—00… 即当数字钟运行到23时59分59秒时,秒的 个位计数器再输入一个秒脉冲时,数字钟 应自动显示为00时00分00秒。

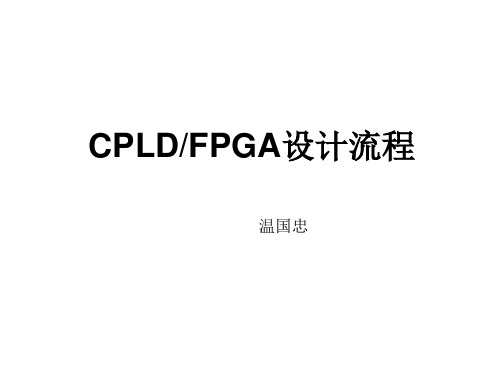

CPLD-FPGA设计流程

设计输入

module paobiao( clk, reset, pause, ms_h, ms_l, s_h, s_l, m_h, m_l

); input output[3:0] clk,reset,pause; ms_h,ms_l,s_h,s_l,m_h,m_l;原理图来自入 Verilog/VHDL 输入

仿真波形

电路综合

Verilog/VHDL 原理图

门级网表 Synthesize

门级网表是利用厂商提 供的器件库生成的, 由与、或、非、寄 存器等基本逻辑单 元组成的连接关系

该网表可以用来进 行门级前仿真, 更重要的是还 可以用来后端 布局布线

综合之后的部分原理图

布局布线

• 布局:将综合输出的逻辑网表适配到 布局: 具体FPGA FPGA器件的物理单元上 具体FPGA器件的物理单元上 • 布线:实现FPGA器件元件之间的互连 布线:实现FPGA FPGA器件元件之间的互连

布局布线之后的电路图

CLB的结构

IOB的结构

Bit文件生成、加载、 Bit文件生成、加载、系统调试 文件生成

CPLD/FPGA设计流程 设计流程

温国忠

主要内容

• 以数字跑表为例介绍 以数字跑表为例介绍CPLD/FPGA设计 设计 的主要流程 • FPGA及其设计优点 及其设计优点

FPGA设计流程示意图

产品需求 FPGA规格 设计方案 设计输入 功能仿真 电路综合 门级前仿真 布局布线 bit文件生成及加载 FPGA系统测试 设计修改

设计方案

跑表模块

pause ms_h

百分秒 计数器

flag1 clk

ms_l

s_h

秒计数器

flag2 reset

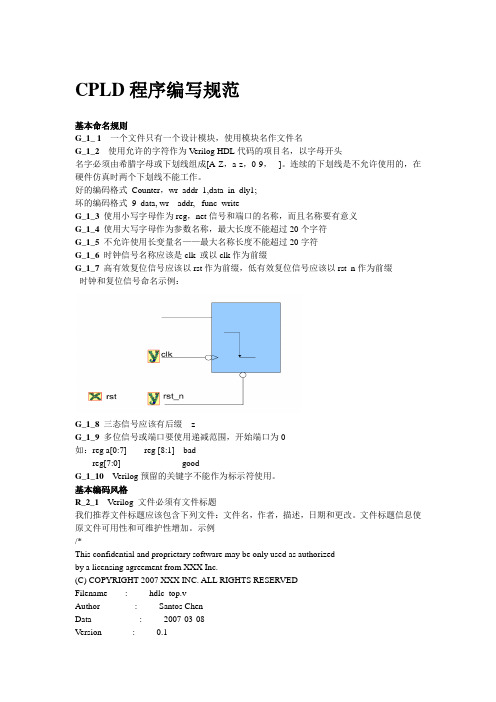

CPLD程序编写规范 altera

CPLD程序编写规范基本命名规则G_1_ 1一个文件只有一个设计模块,使用模块名作文件名G_1_2使用允许的字符作为Verilog HDL代码的项目名,以字母开头名字必须由希腊字母或下划线组成[A-Z,a-z,0-9,_ ]。

连续的下划线是不允许使用的,在硬件仿真时两个下划线不能工作。

好的编码格式Counter,wr_addr_1,data_in_dly1;坏的编码格式9_data, wr__addr, _func_writeG_1_3使用小写字母作为reg,net信号和端口的名称,而且名称要有意义G_1_4使用大写字母作为参数名称,最大长度不能超过20个字符G_1_5不允许使用长变量名——最大名称长度不能超过20字符G_1_6时钟信号名称应该是clk 或以clk作为前缀G_1_7高有效复位信号应该以rst作为前缀,低有效复位信号应该以rst_n作为前缀时钟和复位信号命名示例:G_1_8三态信号应该有后缀_zG_1_9多位信号或端口要使用递减范围,开始端口为0如:reg a[0:7] reg [8:1] badreg[7:0] goodG_1_10Verilog预留的关键字不能作为标示符使用。

基本编码风格R_2_1 Verilog 文件必须有文件标题我们推荐文件标题应该包含下列文件:文件名,作者,描述,日期和更改。

文件标题信息使原文件可用性和可维护性增加。

示例/*-------------------------------------------------------------------------------------------------This confidential and proprietary software may be only used as authorizedby a licensing agreement from XXX Inc.(C) COPYRIGHT 2007 XXX INC. ALL RIGHTS RESERVEDFilename : hdlc_top.vAuthor : Santos ChenData : 2007-03-08Version : 0.1Description : This file has the module of HDLC top.Modification History:Data By Version Change Description========================================================08/09/06 Frack Chen 0.1 Original08/15/06 Peter Liu Add configuration ports….-------------------------------------------------------------------------------------------------*/R_2_2 函数和任务必须有标题内容函数或任务必须有个标题内容来描述函数名,端口和简介;使函数或任务可用性和可维护性增强R_2_3 保持端口声明的一致性按合理的顺序声明端口,并在整个设计中保持声明顺序的一致性R_2_4 一条语句使用单独一行虽然Verilog 允许在一行中书写多条语句,一个命令或一个声明在单独的一行里可读性强可修改性强。

cpld电子钟课程设计

cpld电子钟课程设计一、课程目标知识目标:1. 让学生掌握 CPLD 芯片的基本原理和应用;2. 使学生了解电子时钟的工作原理和设计方法;3. 帮助学生理解数字电路的设计和仿真过程。

技能目标:1. 培养学生运用 CPLD 芯片进行数字电路设计的能力;2. 提高学生利用电子元器件搭建电子时钟的实际操作技能;3. 让学生掌握使用相关软件(如 Multisim、Quartus II 等)进行电路仿真和编程的技术。

情感态度价值观目标:1. 培养学生对电子工程领域的兴趣和热情,激发创新意识;2. 培养学生的团队协作精神和沟通能力,增强合作意识;3. 培养学生严谨、细心的学习态度,提高对工程实践的责任感。

课程性质:本课程为实践性较强的课程,结合理论知识与实际操作,使学生能够将所学知识应用于实际项目中。

学生特点:学生具备一定的电子基础知识,对 CPLD 芯片和电子时钟有一定了解,但缺乏实际设计和操作经验。

教学要求:注重理论与实践相结合,强调动手能力培养,提高学生的创新意识和实际操作技能。

通过课程学习,使学生能够独立完成电子时钟的设计与制作。

二、教学内容1. 理论知识:- CPLD 芯片基本原理、内部结构和编程方法;- 电子时钟工作原理,包括时钟信号产生、分频、计数、显示等;- 数字电路设计基础,包括逻辑门、触发器、计数器等。

相关教材章节:第二章 CPLD 芯片及其应用;第四章 数字电路设计基础;第五章 电子时钟设计。

2. 实践操作:- 使用 Multisim 软件进行电子时钟电路设计和仿真;- 利用 Quartus II 软件对 CPLD 芯片进行编程;- 搭建电子时钟硬件电路,进行实际操作和调试。

教学大纲安排:第1周:CPLD 基本原理及编程方法学习;第2周:电子时钟工作原理及设计方法;第3周:数字电路设计与仿真;第4周:电子时钟硬件电路搭建与调试。

3. 教学进度:- 第1周:理论知识学习,完成相关课后习题;- 第2周:分析电子时钟原理,进行初步设计;- 第3周:实践操作,完成电路仿真与编程;- 第4周:结合理论知识,进行实际电路搭建、调试与优化。

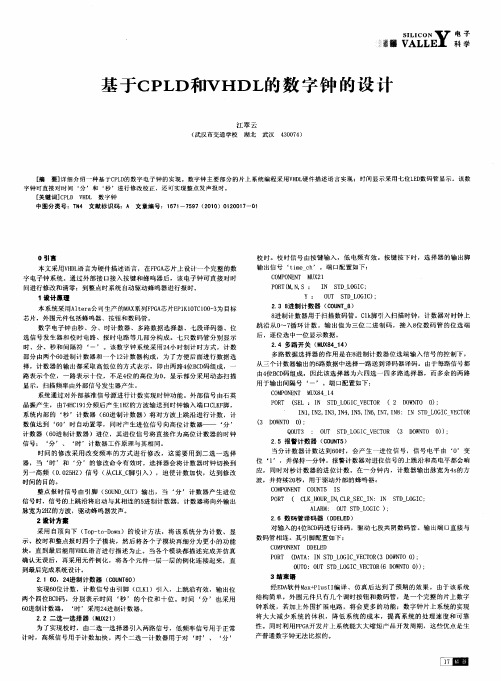

基于CPLD和VHDL的数字钟的设计

基 于CP D和VHDL L 的数 字钟 的设 计

江 翠 云

( 武汉市交通学校 湖北 武汉 407 ) 304

[ 摘

要] 细介绍一 种基于C L 的数字 电子钟 的实现 。数字钟主 要部分 的片上 系统编程采 用V D 硬 件描述 语言实现 ;时 间显示采 用七位L D 详 PD HL E 数码 管显示 。该数

波 ,并持 续Z 秒 ,用于 驱动 外部 的 蜂呜器 。 O

C M O EN C U T I O PN T ON 5 S

字钟可直接 对时间 ‘ ’和 ‘ ’进 行修改校 正,还可实现 整点发声报 时。 分 秒

[ 关键 词 】 P D V D 数 字钟 C L H L

中图分类 号:T 4 文献标识码 :A 文章编 号:1 7 -7 9 2 1 )0 2 0 7 1 N 6 1 5 7( 0 0 1 0 1 —0

P R (,, : OT MN S

Y :

I SD L I : N T O C G

O T S D U T

—

LG C : O I )

2 38 制计 数器 (ON _ ) 进 O UT 8 8 制计 数器 用 于扫 描数 码 管 。Ck 引入 扫描 时钟 ,计数 器对 时钟 上 进 l脚 跳 沿 从 O 循 环计 数 。输 出值 为三 位 二进 制 码 ,接 入 8 数码 管 的 位选 端 ~7 位

2 4 多路 开关 (U 8 _4 . MX 4 1 ) 多 路 数据 选择 器 的作用 是 在 8 进制 计 数 器位 选 端输 入 信 号 的控 制下 , 从三 个 计数 器输 出 的6 路数 据 中选择 一路 送到 译码 器译 码 。 由于 每路 信号 都 由4 BD 位 C 码组 成 ,因 此该 选择 器 为 六 四选 一 四多 路选 择器 ,而 多余 的两 路 用 于输 出 间隔号 ‘ 一’ 。端 口配 置如 下 :

cpld开发流程

cpld开发流程:

CPLD(复杂可编程逻辑器件)的开发流程主要包括以下几个步骤:

1.设计输入:根据项目需求分析编写FPGA任务书,相当于FPGA要实现的具体功能。

然后按照FPGA任务做FPGA概要设计和详细设计。

2.仿真验证:编写测试激励对FPGA各个功能单元进行仿真测试,通过看仿真波形来

确定是否符合功能预期设计。

常用的仿真工具是modelsim。

3.编写时序约束文件:编写FPGA的管脚约束,时钟约束等。

4.编译FPGA项目工程:包括综合、布局布线、生成bit流文件等步骤。

综合就是将较

高级抽象层次的描述转化成较低层次的描述。

综合优化是指将设计输入编译成由与门、或门、非门、RAM、触发器等基本逻辑单元组成的逻辑连接网表,而并非真实的门级电路。

真实具体的门级电路需要利用FPGA制造商的布局布线功能,根据综合后生成的标准门级结构网表来产生。

由于门级结构、RTL级的HDL程序的综合是很成熟的技术,所有的综合器都可以支持这一级别的综合。

常用的综合工具有Synplicity公司的Synplify/Synplify Pro软件以及各个FPGA厂家自己推出的综合开发工具。

5.下载到硬件平台进行功能验证:在硬件功能验证过程中通过内嵌逻辑分析仪,示波

器等进行信号抓取,查波形分析功能是否正确,这一过程非常耗时。

项目制作-多功能数字钟的设计与调试

项目制作-多功能数字钟的设计与调试一、项目制作目的1. 了解并掌握多功能数字钟的设计、制作方法2. 掌握用仿真软件对多功能数字钟电路的仿真调试方法二、项目要求1. 设计电路应能完全满足项目题目的要求。

2. 绘出多功能数字钟电路的逻辑图3. 完成多功能数字钟电路的仿真调试3. 完成多功能数字钟电路的模拟接线安装三、项目步骤(一)电路设计分析1.方案论证数字钟实际上是一个对标准频率(1Hz)进行计数的计数电路。

由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路。

同时标准的1Hz时间信号必须做到准确稳定,通常使用石英晶体振荡器电路构成。

一个用来计“时”、“分”、“秒”的数字钟,主要由六个部分组成。

(1)振荡器主要用来产生频率稳定的时间标准信号,以保证数字钟的走时准确及稳定。

要产生稳定的时标信号,一般采用石英晶体振荡器。

现在使用的指针式电子钟或数字显示的电子钟都是使用石英晶体振荡器电路。

从数字钟精度考虑,晶体振荡器频率越高,计时的精度就愈高,但这样会使分频器的级数增加。

所以在确定频率时应当考虑这两方面的因素,然后再选定石英晶体的具体型号。

(2)分频器振荡器产生的时标信号通常频率很高,为了得到1Hz的秒信号,需要对振荡器的输出信号进行分频。

分频器的级数和每级的分频次数要根据时标频率来定。

例如,目前石英电子钟多采用32768Hz的时标信号,将此信号经过十五级二分频即可得到周期为1s的“秒”信号,电路原理如图4-79所示。

也可以选用其他频率的时基信号,确定分频次数后再选择合适的集成电路。

图4-79 秒信号产生电路(3)计数器“秒”、“分”、“时”分别为六十、六十、二十四进制的计数器。

“秒”和“分”计数器用两块十进制计数器来实现是很容易的,它们的个位为十进制,十位为六进制,这样符合人们通常计数的习惯。

“时”计数也用两块十进制集成块,只是做成二十四进制,上述计数器均可用反馈清零法来实现。

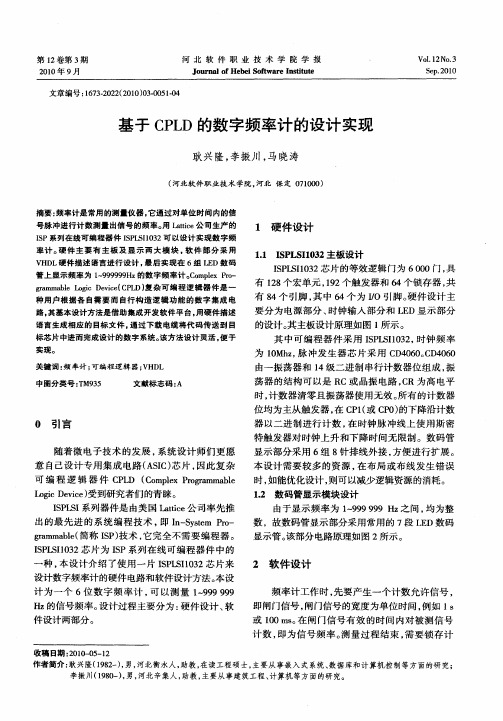

基于CPLD的数字频率计的设计实现

基于 C L P D的 数 字 频 率计 的 设 计 实现

耿兴 隆, 李振川 , 马晓涛

( 北 软 件 职 业技 术 学 院 。 北 保 定 0 10 ) 河 河 7 0 0

摘要 : 频率计是常用的测量仪器 , 它通过对单位 时间内的信 号脉冲进行计 数测量 出信 号的频率。 L tc 用 ai t e公司生产 的

种 , 设 计介 绍 了使 用 一 片 IP S13 本 S L I02芯 片来

2 软 件 设 计

频率计工作时 , 先要产生一个计数允许信号 , 即闸门信号 , 闸门信号的宽度为单位时间, 例如 1 S 或 10m 。 闸门信号有效 的时 间内对被测信号 0 s 在 计数 , 即为信号频率 。 测量过程结束 , 需要锁存计

设 计数 字频率 计 的硬件 电路 和软 件设 计方 法 。 本设 计 为一 个 6位 数 字 频 率 计 , 以 测 量 1 9 9 可 9999

H 的信号频率。 z 设计过程主要分为 : 硬件设计 、 软 件设 计两 部分 。

收稿 日期 :0 0 0 — 2 2 1— 5 1

作者简介 : 耿兴隆(9 2 ) 男, 1 8一 , 河北衡水人 , 助教 , 在读工程硕士 , 要从 事嵌 入式系统、 主 数据 库和计算机控制等方 面的研 究; 李振川(9 0 )男 , 18 一 , 河北 辛集人 , 助教, 主要从事建筑工程 、 计算机 等方面的研 究。

5 2

河 北 软 件 职 业 技 术 学 院 学 报

语言 生成 相应的 目标 文件 , 过下载 电缆将代 码传送 到 目 通 标芯片 中进而完成设计的数字 系统 。 该方法设计灵活 , 便于

实现 。

为 1M z 脉冲发生器芯 片采用 C 4 6 。 D 00 0 h, D 0 0 C 46

理解Altera CPLD 中的时钟

表 1 列出了 MAX II 和 MAX V 器件的外部时序参数。

表 1. MAX II 和 MAX V 器件的外部时序参数

参数 tPD1

tPD2 tCLR tSU tH tCO tCNT

说明

I/O 布局中最差情况下的引脚到引脚延时。使用对角线路径横跨器件,并通过与输出引脚相邻逻辑阵列 模块 (LAB) 中的一个查找表 (LUT)。使用从相邻逻辑单元 (LE) 到输出引脚的快速 I/O 互联。

maxii和maxv器件中的时序模型io引脚io输入延迟input全局输入延迟r4输出延迟glob逻辑阵列io引脚fastio输出布线延迟用户闪存来自相邻的le到相邻的le输入布线延迟lut延迟寄存器控制延迟寄存器延迟clrdatainlut链数据输出iodr输出和输出使能数据延迟comb组合路径延迟计算时序延迟理解alteracpld中的时钟altera公司2010年12要得到最精确的时序结果请使用quartusiitimequest时序分析器它考虑到了次要因素带来的影响例如布局以及扇出

101 Innovation Drive San Jose, CA 95134

© 2010 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Reg. U.S. Pat. & Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trademarks and service marks are the property of their respective holders as described at /common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera’s standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

FPGA与CPLD设计流程

FPGA与CPLD设计流程FPGA(Field-Programmable Gate Array)和CPLD(Complex Programmable Logic Device)是现代数字电路设计中常用的可编程逻辑器件。

它们具有配置灵活、可重构的特点,使得数字电路的设计和开发更加高效和便捷。

本文将介绍FPGA与CPLD的设计流程,并探讨在设计过程中需要注意的一些关键要点。

一、设计前准备在进行FPGA与CPLD设计之前,我们首先需要明确设计的目标和需求,包括功能需求、性能需求和接口需求等。

同时,根据设计的规模和复杂性,确定所需的FPGA或CPLD器件型号,以及需要采用的开发工具和设计语言。

二、设计框架搭建在设计框架搭建阶段,我们需要创建一个新的工程,并选择适当的开发平台和工具。

根据设计需求,将逻辑功能进行划分,确定模块间的接口和数据交互方式。

同时,选择合适的开发语言,如Verilog或VHDL,开始进行设计代码的编写。

三、模块设计与验证在模块设计与验证阶段,我们需要将整个设计划分为多个模块,并逐个进行设计和验证。

每个模块都应该具备独立的功能,并能够与其他模块进行正确的数据交互。

设计人员可以使用仿真工具对每个模块进行功能验证,并通过调试和测试来保证模块的正确性。

四、综合与优化在综合与优化阶段,我们需要使用合成工具将设计代码转换为逻辑网表。

综合工具会将设计代码翻译成与目标FPGA或CPLD器件兼容的逻辑门级表示,并进行优化以提高设计的性能和面积效率。

在这个阶段,设计人员还需根据目标平台的资源限制进行约束设置,以确保设计在合理的范围内。

五、布局布线与时序分析在布局布线与时序分析阶段,我们需要将逻辑网表映射到目标FPGA或CPLD器件的物理资源上,并进行物理布局和布线。

同时,进行时序分析来保证设计在时钟频率和时序要求下能够正常工作。

此外,设计人员还需要注意信号的噪声抑制和时钟域的管理,以确保设计的可靠性和稳定性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity clock isport(clk : in std_logic;rst : in std_logic;inc_min : in std_logic;sub_min : in std_logic;inc_hour : in std_logic;sub_hour : in std_logic;inc_day : in std_logic;sub_day : in std_logic;bao: out bit;set_time : in std_logic;sel : out std_logic_vector(2 downto 0);q : out std_logic_vector(7 downto 0));end clock;architecture Behavioral of clock issignal sec_counter1:std_logic_vector(3 downto 0);signal sec_counter2:std_logic_vector(3 downto 0);signal min_counter1:std_logic_vector(3 downto 0);signal min_counter2:std_logic_vector(3 downto 0);signal hour_counter1:std_logic_vector(3 downto 0);signal hour_counter2:std_logic_vector(3 downto 0);signal day_counter1:std_logic_vector(3 downto 0);signal day_counter2:std_logic_vector(3 downto 0);signal dingshi:std_logic_vector(15 downto 0);signal divcounter : std_logic_vector(27 downto 0);signal div_clk : std_logic;signal scancounter : std_logic_vector(10 downto 0);signal scan_clk : std_logic;signal scan_out : std_logic_vector(2 downto 0);signalsecseg1,secseg2,minseg1,minseg2,hourseg1,hourseg2,dayseg1,dayseg2:std_logic_vector(7 downto 0);begin--计数时钟,对外部输入时钟分频,此处只适用于仿真,实际进行时间计数时,分频后时钟应该满足1HZ。

beginif(rst='0')thendivcounter<= (others=>'0');div_clk<='0';elsif(rising_edge(clk)) thenif(divcounter=X"1024") thendivcounter<= (others=>'0');div_clk<=not div_clk;elsedivcounter<=divcounter+1;end if;end if;end process;--仿真时数码管扫描时钟process(rst,clk)beginif(rst='0')thenscancounter<=(others=>'0');scan_clk<='0';elsif(rising_edge(clk)) thenif(scancounter="00000000011") thenscancounter<=(others=>'0');scan_clk<=not scan_clk;elsescancounter<=scancounter+1;end if;end if;end process;--时钟计数部分主进程clock1:process(div_clk,rst)beginif(rst='0')thensec_counter1<=X"0";sec_counter2<=X"0";min_counter1<=X"0";min_counter2<=X"0";hour_counter1<=X"0";hour_counter2<=X"0";day_counter1<=X"0";day_counter2<=X"0";--手动调分,递增elsif(rising_edge(div_clk))thenif(inc_min='0') thenif(min_counter1=X"9") thenmin_counter1<=X"0";if(min_counter2>=X"5") thenmin_counter2<=X"0";elsemin_counter2<=min_counter2+1;end if;elsemin_counter1<=min_counter1+1;end if;--手动调分,递减elsif(sub_min='0') thenif(min_counter1=X"0") thenmin_counter1<=X"9";if(min_counter2=X"0")thenmin_counter2<=X"5";elsemin_counter2<=min_counter2-1;end if;elsemin_counter1<=min_counter1-1;end if;--手动调时,增时elsif(inc_hour='0') thenif(hour_counter2=X"2")thenif(hour_counter1=X"3")thenhour_counter1<=X"0";hour_counter2<=X"0";elsehour_counter1<=hour_counter1+1;end if;elseif(hour_counter1=X"9") thenhour_counter1<=X"0";hour_counter2<=hour_counter2+1;elsehour_counter1<=hour_counter1+1;end if;end if;--手动调时,减时elsif(sub_hour='0') thenif(hour_counter1=X"0")thenif(hour_counter2=X"0")thenhour_counter1<=X"3";hour_counter2<=X"2";elsehour_counter2<=hour_counter2-1;hour_counter1<=X"9";end if;elsehour_counter1<=hour_counter1-1;end if;--手动调天,增加elsif(inc_day='0') thenif(day_counter2=X"3")thenday_counter1<=X"0";day_counter2<=X"0";elseif(day_counter1=X"9") thenday_counter1<=X"0";day_counter2<=day_counter2+1;elseday_counter1<=day_counter1+1;end if;end if;--手动调天,减少elsif(sub_day='0') thenif(day_counter1=X"0")thenif(day_counter2=X"0")thenday_counter1<=X"0";day_counter2<=X"3";elseday_counter2<=day_counter2-1;day_counter1<=X"9";end if;elseday_counter1<=day_counter1-1;end if;--时分秒正常计数elseif(sec_counter1>=X"9") thensec_counter1<=X"0";if(sec_counter2>=X"5") thensec_counter2<=X"0";if(min_counter1>=X"9") thenmin_counter1<=X"0";if(min_counter2>=X"5") thenmin_counter2<=X"0";if(hour_counter2=X"2") thenif(hour_counter1=X"3") thenif(day_counter2=X"9") thenif(day_counter1=X"9") thenday_counter1<=X"0";day_counter2<=X"0";elseday_counter1<=day_counter1+1;end if;elseif(day_counter1=X"9") thenday_counter1<=X"0";day_counter2<=day_counter2+1;elseday_counter1<=day_counter1+1;end if;end if;day_counter1<=day_counter1+1;hour_counter1<=X"0";elsehour_counter1<=hour_counter1+1;hour_counter2<=X"0";end if;elseif(hour_counter1=X"9") thenhour_counter1<=X"0";hour_counter2<=hour_counter2+1;elsehour_counter1<=hour_counter1+1;end if;end if;elsemin_counter2<=min_counter2+1;end if;elsemin_counter1<=min_counter1+1;elsesec_counter2<=sec_counter2+1;end if;elsesec_counter1<=sec_counter1+1;end if;end if;end if;end process clock1;--生成扫描时钟process(rst,scan_clk)beginif (rst='0') thenscan_out<="000";elsif(rising_edge(scan_clk)) thencase scan_out iswhen "000"=>scan_out<="001";when "001"=>scan_out<="010";when "010"=>scan_out<="011";when "011"=>scan_out<="100";when "100"=>scan_out<="101";when "101"=>scan_out<="110";when "110"=>scan_out<="111";when "111"=>scan_out<="000";when others=> null;end case;end if;end process;--扫描输出进程process(scan_out)begincase scan_out iswhen "000" => q<=secseg1; sel<="111";when "001" => q<=secseg2; sel<="110";when "010" => q<=minseg1; sel<="101";when "011" => q<=minseg2; sel<="100";when "100" => q<=hourseg1; sel<="011";when "101" => q<=hourseg2; sel<="010";when "110" => q<=dayseg1; sel<="001";when "111" => q<=dayseg2; sel<="000";when others => q<="00000000";sel<="000";end case;--秒低位显示second_counter1:process(sec_counter1)begincase sec_counter1 iswhen "0000" => secseg1<="10111111";when "0001" => secseg1<="10000110";when "0010" => secseg1<="11011011";when "0011" => secseg1<="11001111";when "0100" => secseg1<="11100110";when "0101" => secseg1<="11101101";when "0110" => secseg1<="11111101";when "0111" => secseg1<="10000111";when "1000" => secseg1<="11111111";when "1001" => secseg1<="11101111";when others => secseg1<="11111111";end case;end process second_counter1;--秒高位显示second_counter2:process(sec_counter2)begincase sec_counter2 iswhen "0000" => secseg2<="00111111";when "0001" => secseg2<="00000110";when "0010" => secseg2<="01011011";when "0011" => secseg2<="01001111";when "0100" => secseg2<="01100110";when "0101" => secseg2<="01101101";when others => secseg2<="01111111";end case;end process second_counter2;--分低位显示minute_counter1:process(min_counter1)begincase min_counter1 iswhen "0000" => minseg1<="10111111";when "0001" => minseg1<="10000110";when "0010" => minseg1<="11011011";when "0011" => minseg1<="11001111";when "0100" => minseg1<="11100110";when "0101" => minseg1<="11101101";when "0110" => minseg1<="11111101";when "0111" => minseg1<="10000111";when "1000" => minseg1<="11111111";when "1001" => minseg1<="11101111";when others => minseg1<="11111111";end case;end process minute_counter1;--分高位显示minute_counter2:process(min_counter2)begincase min_counter2 iswhen "0000" => minseg2<="00111111";when "0001" => minseg2<="00000110";when "0010" => minseg2<="01011011";when "0011" => minseg2<="01001111";when "0100" => minseg2<="01100110";when "0101" => minseg2<="01101101";when others => minseg2<="01111111";end case;end process minute_counter2;--小时低位显示hor_counter1:process(hour_counter1)begincase hour_counter1 iswhen "0000" => hourseg1<="10111111";when "0001" => hourseg1<="10000110";when "0010" => hourseg1<="11011011";when "0011" => hourseg1<="11001111";when "0100" => hourseg1<="11100110";when "0101" => hourseg1<="11101101";when "0110" => hourseg1<="11111101";when "0111" => hourseg1<="10000111";when "1000" => hourseg1<="11111111";when "1001" => hourseg1<="11101111";when others => hourseg1<="11111111";end case;end process;--小时高位显示hor_counter2:process(hour_counter2)begincase hour_counter2 iswhen "0000" => hourseg2<="00111111";when "0001" => hourseg2<="00000110";when "0010" => hourseg2<="01011011";when others => hourseg2<="01111111";end case;end process;dy_counter1:process(day_counter1)begincase day_counter1 iswhen "0000" => dayseg1<="10111111";when "0001" => dayseg1<="10000110";when "0010" => dayseg1<="11011011";when "0011" => dayseg1<="11001111";when "0100" => dayseg1<="11100110";when "0101" => dayseg1<="11101101";when "0110" => dayseg1<="11111101";when "0111" => dayseg1<="10000111";when "1000" => dayseg1<="11111111";when "1001" => dayseg1<="11101111";when others => dayseg1<="11111111";end case;end process;--小时高位显示dy_counter2:process(day_counter2)begincase day_counter2 iswhen "0000" => dayseg2<="00111111";when "0001" => dayseg2<="00000110";when "0010" => dayseg2<="01011011";when "0011" => dayseg2<="01001111";when "0100" => dayseg2<="01100110";when "0101" => dayseg2<="01101101";when "0110" => dayseg2<="01111101";when "0111" => dayseg2<="00000111";when "1000" => dayseg2<="01111111";when "1001" => dayseg2<="01101111";when others => dayseg2<="01111111";end case;end process;process(clk)beginif(rising_edge(clk)) thenif(set_time='0') thendingshi<= hour_counter2&hour_counter1&min_counter2&min_counter1;end if;end if;end process;process(div_clk)beginif(rising_edge(div_clk))thenbao<='1';if((hour_counter2&hour_counter1&min_counter2&min_counter1)=dingshi) then bao<='0';end if;end if;end process;end Behavioral;。