第五章 触发器

第5章 触发器

46

47

集成电路JK触发器

边沿型集成JK触发器的常用型号有74LS73、74LS76等。

48

5.4 不同类型触发器的相互转换

主要内容

一种触发器转换为另一种触发器的方法 T和T'触发器 D触发器转换为其它触发器 JK触发器转换为其它触发器

5

表5-1 或非门组成的基本RS触发器的真值表

R 0 0 1 1

S 0 1 0 1

Q 不变 1 0 0*

Q

不变 0 1 0*

触发器状态 保持 置1 置0 不定

6

对于左图,可作同样分 析。这种触发器是以低 电平作为输入有效信号 的,在逻辑符号的输入 端用小圆圈表示低电平 输入信号有效。

7

表5-2 与非门组成的RS触发器的真值表

14

1 1 1 1 1 1

0 0 1 1 1 1

1 1 0 0 1 1

0 1 0 1 0 1

0 0 1 1 1* 1*

根据上述真值表,故有钟控RS触发器的特性方程为:

Q

n 1

S RQ

n

RS 0

钟控RS触发器虽然没有实际的IC产品,但它是D触 发器、JK触发器的基础。

15

5.1.3 RS触发器的应用

30

(2)CP由1变为0,即下降沿到来 时,主触发器保持CP=1期间的最后 输出状态不变并作为从触发器的输 入;同时,从触发器开始工作:由 于主触发器的两个输出始终相反, 故从触发器的输出状态跟随主触发 器的最后输出状态(根据钟控RS触 发器的真值表得到)。故有:

Q Q RS 0

41

第五章 触发器

图5.5.2 带异步置位、复位端的CMOS边沿触发器

CMOS边沿触发器的特性表

CP

D

Q

n

Q n 1

0 0

0

0 0

1

0

1 1

1 1

1

(4-33)

二、维持阻塞触发器 1、阻塞RS触发器

S

①置1 维持 线

1

0

S’

& G5 0 1

③置0 阻塞线

&

G3 L1 L2

1 0 1

& G1

Q 0 1

§5.3 电平触发的触发器

一、电路结构及工作原理

(1)CP=0,状态不变。

(2)CP=1,工作,同SR锁存器一样约束条件为:SR=0。

电平触发RS触发器的特性表

*CP回到低电平后状态不定 在使用电平触发RS触发器的过程中,有时还需要CP信号到 来之前将触发器预先置成指定的状态,为此在实用的电平触发 RS触发器电路上往往还设置有专门异步置位输入端和异步复位 输入端,如下页图:1717

1

1 0

1 0

01 10

0 1 0 1

设触发器的初始状态Q=0。

CP=0:基本RS触发器的状态通过A,A’得以保持。

CP变为高电平以后:门 B,B’ 首先解除封锁,若此时输入 为J=1,K=0,则P=0,P’=1 ,…状 态无影响。 CP下降沿到达时:门 B,B’ 首先封锁,P,P’ 的电平不会立

第五章 触发器

§5.1 概述 §5.2 SR锁存器 §5.3 电平触发的触发器

§5.4 脉冲触发的触发器

§5.5 边沿触发的触发器 §5.6 触发器的逻辑功能及其描述方法

第5章-触发器

JK 00 01 10 11

Qn+1 Qn 0 1 Qn

CP

在CP上升沿时,接受J、K 信息,Q不变化

在CP下降沿时,根据接受 到旳J、K信息,Q变化

主从型J-K触发器工作波形图举例

J K Qn+1

CP

0 0 Qn

01 0

J

10 1

1 1 Qn

K

CP

接受JK 信号

Q Q状态 转变

0

置1 清0 翻转 翻转

2、触发器功能表

CP R S Q n+1 1 0 0 Qn 1 01 1

阐明 保持 置1

1 1 0 0 清0

&

&

1 1 1 不定 防止

R

R、S

控制端

CP

S

CP: 时钟脉冲

(Clock Pulse)

0 Qn 保持

3、逻辑符号

Q

Q

R

S

R CP S

4、特征方程

Qn+1=S+RQn SR=0(约束条件)

• 主从触发器旳特点 由两个触发器构成(主触发器和从触发器) 触发方式:主从触发方式(上升沿接受,下降沿触发)

5.4.1 主从RS触发器

1、构造:两个同步RS触发器构成,主从两触发器时钟脉冲反相 2、原理:CP:主触发器输入暂存,CP:从触发器封锁,保持原 状态;时钟后沿出现后从触发器接受主触发器信号而主触发器被 封锁。 3、优点:防止空翻现象 4、缺陷:CP高电平期间受R、S变化旳影响会造成误动作

指R、S从01或10变成11时,输出端状态不变

R-S触发器真值表

Q 1

&

01 RD

Q 1

第5章 触发器

山东大学(威海)机电与信息工程学院 邹晓玉 25

主从JK触发器特性表 CP J K Q Q* Q 0 1 0 0 1 1 1 0

功能 保持 保持 置0

× × × × 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1

根据特性表可写出Q*关于 J、K、Q的函数表达式, 并化简为最简形式,即特 性方程

山东大学(威海)机电与信息工程学院 邹晓玉 17

为适应单输入信号的需要,电平触发的SR触发器 可做成如下的电平触发的D触发器(D锁存器):

电平触发D触发器的特性表

CP

0

D Q

× ×

Q*

Q

功 能

保持

1

1 1 1

0 0

0 1 1 0 1 1

0

0 1 1

置0

置1

CP高电平触发;CP=0时不动作; D=0时,触发器置0; D=1时,触发器置1。

山东大学(威海)机电与信息工程学院 邹晓玉 18

例:已知电平触发的SR触发器的输入信号波形,画出的输出 波形 。设触发器初始状态为0。 保持原态 使输出全为1 Reset Set

CP R

S Q

Q

山东大学(威海)机电与信息工程学院 邹晓玉 19

CP撤去后 状态不定

电平触发的触发器的空翻现象 电平触发的触发器在一个CP脉冲作用期间,出现两次或 两次以上翻转的现象称为空翻。 电平触发的SR触发器, CP=1期间,输入信号仍 直接控制触发器输出端 状态。 CP=1时,S、R状态多次 变化,触发器输出状态随 着变化,触发器的抗干扰 能力较差。

0

1

1

0

1

0

第五章触发器ppt课件

10

次态Qn+1的卡诺图

S Qn

R

00 01 11 10

0× × 0

0

11 1 1 0

特性方程

Qn1 (S ) S RQn

R S 1

约束条件

触发器的特性方程就是触发器次态Qn+1 与输入及现态Qn之间的逻辑关系式

11

波形图

反映触发器输入信号取值和状态之间对应关系的图形称为波形图

跳变

27

存在问题:时钟脉冲不能过宽,否则出现空翻现 象,即在一个时钟脉冲期间触发器翻 转一次以上。

C Q=S Q=R

S R Qn+1 0 0 Qn 01 0 10 1 1 1 不定

克服办法:采用 JK 触发器或 D 触发器

28

1、电路结构

Q

& RD

&

D触发器

Q

& SD

&

2、功能表

CP D Q n+1 1 00

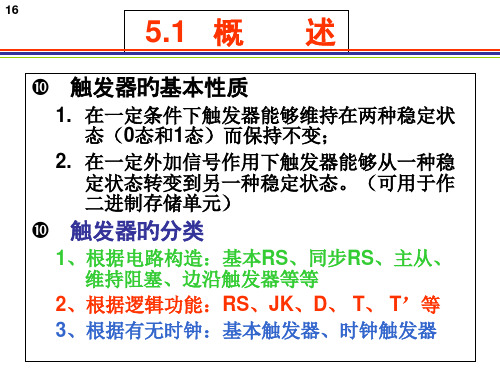

5.1 概述

双稳态触发器: 是一种具有记忆功能的逻辑单元电路,它能储存

一位二进制码。 特点: 1、有两个稳定状态“0”态和“1”态; 2、能根据输入信号将触发器置成“0”或“1”态; 3、输入信号消失后,被置成的“0”或“1”态能

保存下来,即具有记忆功能。

1

触发器的基本概念

1.触发器有两个互补输出端:Q 、 Q 2.有两个稳定的状态:0状态和1状态; 3.在不同的输入情况下,它可以被置成0状态或1状态; 4.具有记忆(存储)功能,当输入信号消失后,所置成的

CLK S R Q Q *

X X X X Qn

0 00 0

0 01 1

1 00 1

触发器的逻辑功能及其描述方法

S CI R

0

S

R

0 1 0 CP

3) 主从SR触发器·特征表

CP

S

R Qn Qn+1

功能

×

×

××

Qn

Q n1 Q n 保持

0

0

0

0

Q n1 Q n 保持

0

0

1

1

0

1

0

0

Q n1 0 置 0

0

1

1

0

1

0

0

1

Q n1 1 置 1

1

0

1

1

1

1

0 不定

1

1

1 不定

不允许

主从SR触发器真值表 (只在CP从1变为0时有效)

G1 &

& G2

G3 & 从触发器 & G4 CP

Qm

Qm

G5 &

& G6 1 G9

G7 & 主触发器 & G8

S

R CP

1) 电路构造 从触发器

主触发器

Q

Q

Q

Q

F从

S CI R

CP

Q

Q

F主

S CI R

S

R

CP

互补时 钟控制 主、从 触发器 不能同 步翻转

1

2) 工作原理

Q

Q

CP=1时 F从封锁

R=1时, 将使触发器 置“1”或称 为置位。

触发器保持

“1”态不

1 Q变

Q0

1.

.0

& G1

& G2

0 S0

1 R1

第5章 触发器

RD

SD

D

CP

4、特性方程 、

Qn+1=D

17

5.3.3 同步JK触发器 同步JK JK触发器

2、逻辑符号 1、电路结构

Q Q

Q & RD & CP J

Q & SD &

J 0 0 1 1 J CP K

3、功能表

K 0 1 0 1 Qn+1 Qn 0 1 Qn 说明 保持 置0 置1 翻转

K

4、特性方程 Qn+1=JQn+KQn Qn

CP J K

Q

Q

5.5 边沿触发器

• 特点:次态仅取决于CP上升沿或者下降沿 特点:次态仅取决于 上升沿或者下降沿 到达前瞬间的输入状态。 到达前瞬间的输入状态。 • 优点:可靠性高,抗干扰能力强,无空翻 优点:可靠性高,抗干扰能力强, 维持阻塞触发器(上升沿触发) 维持阻塞触发器(上升沿触发) • 分类 负边沿触发器(下降沿触发) 负边沿触发器(下降沿触发)

主从JK JK触发器 5.4.2 主从JK触发器

1、结构:将主从RS触发器的 、S端分别与 、Q端相 、结构:将主从 触发器的 触发器的R、 端分别与 端分别与Q、 端相 再分别从G7、 引出 引出J、 输入端 输入端。 连,再分别从 、G8引出 、K输入端。 2、特性方程:Qn+1=JQn+KQn(与JK触发器相同) 、特性方程: 触发器相同) 触发器相同

R-S触发器真值表(特性表) 触发器真值表(特性表) 触发器真值表 RD Q 0 & 1 RD 1 0 Q 1 & 0 SD 0 1 1 0 SD 1 0 1 0 Q 0 1 Q 1(复位 复位) 复位 0(置位 置位)

第五章 触发器ppt课件

Q0 1

& G1

1Q 0 &

G2

0 /R 1

1 /S 1

结论:输入/R和/S为01时,输出为“0”状态。

精品ppt

10

3、 输入R=1, S=0时 ①若原状态:Q=0 , /Q=1

次态输出:Q=1 , /Q=0

Q1 0

& G1

0Q 1 &

G2

1 /R 1

1 /S 0

精品ppt

11

② 若原状态:Q=1 , /Q=0 次态输出:Q=1 , /Q=0

改变。

Q

G1 &

R1

Q

基

本RS&源自G2触 发S1 器

G3 &

& G4

R

精品ppt

0

S

27

cp

真值表(CP=1时)

RS 00 01 10 11

Qn+1 功能说明

Qn

不变

1

置1

0

置0

d

不定

控制,使得多个触发器无法统一工作。

精品ppt

24

§2 钟控RS触发器(同步RS触发器)

触发器只有在同步信号到达时才按输入信号 改变状态。该同步信号叫做时钟脉冲(或时钟 信号),简称时钟,用cp表示。

受时钟信号控制的触发器称为钟控触发器。

精品ppt

25

一、电路结构

由G1、G2组成基本RS触发器,由G3、G4组成输 入控制电路。R为复位端,S为置位端。

Qn+1 = S + /R ·Qn /R + /S = 1 (约束条件)

精品ppt

17

3、 RS触发器状态图

数字电子技术基础第五章触发器

S

(a)

(a)防抖动开关电路图

uA Q uB Q

Q

反跳

反跳

Q (b)

(b)开关反跳现象及改善后的波形图

20

5.3 同步触发器

实际工作中,触发器的工作状态不仅要由触发输入 信号决定,而且要求按照一定的节拍工作。为此,需要 增加一个时钟控制端 CP。

CP 即 Clock Pulse,它是一串 周期和脉宽一定的矩形脉冲。

具有时钟脉冲控制的触发器称为时钟触发器,

又称钟控触发器。

同步触发器是其中最简单的一种,而 基本 RS 触发器称异步触发器。

21

(一)同步 RS 触发器

1. 电路结构与工作原理 Q 基本 RS 触发器 Q

G1

S1 Q3 G3

G2

Q4 R1 G4

S

10 CP

R

增加了由时钟 CP 控制的门 G3、G4

工作原理 ★ CP = 0 ,G3、G4 被封锁。基本 RS 触发 器的输入均为 1,触发器 状态保持不变。

的作用下,状态转换的 方向。

尾端:表示现态,箭头

指向表示次态。

16

(3) 特征方程(也称为状态方程或次态方程)

RD SD Qn Qn+1

说明

0 0 0 × 触发器状态不定

0 0 1×

0 1 0 0 触发器置 0 0110

1 0 0 1 触发器置 1 1011

1 1 0 0 触发器保持原状态不变 1111

9

2. 工作原理及逻辑功能 Q 1 触发器被置 1 0 Q

G1

G2

11

0 SD

输入 RD SD 00 01 10 11

输出 QQ

01 10

第五章 触发器Flip Flop 优质课件

第五章触发器Flip-Flop1、触发器的定义和分类2、常用的触发器3、触发器的分析触发器(Flip-Flop):能够存储一位二进制数字信号的基本单元电路叫做触发器。

(P179引言部分)特点:具有“记忆”功能。

分析下面的电路:当A=0时,F=0某一时刻,由于外界的干扰使得A信号突然消失,此时,相当于A输入端悬空由电路结构得:F=1。

干扰发生前后, F的输出值发生的变化,故该电路没有“记忆”功能再看下面的电路:当A=0时,F=0。

某一时刻,由于外界的干扰使得A信号突然消失,此时,相当于A输入端悬空,但F端反馈回来的值仍然为0,由电路结构得:F=0。

说明该电路具有“记忆”功能。

其根本原因在于,该电路带有反馈。

触发器的分类:P179①按稳定工作状态分:双稳态、单稳态和无稳态(多谐振荡器)触发器。

本章仅讨论双稳态触发器。

②按结构分:主从结构和维持阻塞型(边沿结构)触发器。

本章仅讨论边沿触发器。

③按逻辑功能分:RS、JK、D、T和T’触发器。

本章重点讨论后四种。

常用触发器1、基本RS触发器①电路组成和逻辑符号基本RS触发器有两种:由与非门构成的和由或非门构成的。

我们以前者为例:输出端在正常情形下应是完全相反的两种逻辑状态,即两个稳态。

当Q=0时,称为“0态”;当Q=1时,称为“1态”。

②逻辑功能分析:A)当R=S=0时)(即1==SR11 QQQQ==⋅1可以保证门1的输出值不变。

QQQ=⋅1可以保证门2的输出值不变。

此时,门1和2的输出值均保持不变,称为:触发器的保持功能。

B)当S=0,R=1时)(即0,1==RS1111==⋅可以保证门1的输出值为0。

Q10==⋅Q可以保证门2的输出值为11此时,触发器的Q端始终输出低电平0,称为:触发器复位或触发器清0。

C)当S=1,R=0时)(即1,0==RS1111==⋅可以保证门1的输出值为1。

10==⋅Q可以保证门2的输出值为01此时,触发器的Q端始终输出高电平1,称为:触发器置位或触发器置1。

数电第五章触发器

例5.3.1 对于同步SR触发器,电路、时钟及输入端波形如图 5.3.3所示,若Q =0 ,试画出Q和 Q 的波形 。 5.3 电平触发的触发器 解:输出波形如图5.3.3所示 图5.3.3

5.3 电平触发的触发器

例5.3.2电路如图5.3.4所示,已知S、R、RD和CLK的 波形,且SD=1,试画出Q和Q 的波形。

注:在有些集成触发器中, 输入端J和K不止一个,这 些输入端是与的关系。如图 5.4.6为其逻辑符号图。

分两步动作:第一步在CLK =1时,主触发器受输入信 号控制,从触发器保持原态; 第二步在CLK 到达后,从 触发器按主触发器状态翻转, 故触发器输出状态只能改变 一次;

主从JK触发器在CLK=1期 间,主触发器只可能翻转一 次,因为收到反馈回来的输 出端的影响,故在CLK=1 期间若输入发生变化时,要 找出CLK 来到前的Q 状 态,决定Q*

点 , 在 基

、 逻 辑 功

, 介 绍 触

SR

分 -

各 类 触 发

的触的本

描发功章

述电能重

等平表点 。、、是

状逻各 态辑触 方符发 程号器

、

本章的内容

1

概述

2

SR锁存器

3

电平触发的触发器

4

脉冲触发的触发器

5

边沿触发的触发器

6

五. 触发器的逻辑

功能及其描述

方法 5.7 触发器的

动态特性

1.触发器:

1 1 1 1 1*

5.3 电平触发的触发器

在某些应用场合,有时需要在时钟CLK到来之前,先将

触发器预置成制定状态,故实际的同步SR触发器设置了异步

置位端S D和异步复位端R D,其电路及图形符号如图5.3.2

数字技术电路课件第五章 触发器

5.2

一、 主从RS触发器 1.电路结构

主从触发器

Q Q

由两级同步RS触

发器串联组成。 G1~G4组成从触 发器,G5~G8组 成主触发器。 CP 与CP’互补, 使两个触发器工

CP Q ┌ Q ┌

从 G1 & 触 发 器 G 3 & & G2

&

G4

1R C1 1S

Q' G5 & 主 触 发 器 G7 & R &

知输入R、S的波形图,画出两输出端的波形图。 解: 由表 5.1.1 知,当 R、 S都为 高电平时,触发器保持原状 态不变;当S 变低电平时, 触发器翻转为1状态;当R 变低电平时,触发器翻转为 0 状态;不允许 R 、 S 同时为 低电平。

R S

Q Q

2.用或非门组成的基本RS触发器

Q Q

Q Q

Q ┌ Q ┌

Q ┌ Q ┌ C1 1T

Q

n1

T Q TQ

n

n

当 T 触发器的输入控制端为 T=1 时, 称为T’触发器。 T’触发器的特性方程为:

1K C1 1J

Q n1 Q n

CP

T

4.主从JK触发器存在的问题——一次变化现象

例5.2.2 已知主从 JK触发器 J、 K的波形如图所示,画出输出 Q的波形 图(设初始状态为0)。

Q' G6 1 G9

作在两个不同的

时区内。

&

G8 S

CP

2.工作原理

主从触发器的触发翻转分为两个节拍: (1)当CP=1时,CP’=0,从触发器被封锁,保持原状态不变:主触发器 工作,接收R和S端的输入信号。 (2)当CP由1跃变到0时,即CP=0、CP’=1。主触发器被封锁,输入信号 R、S不再影响主触发器的状态;从触发器工作,接收主触发器输出端的 状态。 特点:(1)主从触发器的翻转是在CP由1变0时刻(CP下降沿)发生的。

5 第五章触发器Flip-Flop解读

1

1 1

0

1 1

1

0 1

0 1

1 1

0 X

0 X

Q

n 1

S RQ

考虑到要避免不定状态发生,(即R、S不能同时为1)故加上一个 约束条件:SR=0。所以,基本RS触发器的逻辑函数表达式(特征 方程)为:

Q S RQ SR 0

n 1

与基本RS触发器完全相同

下面,我们分析一下同步RS触发器的波形。P277

若SR=11,则G3和G4均输出0,触发器不定。

因此,可得出同步RS触发器的功能表:P276

S

S R Qn+1

R 0

0 1

Q 0

1 0

Qn+1 0

1 0 0 1 1 X X 置1 不定 清0 保持

0

0 0

0

0 1 1

0

1 0 1

保持

清0 置1 不定

0

1

1

0

1

0

R、S均为高电平有效,分 别称为:复位端和置位端 进一步得出真值表 再由真值表填卡诺图

n 1

两式若要相等,则必有:

D T Q TQ T Q

作图得:

⑥用D触发器实现T’触发器功能。

分析:D触发器是现有触发器,而T’触发器为待求。

先作出T触发器,再令T为1即得T’触发器。 解:利用上题结论得:

⑦用T触发器实现JK触发器功能。

分析:T触发器是现有触发器,而JK触发器为待求。

常用触发器

1、基本RS触发器

①电路组成和逻辑符号 基本RS触发器有两种:由与非门构成的和由或非门构成的。 我们以前者为例:

输出端在正常情形下应是完全相反的两种逻辑状态,即两个稳态。

5-第五章触发器Flip-Flop解析

称为:不定状态。

此情形应尽量避免。

因此我们得到了基本RS触发器的功能表如下:

S

R

Q

0

0 不定

0

1 置1

1

0 清0

1

1 保持

S 和 R 均为低电平有效,故: S 称为:置1输入端或置位输入端 R 称为:清0输入端或复位输入端

如果我们规定触发器原来的状态称为“现态”(用Qn表示,简记为

Q),将触发器由于输入值的影响后的输出状态称为“次态”(用 Qn+1

将输入值代入特征方程得:

Qn1 TQ T Q 0 Q 0 Q Q

Qn1 TQ T Q 1 Q 1 Q Q

真值表 TQ 00 01 10 11

Qn+1

0 保持 1

1 翻转 0

状态图

6、T’触发器 将T触发器的T端接高电平即为T’触发器。 T’触发器的特征方程为:

Qn1 TQ T Q 1 Q 1 Q Q

1

1Q Q

B)当S=0,R=1时(即S 1, R 0)

1 1

11 1 0 可以保证门1的输出值为0。

Q

0

可以保证门2的输出值为1

0Q 0 1

此时,触发器的Q端始终输出低电平0,称为:触发器复位或触发器

清0。

C)当S=1,R=0时(即S 0, R 1)

0Q 0 1

0

可以保证门1的输出值为1。

1 翻转 反过来使用,即: 当触发器状态保持时,T=0 当触发器状态翻转时,T=1

1101 1

填卡诺图,化简得:

1110 1

0 01 0 1 01 1

作图得:

Qn1 J Q KQ

⑧用T触发器实现D触发器功能。 分析:T触发器是现有触发器,而D触发器为待求。 所以应求出用D来表示T的表达式。 解:比较两种触发器的特征方程得:

5 第五章触发器Flip-Flop解析

若SR=11,则G3和G4均输出0,触发器不定。

因此,可得出同步RS触发器的功能表:P276

S

S R Qn+1

R 0

0 1

Q 0

1 0

Qn+1 0

1 0 0 1 1 X X 置1 不定 清0 保持

0

0 0

0

0 1 1

0

1 0 1

保持

清0 置1 不定

0

1

1

0

1

0

R、S均为高电平有效,分 别称为:复位端和置位端 进一步得出真值表 再由真值表填卡诺图

R 称为:清0输入端或复位输入端

如果我们规定触发器原来的状态称为“现态”(用Qn表示,简记为

Q),将触发器由于输入值的影响后的输出状态称为“次态”(用 Qn+1

n 1 或Qn+1表示),可推导出基本RS触发器的真值表如下:

S

R

Q

0

Q

0

0

X X 1 1 0 0 0 1

不定

0

0 0 1 1 1 1

0

n 1

由真值表还可以推导出触发器的状态变化情况,以图形表示时,称

为状态转换图,简称状态图。

图例

用圆圈表示触发器的状态,用箭头表示状态的变化方向,发生变化 的条件则按顺序标明在箭头旁边。

另外,若已知输入信号的波形,则可以作出触发器的波形图。如:

求在输入作用下的输出波形。

首先,将输入波形分段(作辅助线),再根据触发器的功能表作出

再看下面的电路:

当A=0时,F=0。 某一时刻,由于外界的干扰使得A信号突然消失,此时,相当于A输

入端悬空,但F端反馈回来的值仍然为0,由电路结构得:F=0。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第五章 触发器

题 5.1画出下图由与非门组成的SR 锁存器输出端

Q Q '、的电压波形,输入端D

S '、D R '的电压波形如图中所示。

解:输出波形如下图。

题5.2画出下图由或非门组成的SR 锁存器器输出端Q Q '、的电压波形,输入端D S 、D R 的电压波形如图中所示。

解:输出波形如下图。

题5.5在下图电路中,若CLK 、S 、R 的电压波形如图中所示,试画出Q Q '和端与之对应的电压波形。

假定触发器的初始状态为0Q =。

解:输出波形如下图。

题5.7若主从SR 触发器各输入端的电压波形如下图,试画出Q Q '、端对应的电压波形。

设触发器的初始状态为Q =0。

解:输出波形如下:

题5.9若主从结构SR 触发器的D

CLK S R R '、、、各输入端的电压波形如下图,1D S '=,试画出Q Q '、端对应

的电压波形。

解:输出波形如下:

题5.12若主从结构JK 触发器的D

D CLK R S J K ''、、、、端的电压波形如下图所示,画出Q Q '、端对应的电压波形。

解:输出波形如下:

在第三个CLK =1期间,输入信号J 发生了跳变,此时1Q =,只接受置0信号,出现了 1K =,因此置0。

第四个CLK =1期间,0Q =,只接受置1信号,出现过J =1的尖峰,故有置1信号,那么次态置1。

题5.18设图中各触发器的初始状态皆为0Q =,试画出在CLK 信号连续作用下各触发器输出端的电压波形。

解:(1)JK 触发器的状态方程为:

*Q JQ K Q ''=+

由题意知:1J K == 故有:*1

1Q Q '=;状态翻转 (2)

JK 触发器的状态方程为:

*Q JQ K Q ''=+

由题意知:0J K == 故有:*2

2Q Q =;状态保持 (3)

JK 触发器的状态方程为:

*Q JQ K Q ''=+

由题意知:,J Q K Q '==

故有:*

33

Q Q '=;状态翻转 (4)

T 触发器的状态方程为:

*Q TQ T Q ''=+

由题意知:1T =

故有:*

4

4

Q Q '=;状态翻转 (5)

JK 触发器的状态方程为:

*Q JQ K Q ''=+

由题意知:;J Q K Q '== 故有:*5

5Q Q =;状态保持 (6)

JK 触发器的状态方程为:

*Q JQ K Q ''=+

由题意知:;1J Q K ==

故有:*60Q =;保持0状态

(7)

JK 触发器的状态方程为:

*Q JQ K Q ''=+

由题意知:;1J Q K '==

故有:*7

7

Q Q '=;状态翻转 (8)

SR 触发器的状态方程为:

*

;0()Q S R Q SR '=+=约束条件

由题意知:;S Q R Q '==

故有:*

8

8Q Q '=;状态翻转 (9)

D 触发器的状态方程为:

*Q D =

由题意知:1D = 故有:*9

1Q =;保持1状态 (10)

D 触发器的状态方程为:

*Q D =

由题意知:D Q '=

故有:*

10

10

Q Q '=;状态翻转 (11)

D 触发器的状态方程为:

*Q D =

由题意知:D Q =

故有:*1111Q Q =;状态保持

(12)

T 触发器的状态方程为:

*Q TQ T Q ''=+

由题意知:T Q '= 故有:*12

1Q =;保持1状态

因此,输出电压波形图为:

题5.24试画出下图电路输出端Y 、Z 的电压波形。

输入信号A和CLK 的电压波形如下。

设触发器的初始状态为0Q =。

解:由电路图和D 触发器的特性方程可得:

*1

1Q D A ==;*2

21Q D Q ==

1212

()Y Q Q Q Q '''=⋅=+;1212()Z Q Q Q Q '''=⋅=+

注:第一个CLK 上升沿到达时,因为此前1Q '=1,故*

2Q 变为1。

虽然在CLK 上

升沿时1Q '下降到零,但因建立时间不足,1Q '的新状态不起作用。

次态方程和输出方程用原态和外部输入(若直接引入外部输入)表示。

4.20试画出下图电路输出端Y 、Z 的电压波形。

输入信号A 和CLK 的电压波形如图所示。

设触发器的初始状态为Q =0。

解:由电路图和D 触发器的特性方程可得:

*

1

1Q D A ==;*

221

Q D Q '== 1212

()Y Q Q Q Q '''=⋅=+;1212()Z Q Q Q Q '''=⋅=+。