第5章 stm32单片机外部中断2

stm32单片机中断原理

STM32单片机中断原理1. 什么是中断?在计算机系统中,中断是一种硬件或软件的事件,它打断了正在执行的程序,使CPU能够立即响应某个特定的事件。

中断机制是一种实现多任务处理的重要技术,它能够提高系统的响应速度和处理效率。

2. 中断的基本原理中断的基本原理是通过打断正在运行的程序,跳转到一个中断服务程序(ISR,Interrupt Service Routine)来处理特定的事件。

当发生中断时,CPU会暂停当前的任务,保存上下文(包括程序计数器、寄存器等),然后跳转到中断服务程序执行。

中断服务程序完成后,CPU会恢复之前的任务继续执行。

3. STM32中断的分类在STM32单片机中,中断可以分为两类:外部中断和内部中断。

•外部中断:是由外部设备(如按键、传感器等)触发的中断。

STM32单片机通常具有多个外部中断引脚,可以通过配置外部中断触发源来响应外部设备的事件。

•内部中断:是由单片机内部的事件触发的中断。

例如,定时器溢出、串口接收完成等。

4. STM32中断的基本原理为了使用中断功能,需要进行以下几个步骤:步骤1:中断向量表的配置中断向量表是一个存储中断服务程序地址的表格,用于指示中断发生时应该跳转到哪个中断服务程序执行。

在STM32单片机中,中断向量表位于Flash的起始地址处。

需要在代码中定义中断向量表,并将每个中断的中断服务程序地址写入相应的中断向量表项。

步骤2:中断优先级的配置每个中断都有一个优先级,用于确定中断的相对重要性。

在STM32单片机中,中断优先级可以通过设置优先级分组和优先级子组来进行配置。

优先级分组决定了中断优先级的位数和分配方式,优先级子组决定了同一分组内部的优先级划分。

步骤3:中断源的配置在STM32单片机中,可以通过配置寄存器来选择特定的中断源。

例如,可以通过配置GPIO的寄存器来选择某个引脚触发的外部中断源。

步骤4:中断服务程序的编写中断服务程序是中断发生时需要执行的代码。

stm32外部中断回传参数

stm32外部中断回传参数【最新版】目录1.STM32 外部中断的基本概念2.STM32 外部中断的触发方式3.STM32 外部中断的回传参数4.STM32 外部中断的应用实例5.总结正文一、STM32 外部中断的基本概念STM32 外部中断,也被称为 IO 中断或事件控制器(EXTI)外部中断,是一种在中断系统中产生的中断。

它主要用于检测外部硬件设备的事件,如按键、传感器等。

外部中断可以由上升沿、下降沿或双边沿触发,并且可以单独配置和屏蔽。

在 STM32F103RCT6 芯片中,外部中断通道共有 19 个,每个通道可以独立配置触发事件和屏蔽。

二、STM32 外部中断的触发方式STM32 外部中断的触发方式主要有以下几种:1.上升沿触发:当外部信号从低电平跃升至高电平时,触发外部中断。

2.下降沿触发:当外部信号从高电平跌落至低电平时,触发外部中断。

3.双边沿触发:当外部信号从低电平跃升至高电平,然后再跌落至低电平时,触发外部中断。

三、STM32 外部中断的回传参数当外部中断被触发时,STM32 芯片会将一些相关信息回传给程序,这些信息包括:1.中断类型:用于区分不同类型的外部中断,如按键、传感器等。

2.中断通道:用于指示触发中断的外部中断通道。

3.中断优先级:用于表示当前中断在所有中断中的优先级,便于程序处理。

四、STM32 外部中断的应用实例以下是一个简单的 STM32 外部中断应用实例:假设我们有一个按键,当按键被按下时,触发外部中断。

我们可以通过以下步骤配置 STM32 外部中断:1.配置 GPIO 口:将按键连接到 STM32 的 GPIO 口,并将 GPIO 口设置为外部中断输入模式。

2.配置外部中断:设置触发方式为下降沿触发,并将中断优先级设置为最高。

3.编写中断处理程序:当按键被按下时,执行中断处理程序,实现相应的功能。

五、总结STM32 外部中断是一种灵活的中断方式,可以方便地检测外部硬件设备的事件。

stm32外部中断实验报告-STM32实例外部中断实验

stm32外部中断实验报告_STM32实例外部中断实验上⼀篇⽂章我们介绍了 STM32F10x 的中断,这次我们就来学习下外部中断。

本⽂中要实现的功能与按键实验⼀样,即通过按键控制LED,只不过这⾥采⽤外部中断⽅式进⾏控制。

学习时可以参考《STM32F10x 中⽂参考⼿册》-9 中断和事件章节。

外部中断介绍EXTI 简介STM32F10x 外部中断/事件控制器(EXTI)包含多达 20 个⽤于产⽣事件/中断请求的边沿检测器。

EXTI 的每根输⼊线都可单独进⾏配置,以选择类型(中断或事件)和相应的触发事件(上升沿触发、下降沿触发或边沿触发),还可独⽴地被屏蔽。

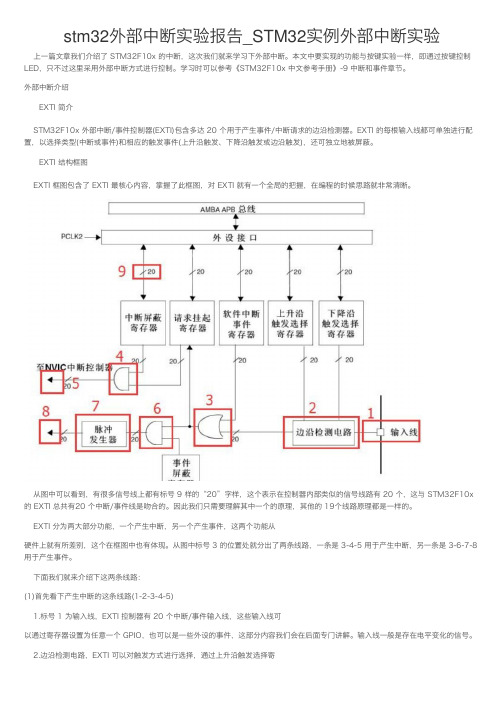

EXTI 结构框图EXTI 框图包含了 EXTI 最核⼼内容,掌握了此框图,对 EXTI 就有⼀个全局的把握,在编程的时候思路就⾮常清晰。

从图中可以看到,有很多信号线上都有标号 9 样的“20”字样,这个表⽰在控制器内部类似的信号线路有 20 个,这与 STM32F10x 的 EXTI 总共有20 个中断/事件线是吻合的。

因此我们只需要理解其中⼀个的原理,其他的 19个线路原理都是⼀样的。

EXTI 分为两⼤部分功能,⼀个产⽣中断,另⼀个产⽣事件,这两个功能从硬件上就有所差别,这个在框图中也有体现。

从图中标号 3 的位置处就分出了两条线路,⼀条是 3-4-5 ⽤于产⽣中断,另⼀条是 3-6-7-8⽤于产⽣事件。

下⾯我们就来介绍下这两条线路:(1)⾸先看下产⽣中断的这条线路(1-2-3-4-5)1.标号 1 为输⼊线,EXTI 控制器有 20 个中断/事件输⼊线,这些输⼊线可以通过寄存器设置为任意⼀个 GPIO,也可以是⼀些外设的事件,这部分内容我们会在后⾯专门讲解。

输⼊线⼀般是存在电平变化的信号。

2.边沿检测电路,EXTI 可以对触发⽅式进⾏选择,通过上升沿触发选择寄存器和下降沿触发选择寄存器对应位的设置来控制信号触发。

边沿检测电路以输⼊线作为信号输⼊端,如果检测到有边沿跳变就输出有效信号 1 给红⾊框 3 电路,否则输出⽆效信号 0。

使用HAL库开发STM32GPIO口基础使用与外部中断

使用HAL库开发STM32GPIO口基础使用与外部中断GPIO(General Purpose Input/Output)是STM32系列微控制器上常见的功能模块之一,它用于与外部设备进行数据交互。

本文主要介绍如何使用HAL库来配置和使用STM32的GPIO口,并实现外部中断功能。

在使用GPIO口之前,我们首先需要了解STM32芯片上的GPIO引脚的命名方式。

以STM32F103C8T6为例,它具有32个GPIO引脚,从PA0到PA15和PB0到PB15、其中,GPIO口的命名方式为"A"加上引脚的编号。

例如,PA0表示GPIOA的第0个引脚,PB10表示GPIOB的第10个引脚。

1.引入头文件和宏定义首先,在代码文件的顶部引入"stm32f1xx_hal.h"头文件。

然后,在需要使用GPIO功能的地方,定义一个GPIO_InitTypeDef结构体变量,并通过它来配置GPIO的参数。

2.配置GPIO模式和速度在设置GPIO口之前,需要配置GPIO的模式和速度。

通过设置GPIO_InitStruct结构体变量的对应成员变量来实现。

例如,要将PA5配置为推挽输出模式,可以使用如下语句:```GPIO_InitStruct.Pin = GPIO_PIN_5;GPIO_InitStruct.Mode = GPIO_MODE_OUTPUT_PP;GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_HIGH;HAL_GPIO_Init(GPIOA, &GPIO_InitStruct);```这里,GPIO_PIN_5表示PA5引脚,GPIO_MODE_OUTPUT_PP表示推挽输出模式,GPIO_SPEED_FREQ_HIGH表示高速模式。

3.配置GPIO引脚在配置好GPIO模式和速度后,可以通过HAL_GPIO_Init函数来配置GPIO引脚,并进行初始化。

野火F1开发板STM32案例-外部中断(按键)使用

野⽕F1开发板STM32案例-外部中断(按键)使⽤野⽕F1开发板STM32案例-外部中断(按键)使⽤硬件平台野⽕STM32F103ZET6 霸道V2开发板正点原⼦F1系列开发板软件平台Keil MDK 5.31串⼝调试助⼿Gitee .中断相关概念中断配置寄存器# 配置中断时,使⽤ISER、 ICER 和 IP 寄存器,## ISER 是中断使能寄存器## ICER 是中断清除寄存器## IP 是中断优先级寄存器中断优先级1. 数值越⼩,优先级越⾼2. STM32F103 中只使⽤4位,⾼4位有效。

3. ⽤于表达优先级的⾼ 4 位⼜被分组成抢占式优先级和响应优先级,称为“亚优先级”或“副优先级”4. 每个中断源都需要被指定这两种优先级。

中断配置步骤1.使能外设中断6. 设置中断优先级分组初始化 NVIC_InitTypeDef 结构体,设置抢占优先级和响应优先级,使能中断请求。

typedef struct{uint8_t NVIC_IRQChannel; //中断源uint8_t NVIC_IRQChannelPreemptionPriority; //抢占优先级uint8_t NVIC_IRQChannelSubPriority; //响应优先级FunctionalState NVIC_IRQChannelCmd; //中断使能或失能} NVIC_InitTypeDef;NVIC_IRQChannel 中断源:中断源的设置,不同的外设中断,中断源不⼀样NVIC_IRQChannelPreemptionPriority //抢占优先级NVIC_IRQChannelSubPriority //响应优先级NVIC_IRQChannelCmd //中断使能或失能:使能配置为 ENABLE,失能配置为 DISABLE。

NVIC_IRQChannel //中断源/****** Cortex-M3 Processor Exceptions Numbers ***************************************************/NonMaskableInt_IRQn = -14, /*!< 2 Non Maskable Interrupt */MemoryManagement_IRQn = -12, /*!< 4 Cortex-M3 Memory Management Interrupt */BusFault_IRQn = -11, /*!< 5 Cortex-M3 Bus Fault Interrupt */UsageFault_IRQn = -10, /*!< 6 Cortex-M3 Usage Fault Interrupt */SVCall_IRQn = -5, /*!< 11 Cortex-M3 SV Call Interrupt */DebugMonitor_IRQn = -4, /*!< 12 Cortex-M3 Debug Monitor Interrupt */PendSV_IRQn = -2, /*!< 14 Cortex-M3 Pend SV Interrupt */SysTick_IRQn = -1, /*!< 15 Cortex-M3 System Tick Interrupt *//****** STM32 specific Interrupt Numbers *********************************************************/WWDG_IRQn = 0, /*!< Window WatchDog Interrupt */PVD_IRQn = 1, /*!< PVD through EXTI Line detection Interrupt */TAMPER_IRQn = 2, /*!< Tamper Interrupt */RTC_IRQn = 3, /*!< RTC global Interrupt */FLASH_IRQn = 4, /*!< FLASH global Interrupt */RCC_IRQn = 5, /*!< RCC global Interrupt */EXTI0_IRQn = 6, /*!< EXTI Line0 Interrupt */EXTI1_IRQn = 7, /*!< EXTI Line1 Interrupt */EXTI2_IRQn = 8, /*!< EXTI Line2 Interrupt */EXTI3_IRQn = 9, /*!< EXTI Line3 Interrupt */EXTI4_IRQn = 10, /*!< EXTI Line4 Interrupt */DMA1_Channel1_IRQn = 11, /*!< DMA1 Channel 1 global Interrupt */DMA1_Channel2_IRQn = 12, /*!< DMA1 Channel 2 global Interrupt */DMA1_Channel3_IRQn = 13, /*!< DMA1 Channel 3 global Interrupt */DMA1_Channel4_IRQn = 14, /*!< DMA1 Channel 4 global Interrupt */DMA1_Channel5_IRQn = 15, /*!< DMA1 Channel 5 global Interrupt */DMA1_Channel6_IRQn = 16, /*!< DMA1 Channel 6 global Interrupt */DMA1_Channel7_IRQn = 17, /*!< DMA1 Channel 7 global Interrupt */STM32F103 中断向量表EXTI外部中断1. STM32F10x 外部中断/事件控制器(EXTI)包含多达 20 个⽤于产⽣事件/中断请求的边沿检测器。

stm32外部中断的使用(含实例)

stm32外部中断的使⽤(含实例)中断对于开发嵌⼊式系统来讲的地位绝对是⽏庸置疑的,在C51单⽚机时代,⼀共只有5个中断,其中2个外部中断,2个定时/计数器中断和⼀个串⼝中断,但是在STM32中,中断数量⼤⼤增加,⽽且中断的设置也更加复杂。

今天就将来探讨⼀下关于STM32中的中断系统。

1 基本概念ARM Coetex-M3内核共⽀持256个中断,其中16个内部中断,240个外部中断和可编程的256级中断优先级的设置。

STM32⽬前⽀持的中断共84个(16个内部+68个外部),还有16级可编程的中断优先级的设置,仅使⽤中断优先级设置8bit中的⾼4位。

STM32可⽀持68个中断通道,已经固定分配给相应的外部设备,每个中断通道都具备⾃⼰的中断优先级控制字节PRI_n(8位,但是STM32中只使⽤4位,⾼4位有效),每4个通道的8位中断优先级控制字构成⼀个32位的优先级寄存器。

68个通道的优先级控制字⾄少构成17个32位的优先级寄存器。

4bit的中断优先级可以分成2组,从⾼位看,前⾯定义的是抢占式优先级,后⾯是响应优先级。

按照这种分组,4bit⼀共可以分成5组第0组:所有4bit⽤于指定响应优先级;第1组:最⾼1位⽤于指定抢占式优先级,后⾯3位⽤于指定响应优先级;第2组:最⾼2位⽤于指定抢占式优先级,后⾯2位⽤于指定响应优先级;第3组:最⾼3位⽤于指定抢占式优先级,后⾯1位⽤于指定响应优先级;第4组:所有4位⽤于指定抢占式优先级。

所谓抢占式优先级和响应优先级,他们之间的关系是:具有⾼抢占式优先级的中断可以在具有低抢占式优先级的中断处理过程中被响应,即中断嵌套。

当两个中断源的抢占式优先级相同时,这两个中断将没有嵌套关系,当⼀个中断到来后,如果正在处理另⼀个中断,这个后到来的中断就要等到前⼀个中断处理完之后才能被处理。

如果这两个中断同时到达,则中断控制器根据他们的响应优先级⾼低来决定先处理哪⼀个;如果他们的抢占式优先级和响应优先级都相等,则根据他们在中断表中的排位顺序决定先处理哪⼀个。

STM32外部中断以及中断优先级

外部中断(zhōngduàn)的初始化过程:1.初始化IO为输入(shūrù)(可以设置上拉,下拉,浮空)2.开启(kāiqǐ)IO复用(fù yònɡ)时钟3.开启(kāiqǐ)与该IO相对的线上(详解下)4.配置NVIC,使能中断5.编写中断服务函数外部中断:Stm32中总共有19个外部中断包括:线0-15:IO输入中断(每条线上最多有7个IO,如GPIOA~GPIOG,但是每一条线每次只允许同时连接到一个IO)线16:PVD线17:RTC线18:USB关于(guānyú)优先级:CM3中内核(nèi hé)支持256个中断(zhōngduàn)(16个内核(nèi hé)+240外部(wàibù))和可编程256级中断优先级的设置Stm32目前(mùqián)支持84个中断(zhōngduàn)(16个内核(nèi hé)+68个外部(wàibù),注:不是(bù shi)指68个外部中断),16级可编程优先级(优先级设置寄存器中使用了4位)注意:其中(qízhōng)外部中断5-9和中断(zhōngduàn)10-15向量存放(cúnfàng)在一起优先级:数值(shùzí)低的优先级要高于数值高的!!!!!!上电复位后,系统默认(mòrèn)使用的是组0;一个系统只能使用一组优先级组,不可使用多个,优先级的设置不能超过组的范围,否则会产生不可预计的错误1.高抢先级的中断可以打断低优先级的中断响应,构成中断嵌套2.相同抢先级的中断不可以构成嵌套,系统会优先响应子优先级高的3.当2(n)个相同抢先优先级和相同子优先级的中断(zhōngduàn)出现,STM32首先响应中断通道所对应的中断向量地址(dìzhǐ)低的那个中断4.0号抢先优先级的中断,可以(kěyǐ)打断任何中断抢先优先级为非0号的中断(zhōngduàn);1号抢先优先级的中断(zhōngduàn),可以打断任何中断抢先优先级为2、3、4号的中断;……;构成中断嵌套。

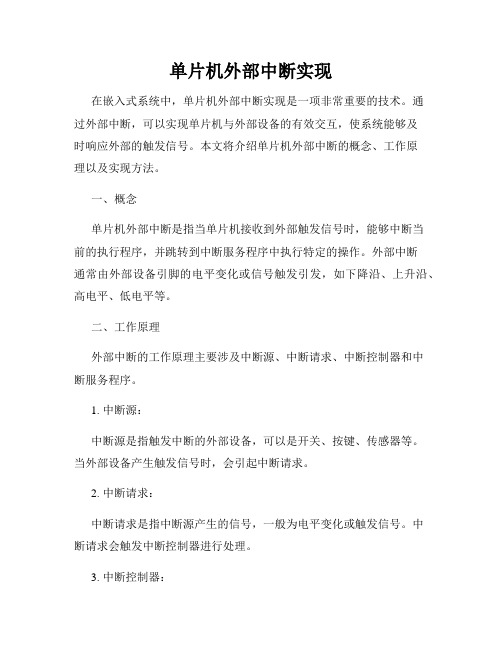

单片机外部中断实现

单片机外部中断实现在嵌入式系统中,单片机外部中断实现是一项非常重要的技术。

通过外部中断,可以实现单片机与外部设备的有效交互,使系统能够及时响应外部的触发信号。

本文将介绍单片机外部中断的概念、工作原理以及实现方法。

一、概念单片机外部中断是指当单片机接收到外部触发信号时,能够中断当前的执行程序,并跳转到中断服务程序中执行特定的操作。

外部中断通常由外部设备引脚的电平变化或信号触发引发,如下降沿、上升沿、高电平、低电平等。

二、工作原理外部中断的工作原理主要涉及中断源、中断请求、中断控制器和中断服务程序。

1. 中断源:中断源是指触发中断的外部设备,可以是开关、按键、传感器等。

当外部设备产生触发信号时,会引起中断请求。

2. 中断请求:中断请求是指中断源产生的信号,一般为电平变化或触发信号。

中断请求会触发中断控制器进行处理。

3. 中断控制器:中断控制器会根据中断请求的优先级和设置的中断屏蔽位,确定是否接受中断请求,并决定是否触发中断。

常见的中断控制器有外部中断控制器(例如8051中的中断0、中断1)和内部中断控制器(例如NVIC)。

4. 中断服务程序:中断服务程序是事先编写好的程序,用于处理中断事件。

当中断控制器接受到中断请求后,会跳转到对应的中断服务程序执行相应的操作。

中断服务程序需高效地完成相应的操作,然后返回到中断之前的程序位置,继续执行。

三、实现方法单片机外部中断的实现方法因芯片型号和开发环境而异,下面以常用的STM32单片机为例,介绍两种常见的外部中断实现方法。

1. EXTI外部中断:STM32单片机中,外部中断的实现依赖于外部中断线(EXTI)。

使用EXTI可以将特定GPIO引脚与中断源连接,当GPIO引脚的电平变化满足中断触发条件时,触发并处理相应的中断。

外部中断的实现步骤如下:(1)配置GPIO引脚为输入模式,设置中断触发模式(例如边沿触发模式)。

(2)配置EXTI中断线,绑定对应的GPIO引脚和中断触发源。

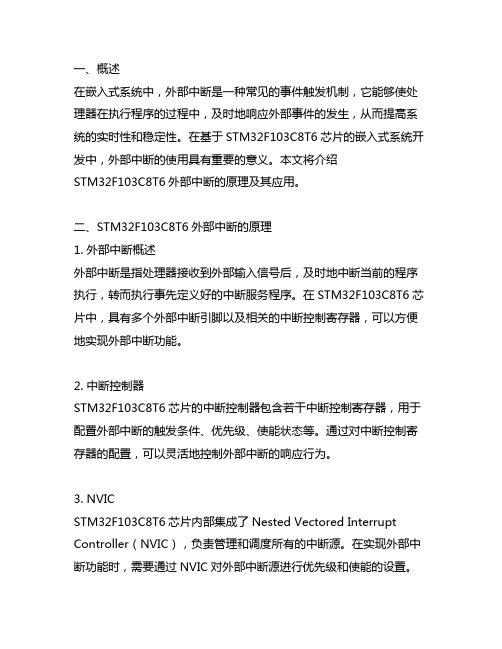

stm32f103c8t6外部中断原理

一、概述在嵌入式系统中,外部中断是一种常见的事件触发机制,它能够使处理器在执行程序的过程中,及时地响应外部事件的发生,从而提高系统的实时性和稳定性。

在基于STM32F103C8T6芯片的嵌入式系统开发中,外部中断的使用具有重要的意义。

本文将介绍STM32F103C8T6外部中断的原理及其应用。

二、STM32F103C8T6外部中断的原理1. 外部中断概述外部中断是指处理器接收到外部输入信号后,及时地中断当前的程序执行,转而执行事先定义好的中断服务程序。

在STM32F103C8T6芯片中,具有多个外部中断引脚以及相关的中断控制寄存器,可以方便地实现外部中断功能。

2. 中断控制器STM32F103C8T6芯片的中断控制器包含若干中断控制寄存器,用于配置外部中断的触发条件、优先级、使能状态等。

通过对中断控制寄存器的配置,可以灵活地控制外部中断的响应行为。

3. NVICSTM32F103C8T6芯片内部集成了Nested Vectored Interrupt Controller(NVIC),负责管理和调度所有的中断源。

在实现外部中断功能时,需要通过NVIC对外部中断源进行优先级和使能的设置。

4. 外部中断触发条件在STM32F103C8T6芯片中,外部中断可以以上升沿、下降沿、上升沿和下降沿、低电平或者高电平触发。

在配置外部中断时,需要根据实际应用需求选择合适的触发条件,并进行相应的配置。

5. 外部中断服务程序一旦外部中断触发条件满足,处理器将立即响应中断,并跳转到预先定义好的外部中断服务程序中执行。

外部中断服务程序通常用于处理外部事件的逻辑,例如状态更新、数据采集、报警处理等。

三、STM32F103C8T6外部中断的应用1. 外部按键控制在很多嵌入式系统中,外部按键常常作为用户与系统交互的途径。

通过STM32F103C8T6的外部中断功能,可以轻松地实现外部按键的检测和响应,从而实现用户界面的交互控制。

第5章 stm32单片机外部中断1

5.3.3 相关功能寄存器

EXTI_IMR(Interrupt mask register )中断屏蔽寄存器

5.3.3 相关功能寄存器

EXTI_EMR( Event mask register )中断事件屏蔽寄存器

5.3.3 相关功能寄存器

EXTI_RTSR(Rising trigger selection register)上升沿触发寄存器

5.3.2 中断控制器

具体有哪些外部中断,在“stm32f10x_nvic.h”这个头文件中 已经定义

5.3.2 中断控制器

5.3.2 中断控制器

ICER[2]:全称Interrupt Clear-Enable Registers,是 一个中断清除使能寄存器组。 该寄存器组与ISER寄存器功能相反,用来清除某个 中断的使能位。由于NVIC的这些寄存器都是写1有 效的,写0是无效的。设置一组ICER 寄存器来清除 相应中断使能位。 ISPR[2]:全称Interrupt Set-Pending Registers,是 一个中断挂起控制寄存器组。 每个位对应的外部中断和ISER内容是一样的。通过 向相应的位写1,可以将正在执行的中断挂起,去执 行同级或更高级别的中断。向这个寄存器组写0是无 效的。

抢占优先级和响应优先级

假定设置中断优先级为组2,然后设置: 中断3(RTC中断)的抢占优先级为2,响应优先级为1。 中断6(外部中断0)的抢占优先级为3,响应优先级为0。 中断7(外部中断1)的抢占优先级为2,响应优先级为0。 求这3个中断的优先级顺序? 上面例子中的中断3和中断7都可以打断中断6 的中断。而中 断7和中断3却不可以相互打断(这是因为他们的抢占优先级 是相同的)。

5.3.2 中断控制器

STM32CubeMX实战教程(三)——外部中断(中断及HAL_Delay函数避坑)

STM32CubeMX实战教程(三)——外部中断(中断及HAL_Delay函数避坑)在STM32CubeMX实战教程中,我们已经学习了如何使用GPIO来控制LED的亮灭。

在这篇文章中,我们将进一步学习如何使用外部中断来实现更复杂的功能。

外部中断可以使我们的微控制器能够在输入发生变化时立即做出响应。

这对于需要实时性的应用非常重要,比如按钮的按下或松开的检测。

外部中断类似于计数器,不断地检测输入引脚的变化,并在变化时触发中断。

在STM32CubeMX中配置外部中断非常简单。

我们只需要选择外部输入引脚作为中断源,然后为中断配置触发方式即可。

触发方式可以是上升沿、下降沿或双边沿触发。

但要注意的是,当使用外部中断时,我们应该避免在中断服务子程序(ISR)中使用延时函数,如HAL_Delay。

这是因为在ISR中调用延时函数会导致中断响应时间增加,从而影响其他中断的响应和整个系统的实时性。

所以在ISR中,我们只能执行最核心、最迅速的操作。

为了避免在ISR中使用延时函数,我们可以使用定时器中断来实现延时。

定时器中断是一种定期触发的中断,在ISR中我们可以通过判断定时器的计数值来实现一定时间的延时。

下面是一个使用外部中断的示例代码:```c#include "stm32f4xx_hal.h"GPIO_InitTypeDef GPIO_InitStruct;EXTI_HandleTypeDef hexti;void SysTick_Handler(void)HAL_IncTick(;HAL_SYSTICK_IRQHandler(;void EXTI_IRQHandler(void)HAL_GPIO_EXTI_IRQHandler(GPIO_PIN_0);void HAL_GPIO_EXTI_Callback(uint16_t GPIO_Pin) //在这里执行最核心、最迅速的操作int main(void)HAL_Init(;SystemClock_Config(;__HAL_RCC_GPIOA_CLK_ENABLE(;__HAL_RCC_SYSCFG_CLK_ENABLE(;GPIO_InitStruct.Pin = GPIO_PIN_0;GPIO_InitStruct.Mode = GPIO_MODE_IT_RISING; GPIO_InitStruct.Pull = GPIO_PULLDOWN;HAL_GPIO_Init(GPIOA, &GPIO_InitStruct);HAL_NVIC_SetPriority(EXTI0_IRQn, 0, 0);HAL_NVIC_EnableIRQ(EXTI0_IRQn);while (1)//在这里执行其他操作}```在这个示例中,我们使用PA0引脚,即用户按钮作为外部中断源。

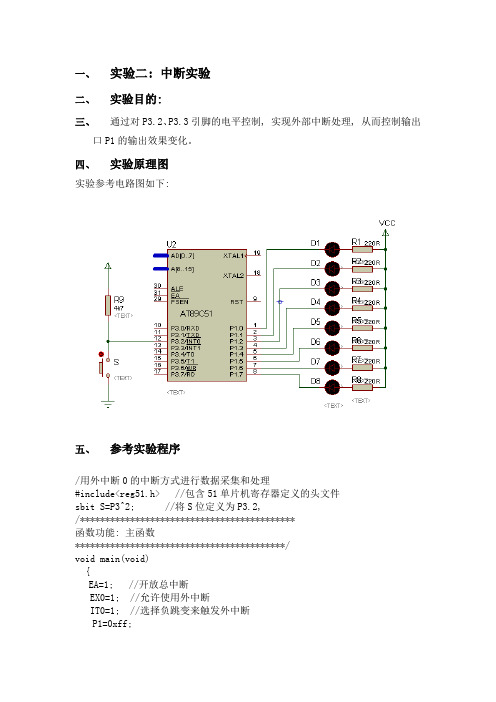

单片机实验二_外部中断

一、实验二: 中断实验二、实验目的:三、通过对P3.2、P3.3引脚的电平控制, 实现外部中断处理, 从而控制输出口P1的输出效果变化。

四、实验原理图实验参考电路图如下:五、参考实验程序/用外中断0的中断方式进行数据采集和处理#include<reg51.h> //包含51单片机寄存器定义的头文件sbit S=P3^2; //将S位定义为P3.2,/*******************************************函数功能: 主函数******************************************/void main(void){EA=1; //开放总中断EX0=1; //允许使用外中断IT0=1; //选择负跳变来触发外中断P1=0xff;while(1); //无限循环, 防止程序跑飞}/************************************************************** 函数功能: 外中断T0的中断服务程序**************************************************************/ void int0(void) interrupt 0 using 0 //外中断0的中断编号为0 {P1=~P1; //每产生一次中断请求, P1取反一次。

}实验思考题:(1) 根据指导书中提供的原理图, 自行设计一个外部中断实验, 要求:(2) 两个外部中断全部用上;(3) 实验能体现不同中断优先级的中断源的相应情况;(4) 不同中断处理程序能输出不同的响应效果//用外中断0的中断方式进行数据采集和处理00000000#include<reg51.h> //包含51单片机寄存器定义的头文件sbit S=P3^2; //将S位定义为P3.2,/*******************************************函数功能: 主函数******************************************/void main(void){EA=1; //开放总中断EX0=1; //允许使用外中断IT0=1; //选择负跳变来触发外中断P1=0xf0;PX0=1;// PX1=1;while(1); //无限循环, 防止程序跑飞}/************************************************************** 函数功能: 外中断T0的中断服务程序**************************************************************/ void int0(void) interrupt 0 using 0 //外中断0的中断编号为0 {//P1=~P1;P1=0x01;}void int1(void) interrupt 1 using 1{//P1=~P1;P1=0XFe; }。

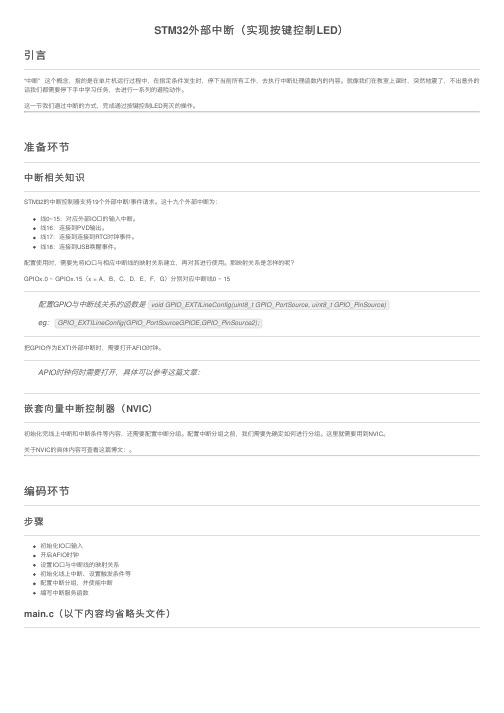

STM32外部中断(实现按键控制LED)

STM32外部中断(实现按键控制LED)引⾔“中断” 这个概念,指的是在单⽚机运⾏过程中,在指定条件发⽣时,停下当前所有⼯作,去执⾏中断处理函数内的内容。

就像我们在教室上课时,突然地震了,不出意外的话我们都需要停下⼿中学习任务,去进⾏⼀系列的避险动作。

这⼀节我们通过中断的⽅式,完成通过按键控制LED亮灭的操作。

准备环节中断相关知识STM32的中断控制器⽀持19个外部中断/事件请求。

这⼗九个外部中断为:线0~15:对应外部IO⼝的输⼊中断。

线16:连接到PVD输出。

线17:连接到连接到RTC时钟事件。

线18:连接到USB唤醒事件。

配置使⽤时,需要先将IO⼝与相应中断线的映射关系建⽴,再对其进⾏使⽤。

那映射关系是怎样的呢?GPIOx.0 ~ GPIOx.15(x = A,B,C,D,E,F,G)分别对应中断线0 ~ 15配置GPIO与中断线关系的函数是void GPIO_EXTILineConfig(uint8_t GPIO_PortSource, uint8_t GPIO_PinSource)eg:GPIO_EXTILineConfig(GPIO_PortSourceGPIOE,GPIO_PinSource2);把GPIO作为EXTI外部中断时,需要打开AFIO时钟。

APIO时钟何时需要打开,具体可以参考这篇⽂章:嵌套向量中断控制器(NVIC)初始化完线上中断和中断条件等内容,还需要配置中断分组。

配置中断分组之前,我们需要先确定如何进⾏分组。

这⾥就需要⽤到NVIC。

关于NVIC的具体内容可查看这篇博⽂:。

编码环节步骤初始化IO⼝输⼊开启AFIO时钟设置IO⼝与中断线的映射关系初始化线上中断、设置触发条件等配置中断分组,并使能中断编写中断服务函数main.c(以下内容均省略头⽂件)int main(void){delay_init();NVIC_PriorityGroupConfig(NVIC_PriorityGroup_2); //设置NVIC终端分组2LED_Init();KEY_Init();EXTIX_Init(); //外部中断初始化LED1 = 0;}exti.h#ifndef __EXTI_H#define __EXIT_H#include "sys.h"void EXTIX_Init(void); //外部中断初始化#endifexti.cvoid EXTIX_Init(void){EXTI_InitTypeDef EXTI_InitStructure; //外部中断结构体初始化NVIC_InitTypeDef NVIC_InitStructure; //中断分组结构体初始化KEY_Init();RCC_APB2PeriphClockCmd(RCC_APB2Periph_AFIO, ENABLE); //开启AFIO时钟GPIO_EXTILineConfig(GPIO_PortSourceGPIOA, GPIO_PinSource0); //映射IO⼝与中断线//以下为配置中断线初始化EXTI_InitStructure.EXTI_Mode = EXTI_Mode_Interrupt; //中断模式EXTI_InitStructure.EXTI_LineCmd = ENABLE; //使能中断线EXTI_InitStructure.EXTI_Line = EXTI_Line0; //中断线标号EXTI_InitStructure.EXTI_Trigger = EXTI_Trigger_Rising; //触发⽅式EXTI_Init(&EXTI_InitStructure);//以下为中断优先级的配置NVIC_InitStructure.NVIC_IRQChannel = EXTI0_IRQn; //声明使⽤的中断是哪⼀个NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0x02; //设置抢占优先级为2 NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0x03; //设置⼦优先级为3NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE; //使能中断NVIC_Init(&NVIC_InitStructure);}void EXTI0_IRQHandler(void) //中断服务函数{delay_ms(10); //软件去抖if(WK_UP==1){LED0 = !LED0;LED1 = !LED1;}EXTI_ClearITPendingBit(EXTI_Line0); //清除中断位}补充中断服务函数中断服务函数的名称是固定的,写错会导致⽆法中断。

第五章GPIO及外部中断的使用

功能描述

模拟输入 浮点输入 下拉输入 上拉输入 开漏输出 推挽输出 复用开漏输出 复用推挽输出

实例: 定义引脚PB0、PB1推挽输出,最大速率10MHz

GPIO_InitTypeDef GPIO_InitStructure;

//定义结构体

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOB,ENABLE); //开启GPIOB时 钟

第五章 GPIO及外部中断的使用

5.1 综述

STM32F10x系列端口:26、37、51、80、112个多功能 双向5V兼容的快速I/O口,所有I/O都可以映射到16个外部 中断。

STM32F10xxx系列中,每个通用I/O(GPIO)端口都有 7 个 寄 存 器 : 两 个 32 位 配 置 寄 存 器 ( GPIOx_CRL , GPIOx_CRH ) , 两 个 32 位 数 据 寄 存 器 ( GPIOx_IDR 和 GPIOx_ODR ) , 一 个 32 位 置 位 / 复 位 寄 存 器 ( GPIOx_BSRR),一个16位复位寄存器(GPIOx_BRR) 和一个32位锁存器(GPIOx_LCKP)。

5.2.1 函数GPIO_Init

3)GPIO_Mode 设置选中引脚的工作状态

GPIO_Mode可取值 GPIO_Mode_AIN GPIO_Mode_IN_FLOATING GPIO_Mode_IPD GPIO_Mode_IPU GPIO_Mode_Out_OD GPIO_Mode_Out_PP GPIO_Mode_AF_OD GPIO_Mode_AF_PP

返回值

无

先决条件 无

被调用函数 无

两个32位配置寄存器(GPIOx_CRL,GPIOx_CRH)

stm32外部中断实验原理

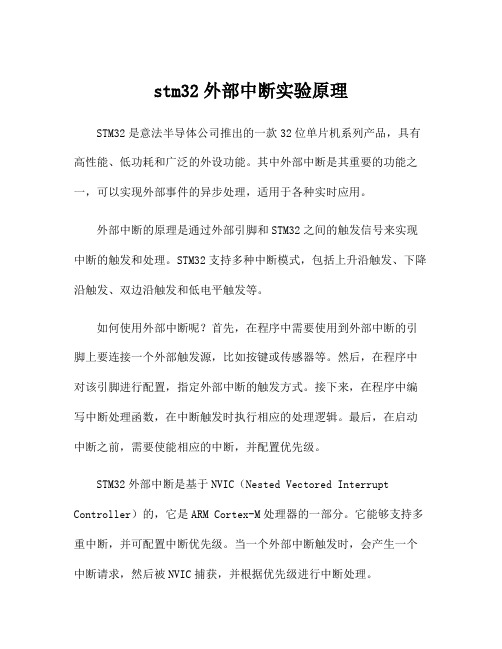

stm32外部中断实验原理STM32是意法半导体公司推出的一款32位单片机系列产品,具有高性能、低功耗和广泛的外设功能。

其中外部中断是其重要的功能之一,可以实现外部事件的异步处理,适用于各种实时应用。

外部中断的原理是通过外部引脚和STM32之间的触发信号来实现中断的触发和处理。

STM32支持多种中断模式,包括上升沿触发、下降沿触发、双边沿触发和低电平触发等。

如何使用外部中断呢?首先,在程序中需要使用到外部中断的引脚上要连接一个外部触发源,比如按键或传感器等。

然后,在程序中对该引脚进行配置,指定外部中断的触发方式。

接下来,在程序中编写中断处理函数,在中断触发时执行相应的处理逻辑。

最后,在启动中断之前,需要使能相应的中断,并配置优先级。

STM32外部中断是基于NVIC(Nested Vectored Interrupt Controller)的,它是ARM Cortex-M处理器的一部分。

它能够支持多重中断,并可配置中断优先级。

当一个外部中断触发时,会产生一个中断请求,然后被NVIC捕获,并根据优先级进行中断处理。

在硬件层面上,外部中断将通过外部中断控制器(EXTI)和GPIO控制器进行连接。

外部中断的引脚通过GPIO控制器配置为中断模式,并通过EXTI控制器与NVIC连接。

当外部触发源产生中断信号时,通过GPIO控制器将该中断信号传递给EXTI控制器,然后触发中断处理。

在软件编程方面,首先需要对GPIO和EXTI进行相应的初始化配置。

对于GPIO,我们需要设置引脚的模式、速度和上下拉等参数。

对于EXTI,我们需要设置中断触发方式(例如上升沿触发)和中断屏蔽(可以选择屏蔽或非屏蔽中断)等。

接着,使用STM32提供的库函数进行中断处理的配置。

首先,我们需要使用NVIC_Init函数来配置NVIC,使能相应的中断和设置中断优先级。

然后,使用EXTI_Init函数设置外部中断的触发方式和屏蔽等。

最后,编写中断处理函数,当外部中断触发时进行相应的处理。

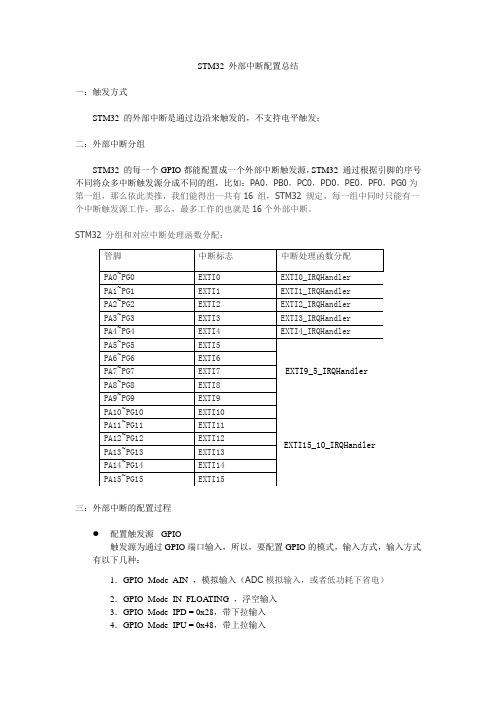

STM32外部中断总结

STM32 外部中断配置总结一:触发方式STM32 的外部中断是通过边沿来触发的,不支持电平触发;二:外部中断分组STM32 的每一个GPIO 都能配置成一个外部中断触发源,STM32 通过根据引脚的序号不同将众多中断触发源分成不同的组,比如:PA0,PB0,PC0,PD0,PE0,PF0,PG0为第一组,那么依此类推,我们能得出一共有16 组,STM32 规定,每一组中同时只能有一个中断触发源工作,那么,最多工作的也就是16个外部中断。

STM32 分组和对应中断处理函数分配:三:外部中断的配置过程配置触发源 -GPIO触发源为通过GPIO 端口输入,所以,要配置GPIO 的模式,输入方式,输入方式有以下几种:1.GPIO_Mode_AIN ,模拟输入(ADC 模拟输入,或者低功耗下省电)2.GPIO_Mode_IN_FLOATING ,浮空输入3.GPIO_Mode_IPD = 0x28,带下拉输入4.GPIO_Mode_IPU = 0x48,带上拉输入管脚 中断标志 中断处理函数分配PA0~PG0 EXTI0 EXTI0_IRQHandlerPA1~PG1 EXTI1 EXTI1_IRQHandlerPA2~PG2 EXTI2 EXTI2_IRQHandlerPA3~PG3 EXTI3 EXTI3_IRQHandler PA4~PG4 EXTI4 EXTI4_IRQHandler PA5~PG5 EXTI5 EXTI9_5_IRQHandler PA6~PG6 EXTI6 PA7~PG7 EXTI7 PA8~PG8 EXTI8 PA9~PG9 EXTI9 PA10~PG10 EXTI10 EXTI15_10_IRQHandler PA11~PG11 EXTI11 PA12~PG12 EXTI12 PA13~PG13 EXTI13 PA14~PG14 EXTI14 PA15~PG15 EXTI15●引脚与外部中断关联●外部中断AFIO时钟开启●外部中断配置这个主要是中断线路选择,中断触发方式,中断使能。

第5章 STM32系列微控制器开发基础

系统总线

连接Cortex-M3内核的系统总线(外设总线)到总线矩阵,总线矩阵协调着内核和DMA间 的访问。

DMA总线

将DMA的AHB主控接口与总线矩阵相联,总线矩阵协调着CPU的DCode和DMA到 SRAM、闪存和外设的访问。

总线矩阵

协调内核系统总线和DMA主控总线之间的访问仲裁,仲裁利用轮换算法。AHB外设通过 总线矩阵与系统总线相连,允许DMA访问。

时钟和启动

• 在启动的时候还是要进行系统时钟选择,但复位的 时候内部8MHz的晶振被选作CPU时钟。可以选择一 个外部的4-16MHz的时钟,并且会被监视判定是否 成功。

嵌入式系统原理与接口技术

11

5.2 STM32F103系列微控制器

功能概述

Boot模式

• 在启动的时候,boot引脚被用来在三种boot选项中的 选择一种:从用户Flash导入;从系统存储器导入; 从SRAM导入。boot导入程序位于系统存储器,用于 通过USART1重新对Flash存储器进行编程。

• STM32F103xx系列微控制器嵌入了一个嵌套矢量中 断控制器,可以处理43个可屏蔽中断通道(不包括 Cortex-M3的16根中断线),提供16个中断优先级。

嵌入式系统原理与接口技术

10

5.2 STM32F103系列微控制器

功能概述

外部中断/事件控制器(EXTI)

• 外部中断/事件控制器由用于19条产生中断/事件请 求的边沿探测器线组成。每条线可以被单独配置用 于选择触发事件(上升沿,下降沿或者两者都可 以),也可以被单独屏蔽。

嵌入式系统原理与接口技术

第5章 STM32系列微控制器开发基础

教师:姓名

5.1 STM32系列微控制器概述

STM32GPIO外部中断总结

GPIO引脚中断标志位中断处理函数PA0~PG0EXTI0EXTI0_IRQHandlerPA1~PG1EXTI1EXTI1_IRQHandlerPA2~PG2EXTI2EXTI2_IRQHandlerPA3~PG3EXTI3EXTI3_IRQHandlerPA4~PG4EXTI4EXTI4_IRQHandlerPA5~PG5EXTI5EXTI9_5_IRQHandler PA6~PG6EXTI6PA7~PG7EXTI7PA8~PG8EXTI8PA9~PG9EXTI9PA10~PG10EXTI10EXTI15_10_IRQHandler PA11~PG11EXTI11PA12~PG12EXTI12PA13~PG13EXTI13PA14~PG14EXTI14PA15~PG15EXTI15STM32GPIO外部中断总结⼀、STM32中断分组: STM32 的每⼀个GPIO都能配置成⼀个外部中断触发源,这点也是 STM32 的强⼤之处。

STM32 通过根据引脚的序号不同将众多中断触发源分成不同的组,⽐如:PA0,PB0,PC0,PD0,PE0,PF0,PG0为第⼀组,那么依此类推,我们能得出⼀共有16 组,STM32 规定,每⼀组中同时只能有⼀个中断触发源⼯作,那么,最多⼯作的也就是16个外部中断。

STM32F103 的中断控制器⽀持 19 个外部中断/事件请求。

每个中断设有状态位,每个中断/事件都有独⽴的触发和屏蔽设置。

STM32F103 的19 个外部中断为:线 0~15:对应外部 IO ⼝的输⼊中断。

线 16:连接到 PVD 输出。

线 17:连接到 RTC 闹钟事件。

线 18:连接到 USB 唤醒事件。

⼆:外部中断的配置过程: 1、配置触发源GPIO⼝: 因为GPIO⼝作为触发源使⽤,所以将GPIO⼝配置成输⼊模式,触发模式有以下⼏种: a.GPIO_Mode_AIN ,模拟输⼊(ADC模拟输⼊,或者低功耗下省电) b.GPIO_Mode_IN_FLOATING ,浮空输⼊ c.GPIO_Mode_IPD ,带下拉输⼊ d.GPIO_Mode_IPU ,带上拉输⼊ GPIO_InitTypeDef GPIO_InitStructure;//定义结构体 RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOE,ENABLE);//使能时钟 GPIO_InitStructure.GPIO_Pin = GPIO_Pin_2;//选择IO⼝ PE2 GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IPU;//设置成上拉输⼊ GPIO_Init(GPIOE, &GPIO_InitStructure);//使⽤结构体信息进⾏初始化IO⼝ 2、使能AFIO复⽤时钟功能: RCC_APB2PeriphClockCmd(RCC_APB2Periph_AFIO,ENABLE); 3、将GPIO⼝与中断线映射起来: GPIO_EXTILineConfig(GPIO_PortSourceGPIOE,GPIO_PinSource2); 4、中断线上进⾏中断初始化: EXTI_InitTypeDef EXTI_InitStructure;//定义初始化结构体 EXTI_InitStructure.EXTI_Line=EXTI_Line2; //中断线的标号取值范围为EXTI_Line0~EXTI_Line15 EXTI_InitStructure.EXTI_Mode = EXTI_Mode_Interrupt;//中断模式,可选值为中断 EXTI_Mode_Interrupt 和事件 EXTI_Mode_Event。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

5.2.3 中断控制器

NVIC为中断总开关:支持68个可屏蔽中断。提供16个 可编程的优先级,支持中断嵌套,提供向量中断处理 机制等功能。中断发生时,自动获得服务例程入口地 址并直接调用,无需软件判定中断源。主要包括:

中断设置允许寄存器(NVIC_ISER) 中断清除允许寄存器(NVIC_ICER) 中断设置挂起寄存器(NVIC_ISPR) 中断清除挂起寄存器(NVIC_ICPR) 中断状态寄存器(NVIC_IABR)控制。

ISPR[2]:全称Interrupt Set-Pending Registers,是 一个中断挂起控制寄存器组。

每个位对应的外部中断和ISER内容是一样的。通过 向相应的位写1,可以将正在执行的中断挂起,去执 行同级或更高级别的中断。向这个寄存器组写0是无 效的。

5.2.3 中断控制器

ICPR[2]:全称Interrupt Clear-Pending Registers,是单片机 的中断解挂寄存器组。 其功能和ISPR寄存器相反,对应位的内容也和ISER寄存器是 一样的。通过写1,可以将相应的中断解挂。写0无效。

IABR[2]:全称Interrupt Active Bit Registers,单片机中断激 活标志位寄存器组。 它是一个只读寄存器,CPU通过读取这个寄存器的相应位就 可以知道当前有哪些中断正在执行。在相应的中断执行完成 以后由硬件自动清零。对应位所代表的中断内容和ISER一样

5.2.3 中断控制器

与NVIC相关的寄存器 在“stm32f10x_map.h” 文件中定义了一个结构 体,结构体的内容如下

STM32F103系列单片机 的中断系统在这些寄存 器的控制下有序执行。 了解这些中断寄存器的 含义,才能更好的理解 STM32单片机中断系统 的工作原理

typedef struct {

5.2.3 中断控制器

ISER[2]:ISER全称是:Interrupt Set-Enable Registers,中断使能寄存器组。 STM32F103系列的单片机可屏蔽外部中断有60个, 用2个32位的ISER寄存器来表示,这2个32位的寄存 器总共可以表示64个外部中断。而STM32F103系列 单片机只用了ISER寄存器其中的前60位。 ISER[0]的bit0~bit31分别对应是外部中断0~31。 ISER[1]的bit0~27对应外部中断32~59;这样总共60 个外部中断就分别对应上了。 使能某个中断,必须设置相应的ISER位为1

5.1 中断的相关概念

中断服务程序与中断向量:为了处理中断而编写的程序称为 中断服务程序,对应中断服务程序的入口地址被称为中断向 量。 中断请求、中断响应、中断处理及中断返回:中断源对主程 序或中断服务程序提出中断要求,叫作中断请求;主程序或 中断服务程序接受中断请求,进入中断服务程序的过程叫作 中断响应;执行中断服务程序的过程叫作中断处理;中断服 务程序执行完毕后回到主程序或者次一级别中断服务程序的 过程叫作中断返回。 中断处理的整个过程包含了中断请求、中断响应、中断处理 及中断返回四个步骤。 中断系统:实现中断处理功能的软件、硬件系统称为中断系 统。

5.2.1 中断源

ARM Coetex-M3内核共支持256个中断,其中16 个内部中断,240个外部中断和可编程的256级中断优 先级的设置。STM32目前支持的中断共84个(16个内 部+68个外部),还有16级可编程的中断优先级的设 置,仅使用中断优先级设置8bit中的高4位。

5.2.2 中断向量:表5-1 给出STM32F103中断向量表

5.2.3 中断控制器

ICER[2]:全称Interrupt Clear-Enable Registers,是 一个中断清除使能寄存器组。

该寄存器组与ISER寄存器功能相反,用来清除某个 中断的使能位。由于NVIC的这些寄存器都是写1有 效的,写0是无效的。设置一组ICER 寄存器来清除 相应中断使能位。

第5章 STM32单片机外部中断

5.1 中断相关概念 5.2 STM32F103中断系统组成 5.3 中断控制 5.4 中断执行过程和中断嵌套 5.5 STM32外部中断应用设计

退出

5.1 中断的相关概念

中断:单片机执行主程序时,由于某个事件的原因,暂停主 程序的执行,调用相应的程序处理该事件,处理完毕后再自 动继续执行主程序的过程。 中断的优先级:由中断的嵌套可以看出,不同事件的重要程 度不同。重要的事件可以打断相对不重要的事件的处理,用 户可以根据自己的需求对不同的事件设定重要级别,称为中 断的优先级。 中断的嵌套:如果在执行一个中断时又被另一个更重要的事 件打断,暂停该中断处理过程转去处理这个更重要的事件, 处理完毕后再继续处理本中断的过程,叫作中断的嵌套。 中断源:可以引起中断的事件称为中断源。

嵌入式单片机原理及应用

电气工程学院仪器科学与工程系

退出

1 ARM嵌入式系统概述 2 STM32单片机结构和最小系统 3 基于标准外设库的C语言程序设计基础 4 STM32通用输入输出GPIO 5 STM32外部中断

6 STM32通用定时器 7 STM32通用同步/异步收发器USART 8 直接存储器存取DMA 9 STM32的模数转换器ADC 10 STM32的集成电路总线I2C 11 STM32的串行外设接口SPI

5.2 STM32F103中断系统组成

5.2.1中断源 STM32F103中断系统提供10个系统异常和60个可屏蔽 中断(STM32F107系列为68个)源,具有16个中断优 先级。 可屏蔽中断源包括:

外部中断、定时器中断、串口中断 直接内存访问中断 模数转换中断 集成电路总线中断 串行外设接口中断等。