第一章第二章习题及答案

高一物理必修1第一章、第二章知识点复习与习题与答案

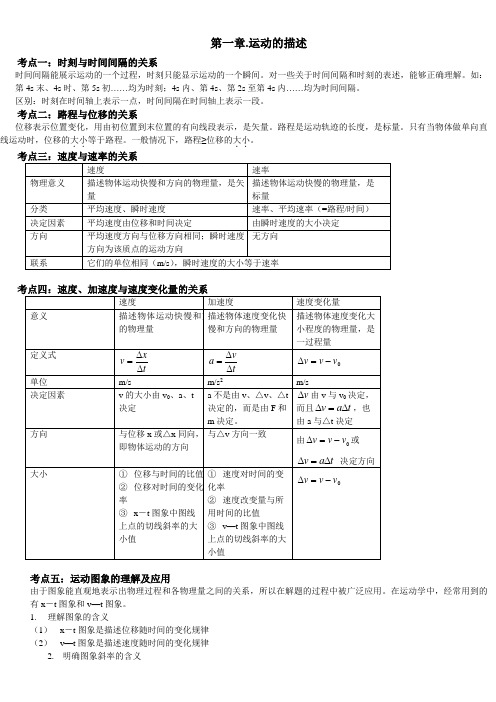

第一章.运动的描述考点一:时刻与时间间隔的关系时间间隔能展示运动的一个过程,时刻只能显示运动的一个瞬间。

对一些关于时间间隔和时刻的表述,能够正确理解。

如:第4s末、4s时、第5s初……均为时刻;4s内、第4s、第2s至第4s内……均为时间间隔。

区别:时刻在时间轴上表示一点,时间间隔在时间轴上表示一段。

考点二:路程与位移的关系位移表示位置变化,用由初位置到末位置的有向线段表示,是矢量。

路程是运动轨迹的长度,是标量。

只有当物体做单向直线运动时,位移的大小..。

..等于路程。

一般情况下,路程≥位移的大小考点五:运动图象的理解及应用由于图象能直观地表示出物理过程和各物理量之间的关系,所以在解题的过程中被广泛应用。

在运动学中,经常用到的有x-t图象和v—t图象。

1.理解图象的含义(1)x-t图象是描述位移随时间的变化规律(2)v—t图象是描述速度随时间的变化规律2.明确图象斜率的含义(1) x -t 图象中,图线的斜率表示速度 (2) v —t 图象中,图线的斜率表示加速度第二章.匀变速直线运动的研究考点一:匀变速直线运动的基本公式和推理1. 基本公式(1) 速度—时间关系式:at v v +=0 (2) 位移—时间关系式:2021at t v x += (3) 位移—速度关系式:ax v v 2202=-三个公式中的物理量只要知道任意三个,就可求出其余两个。

利用公式解题时注意:x 、v 、a 为矢量及正、负号所代表的是方向的不同, 解题时要有正方向的规定。

2. 常用推论(1) 平均速度公式:()v v v +=021(2) 一段时间中间时刻的瞬时速度等于这段时间内的平均速度:()v v v v t +==0221(3) 一段位移的中间位置的瞬时速度:22202v v v x +=(4) 任意两个连续相等的时间间隔(T )内位移之差为常数(逐差相等):()2aT n m x x x n m -=-=∆考点二:对运动图象的理解及应用1. 研究运动图象(1) 从图象识别物体的运动性质(2) 能认识图象的截距(即图象与纵轴或横轴的交点坐标)的意义 (3) 能认识图象的斜率(即图象与横轴夹角的正切值)的意义 (4) 能认识图象与坐标轴所围面积的物理意义 (5) 能说明图象上任一点的物理意义 2. x -t 图象和v —t 图象的比较如图所示是形状一样的图线在x -t 图象和v —t 图象中,1.“追及”、“相遇”的特征“追及”的主要条件是:两个物体在追赶过程中处在同一位置。

《现代控制理论》课后习题全部答案(最完整打印版)

第一章习题答案1-1试求图1-27系统的模拟结构图,并建立其状态空间表达式。

解:系统的模拟结构图如下:系统的状态方程如下:阿令,则所以,系统的状态空间表达式及输出方程表达式为状态变量的状态方程,和以电阻上的电压作为输出量的输出方程。

解:由图,令,输出量有电路原理可知:既得写成矢量矩阵形式为:1-3参考例子1-3(P19).1-4两输入,,两输出,的系统,其模拟结构图如图1-30所示,试求其状态空间表达式和传递函数阵。

解:系统的状态空间表达式如下所示:1-5系统的动态特性由下列微分方程描述列写其相应的状态空间表达式,并画出相应的模拟结构图。

解:令,则有相应的模拟结构图如下:1-6(2)已知系统传递函数,试求出系统的约旦标准型的实现,并画出相应的模拟结构图解:1-7给定下列状态空间表达式(1)画出其模拟结构图(2)求系统的传递函数解:(2)1-8求下列矩阵的特征矢量(3)解:A的特征方程解之得:当时,解得:令得(或令,得)当时,解得:令得(或令,得)当时,解得:令得1-9将下列状态空间表达式化成约旦标准型(并联分解)(2)解:A的特征方程当时,解之得令得当时,解之得令得当时,解之得令得约旦标准型1-10已知两系统的传递函数分别为W1(s)和W2(s)试求两子系统串联联结和并联连接时,系统的传递函数阵,并讨论所得结果解:(1)串联联结(2)并联联结1-11(第3版教材)已知如图1-22所示的系统,其中子系统1、2的传递函数阵分别为求系统的闭环传递函数解:1-11(第2版教材)已知如图1-22所示的系统,其中子系统1、2的传递函数阵分别为求系统的闭环传递函数解:1-12已知差分方程为试将其用离散状态空间表达式表示,并使驱动函数u的系数b(即控制列阵)为(1)解法1:解法2:求T,使得得所以所以,状态空间表达式为第二章习题答案2-4用三种方法计算以下矩阵指数函数。

(2)A=解:第一种方法:令则,即。

求解得到,当时,特征矢量由,得即,可令当时,特征矢量由,得即,可令则,第二种方法,即拉氏反变换法:第三种方法,即凯莱—哈密顿定理由第一种方法可知,2-5下列矩阵是否满足状态转移矩阵的条件,如果满足,试求与之对应的A阵。

汽车理论习题指导及参考答案(清华-修改4)

目录第一章汽车的动力性............................. 错误!未定义书签。

第二章汽车的燃油经济性......................... 错误!未定义书签。

第三章汽车动力装置参数的选定................... 错误!未定义书签。

第四章汽车的制动性............................. 错误!未定义书签。

第五章汽车的操纵稳定性......................... 错误!未定义书签。

第六章汽车的平顺性............................. 错误!未定义书签。

第一章 汽车的动力性试说明轮胎滚动阻力的定义,产生机理和作用形式。

答:车轮滚动时,由于车轮的弹性变形、路面变形和车辙摩擦等原因所产生的阻碍汽车行驶的力称为轮胎滚动阻力。

产生机理和作用形式:(1) 弹性轮胎在硬路面上滚动时,轮胎的变形是主要的,由于轮胎有内部摩擦,产生弹性迟滞损失,使轮胎变形时对它做的功不能全部回收。

由于弹性迟滞,地面对车轮的法向作用力并不是前后对称的,这样形成的合力z F 并不沿车轮中心(向车轮前进方向偏移a )。

如果将法向反作用力平移至与通过车轮中心的垂线重合,则有一附加的滚动阻力偶矩f z T F a =⋅。

为克服该滚动阻力偶矩,需要在车轮中心加一推力P F 与地面切向反作用力构成一力偶矩。

(2)轮胎在松软路面上滚动时,由于车轮使地面变形下陷,在车轮前方实际形成了具有一定坡度的斜面,对车轮前进产生阻力。

(3)轮胎在松软地面滚动时,轮辙摩擦会引起附加阻力。

(4)车轮行驶在不平路面上时,引起车身振荡、减振器压缩和伸长时做功,也是滚动阻力的作用形式。

滚动阻力系数与哪些因素有关答:滚动阻力系数与路面的种类、行驶车速以及轮胎的构造、材料和气压有关。

这些因素对滚动阻力系数的具体影响参考课本P9。

确定一轻型货车的动力性能(货车可装用4挡或5挡变速器,任选其中的一种进行整车性能计算):1)绘制汽车驱动力与行驶阻力平衡图。

数据库第一章第二章练习题

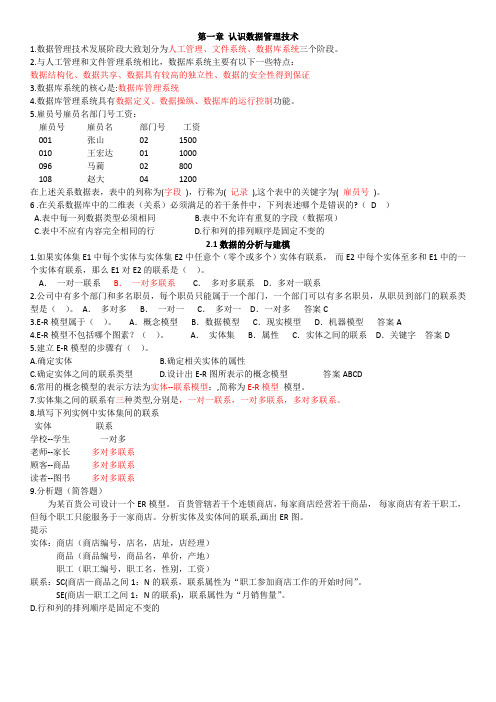

第一章认识数据管理技术1.数据管理技术发展阶段大致划分为人工管理、文件系统、数据库系统三个阶段。

2.与人工管理和文件管理系统相比,数据库系统主要有以下一些特点:数据结构化、数据共享、数据具有较高的独立性、数据的安全性得到保证3.数据库系统的核心是:数据库管理系统4.数据库管理系统具有数据定义、数据操纵、数据库的运行控制功能。

5.雇员号雇员名部门号工资:雇员号雇员名部门号工资001 张山02 1500010 王宏达01 1000096 马蔺02 800108 赵大04 1200在上述关系数据表,表中的列称为(字段),行称为( 记录),这个表中的关键字为( 雇员号)。

6 .在关系数据库中的二维表(关系)必须满足的若干条件中,下列表述哪个是错误的?(D )A.表中每一列数据类型必须相同B.表中不允许有重复的字段(数据项)C.表中不应有内容完全相同的行D.行和列的排列顺序是固定不变的2.1数据的分析与建模1.如果实体集E1中每个实体与实体集E2中任意个(零个或多个)实体有联系,而E2中每个实体至多和E1中的一个实体有联系,那么E1对E2的联系是()。

A.一对一联系B.一对多联系C.多对多联系D.多对一联系2.公司中有多个部门和多名职员,每个职员只能属于一个部门,一个部门可以有多名职员,从职员到部门的联系类型是()。

A.多对多B.一对一C.多对一D.一对多答案C3.E-R模型属于()。

A.概念模型B.数据模型C.现实模型D.机器模型答案A4.E-R模型不包括哪个图素?()。

A.实体集B.属性C.实体之间的联系D.关键字答案D5.建立E-R模型的步骤有()。

A.确定实体B.确定相关实体的属性C.确定实体之间的联系类型D.设计出E-R图所表示的概念模型答案ABCD6.常用的概念模型的表示方法为实体--联系模型:,简称为E-R模型模型。

7.实体集之间的联系有三种类型,分别是,一对一联系,一对多联系,多对多联系。

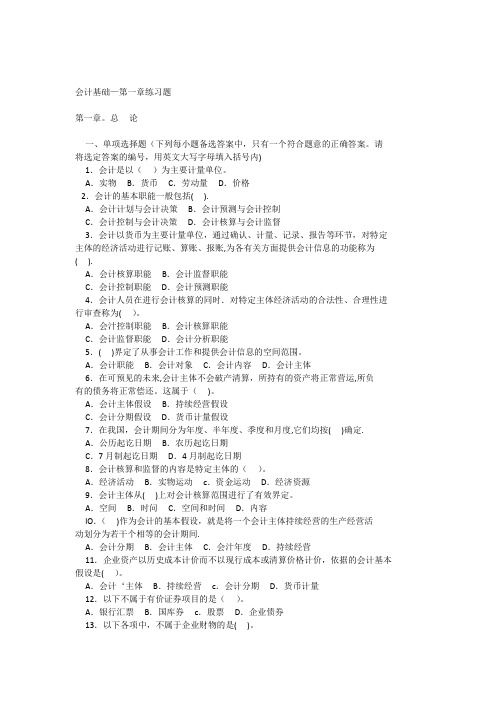

会计基础第一章第二章习题

会计基础—第一章练习题第一章。

总论一、单项选择题(下列每小题备选答案中,只有一个符合题意的正确答案。

请将选定答案的编号,用英文大写字母填入括号内)1.会计是以()为主要计量单位。

A.实物B.货币C.劳动量D.价格2.会计的基本职能一般包括().A.会计计划与会计决策B.会计预测与会计控制C.会计控制与会计决策D.会计核算与会计监督3.会计以货币为主要计量单位,通过确认、计量、记录、报告等环节,对特定主体的经济活动进行记账、算账、报账,为各有关方面提供会计信息的功能称为().A.会计核算职能B.会计监督职能C.会计控制职能D.会计预测职能4.会计人员在进行会计核算的同时.对特定主体经济活动的合法性、合理性进行审查称为()。

A.会汁控制职能B.会计核算职能C.会计监督职能D.会计分析职能5.()界定了从事会计工作和提供会计信息的空间范围。

A.会计职能B.会计对象C.会计内容D.会计主体6.在可预见的未来,会计主体不会破产清算,所持有的资产将正常营运,所负有的债务将正常偿还。

这属于()。

A.会计主体假设B.持续经营假设C.会计分期假设D.货币计量假设7.在我国,会计期间分为年度、半年度、季度和月度,它们均按()确定.A.公历起讫日期B.农历起讫日期C.7月制起讫日期D.4月制起讫日期8.会计核算和监督的内容是特定主体的()。

A.经济活动B.实物运动c.资金运动D.经济资源9.会计主体从()上对会计核算范围进行了有效界定。

A.空间B.时问C.空间和时间D.内容lO.()作为会计的基本假设,就是将一个会计主体持续经营的生产经营活动划分为若干个相等的会计期间.A.会计分期B.会计主体C.会汁年度D.持续经营11.企业资产以历史成本计价而不以现行成本或清算价格计价,依据的会计基本假设是()。

A.会计‘主体B.持续经营c.会计分期D.货币计量12.以下不属于有价证券项目的是()。

A.银行汇票B.国库券c.股票D.企业债券13.以下各项中,不属于企业财物的是()。

液压与气压传动第三版 许福玲 习题及答案(第一章,第二章)

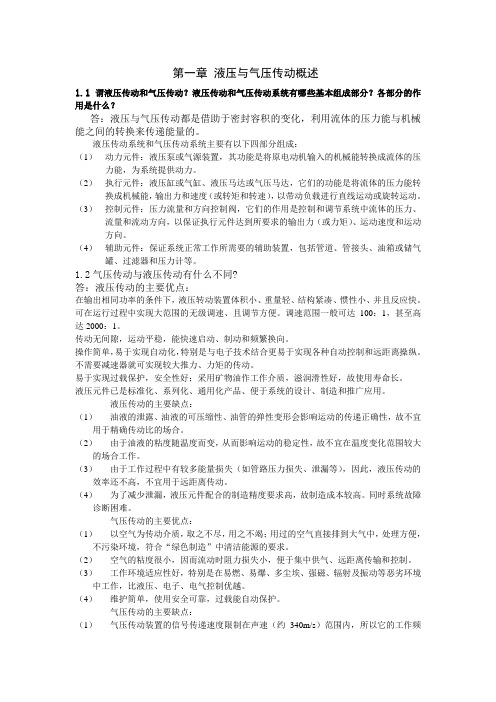

第一章液压与气压传动概述1.1谓液压传动和气压传动?液压传动和气压传动系统有哪些基本组成部分?各部分的作用是什么?答:液压与气压传动都是借助于密封容积的变化,利用流体的压力能与机械能之间的转换来传递能量的。

液压传动系统和气压传动系统主要有以下四部分组成:(1)动力元件:液压泵或气源装置,其功能是将原电动机输入的机械能转换成流体的压力能,为系统提供动力。

(2)执行元件:液压缸或气缸、液压马达或气压马达,它们的功能是将流体的压力能转换成机械能,输出力和速度(或转矩和转速),以带动负载进行直线运动或旋转运动。

(3)控制元件:压力流量和方向控制阀,它们的作用是控制和调节系统中流体的压力、流量和流动方向,以保证执行元件达到所要求的输出力(或力矩)、运动速度和运动方向。

(4)辅助元件:保证系统正常工作所需要的辅助装置,包括管道、管接头、油箱或储气罐、过滤器和压力计等。

1.2气压传动与液压传动有什么不同?答:液压传动的主要优点:在输出相同功率的条件下,液压转动装置体积小、重量轻、结构紧凑、惯性小、并且反应快。

可在运行过程中实现大范围的无级调速、且调节方便。

调速范围一般可达100:1,甚至高达2000:1。

传动无间隙,运动平稳,能快速启动、制动和频繁换向。

操作简单,易于实现自动化,特别是与电子技术结合更易于实现各种自动控制和远距离操纵。

不需要减速器就可实现较大推力、力矩的传动。

易于实现过载保护,安全性好;采用矿物油作工作介质,滋润滑性好,故使用寿命长。

液压元件已是标准化、系列化、通用化产品、便于系统的设计、制造和推广应用。

液压传动的主要缺点:(1)油液的泄露、油液的可压缩性、油管的弹性变形会影响运动的传递正确性,故不宜用于精确传动比的场合。

(2)由于油液的粘度随温度而变,从而影响运动的稳定性,故不宜在温度变化范围较大的场合工作。

(3)由于工作过程中有较多能量损失(如管路压力损失、泄漏等),因此,液压传动的效率还不高,不宜用于远距离传动。

中国法制史习题集及参考答案

中国法制史习题集及参考答案第一章中国奴隶制法概述一、填空题1、我国奴隶社会法律规范的两种基本形式是()和()。

2、宗法制度是在原始社会后期的父权家长制基础上演变而来的一种以()为纽带、以()统治为核心的综合性的社会制度。

3、据商代资料,商代中期以后,主要是实行兄终弟及或父死子继,并出现了()继承制。

二、判断题1、夏礼和殷礼无论在内容和形式上都以神为核心。

()2、中国法起源于贵族与平民的斗争与妥协。

()3、中国奴隶制时代的礼起源于原始氏族的祭祀活动。

()三、简答题:1、试述西周的宗法制度。

2、简述西周的继承制度。

第二章中国奴隶社会的立法一、填空题1、春秋时期正式公布的成文法有郑国()、晋国()和邓析的竹刑。

2、中国法制史上第一部正式公布的成文法典,是郑子产所铸的()。

3、第一次礼法之争的焦点是为国以礼还是()的问题。

二、名词解释1、铸刑书2、铸刑鼎3、竹刑三、简答题试述春秋时期成文法的公布及意义。

第三章中国奴隶制时代的法律制度分论一、判断1、所谓“三不去”包括有所取无所归不去、前贫贱后富贵不去、与更三年丧不去。

()2、三不去制度的立法精神,是为了保护妇女的权益。

()3、奴隶制五刑包括自由刑。

()4、西周的民本思想是以人为本。

()二、名词解释1、以德配天2、明德慎罚3、出礼入刑4、五刑5、六礼6、同姓不婚7、五过之疵8、五声听狱讼三、简答题1、简述西周礼与刑的关系。

2、怎样理解“礼不下庶人,刑不上大夫”?3、简述西周的婚姻制度。

4、简述西周诉讼审判制度的主要内容。

第四章中国奴隶制时代重要法制人物点评简答题1、简述周公在中国法制史上的地位。

2、论孔子的法律思想在中国法制史上的地位。

第五章中国封建制法概述一、填空题1、礼与法的关系问题的实质,是儒家所提倡的()法律规范与法家所倡导的()法律规范的矛盾与协调问题。

2、西汉时代的“引经决狱”打开了法律儒家化的开端,东汉时代的以经注律开辟了法律儒家化的新途径,魏晋时代的()完成了法律儒家化的过程。

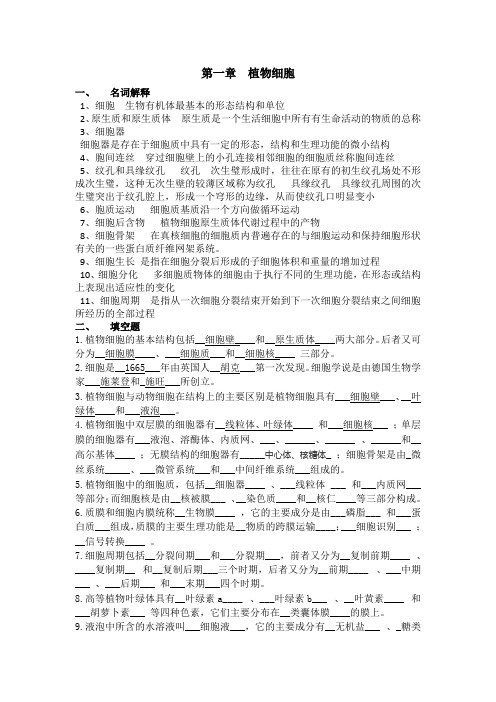

植物学第一章第二章复习题-凑合着看的参考答案-(xз」∠)-

第一章植物细胞一、名词解释1、细胞生物有机体最基本的形态结构和单位2、原生质和原生质体原生质是一个生活细胞中所有有生命活动的物质的总称3、细胞器细胞器是存在于细胞质中具有一定的形态,结构和生理功能的微小结构4、胞间连丝穿过细胞壁上的小孔连接相邻细胞的细胞质丝称胞间连丝5、纹孔和具缘纹孔纹孔次生璧形成时,往往在原有的初生纹孔场处不形成次生璧,这种无次生壁的较薄区域称为纹孔具缘纹孔具缘纹孔周围的次生璧突出于纹孔腔上,形成一个穹形的边缘,从而使纹孔口明显变小6、胞质运动细胞质基质沿一个方向做循环运动7、细胞后含物植物细胞原生质体代谢过程中的产物8、细胞骨架在真核细胞的细胞质内普遍存在的与细胞运动和保持细胞形状有关的一些蛋白质纤维网架系统。

9、细胞生长是指在细胞分裂后形成的子细胞体积和重量的增加过程10、细胞分化多细胞质物体的细胞由于执行不同的生理功能,在形态或结构上表现出适应性的变化11、细胞周期是指从一次细胞分裂结束开始到下一次细胞分裂结束之间细胞所经历的全部过程二、填空题1.植物细胞的基本结构包括__细胞壁____和__原生质体____两大部分。

后者又可分为__细胞膜____、___细胞质___和__细胞核____ 三部分。

2.细胞是__1665___年由英国人__胡克___第一次发现。

细胞学说是由德国生物学家___施莱登和_施旺___所创立。

3.植物细胞与动物细胞在结构上的主要区别是植物细胞具有___细胞壁___、__叶绿体____和___液泡___。

4.植物细胞中双层膜的细胞器有__线粒体、叶绿体____ 和___细胞核___ ;单层膜的细胞器有___液泡、溶酶体、内质网、___、______、______ 、______和__高尔基体____ ;无膜结构的细胞器有_____中心体、核糖体_ ;细胞骨架是由_微丝系统_____、___微管系统___和___中间纤维系统___组成的。

5.植物细胞中的细胞质,包括__细胞器____ 、___线粒体 ___ 和___内质网___ 等部分;而细胞核是由__核被膜___ 、__染色质____和__核仁____等三部分构成。

《公司财务》练习题及参考答案1

《公司财务》练习题及参考答案第一章公司财务总论第二章财务估价练习题1.资金时间价值相关计算:(1)某公司2008年年初对某项目投资100万元,预计该项目2010年年初完工投产。

2010年、2011年、2012年年末预期收益各为20万元、30万元、50万元。

若公司资金成本为10% ,求:按复利计算2010年年初投资额的终值和2010年年初各年预期收益的现值之和。

(2)某公司2008年初对某项目投资250万元,预计该项目2009年年末完工投产。

2010年、2011年、2012年年末预期收益均为100万元。

若该公司资金成本为10% ,求:按复利计算2008年年初各年预期收益的现值之和。

(3) 某企业租用设备一台,在10年中每年年初支付1000元,年利息率5%,问:这些租金的现值是多少?2.大华公司于2008年6月30日发行票面价格为100元,票面利率10%的债券,期限为3年,利息分别在每年12月31日和6月30日支付,求市场利率为12%时该债券的价格。

估计今后年股利增长率为5%。

投资者期望的收益率为15%,请计算该股票的价值。

答案:1、(1)2010年年初投资额的终值F=100*(F/P,10%,2)=100*1.21=121万元2010年年初各年预期收益的现值之和=20*(P/F,10%,1)+30*(P/F,10%,2)+50*(P/F,10%,3)=20*0.90909+30*0.82645+50*0.75131=80.5408 万元(2)2008年年初各年预期收益的现值之和=100*(P/A,10%,3)*(P/F,10%,2)=100*2.48685*0.82645=205.53万元(3) P=1000*[(P/A,5%,10-1)+1]=1000*(7.10782 +1)=8107.82元2、V=100*(P/F, 12%/2, 2*3)+100*10%/2*(P/A, 12%/2, 2*3)=100*0.70496 +5*4.91732 =95.0826元3、V=10(1+5%)/(15%-5%)=105元第三章筹资方式练习题1.某公司发行可转换债券,该债券面值为1 000元,期限为10年,年利率为4%,市场利率为5%。

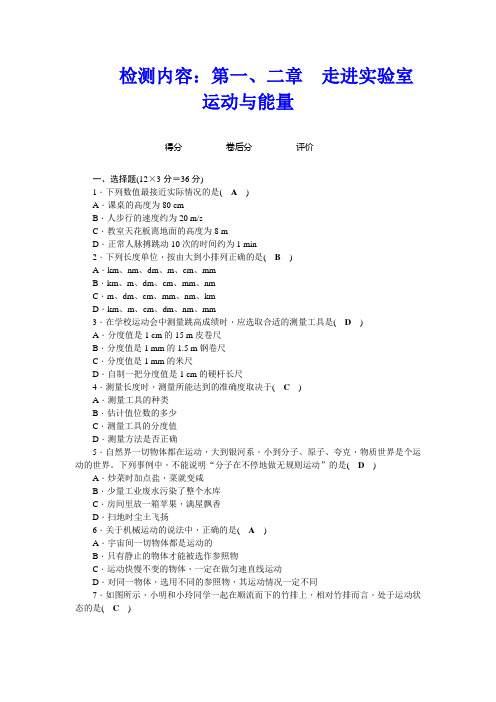

2022年教科版八年级物理上册练习题及答案7份- 第一章、第二章.doc

检测内容:第一、二章走进实验室运动与能量得分________卷后分________评价________一、选择题(12×3分=36分)1.下列数值最接近实际情况的是(A)A.课桌的高度为80 cmB.人步行的速度约为20 m/sC.教室天花板离地面的高度为8 mD.正常人脉搏跳动10次的时间约为1 min2.下列长度单位,按由大到小排列正确的是(B)A.km、nm、dm、m、cm、mmB.km、m、dm、cm、mm、nmC.m、dm、cm、mm、nm、kmD.km、m、cm、dm、nm、mm3.在学校运动会中测量跳高成绩时,应选取合适的测量工具是(D)A.分度值是1 cm的15 m皮卷尺B.分度值是1 mm的1.5 m钢卷尺C.分度值是1 mm的米尺D.自制一把分度值是1 cm的硬杆长尺4.测量长度时,测量所能达到的准确度取决于(C)A.测量工具的种类B.估计值位数的多少C.测量工具的分度值D.测量方法是否正确5.自然界一切物体都在运动,大到银河系,小到分子、原子、夸克,物质世界是个运动的世界。

下列事例中,不能说明“分子在不停地做无规则运动”的是(D) A.炒菜时加点盐,菜就变咸B.少量工业废水污染了整个水库C.房间里放一箱苹果,满屋飘香D.扫地时尘土飞扬6.关于机械运动的说法中,正确的是(A)A.宇宙间一切物体都是运动的B.只有静止的物体才能被选作参照物C.运动快慢不变的物体,一定在做匀速直线运动D.对同一物体,选用不同的参照物,其运动情况一定不同7.如图所示,小明和小玲同学一起在顺流而下的竹排上,相对竹排而言,处于运动状态的是(C)A.小明同学B.小玲同学C.岸边的山D.竹排上的凳子8.在飞机降落的时候,小明向外望时觉得大地向他扑过来,这是他以哪个物体做参照物(B)A.地面B.飞机C.飞机场D.无法判断9.甲、乙两小车同时同地同方向做匀速直线运动,它们的s-t图像如图所示。

经过6秒,两车的位置关系是(A)A.甲在乙前面0.3米处B.甲在乙前面0.6米处C.乙在甲前面0.3米处D.乙在甲前面0.6米处10.一列队伍长50 m,跑步速度是2.5 m/s,队伍全部通过一长100 m的涵洞,需要的时间是(A)A.60 s B.50 s C.40 s D.20 s11.甲、乙两辆汽车行驶在平直的公路上,甲车上的乘客看乙车在向北运动,乙车上的乘客看到甲车和树木都向南运动。

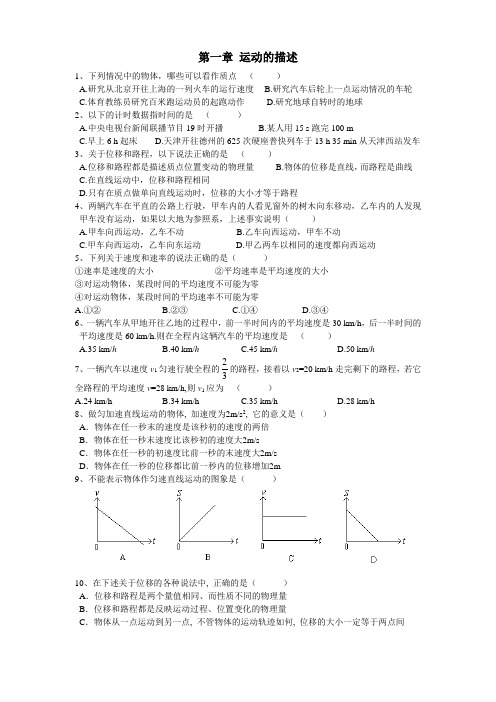

高一物理必修1第一章、第二章习题与答案

第一章 运动的描述1、下列情况中的物体,哪些可以看作质点 ( )A.研究从北京开往上海的一列火车的运行速度B.研究汽车后轮上一点运动情况的车轮C.体育教练员研究百米跑运动员的起跑动作D.研究地球自转时的地球2、以下的计时数据指时间的是 ( )A.中央电视台新闻联播节目19时开播B.某人用15 s 跑完100 mC.早上6 h 起床D.天津开往德州的625次硬座普快列车于13 h 35 min 从天津西站发车3、关于位移和路程,以下说法正确的是 ( )A.位移和路程都是描述质点位置变动的物理量B.物体的位移是直线,而路程是曲线C.在直线运动中,位移和路程相同D.只有在质点做单向直线运动时,位移的大小才等于路程4、两辆汽车在平直的公路上行驶,甲车内的人看见窗外的树木向东移动,乙车内的人发现甲车没有运动,如果以大地为参照系,上述事实说明( )A.甲车向西运动,乙车不动B.乙车向西运动,甲车不动C.甲车向西运动,乙车向东运动D.甲乙两车以相同的速度都向西运动5、下列关于速度和速率的说法正确的是( )①速率是速度的大小 ②平均速率是平均速度的大小③对运动物体,某段时间的平均速度不可能为零④对运动物体,某段时间的平均速率不可能为零A.①②B.②③C.①④D.③④6、一辆汽车从甲地开往乙地的过程中,前一半时间内的平均速度是30 km/h ,后一半时间的平均速度是60 km/h.则在全程内这辆汽车的平均速度是 ( )A.35 km/hB.40 km/hC.45 km/hD.50 km/h7、一辆汽车以速度v 1匀速行驶全程的32的路程,接着以v 2=20 km/h 走完剩下的路程,若它全路程的平均速度v =28 km/h,则v 1应为 ( )A.24 km/hB.34 km/hC.35 km/hD.28 km/h8、做匀加速直线运动的物体, 加速度为2m/s 2, 它的意义是( )A .物体在任一秒末的速度是该秒初的速度的两倍B .物体在任一秒末速度比该秒初的速度大2m/sC .物体在任一秒的初速度比前一秒的末速度大2m/sD .物体在任一秒的位移都比前一秒内的位移增加2m9、不能表示物体作匀速直线运动的图象是( )10、在下述关于位移的各种说法中, 正确的是( )A .位移和路程是两个量值相同、而性质不同的物理量B .位移和路程都是反映运动过程、位置变化的物理量C .物体从一点运动到另一点, 不管物体的运动轨迹如何, 位移的大小一定等于两点间的距离D.位移是矢量, 物体运动的方向就是位移的方向11、下列说法正确的是()A.匀速直线运动就是速度大小不变的运动B.在相等的时间里物体的位移相等, 则物体一定匀速直线运动C.一个做直线运动的物体第一秒内位移1m, 则第一秒内的平均速度一定是1m / sD.一个做直线运动的物体第一秒内的位移1m, 则1秒末的即时速度一定是1m / s12、对做匀减速运动的物体(无往返),下列说法中正确的是()A.速度和位移都随时间减小B.速度和位移都随时间增大C.速度随时间增大,位移随时间减小D.速度随时间减小,位移随时间增大13、下面关于加速度的描述中正确的有()B.加速度在数值上等于单位时间里速度的变化C.当加速度与位移方向相反时,物体做减速运动D.当加速度与速度方向相同且又减小时,物体做减速运动14、甲、乙两物体沿一直线同向运动,其速度图象如图所示,在 t时刻,下列物理量中相等的是()A.运动时间B.速度C.位移D.加速度15、骑自行车的人沿着直线从静止开始运动,运动后,在第1、2、3、4秒内,通过的路程分别为1米、2米、3米、4米。

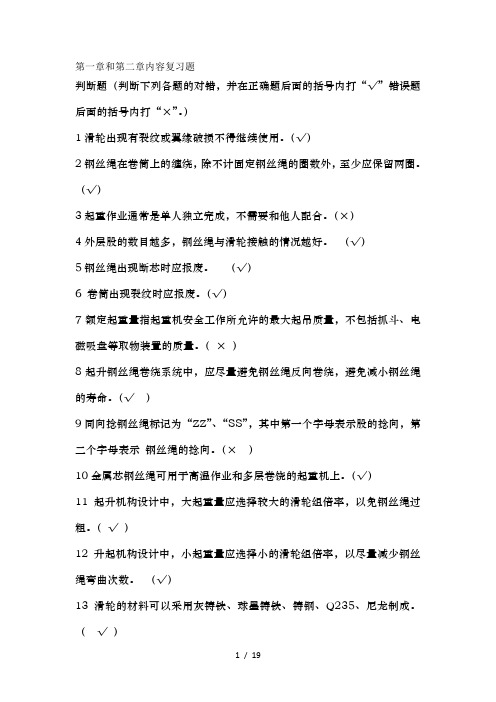

起重机习题有答案版

第一章和第二章内容复习题判断题(判断下列各题的对错,并在正确题后面的括号内打“√”错误题后面的括号内打“×”。

)1滑轮出现有裂纹或翼缘破损不得继续使用。

(√)2钢丝绳在卷筒上的缠绕,除不计固定钢丝绳的圈数外,至少应保留两圈。

(√)3起重作业通常是单人独立完成,不需要和他人配合。

(×)4外层股的数目越多,钢丝绳与滑轮接触的情况越好。

(√)5钢丝绳出现断芯时应报废。

(√)6 卷筒出现裂纹时应报废。

(√)7额定起重量指起重机安全工作所允许的最大起吊质量,不包括抓斗、电磁吸盘等取物装置的质量。

(×)8起升钢丝绳卷绕系统中,应尽量避免钢丝绳反向卷绕,避免减小钢丝绳的寿命。

(√)9同向捻钢丝绳标记为“ZZ”、“SS”,其中第一个字母表示股的捻向,第二个字母表示钢丝绳的捻向。

(×)10金属芯钢丝绳可用于高温作业和多层卷饶的起重机上。

(√)11起升机构设计中,大起重量应选择较大的滑轮组倍率,以免钢丝绳过粗。

(√)12升起机构设计中,小起重量应选择小的滑轮组倍率,以尽量减少钢丝绳弯曲次数。

(√)13滑轮的材料可以采用灰铸铁、球墨铸铁、铸钢、Q235、尼龙制成。

(√)14滑轮组的倍率等于承载分支数比上绕入卷筒分支数。

(√)15吊钩的材料要求没有突然断裂的危险,故不允许使用铸造方法或焊接制造的吊钩。

(√)16起重机吊钩磨损后,必须与时补焊方可使用。

(√)17在起重机各机构中,通常将制动器安装在机构的低速轴上。

(×)18起重机运行机构产生“啃轨”故障与车轮安装角度超差无关。

(×)19起重机运行机构的两个电机不同步也将产生“啃轨”故障。

(√)20起重机车轮多采用锻钢制造。

(×)21为了减少摩擦阻力,起重机车轮踏面应经常润滑。

(×)22起重机吊钩上的缺陷可以焊补。

(×)选择题1制动器的制动衬垫磨损达原厚度的(B)%时应报废。

A. 40B. 50C. 60D. 702在具有腐蚀性气体场合使用的起重机应采用( C )钢丝绳。

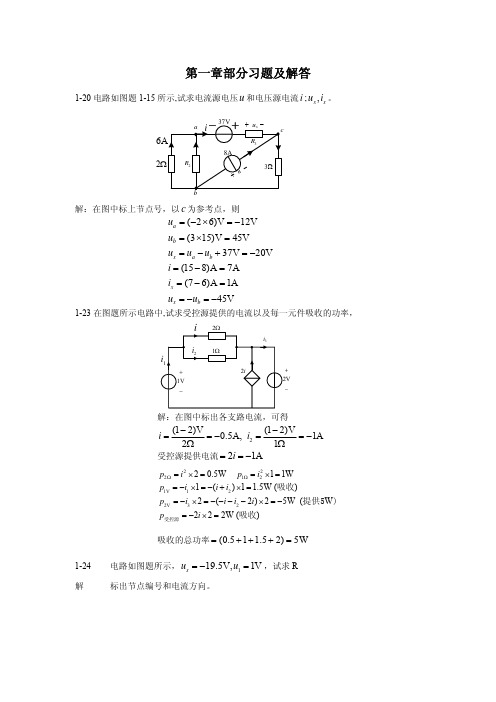

电路分析基础第四版课后习题第一章第二章第三章第四章答案

+ 42V

−

i1

18Ω

i2 3Ω

i3

gu

2−5

解

设网孔电流为 i1, i2 , i3 ,则 i3 = −guA = −0.1uA ,所以只要列出两个网孔方程

27i1 −18i2 = 42 −18i1 + 21i2 − 3(−0.1uA ) = 20

因 uA = 9i1 ,代入上式整理得

−15.3i1 + 21i2 = 20

⎪⎩i3 = 4A

第二章部分习题及解答

2-1 试用网孔电流法求图题所示电路中的电流 i 和电压 uab 。

4Ω

1Ω

i2

+

7V

−

i1

2Ω

i3 i

+ 3V

−

解

设网孔电流为 i1, i2 ,i3 ,列网孔方程

⎪⎨⎧3−ii11

− i2 − 2i3 = 7 + 8i2 − 3i3 = 9

⎪⎩−2i1 − 3i2 + 5i3 = −12

解得

i1 = 4.26A uA = (9× 4.26)V = 38.34V i3 = −0.1uA = −3.83A

2-8 含 CCVS 电路如图题 2-6 所示,试求受控源功率。

1Ω i3

5Ω

+

i 4Ω

+

50V i1 −

20Ω i2

15i −

2−6

解

标出网孔电流及方向,

⎧⎪⎨2−52i01i−1 +202i42i−2 −5i43 i=3

50 = −15i

⎪⎩−5i1 − 4i2 +10i3 = 0

又受控源控制量 i 与网孔电流的关系为 i = i1 − i2

《材料科学基础》习题及参考答案

形核功,还是可以成核的。

答案

(7)测定某纯金属铸件结晶时的最大过冷度,其实测

值与用公式ΔT=0.2Tm计算值基本一致。

答案

(8) 某些铸件结晶时,由于冷却较快,均匀形核率N1

提高,非均匀形核率N2也提高,故总的形核率为N=

N1 +N2。

答案

返回

53

(9) 若在过冷液体中,外加10 000颗形核剂,则结晶

❖ ②比较Cu-10% Sn合金铸件和Cu-30%合金铸件的铸造性能 及铸造组织,说明Cu-10% Sn合金铸件中有许多分散砂眼的 原因。

③ω(Sn}分别为2%,11%和15%的青铜合金,哪一种可进行 压力加工?哪种可利用铸造法来制造机件?

答案

返7回8

❖ 9.如下图所示,已知A,B,C三组元固态完全不互溶,质量 分数分别84%A,,10%B,10%C的O合金在冷却过程中将进 行二元共晶反应和三元共晶反应,在二元共晶反应开始时, 该合金液相成分(a点)为60%A,20%B,20%C,而三元共 晶反应开始时的液相成分(E点)为50%A,10%B,40%C。

答案

返回

6

❖ 6.位错受力后运动方向处处垂直于位错线,在运动

过程中是可变的,晶体作相对滑动的方向应是什么

方向?

答案

❖ 7.位错线上的割阶一般如何形成?

答案

❖ 8.界面能最低的界面是什么界面?

答案

❖ 9. “小角度晶界都是由刃型位错排成墙而构成的”这

种说法对吗?

答案

返回

7

三、综合题

❖ 1. 作图表示立方晶体的(123)(0 -1 -2) (421)晶面及[-102][-211][346]晶向。 答案

❖ 9. 在Fe中形成1mol 空位的能量为104. 67kJ,

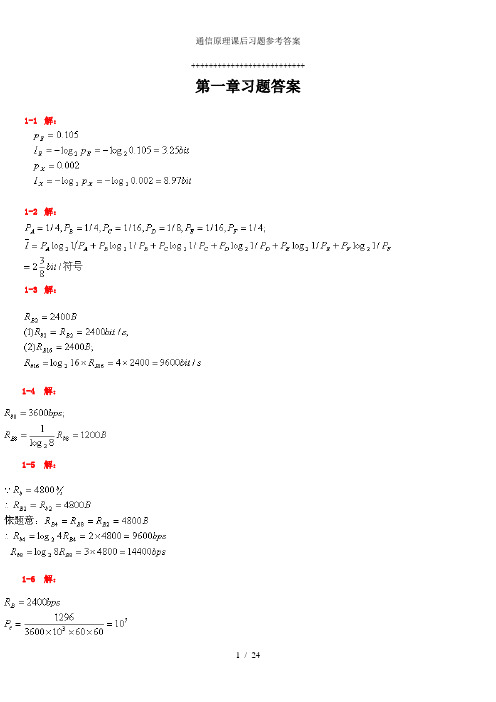

通信原理课后习题参考答案

++++++++++++++++++++++++++第一章习题答案1-1解:1-2解:1-3解:1-4 解:1-5 解:1-6 解:1-7 解:1-8 解:第二章习题答案2-1 解:群延迟特性曲线略2-2 解:2-3 解:2-4 解:二径传播时选择性衰落特性图略。

2-5 解:2-6 解:2-7 解:2-8 解:第三章习题答案3-4 解:3-5 解:3-6 解:3-7 解:3-8 解:3-9 解:3-10 解:3-11 解:第四章习题答案4-2 解:4-3 解:4-4 解:4-6 解:4-8 解:4-9 解:4-10 解:4-11 解:4-12 解:4-13 解:4-15 解:4-16 解:4-17 解:第五章习题答案5-1 解:,,,(1)波形(2)5-2 解:,,(1)(2)相干接收时5-3 解:,,(1)相干解调时(2)非相干解调时5-4 解:,,,(1)最佳门限:而:所以:(2)包检:5-5 解:系统,,5-6 解:(1)信号与信号的区别与联系:一路可视为两路(2)解调系统与解调系统的区别与联系:一路信号的解调,可利用分路为两路信号,而后可采用解调信号的相干或包检法解调,再进行比较判决。

前提:信号可分路为两路信号谱不重叠。

5-7 解:系统,,,(1)(2)5-8 解:系统,,,,(1)(2)所以,相干解调时:非相干解调时:5-9 解:5-10 解:(1)信号时1 0 0 1 0(2)1 0 1 0 0,5-12 解:时:相干解调码变换:差分相干解调:,,(1):a:相干解调时解得:b:非相干解调时解得:(2):(同上)a:相干解调时,b:非相干解调时,(3)相干解调时即在保证同等误码率条件下,所需输入信号功率为时得1/4,即(4)a:差分相干解调时即在保证同等误码率条件下,所需输入信号功率为时得1/4,即b:相干解调的码变换后解得:5-16 解:(A方式)0 1 1 0 0 1 1 1 0 1 0 0 ,5-17 解:(1)时所以(2)时所以5-18 解:5-19 解:,::一个码元持续时间,含:个周波个周波。

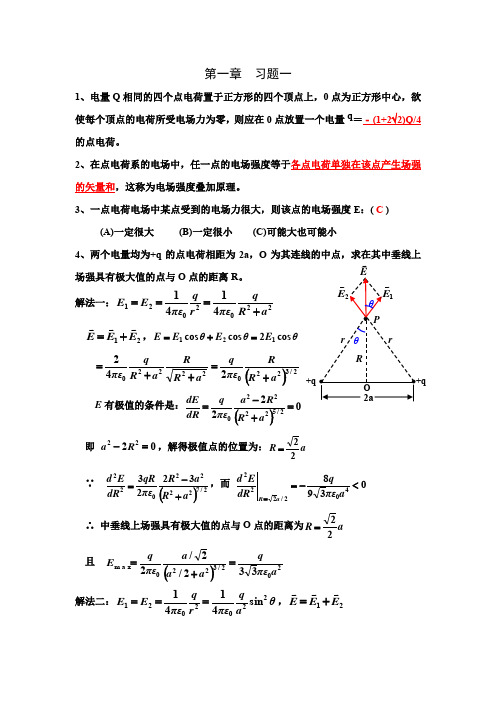

电磁学习题答案1-3章

第一章 习题一1、电量Q 相同的四个点电荷置于正方形的四个顶点上,0点为正方形中心,欲使每个顶点的电荷所受电场力为零,则应在0点放置一个电量q =-(1+2√2)Q/4 的点电荷。

2、在点电荷系的电场中,任一点的电场强度等于各点电荷单独在该点产生场强的矢量和,这称为电场强度叠加原理。

3、一点电荷电场中某点受到的电场力很大,则该点的电场强度E :( C )(A)一定很大 (B)一定很小 (C)可能大也可能小4、两个电量均为+q 的点电荷相距为2a ,O 为其连线的中点,求在其中垂线上场强具有极大值的点与O 点的距离R 。

解法一:22020214141aR qπεr q πεE E +=== 21E E E+=,θE θE θE E cos 2cos cos 121=+=2222042a R R a R q πε++=()2/32202a R R πεq +=E 有极值的条件是:()0222/522220=+-=a R R a πεq dR dE 即 0222=-R a ,解得极值点的位置为:a R 22=∵ ()2/722220223223a R a R πεqR dR E d +-=,而 0398402/222<-==aπεqdR E d a R ∴ 中垂线上场强具有极大值的点与O 点的距离为a R 22= 且 ()202/3220m a x 332/2/2aπεq a a a πεq E =+=解法二:θaq πεr q πεE E 2202021sin 4141===,21E E E +=+qθE θE θE E cos 2cos cos 121=+=θθaq πεcos sin 21220=)cos (cos 21320θθaq πε-=E 有极值的条件是:0)sin 3sin 2(2320=-=θθaπεq θd dE E 有极值时的θ满足:31cos 32sin 1cos 0sin 2211====θ,θ;θ,θ )cos 7cos 9(2)cos sin 9cos 2(232022022θθaπεq θθθa πεq θd E d -=-= 0)cos 7cos 9(22011320221>=-==aπεq θθa πεq θd E d θθ 032)cos 7cos 9(22022320222<-=-==aπεq θθa πεq θd E d θθ 可见 θ = θ2时,E 有极大值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

计算机体系结构习题及答案第一章基础知识1.名词解释翻译解释模拟仿真透明性程序访问局部性[答案]略翻译:先用转换程序将高一级机器上的程序整个地变换成为低一级机器上可运行的等效程序,然后再在低一级机器级上去实现的技术。

解释:在低一级机器上用它的一串语句或指令来仿真高一级机器级上的一条语句或指令的功能,通过对高一级机器语言程序中的每条语句或指令逐条解释来实现的技术。

模拟:指用软件的方法在一台计算机(宿主机A)上,实现另一台计算机(虚拟机B)的指令系统。

仿真:用微程序的方法在一台计算机(宿主机A)上实现另一台计算机(目标机B)的指令系统。

透明性:一种本来是存在的事务或属性, 但从某种角度看却好像不存在。

程序访问的局部性原理:是指程序执行过程中,呈现出频繁重新使用那些最近已被使用过的数据和指令的规律。

程序访问的局部性包括时间局部性和空间局部性。

2. 一个经解释实现的计算机可以按功能划分为四级. 每一级为了执行一条指令需要下一级的N条指令. 若执行第一级的一条指令需要的时间为K ns, 那么执行第二、三、四级的一条指令各需要多少时间?[答案] NK ns; N2K ns; N3K ns3. 计算机系统按功能划分层次结构的好处主要体现在哪些方面?[答案] (1) 有利于理解软件, 硬件和固件在系统中的地位和作用;(2) 有利于理解各种语言的实质和实现途径;(3) 有利于推动计算机系统结构的发展;(4) 有利于理解计算机系统结构的定义.4. 什么是透明性? 对计算机系统结构, 下列哪些是透明的? 哪些是不透明的?1)存储器的模m交叉存取; 2)浮点数据表示; 3) I/O系统是采用通道方式还是I/O处理机方式; 4) 阵列运算部件; 5) 数据总线宽度; 6) 通道是采用结合型的还是独立型的; 7) 访问方式保护; 8) 程序性中断; 9) 串行、重叠还是流水控制方式; 10) 堆栈指令; 11) 存储器的最小编址单位; 12) Cache存储器.[答案] 一种本来是存在的事务或属性, 但从某种角度看却好像不存在, 称为透明性.对计算机系统结构来说透明的是: 1), 4), 5), 6), 9), 12)对计算机系统结构来说不透明的是:2), 3), 7), 8), 10), 11)5. 什么是计算机体系结构? 什么是计算机组成? 什么是计算机实现? 并说明三者的关系和相互影响?[答案] 计算机系统结构是计算机系统的软, 硬件分界面, 是机器语言程序员或是编译程序员所需了解的计算机属性;计算机组成是计算机系统结构的逻辑事项;计算机实现是计算机组成的物理实现.三者的关系和互相影响为:(1) 具有相同系统结构的计算机可以采用不同的组成; (2) 一种计算机组成可以采用多种不同的计算机实现;(3) 计算机组成、计算机实现对计算机系统结构有着很大的影响;(4) 计算机系统结构的设计不应限制计算机组成和实现技术,应能用于高档机,也可用于低挡机;(5) 在不同时期, 计算机系统结构,、组成和实现所包含的内容会有所变化,三者之间的界线常常很模糊.6. 从机器(汇编)语言程序员角度看, 以下哪些是透明的? 1) 指令地址存储器; 2) 指令缓冲器; 3) 时标发生器; 4) 条件码寄存器; 5) 乘法器; 6) 主存地址寄存器; 7) 磁盘外设; 8) 先行进位链; 10) 通用寄存器; 11) 中断字寄存器. [答案] 对机器(汇编)语言程序员来说透明的有: 2), 3), 5), 6), 8), 9) 对机器(汇编)语言程序员来说不透明的有: 1), 4), 7), 10), 11)7. 假设在一台40 MHz 处理机上运行200 000条指令的目标代码, 程序主要由四种类型的指令所组成. 根据程序跟踪实验结果, 各类指令的混合比和每类指令的CPI 值如表1.9所示.表1.9 各类指令的指令混合比及每类指令的CPI 值指令类型 指令混合比CPI算术和逻辑60% 1 高速缓存命中的加载/存储18% 2 转移12% 3 高速缓存缺失的存储器访问10% 4(1) 试计算在单处理机上执行上述该程序时的平均CPI;(2) 根据(1)所得到的CPI, 计算相应的MIPS 速率及程序的执行时间. [答案] (1) 2.24 CPI (2) 17.86 MPIS; 0.0112 s8. 某工作站采用时钟频率为15 MHz 、处理速率为10 MIPS 的处理机来执行一个程序,假定每次存储器存取为1周期延迟, 试问:(1) 此计算机的有效CPI 是多少?(2) 假定将处理机的时钟频率提高到30 MHz, 但存储器子系统速率不变, 这样, 每次存储器存取需要两个时钟周期. 如果30%的指令每条只需要一次存储存取, 而另外5%的指令每条需要两次存储存取, 还假定已知混合程序的指令数不变, 并与原工作站兼容, 试求改进后的处理机性能(计算MIPS ).[答案] (1) 5.1=10×1010×15=10×=666MIPS f CPI ;(2) 改造以后处理机的CPI 发生变化,30%的指令每条只需要一次存储存取, 由于时钟周期缩短,这类以前需要1个时钟周期用于存储,而现在需要增加1个时钟周期用于存储。

同理,5%的指令每条需要两次存储存取, 这类以前需要2个时钟周期用于存储,而现在需要增加2*2个时钟周期用于存储。

而其他指令不需访存,所以所需时钟周期不变,改造后 CPI 为:9.1=1.0+3.0+5.1=)24(×%5+)12(×%30+=OLD NEW CPI CPI789.15≈10×9.110×30=10×=666NEW NEW NEWCPI f MIPS 9.什么是并行性?它分为哪两种类型?开发计算机系统并行性的主要技术途径有哪三个?沿这些途径分别发展出什么类型的计算机?[答案] 并行性指同一时刻或同一时间间隔内发生两件或两件以上事件。

并行性分为同时性和并发性。

同时性指的是两个或多个事件发生在同一时刻。

并发性则是指两个或多个事件发生在同一段时间间隔内。

在计算机系统中,提高并行性的技术途径可以归纳为以下三种:1)时间重叠:在并行性概念中引入时间因素,让多个处理过程在时间上相互错开,重叠的使用同一套部件的各个部分,加快硬件使用的周转来提高处理速度。

典型的例子有流水技术。

2)资源重复:在并行性概念中引入空间因素,通过重复设置资源,尤其是硬件资源,来提高系统的性能。

典型的例子有双工系统、相联处理机和阵列处理机等。

3)资源共享:主要是采用软件手段让多个任务按一定顺序轮流使用一套资源,通过提高资源利用率来提高系统的性能和效率。

典型的例子有多道程序分时系统、计算机网络和分布处理系统等。

10.实现软件移植的途径有哪些? [答案]略11.什么是Flynn 分类法,按照Flynn 分类法可将计算机系统分为哪几类? [答案]略第二章 指令系统1. 名词解释数据类型、数据表示、规格化浮点数、Huffman 编码、扩展编码、RISC [答案]略2. 某模型机有8条指令I 1~I 8, 它们的使用频度分别为0.3, 0.3, 0.2, 0.1, 0.05, 0.02, 0.02, 0.01.(1) 试分别用Huffman 编码和平均码长最短的等长扩展码(限定为两种码长)对其操作码进行编码.(2) 分别计算Huffman 编码和等长扩展码编码的平均长度.[答案] (1) 操作码的Huffman 编码和2-4等长扩展码编码如下表1所示.表1 操作码的Huffman 编码和2-4等长扩展码编码Huffman 编码法 2-4等长扩展码编码法指 令指令使用 频度P iHuffman 编码操作码长度l i 2-4等长扩展码操作码长度l iI 1 0.3 00 2 00 2 I 2 0.3 01 2 01 2 I 3 0.2 10 2 1000 4 I 4 0.1 110 3 1001 4 I 5 0.05 1110 4 1010 4 I 6 0.02 11110 5 1011 4 I 7 0.02 111110 6 1100 4 I 8 0.01 111111 6 11014(2) Huffman 编码的平均长度为2.38位; 等长扩展码编码的平均码长为2.8位.3. 某模型机有10条指令I 1~I 10, 它们的使用频度分别为0.3, 0.24, 0.16, 0.12, 0.07, 0.04, 0.03,0.02, 0.01, 0.01.(1) 计算机采用等长操作码表示时的信息冗余量.(2) 要求操作码平均码长最短, 试设计操作码的编码, 并计算所设计操作码的平均长度. (3) 设计2-5扩展操作码编码,并计算平均码长.(4) 设计2-4(2/8)等长扩展码编码,并计算平均码长. [答案] (1) 采用等长操作码表示时的信息冗余量为33.5%. (2) 操作码的Huffman 编码如表2所示, 此种编码的平均长度为2.7位.(3) 操作码的2-5扩展码编码如表2所示, 此种编码的平均长度为2.9位.(4) 操作码的2-4(2/8)等长扩展码编码如表2所示, 此种编码的平均长度为2.92位.表2 操作码的Huffman 编码, 2-5扩展码和2-4等长扩展码Huffman 编码法 2-5扩展码编码法 2-4等长扩展码编码法指令指令使用 频度P iHuffman 编码操作码长度l i2-5扩展码操作码 长度l i2-4等长 扩展码操作码 长度l iI 1 0.3 00 2 00 2 00 2 I 2 0.24 10 2 01 2 01 2 I 3 0.16 010 3 10 2 1000 4 I 4 0.12 011 3 11000 5 1001 4 I 5 0.07 110 3 11001 5 1010 4 I 6 0.04 111005 110105 10114I7 0.03 11101 5 11011 5 1100 4I8 0.02 11110 5 11100 5 1101 4I9 0.01 111110 6 11101 5 1110 4I10 0.01 111111 6 11110 5 1111 44. 何谓指令格式的优化? 操作码和地址码的优化一般采用哪些方法?[答案] 指令格式的优化是指通过采用多种不同的寻址方式, 地址制, 地址形式和地址码长度以及多种指令字长, 并将它们与可变长操作码的优化表示相结合, 就可以构成冗余度尽可能少的指令字.操作码的优化采用扩展操作码编码法.地址码优化有以下四种方法:(1)在指令中采用不同的寻址方式;(2)在指令中采用多地址制;(3)同一种地址制还可以采用多种地址形式和长度, 也可以考虑利用空白处来存放直接操作数或常数等;(4)在以上措施的基础上, 还可以进一步考虑采用多种指令字长度的指令.5. 若某机设计有如下指令格式的指令:三地址指令12种, 一地址指令254种, 设计指令的长度为16位, 每个地址码字段的位数均为4位. 若操作码的编码采用扩展操作码, 问二地址指令最多可以设计多少种?[答案] 二地址指令最多可以设计48种.6. 一台模型机共有九条指令I1~I9, 各指令的使用频度分别为0.3, 0.2, 0.2, 0.1, 0.08, 0.06, 0.03,0.02, 0.01. 该模型机有8位和16位两种指令字长. 8位字长指令为寄存器--寄存器(R--R)二地址类型, 16位字长指令为寄存器--存储器(R--M)二地址变址寻址类型.(1)试设计有两种码长的扩展操作码, 使其平均码长最短, 并计算此种编码的平均码长.(2)在(1)的基础上, 该机允许使用多少个可编址的通用寄存器?(3)若采用通用寄存器作为变址寄存器, 试设计该机的两种指令格式, 并标出各字段的位数.(4)计算变址寻址的偏移地址范围.[答案] (1) 操作码的2-5扩展码编码如表3所示, 此种编码的平均长度位2.9位.表3 操作码的2-5扩展码编码指令指令使用频度P i 2-5扩展码操作码长度l iI1 0.3 00 2 I2 0.2 01 2 I3 0.2 10 2 I4 0.1 11000 5 I5 0.08 11001 5 I6 0.06 11010 5 I7 0.03 11011 5 I8 0.02 11100 5 I9 0.01 11101 5 在(1)的基础上, 该机允许使用8个可编址的通用寄存器.(2)(3)该机的两种指令格式及各字段的位数如下:R-R型: 操作码OP (2位) | 源寄存器R S (3位) | 目的寄存器R d (3位)R-M型: 操作码OP (5位) | 源寄存器R S (3位) | 变址寄存器R X (3位) | 偏移地址 (5位)变址寻址的偏移地址范围为-16~+15.(4)7. 简述CISC的特点.[答案] CISC的特点如下:(1)庞大的指令系统;(2)采用了可变长度的指令格式;(3)指令使用的寻址方式繁多;(4)CISC指令系统中包括一些用于特殊用途的指令, 各种指令的使用频度相当悬殊.8. 从指令格式, 寻址方式以及平均CPI三个方面, 比较经典CISC和纯RISC体系结构. [答案] 略9.简述RISC设计的一般原则。