图文详解stm32时钟树

stm32单片机时钟

stm32单⽚机时钟stm32 单⽚机时钟学习以及分析1 引⾔:单⽚机(Microcontrollers),采⽤超⼤规模集成电路技术把具有数据处理能⼒的中央处理器CPU、随机存储器RAM、只读存储器ROM、多种I/O⼝和中断系统、定时器/计数器等功能(可能还包括显⽰驱动电路、脉宽调制电路、模拟多路转换器、A/D转换器等电路)集成到⼀块硅⽚上构成的⼀个⼩⽽完善的微型计算机系统,在⼯业控制领域⼴泛应⽤。

单⽚机时钟可以说如同⼈的⼼脏那样重要,我们在⼼脏的搏动下进⾏⾃⼰的⽣命活动,同样的单⽚机在时钟下进⾏⾃⼰的控制活动。

2 时钟的分类:单⽚机的时钟分为内部时钟与外部时钟:⼀般⽽⾔,内部时钟集成在芯⽚内部(RC振荡电路),其精度⽐较低;外部时钟,顾名思义,存在于芯⽚外部(晶体或陶瓷谐振器),可以为系统提供精确的时钟。

晶振是给单⽚机提供⼯作信号脉冲的,如图所⽰的为外部晶振,频率为4MHz,我们常⽤的晶振频率为12MHz,单⽚机⼯作时,是⼀条⼀条地从RoM中取指令,然后⼀步⼀步地执⾏。

单⽚机访问⼀次存储器的时间,称之为⼀个机器周期,这是⼀个时间基准。

—个机器周期包括12个时钟周期。

如果⼀个单⽚机选择了12MHz晶振,它的时钟周期是1/12us,它的⼀个机器周期是12×(1/12)us,也就是1us。

有些晶振的频率并数是整数,如:11.0592MHz的晶振。

单⽚机在进⾏串⾏通信时,常⽤的波特率为1200,2400,4800,9600,115200等,为了适应单⽚机的串⼝通讯波特率的计算⽽来的。

⽤11.0592MHz晶振经过相应的分频或者倍频后刚好能够得出⼀个整数的波特率,这样在上位机和下位机的同步⽅⾯⽐较⽅便。

3 stm32的时钟来源这⾥以stm32f1系列的芯⽚为例。

由上⾯可知,系统的时钟来源有内部时钟与外部时钟,详细的来说stm32f1有五个时钟源:HSI(⾼速内部时钟)HSE(⾼速外部时钟)LSI(低速内部时钟)LSE(低速外部时钟)PLL(锁相环倍频输出)每⼀个时钟都可以独⽴的开启与关闭。

Finder自学stm32笔记之电源时钟

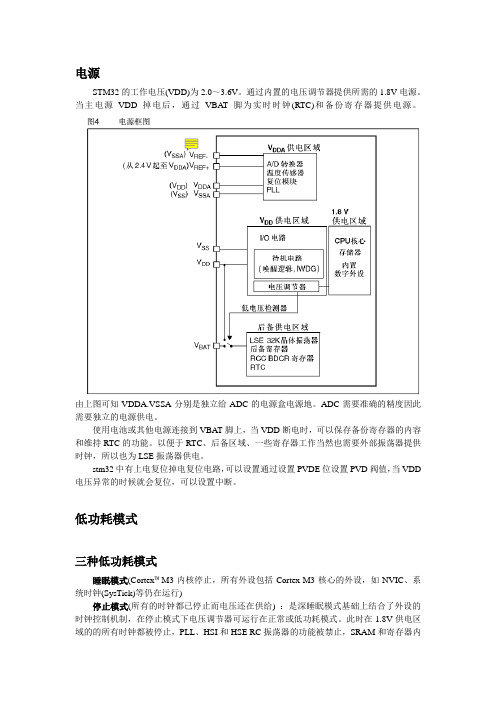

电源STM32的工作电压(VDD)为2.0~3.6V。

通过内置的电压调节器提供所需的1.8V电源。

当主电源VDD掉电后,通过VBA T脚为实时时钟(RTC)和备份寄存器提供电源。

由上图可知VDDA.VSSA分别是独立给ADC的电源盒电源地。

ADC需要准确的精度因此需要独立的电源供电。

使用电池或其他电源连接到VBAT脚上,当VDD断电时,可以保存备份寄存器的内容和维持RTC的功能。

以便于RTC、后备区域、一些寄存器工作当然也需要外部振荡器提供时钟,所以也为LSE振荡器供电。

stm32中有上电复位掉电复位电路,可以设置通过设置PVDE位设置PVD阀值,当VDD 电压异常的时候就会复位,可以设置中断。

低功耗模式三种低功耗模式睡眠模式(Cortex™-M3内核停止,所有外设包括Cortex-M3核心的外设,如NVIC、系统时钟(SysTick)等仍在运行)停止模式(所有的时钟都已停止而电压还在供给) :是深睡眠模式基础上结合了外设的时钟控制机制,在停止模式下电压调节器可运行在正常或低功耗模式。

此时在1.8V供电区域的的所有时钟都被停止,PLL、HSI和HSE RC振荡器的功能被禁止,SRAM和寄存器内容被保留下来。

在停止模式下,所有的I/O引脚都保持它们在运行模式时的状态。

待机模式(1.8V电源关闭):待机模式可实现系统的最低功耗。

该模式是在Cortex-M3深睡眠模式时关闭电压调节器。

整个1.8V供电区域被断电。

PLL、HSI和HSE振荡器也被断电。

SRAM和寄存器内容丢失。

只有备份的寄存器和待机电路维持供电。

前面是三者的详细介绍,初一看看不出有什么区别,我当时都看的晕呼呼地,做笔记时候才发现他们真正的不同。

现在讲解一下。

睡眠模式只是关掉了CM3的内核,外设都在运行包过内部外部时钟、IO口、中断NVIC 等等。

停止模式是进一步的睡眠模式它是关掉了所有的外设时钟,但是仍旧在供电。

待机模式是最低功耗的模式,它连时钟供电全部禁止除了备份的寄存器和待机电路维持供电。

STM32F4时钟树概述

STM32F4时钟树概述STM32F4 相对于 STM32F1 来说,时钟部分复杂了很多, STM32F4 的时钟配置,我们提供两个函数: Sys_Clock_Set 和Stm32_Clock_Init。

其中 Sys_Clock_Set 是核⼼的系统时钟配置函数,由 Stm32_Clock_Init 调⽤,实现对系统时钟的配置。

外部程序,⼀般调⽤ Stm32_Clock_Init函数来配置时钟。

sys⽂件夹中在 STM32F4 中,有 5 个最重要的时钟源,为 HSI、 HSE、 LSI、 LSE、 PLL。

其中 PLL 实际是分为两个时钟源,分别为主 PLL 和专⽤PLL。

从时钟频率来分可以分为⾼速时钟源和低速时钟源,在这 5 个中 HSI, HSE 以及 PLL 是⾼速时钟, LSI 和 LSE 是低速时钟。

从来源可分为外部时钟源和内部时钟源,外部时钟源就是从外部通过接晶振的⽅式获取时钟源,其中 HSE 和LSE 是外部时钟源,其他的是内部时钟源。

①、 LSI 是低速内部时钟, RC 振荡器,频率为 32kHz 左右。

供独⽴看门狗和⾃动唤醒单元使⽤。

②、 LSE 是低速外部时钟,接频率为 32.768kHz 的⽯英晶体。

这个主要是 RTC 的时钟源。

③、 HSE 是⾼速外部时钟,可接⽯英/陶瓷谐振器,或者接外部时钟源,频率范围为 4MHz~26MHz。

我们的开发板接的是 8M 的晶振。

HSE 也可以直接做为系统时钟或者 PLL 输⼊。

④、 HSI 是⾼速内部时钟, RC 振荡器,频率为 16MHz。

可以直接作为系统时钟或者⽤作 PLL输⼊。

⑤、 PLL 为锁相环倍频输出。

STM32F4 有两个 PLL:1)主 PLL(PLL)由 HSE 或者 HSI 提供时钟信号,并具有两个不同的输出时钟。

第⼀个输出 PLLP ⽤于⽣成⾼速的系统时钟(最⾼ 168MHz)第⼆个输出 PLLQ ⽤于⽣成 USB OTG FS 的时钟(48MHz),随机数发⽣器的时钟和 SDIO时钟。

STM32实验手册

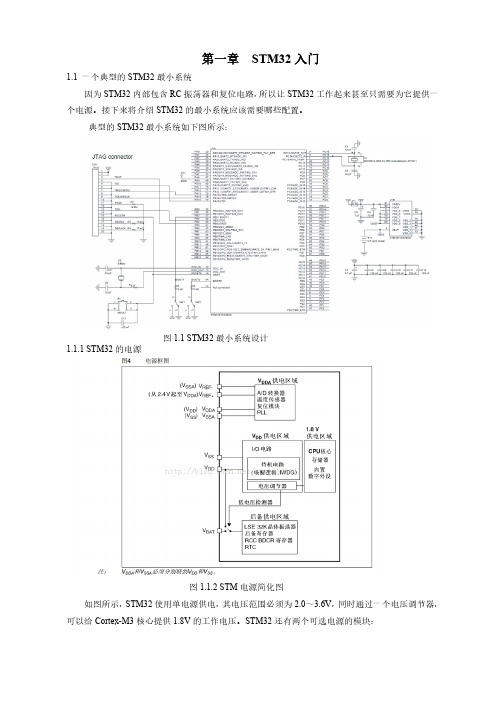

第一章STM32入门1.1 一个典型的STM32最小系统因为STM32内部包含RC振荡器和复位电路,所以让STM32工作起来甚至只需要为它提供一个电源。

接下来将介绍STM32的最小系统应该需要哪些配置。

典型的STM32最小系统如下图所示:图1.1 STM32最小系统设计1.1.1 STM32的电源图1.1.2 STM电源简化图如图所示,STM32使用单电源供电,其电压范围必须为2.0~3.6V,同时通过一个电压调节器,可以给Cortex-M3核心提供1.8V的工作电压。

STM32还有两个可选电源的模块:1.实时时钟和一小部分备份寄存器,它们可以在STM32进入深度节电模式时在备份电池的支持下保持数据不丢失。

但如果STM32最小系统没有使用备份电池,则VBAT引脚必须和VDD引脚相连接。

2.ADC模块,如果要启用ADC功能,则主电源VDD必须限制在2.4~3.6V。

在引脚数大于100的STM32版本里,ADC模块有额外有额外的参考电压引脚VREF+和VREF-,则VREF-引脚必须与VDDA相连,而VREF+可以接入2.4V~VDD。

1.1.2STM32的时钟系统图1.1.2 STM32时钟树STM32带有内部的RC振荡器,可以为内部PLL(锁相环)提供时钟,这样STM32依靠振荡器就可以在72MHZ的满速状态运行。

但是内部RC振荡器相比外部晶振相比外部晶振来说不够准确,同时也不够稳定,所以在条件允许的情况下,建议尽量使用外部时钟源。

1.高速外部振荡器如图所示,外部主时钟源主要作为Cortex-M3处理器和STM32外设的驱动时钟,一般称为高速外部振荡器(HSE OSC)。

2.低速外部振荡器STM32还可以使用第2个外部振荡器,一般称为低速外部振荡器(LSE OSC)。

一般用于驱动实时时钟(RTC)以及窗口看门狗。

像HSE一样,LSE也可以使用外部晶振或者用户自行供给。

LSE的典型频率为32.768KHZ3.时钟输出有一个GPIO引脚可以配置为STM32微控制器的时钟输出引脚(MCO),该引脚可以输出频率为内部时钟1/4的时钟脉冲。

基于STM32的嵌入式系统原理与设计第一章ppt课件

3

1.1 STM32性能和结构 1.1.1总体性能

以高密度的STM32F103VET6为例,能适合一般项目的 需要,价格在30元以下,避免由于FLASH和RAM太小 造成的瓶颈。 VET6的含义为:

P33图1-18.

35

1.SysTic定时器的位置和功能 2. SysTic定时器的4个寄存器 表1-12 表1-15 3. SysTic定时器编程(寄存器级别)。

P36代码1-10. 4. SysTic定时器编程(库函数级别)。

P36代码1-11. 库函数实现原理 P36代码1-12

36

STM32的常规定时器分为三类,包括 1.高级控制定时器TIM1和TIM8 2.通用定时器TIM2、TIM3、TIM4、TIM5 3.基本定时器TIM6、TIM7 三种定时器功能 P39表1-16

55

亮点嵌入式

56

+ 选择NOR这个块连接TFT控制器,采用8080接口(接 口详细信息见液晶驱动板设计部分)。8080接口需 16跟数据线,可以用FSMC_D[15..0]做数据线。

+ 写信号是FSMC_NWE,读信号是FSMC_NOE。 + 地址信号的设置 + 液晶控制器RS信号的设置

54

+ P48 1,3,5,7,8

V的含义为100pins,即100个管脚。 E表示512KB的FLASH。 T表示LQFP封装。 6 表示-40到85度的温度范围。

4

1.1 STM32性能和结构 1.1.2 系统结构分析

5

ห้องสมุดไป่ตู้

stm32的时钟配置(非常详细)

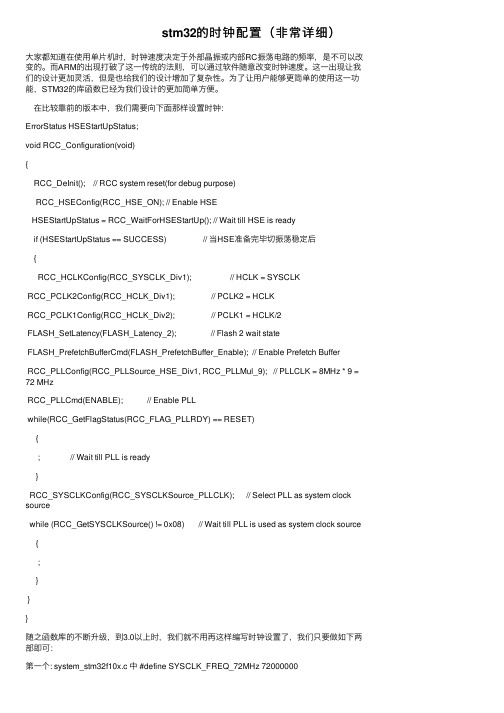

stm32的时钟配置(⾮常详细)⼤家都知道在使⽤单⽚机时,时钟速度决定于外部晶振或内部RC振荡电路的频率,是不可以改变的。

⽽ARM的出现打破了这⼀传统的法则,可以通过软件随意改变时钟速度。

这⼀出现让我们的设计更加灵活,但是也给我们的设计增加了复杂性。

为了让⽤户能够更简单的使⽤这⼀功能,STM32的库函数已经为我们设计的更加简单⽅便。

在⽐较靠前的版本中,我们需要向下⾯那样设置时钟:ErrorStatus HSEStartUpStatus;void RCC_Configuration(void){RCC_DeInit(); // RCC system reset(for debug purpose)RCC_HSEConfig(RCC_HSE_ON); // Enable HSEHSEStartUpStatus = RCC_WaitForHSEStartUp(); // Wait till HSE is readyif (HSEStartUpStatus == SUCCESS) // 当HSE准备完毕切振荡稳定后{RCC_HCLKConfig(RCC_SYSCLK_Div1); // HCLK = SYSCLKRCC_PCLK2Config(RCC_HCLK_Div1); // PCLK2 = HCLKRCC_PCLK1Config(RCC_HCLK_Div2); // PCLK1 = HCLK/2FLASH_SetLatency(FLASH_Latency_2); // Flash 2 wait stateFLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable); // Enable Prefetch BufferRCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9); // PLLCLK = 8MHz * 9 = 72 MHzRCC_PLLCmd(ENABLE); // Enable PLLwhile(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET){; // Wait till PLL is ready}RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK); // Select PLL as system clock sourcewhile (RCC_GetSYSCLKSource() != 0x08) // Wait till PLL is used as system clock source {;}}}随之函数库的不断升级,到3.0以上时,我们就不⽤再这样编写时钟设置了,我们只要做如下两部即可:第⼀个: system_stm32f10x.c 中 #define SYSCLK_FREQ_72MHz 72000000第⼆个:调⽤SystemInit()说明:在stm32固件库3.0中对时钟频率的选择进⾏了⼤⼤的简化,原先的⼀⼤堆操作都在后台进⾏。

stm32定时器时钟以及中间对齐模式

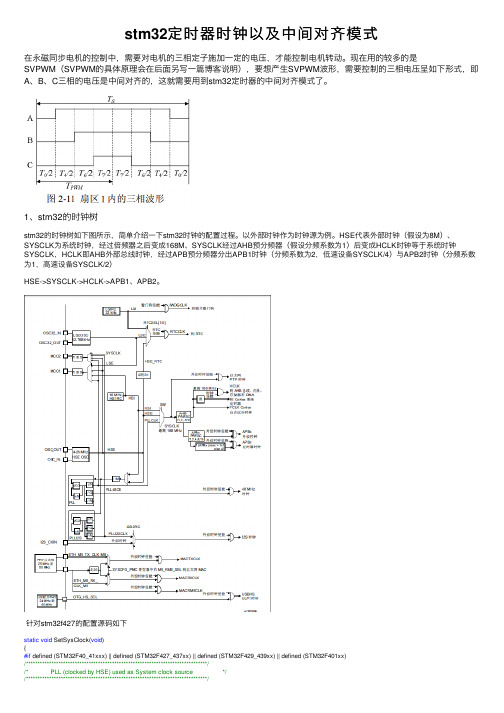

stm32定时器时钟以及中间对齐模式在永磁同步电机的控制中,需要对电机的三相定⼦施加⼀定的电压,才能控制电机转动。

现在⽤的较多的是SVPWM(SVPWM的具体原理会在后⾯另写⼀篇博客说明),要想产⽣SVPWM波形,需要控制的三相电压呈如下形式,即A、B、C三相的电压是中间对齐的,这就需要⽤到stm32定时器的中间对齐模式了。

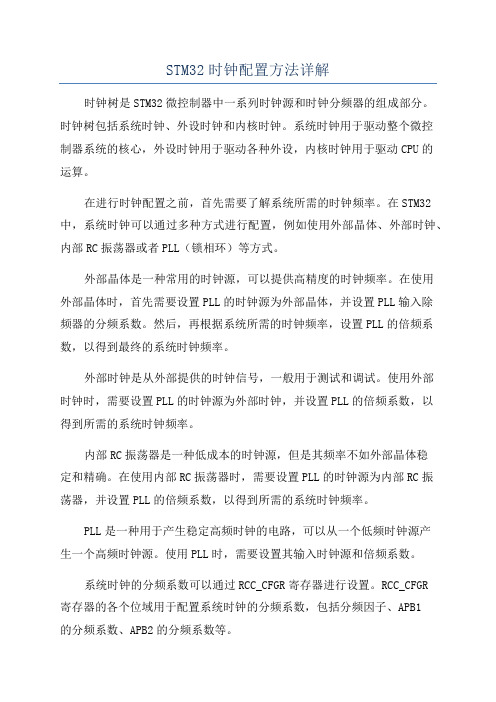

1、stm32的时钟树stm32的时钟树如下图所⽰,简单介绍⼀下stm32时钟的配置过程。

以外部时钟作为时钟源为例。

HSE代表外部时钟(假设为8M)、SYSCLK为系统时钟,经过倍频器之后变成168M、SYSCLK经过AHB预分频器(假设分频系数为1)后变成HCLK时钟等于系统时钟SYSCLK,HCLK即AHB外部总线时钟,经过APB预分频器分出APB1时钟(分频系数为2,低速设备SYSCLK/4)与APB2时钟(分频系数为1,⾼速设备SYSCLK/2)HSE->SYSCLK->HCLK->APB1、APB2。

针对stm32f427的配置源码如下static void SetSysClock(void){#if defined (STM32F40_41xxx) || defined (STM32F427_437xx) || defined (STM32F429_439xx) || defined (STM32F401xx)/******************************************************************************//* PLL (clocked by HSE) used as System clock source *//******************************************************************************/__IO uint32_t StartUpCounter = 0, HSEStatus = 0;/* Enable HSE */RCC->CR |= ((uint32_t)RCC_CR_HSEON);/* Wait till HSE is ready and if Time out is reached exit */do{HSEStatus = RCC->CR & RCC_CR_HSERDY;StartUpCounter++;} while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));if ((RCC->CR & RCC_CR_HSERDY) != RESET){HSEStatus = (uint32_t)0x01;}else{HSEStatus = (uint32_t)0x00;}if (HSEStatus == (uint32_t)0x01){/* Select regulator voltage output Scale 1 mode */RCC->APB1ENR |= RCC_APB1ENR_PWREN;PWR->CR |= PWR_CR_VOS;/* HCLK = SYSCLK / 1*/RCC->CFGR |= RCC_CFGR_HPRE_DIV1;//AHB时钟#if defined (STM32F40_41xxx) || defined (STM32F427_437xx) || defined (STM32F429_439xx)/* PCLK2 = HCLK / 2*/RCC->CFGR |= RCC_CFGR_PPRE2_DIV2;//APB2时钟/* PCLK1 = HCLK / 4*/RCC->CFGR |= RCC_CFGR_PPRE1_DIV4;//APB1时钟#endif /* STM32F40_41xxx || STM32F427_437x || STM32F429_439xx *//* Configure the main PLL */RCC->PLLCFGR = PLL_M | (PLL_N << 6) | (((PLL_P >> 1) -1) << 16) |(RCC_PLLCFGR_PLLSRC_HSE) | (PLL_Q << 24);/* Enable the main PLL */RCC->CR |= RCC_CR_PLLON;/* Wait till the main PLL is ready */while((RCC->CR & RCC_CR_PLLRDY) == 0){}#if defined (STM32F427_437xx) || defined (STM32F429_439xx)/* Enable the Over-drive to extend the clock frequency to 180 Mhz */PWR->CR |= PWR_CR_ODEN;while((PWR->CSR & PWR_CSR_ODRDY) == 0){}PWR->CR |= PWR_CR_ODSWEN;while((PWR->CSR & PWR_CSR_ODSWRDY) == 0){}/* Configure Flash prefetch, Instruction cache, Data cache and wait state */FLASH->ACR = FLASH_ACR_PRFTEN | FLASH_ACR_ICEN |FLASH_ACR_DCEN |FLASH_ACR_LATENCY_5WS; #endif /* STM32F427_437x || STM32F429_439xx *//* Select the main PLL as system clock source */RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));RCC->CFGR |= RCC_CFGR_SW_PLL;/* Wait till the main PLL is used as system clock source */while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS ) != RCC_CFGR_SWS_PLL);{}}else{ /* If HSE fails to start-up, the application will have wrong clockconfiguration. User can add here some code to deal with this error */}}2、stm32定时器的时钟stm32定时器分为⾼级定时器(TIM1与TIM8)、通⽤定时器(TIM2-TIM5、TIM9-TIM14)、基本定时器(TIM6、TIM7)。

stm32 25m晶振时钟树计算公式

为stm32 25m晶体振荡器设计时钟树就像为完美的系统时钟频率创造了一种神奇的食谱。

这就像混合和匹配不同的成分,以达到最迷人的结果。

想象一下用分时器,乘数器和源头来为您的系统时钟创造最终的药剂!首先以25MHz晶体振荡器作为主要成分。

将一些 PLLM 作为密制时钟分割器,添加一个 PLLN 的破折叠乘法因子,并在一些 PLLP 和PLLQ 中分别作为主除法因子和 USB OTG FS, SDIO 和随机数生成时钟分割因子。

在使用魔法公式: SystemClock = (InputFreency 、 PLLM)× PLLN 、 PLLP 、 PLLQ 进行混合和计算时,你会感觉自己是一个巫师,为你的系统时钟频率酝酿出最强大的咒语。

一旦你完成了,呜!你会为钟表树设计配制完美的配方以最迷人的方式让你的stm32复活当我们找出PLLM,PLLN,PLLP,PLLP,和PLLQ因素时,我们需要思考一下我们的系统时钟需要什么,以及我们的STM32微控制器能够处理什么。

我们选择PLLM系数,以确保我们的输入频率适合PLL。

我们选择PLLN系数来获得我们想要的乘法,我们主系统时钟的PLLP 系数,以及USB OTG FS,SDIO和RNG时钟的PLLQ系数。

一旦我们掌握了所有这些因素,我们就可以把它们插进一个公式中,来研究系统时钟频率。

在计算PLLM,PLLN,PLLP,以及PLLQ因子后,通过配置STM32微控制器的RCC(重置和时钟控制)登记器来实施时钟树设计。

这一过程需要精确设定RCC—PLLCFGR登记册中的PLLM、PLLN、PLLLP和PLLQ值,然后启用和配置RCC—CR登记册中的PLL。

通过坚持这一系统化程序,stm32 25m晶体振荡器可以被高效地利用,为微控制器产生必要的系统时钟频率。

这一方法符合现行意识形态框架和战略指令规定的硬件资源利用既定办法和政策。

STM32时钟详解

STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。该时钟源只能从PLL输出端获 取,可以选择为1.5分频或者1分频,也就是,当需要使用USB模块时,PLL必须使能,并且时钟频率配置为48MHz或72MHz。

在以上的时钟输出中,有很多是带使能控制的,例如AHB总线时钟、内核时钟、各种APB1外设、APB2外设等等。当需要 使用某模块时,记得一定要先使能对应的时钟。

需要注意的是定时器的倍频器,当APB的分频为1时,它的倍频值为1,否则它的倍频值就为2。

连接在APB1(低速外设)上的设备有:电源接口、备份接口、CAN、USB、I2C1、I2C2、UART2、UART3、SPI2、窗口看门 狗、Timer2、Timer3、Timer4。注意USB模块虽然需要一个单独的48MHz时钟信号,但它应该不是供USB模块工作的时钟,而 只是提供给串行接口引擎(SIE)使用的时钟。USB模块工作的时钟应该是由APB1提供的。

同时这种设定也是有规律可循的设定参数也是有顺序规范的这是应用中应当注意的例如pll的设定需要在使能之前一旦pll使能后参数不可更经过此番设置后由于我的电路板上是8mhz晶振所以系统时钟为72mhz高速总线和低速总线2都为72mhz低速总线1为36mhzadc时钟为12mhzusb时钟经过15分频设置就可以实现48mhz的数据传输

static void RCC_Config(void)

第2页

STM32时钟讲解.txt {

/* 这里是重置了RCC的设置,类似寄存器复位 */ RCC_DeInit();

STM32F427xx系列芯片系统时钟讲解

STM32F427xx系列芯片系统时钟讲解——写代码的Tobem 为了进行通用定时器的设置,有必要先了解STM32F427xx系列芯片的时钟系统。

为了实现低功耗(对于每个时钟源来说,在未使用时都可单独打开或者关闭,以降低功耗),STM32F427xx设计了功能完善但却有点复杂的时钟系统,见下图:图2 STM32F427xx系统时钟树从图中可以看出,STM32F427xx具有4个时钟源,分别为2个内部时钟源和2个外部时钟源,也可以分为2个高速时钟源和2个低速时钟源,具体为:1、HSE(高速外部时钟):以外部晶振作时钟源,晶振频率可取范围为4~26MHz,实际电路图中我们采用12MHz的晶振。

2、HSI(高速内部时钟):由内部RC振荡器产生,频率为16MHz。

其特点是起振快,在芯片刚上电的时候,就是使用高速内部时钟,但其精度不高,因此,上电之后我们再通过软件配置(SystemInit()函数),转而采用高速外部时钟信号。

3、LSE(低速外部时钟):以外部晶振作时钟源,主要提供给实时时钟模块(RTC),一般采用32.768KHz。

4、LSI(低速内部时钟):由内部RC振荡器产生,频率为32KHz,主要用于驱动独立看门狗,也可选择提供给RTC 用于停机/待机模式下的自动唤醒。

程序在执行主函数main()之前,要先进行堆栈指针SP、程序计数器PC的初始化、设置异常中断向量地址等工作,最后才进入到主函数main()中去执行,这其中包括系统时钟的配置(在startup_stm32f4xx.s启动文件中)。

系统时钟的配置由system_stm32f4xx.c文件中的SystemInit()函数完成,配置结果如下:图3 系统时钟配置情况从时钟树中可以看到,系统时钟SYSCLK是大部分器件的时钟来源,因此SYSCLK的配置就显得十分重要。

SYSCLK可以从三个时钟源中进行选择,分别为HSI、HSE和PLLCLK。

HSI 不稳定,而HSE速率太低(4~26MHz),为了使系统获得较快的运行速率和稳定性,我们选择PLLCLK来作为SYSCLK(见备注1),而PLLCLK又可以选择HSI或者HSE作为时钟源,我们选择HSE作为时钟源(见备注2)根据时钟树的走向,SYSCLK(即PLLCLK)计算过程为:PLL_VCO = (HSE_VALUE / PLL_M) * PLL_NSYSCLK = PLL_VCO / PLL_P而宏定义有#if !defined (HSE_VALUE)#define HSE_VALUE ((uint32_t)12000000) /*!< Value of the External oscillator in Hz */#endif /* HSE_VALUE */#define PLL_M 12#define PLL_Q 7#if defined (STM32F427_437xx) || defined (STM32F429_439xx)#define PLL_N 360#define PLL_P 2故SYSCLK最终为180MHz。

STM32F103时钟部分归纳

学习一款单片机,首先要了解的是它的时钟部分,在网上找到一些stm32F103时钟部分的资料,归纳总结一下。

时钟模块框图如下:仔细看上面这个框图,就可以对F103的时钟有一个清晰的认识了。

三种不同的时钟源可用作系统时钟(SYSCLOCK):HSI振荡器时钟(由芯片内部RC振荡器提供)HSE振荡器时钟(由芯片外部晶体振荡器提供)PLL时钟(通过倍频HIS或HSE振荡器倍频得到)另外还有两个时钟源:LSI内部40kHz低速RC振荡器时钟,用于驱动独立看门狗或选择驱动RTCLSE外部32.768kHz低速外部输入时钟,用于驱动RTC1.当HSI被用于作为PLL时钟的输入时,系统时钟能得到的最大频率是64MHz。

2.用户可通过多个预分频器分别配置AHB、高速APB(APB2)和低速APB(APB1)域的频率。

AHB和APB2域的最大频率是72MHz。

APB1域的最大允许频率是36MHz。

SDIO接口的时钟频率固定为HCLK/2。

3. RCC通过AHB时钟(HCLK)8分频后作为Cortex系统定时器(SysTick)的外部时钟。

通过对SysTick控制与状态寄存器的设置,可选择上述时钟或Cortex(HCLK)时钟作为SysTick时钟。

ADC时钟由高速APB2时钟经2、4、6或8分频后获得。

定时器时钟频率由APB1(PCLK1)时钟获得,分配由硬件按以下2种情况自动设置:a. 如果相应的APB预分频系数是1,定时器的时钟频率与所在APB总线频率一致。

b. 否则,定时器的时钟频率被设为与其相连的APB总线频率的2倍。

4. FCLK是Cortex-M3的自由运行时钟。

详情见ARM的Cortex-M3技术参考手册。

关于HSE、HIS、PLL、LSE、LSI时钟特性及校准直接参考STM32相关Datasheet。

系统时钟配置过程:配置过程主要对RCC_CR、RCC_CFGR、RCC_CIR这三个寄存器,进行读写访问,配置系统时钟完成后,进行对要使用的相应外设时钟进行使能和配置,不用的外设建议关闭相应的外设时钟(降低功耗)。

STM32F051x8数据手册 v1(中文版)

- 4 to 32 MHz 晶体振荡器 - 32 kHz RTC 用可的校准振荡器 - 内部 8 MHz RC 带 x6 锁相环倍频 - 内部 32 kHz RC 振荡器 ■ 日历型 RTC 集成闹钟可周期性自动从 Stop/ Standby 状态唤醒 ■ 复位和供电管理

2 器件总览.............................................................................8

3 功能概述............................................................................10 3.1 ARM® CortexTM-M0 内核结合嵌入式闪存和 SRAM................................. 10 3.2 存储器........................................................................ 10 3.3 循环冗余校验计算单元(CRC)..................................................10 3.4 直接存储器访问控制器(DMA).................................................. 11 3.5 向量嵌套中断控制器(NVIC)................................................... 11 3.6 扩展中断 / 事件控制器(EXTI)..................................................11 3.7 时钟和启动.................................................................... 12 3.8 引导模式...................................................................... 12 3.9 电源管理...................................................................... 12 3.9.1 供电方式............................................................... 12 3.9.2 电源监测............................................................... 12 3.9.3 稳压器................................................................. 13 3.10 低功耗模式.................................................................... 13 3.11 实时时钟(RTC)和后备寄存器.................................................. 14 3.12 定时器和看门狗................................................................ 15 3.12.1 高级控制定时器(TIM1)................................................. 15 3.12.2 通用定时器(TIM2. .3,TIM14 .. 17)....................................... 16 3.12.3 基本定时器 TIM6........................................................ 16 3.12.4 独立窗口看门狗 (IWWDG)................................................. 17 3.12.5 系统窗口看门狗(WWDG)............................................... 17 3.12.6 SysTick 定时器......................................................... 17 3.13 内部集成电路接口(I2C)....................................................... 17 3.14 通用同步 / 异步收发器(USART)............................................... 18 3.15 串行外设接口(SPI)/ 集成声音接口(I2S)....................................... 19 3.16 高清晰度多媒体接口(HDMI) - 消费电子控制(CEC).............................20 3.17 通用输入 / 输出端口(GPIO)...................................................20 3.18 触摸传感控制器 (TSC).......................................................... 20

STM32F103ZET6时钟

STM32F103ZET6时钟1、STM32F103ZET6时钟说明 STM32F103ZET6的时钟树图如下所⽰: STM32F103ZET6有很多个时钟源,分别有: HSE:⾼速外部时钟信号。

HSI:⾼速内部部时钟信号。

LSI:低速内部时钟信号。

LSE:低速外部时钟信号。

HSI和LSI是芯⽚内置的时钟源,它们的频率⼤⼩是固定的,HSI是8MHZ,LSI是⼤约40KHZ。

时钟树中的序号1是⾼速外部时钟信号HSE: HSE是由有源晶振或⽆源晶振通过OSC_OUT和OSC_IN脚提供的,从图⽚中可以看到,HSE频率从4MHZ到16MHZ不等。

当使⽤有源晶振时,时钟从OSC_IN引脚进⼊,OSC_OUT引脚悬空;当使⽤⽆源晶振时,时钟从OSC_IN和OSC_OUT进⼊,并且要配谐振电容。

HSE最常使⽤的就是8MHZ的⽆源晶振。

时钟树中的序号D是外部低速时钟LSE: LSE是由有源晶振或⽆源晶振通过OSC32_OUT和OSC32_IN脚提供的。

LSE⼀般使⽤的是32.768KHZ的⽆源晶振。

时钟树中的序号2是选择PLL(倍频后的时钟)的时钟源: 从图中可以看出,PLL时钟的来源可以是HSE或HSI/2,通过PLLSRC(CFGR寄存器的bit16)来选择使⽤哪⼀个时钟源。

HSI是8MHZ的内部⾼速时钟信号,HSI会根据温度和环境的情况频率会有漂移,⼀般不作为PLL的时钟来源。

⼀般使⽤HSE作为PLL的时钟源。

时钟树中的序号3是设置PLL的倍频因⼦: 可以对PLL的时钟来源进⾏倍频,然后得到PLLCLK时钟源。

倍频因⼦可以通过时钟配置寄存器CFGR的bit21~bit18:PLLMUL[3:0]来配置,分别可配置成2、3、4、5、6、7、8、9、10、11、12、13、14、15、16倍频。

举个例⼦来说,如果选择HSE作为PLL的时钟源,⽽且HSE=8MHZ,且将PLL的倍频因⼦设置为9倍频,那么PLLCLK=9*8MHZ = 72MZH。

零死角玩转stm32-初级篇6、Systick(操作系统的心脏)

0、友情提示《零死角玩转STM32》系列教程由初级篇、中级篇、高级篇、系统篇、四个部分组成,根据野火STM32开发板旧版教程升级而来,且经过重新深入编写,重新排版,更适合初学者,步步为营,从入门到精通,从裸奔到系统,让您零死角玩转STM32。

M3的世界,与野火同行,乐意惬无边。

另外,野火团队历时一年精心打造的《STM32库开发实战指南》将于今年10月份由机械工业出版社出版,该书的排版更适于纸质书本阅读以及更有利于查阅资料。

内容上会给你带来更多的惊喜。

是一本学习STM32必备的工具书。

敬请期待!6、Sysstick(系统滴答定时器)6.1 SysTick——操作系统的心跳SysTick定时器被捆绑在NVIC中,用于产生SysTick异常(异常号:15)。

在以前,操作系统和有所有使用了时基的系统,都必须要一个硬件定时器来产生需要的“滴答”中断,作为整个系统的时基。

滴答中断对操作系统尤其重要。

例如,操作系统可以为多个任务许以不同数目的时间片,确保没有一个任务能霸占系统;或者把每个定时器周期的某个时间范围赐予特定的任务等,还有操作系统提供的各种定时功能,都与这个滴答定时器有关。

因此,需要一个定时器来产生周期性的中断,而且最好还让用户程序不能随意访问它的寄存器,以维持操作系统“心跳”的节律。

Cortex-M3在内核部分包含了一个简单的定时器——SysTick timer。

因为所有的CM3芯片都带有这个定时器,软件在不同芯片生产厂商的 CM3器件间的移植工作就得以化简。

该定时器的时钟源可以是内部时钟(FCLK,CM3上的自由运行时钟),或者是外部时钟( CM3处理器上的STCLK信号)。

不过,STCLK的具体来源则由芯片设计者决定,因此不同产品之间的时钟频率可能会大不相同。

因此,需要阅读芯片的使用手册来确定选择什么作为时钟源。

在STM32中SysTick 以 HCLK(AHB时钟)或HCLK/8 作为运行时钟。

STM32时钟树

STM32的时钟树对于广大初次接触STM32的读者朋友(甚至是初次接触ARM器件的读者朋友)来说,在熟悉了开发环境的使用之后,往往“栽倒”在同一个问题上。

这问题有个关键字叫:时钟树。

众所周知,微控制器(处理器)的运行必须要依赖周期性的时钟脉冲来驱动——往往由一个外部晶体振荡器提供时钟输入为始,最终转换为多个外部设备的周期性运作为末,这种时钟“能量”扩散流动的路径,犹如大树的养分通过主干流向各个分支,因此常称之为“时钟树”。

在一些传统的低端8位单片机诸如51,AVR,PIC等单片机,其也具备自身的一个时钟树系统,但其中的绝大部分是不受用户控制的,亦即在单片机上电后,时钟树就固定在某种不可更改的状态(假设单片机处于正常工作的状态)。

比如51单片机使用典型的12MHz 晶振作为时钟源,则外设如IO口、定时器、串口等设备的驱动时钟速率便已经是固定的,用户无法将此时钟速率更改,除非更换晶振。

而STM32微控制器的时钟树则是可配置的,其时钟输入源与最终达到外设处的时钟速率不再有固定的关系,本文将来详细解析STM32微控制器的时钟树。

图1是STM32微控制器的时钟树,表1是图中各个标号所表示的部件。

表1 图1标号释义图1 STM32的时钟树在认识这颗时钟树之前,首先要明确“主干”和最终的“分支”。

假设使用外部8MHz 晶振作为STM32的时钟输入源(这也是最常见的一种做法),则这个8MHz便是“主干”,而“分支”很显然是最终的外部设备比如通用输入输出设备(GPIO)。

这样可以轻易找出第一条时钟的“脉络”:○3——○5——○7——○21——○8——○9——○11——○13对此条时钟路径做如下解析:●对于○3,首先是外部的3-25MHz(前文已假设为8MHz)输入;●对于○5,通过PLL选择位预先选择后续PLL分支的输入时钟(假设选择外部晶振);●对于○7,设置外部晶振的分频数(假设1分频);●对于○21,选择PLL倍频的时钟源(假设选择经过分频后的外部晶振时钟);●对于○8,设置PLL倍频数(假设9倍频);●对于○9,选择系统时钟源(假设选择经过PLL倍频所输出的时钟);●对于○11,设置AHB总线分频数(假设1分频);●对于○13,时钟到达AHB总线;在上一章节中所介绍的GPIO外设属于APB2设备,即GPIO的时钟来源于APB2总线,同样在图1中也可以寻获GPIO外设的时钟轨迹:○3——○5——○7——○21——○8——○9——○11——○15——○16●对于○3,首先是外部的3-25MHz(前文已假设为8MHz)输入;●对于○5,通过PLL选择位预先选择后续PLL分支的输入时钟(假设选择外部晶振);●对于○7,设置外部晶振的分频数(假设1分频);●对于○21,选择PLL倍频的时钟源(假设选择经过分频后的外部晶振时钟);●对于○8,设置PLL倍频数(假设9倍频);●对于○9,选择系统时钟源(假设选择经过PLL倍频所输出的时钟);●对于○11,设置AHB总线分频数(假设1分频);●对于○15,设置APB2总线分频数(假设1分频);●对于○16,时钟到达APB2总线;现在来计算一下GPIO设备的最大驱动时钟速率(各个条件已在上述要点中假设):1)由○3所知晶振输入为8MHz,由○5——○21知PLL的时钟源为经过分频后的外部晶振时钟,并且此分频数为1分频,因此首先得出PLL的时钟源为:8MHz / 1 = 8MHz。

STM32时钟源的介绍及使用方法——STM32时钟树

STM32时钟源的介绍及使⽤⽅法——STM32时钟树【温馨提⽰:以下内容均来⾃⽹友的⽆私奉献或书本的摘抄,在此表⽰感谢!】上图是STM32的时钟树,从树上我们可以看到,STM32的时钟有两个来源——内部时钟和外部时钟。

按时钟频率来分,⼜可分为⾼速时钟和低速时钟。

因此STM32的时钟有四个来源:⾼速外部时钟信号(HSE)、低速外部时钟信号(LSE)、⾼速内部时钟信号(HSI)和低速内部时钟信号(LSI)(图中分别⽤蓝⾊的①~④标注)。

①HSE⾼速外部时钟:由外部4~16MHz的晶体或有源晶振提供,通常采⽤8MHz。

②LSI低速外部时钟:外部晶体提供,主要是给实时时钟(RTC),⼀般为32.768kHz。

③HSI⾼速内部时钟:由内部RC振荡器产⽣的8MHz时钟,但不够稳定。

④LSI低速内部时钟:内部RC振荡器产⽣的供给RTC的时钟,频率在30kHz~60kHz之间,通常约40kHz。

时钟在STM32内部最终是供给四⼤块(图中⽤红⾊椭圆圈出):USB的48MHz时钟、系统时钟SYSCLK、实时时钟模块RTC、独⽴看门狗的时钟IWDGCLK。

其中最主要的,也是最⼤头是系统时钟SYSCLK,它可以是内部或外部⾼速时钟直接接过来,也可以内、外部⾼速时钟是PLL倍频后提供的,系统时钟再分别供给Cortex内核、SDIO、AHB总线、DMA、APB1、APB2等。

我们通常是采⽤外部8MHz⾼速时钟(HSE),所以着重说HSE。

我们以前⾯的GPIO上的时钟为例,由ST的Datasheet可知,GPIO是在APB2⾼速外设总线上的,图中绿⾊的线就是时钟的流程,我们⼀步步地来看。

8MHz外部晶体(或晶振)输⼊后,先经过⼀个开关PLLXTPRE(HSE divider for PLL entry),此开关决定对HSE进⾏2分频再输⼊到PLL或直接到PLL。

我们选择不分频。

这样时钟⼜到了第⼆个开关PLLSRC(PLL entry clock source),此开关决定PLL的时钟来源,是内部⾼速时钟⼆分频的时钟还是PLLXTPRE的输出。

STM32时钟配置方法详解

STM32时钟配置方法详解时钟树是STM32微控制器中一系列时钟源和时钟分频器的组成部分。

时钟树包括系统时钟、外设时钟和内核时钟。

系统时钟用于驱动整个微控制器系统的核心,外设时钟用于驱动各种外设,内核时钟用于驱动CPU的运算。

在进行时钟配置之前,首先需要了解系统所需的时钟频率。

在STM32中,系统时钟可以通过多种方式进行配置,例如使用外部晶体、外部时钟、内部RC振荡器或者PLL(锁相环)等方式。

外部晶体是一种常用的时钟源,可以提供高精度的时钟频率。

在使用外部晶体时,首先需要设置PLL的时钟源为外部晶体,并设置PLL输入除频器的分频系数。

然后,再根据系统所需的时钟频率,设置PLL的倍频系数,以得到最终的系统时钟频率。

外部时钟是从外部提供的时钟信号,一般用于测试和调试。

使用外部时钟时,需要设置PLL的时钟源为外部时钟,并设置PLL的倍频系数,以得到所需的系统时钟频率。

内部RC振荡器是一种低成本的时钟源,但是其频率不如外部晶体稳定和精确。

在使用内部RC振荡器时,需要设置PLL的时钟源为内部RC振荡器,并设置PLL的倍频系数,以得到所需的系统时钟频率。

PLL是一种用于产生稳定高频时钟的电路,可以从一个低频时钟源产生一个高频时钟源。

使用PLL时,需要设置其输入时钟源和倍频系数。

系统时钟的分频系数可以通过RCC_CFGR寄存器进行设置。

RCC_CFGR寄存器的各个位域用于配置系统时钟的分频系数,包括分频因子、APB1的分频系数、APB2的分频系数等。

外设时钟是用于驱动外设的时钟,可以由系统时钟分频得到。

外设时钟的分频系数可以通过RCC_CFGR寄存器及各个外设的控制寄存器进行设置。

内核时钟是用于驱动CPU的运算的时钟。

在STM32微控制器中,CPU 时钟可以由系统时钟分频得到,分频系数可以通过RCC_CFGR寄存器和FLASH_ACR寄存器进行设置。

除了上述方法之外,STM32还可以使用时钟配置工具进行时钟配置。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

对于广大初次接触STM32的读者朋友(甚至是初次接触ARM器件的读者朋友)来说,在熟悉了开发环境的使用之后,往往“栽倒”在同一个问题上。

这问题有个关键字叫:时钟树。

众所周知,微控制器(处理器)的运行必须要依赖周期性的时钟脉冲来驱动——往往由一个外部晶体振荡器提供时钟输入为始,最终转换为多个外部设备的周期性运作为末,这种时钟“能量”扩散流动的路径,犹如大树的养分通过主干流向各个分支,因此常称之为“时钟树”。

在一些传统的低端8位单片机诸如51,AVR,PIC等单片机,其也具备自身的一个时钟树系统,但其中的绝大部分是不受用户控制的,亦即在单片机上电后,时钟树就固定在某种不可更改的状态(假设单片机处于正常工作的状态)。

比如51单片机使用典型的12MHz晶振作为时钟源,则外设如IO口、定时器、串口等设备的驱动时钟速率便已经是固定的,用户无法将此时钟速率更改,除非更换晶振。

而STM32微控制器的时钟树则是可配置的,其时钟输入源与最终达到外设处的时钟速率不再有固定的关系,本文将来详细解析STM32微控制器的时钟树。

图1是STM32微控制器的时钟树,表1是图中各个标号所表示的部件。

标号图1标号释义

1 内部低速振荡器(LSI,40Khz)

2 外部低速振荡器(LSE,32.768Khz)

3 外部高速振荡器(HSE,3-25MHz)

4 内部高速振荡器(HIS,8MHz)

5 PLL输入选择位

6 RTC时钟选择位

7 PLL1分频数寄存器

8 PLL1倍频寄存器

9 系统时钟选择位

10 USB分频寄存器

11 AHB分频寄存器

12 APB1分频寄存器

13 AHB总线

14 APB1外设总线

15 APB2分频寄存器

16 APB2外设总线

17 ADC预分频寄存器

18 ADC外设

19 PLL2分频数寄存器

20 PLL2倍频寄存器

21 PLL时钟源选择寄存器

22 独立看门狗设备

23 RTC设备

图1 STM32的时钟树

在认识这颗时钟树之前,首先要明确“主干”和最终的“分支”。

假设使用外部8MHz 晶振作为STM32的时钟输入源(这也是最常见的一种做法),则这个8MHz便是“主干”,而“分支”很显然是最终的外部设备比如通用输入输出设备(GPIO)。

这样可以轻易找出第一条时钟的“脉络”:3——5——7——21——8——9——11——13

对此条时钟路径做如下解析:

对于3,首先是外部的3-25MHz(前文已假设为8MHz)输入;

对于5,通过PLL选择位预先选择后续PLL分支的输入时钟(假设选择外部晶振);

对于7,设置外部晶振的分频数(假设1分频);

对于21,选择PLL倍频的时钟源(假设选择经过分频后的外部晶振时钟);

对于8,设置PLL倍频数(假设9倍频);

对于9,选择系统时钟源(假设选择经过PLL倍频所输出的时钟);

对于11,设置AHB总线分频数(假设1分频);

对于13,时钟到达AHB总线;

在上一章节中所介绍的GPIO外设属于APB2设备,即GPIO的时钟来源于APB2总线,同样在图1中也可以寻获GPIO外设的时钟轨迹:

3——5——7——21——8——9——11——15——16

对于3,首先是外部的3-25MHz(前文已假设为8MHz)输入;

对于5,通过PLL选择位预先选择后续PLL分支的输入时钟(假设选择外部晶振);

对于7,设置外部晶振的分频数(假设1分频);

对于21,选择PLL倍频的时钟源(假设选择经过分频后的外部晶振时钟);

对于8,设置PLL倍频数(假设9倍频);

对于9,选择系统时钟源(假设选择经过PLL倍频所输出的时钟);

对于11,设置AHB总线分频数(假设1分频);

对于15,设置APB2总线分频数(假设1分频);

对于16,时钟到达APB2总线;

现在来计算一下GPIO设备的最大驱动时钟速率(各个条件已在上述要点中假设):

1) 由3所知晶振输入为8MHz,由5——21知PLL的时钟源为经过分频后的外部晶振时钟,并且此分频数为1分频,因此首先得出PLL的时钟源为:8MHz / 1 = 8MHz。

2) 由8、9知PLL倍频数为9,且将PLL倍频后的时钟输出选择为系统时钟,则得出系统时钟为8MHz * 9 = 72MHz。

3) 时钟到达AHB预分频器,由11知时钟经过AHB预分频器之后的速率仍为72MHz。

4) 时钟到达APB2预分频器,由15经过APB2预分频器后速率仍为72MHz。

5) 时钟到达APB2总线外设。

因此STM32的APB2总线外设,所能达到的最大速率为72MHz。

依据以上方法读者可以搜寻出APB1总线外设时钟、RTC外设时钟、独立看门狗等外设时钟的来龙去脉。

接下来从程序的角度分析时钟树的设置,程序清单如下:

void RCC_Configuration(void)

{

ErrorStatus HSEStartUpStatus;

(1)

RCC_DeInit();

(2)

RCC_HSEConfig(RCC_HSE_ON);

(3)

HSEStartUpStatus = RCC_WaitForHSEStartUp();

(4)

if(HSEStartUpStatus == SUCCESS)

(5)

{

RCC_HCLKConfig(RCC_SYSCLK_Div1);

(6)

RCC_PCLK2Config(RCC_HCLK_Div1);

(7)

RCC_PCLK1Config(RCC_HCLK_Div2);

(8)

FLASH_SetLatency(FLASH_Latency_2);

(9)

FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);

(10)

RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9);

(11)

RCC_PLLCmd(ENABLE);

(12)

while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET);

(13)RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

(14)while(RCC_GetSYSCLKSource() != 0x08);

(15)

}

}

以上是ST官方所提供的STM32时钟树配置函数,读者首先要知道3点

1、ST所提供的库函数在函数和变量命名上有非常良好的规范性和易读性(虽然有点冗长),即便没有注释,也可从函数名和变量名来大致判断该函数或变量所包含的意义。

2、其次,读者应从上图区分出各个总线和对应的时钟:其中PLLCLK表示PLL锁相环的输出时钟,SYSCLK 表示系统时钟,HCLK表示AHB总线的时钟,PCLK1表示APB1总线的时钟,PCLK2则表示APB2总线的时钟。

3、9、10两句代码的作用是设置STM32内部FLASH的等待周期。

做如下解释:STM32的内部用户FLASH用以存储代码指令供CPU存取以执行,STM32的CPU的最大速率已知为72MHz,但FLASH无法达到这么高的速度,因此要在CPU存取FLASH的过程中插入所谓的“等待周期”,显然CPU速度越快,所要插入的等待周期个数越多,原则是

1)当CPU速率为0 ~ 24MHz时,不需要插入等待周期,即等到周期个数为0;

2)当CPU速率为24 ~ 48MHz时,插入1个等待周期;

3)当CPU速率为48MHz ~ 72MHz时,插入2个等待周期;

有以上三点准备之后,开始解析这段程序:

(1)定义一个ErrorStatus类型的变量HSEStartUpStatus;

(2)将时钟树复位至默认设置;

(3)开启HSE晶振;

(4)等待HSE晶振起振稳定,并将起振结果保存至HSEStartUpStatus变量中;

(5)判断HSE晶振是否起振成功(假设成功了,进入if内部);

(6)设置HCLK时钟为SYSCLK的1分频;

(7)设置PLCK2时钟为SYSCLK的1分频;

(8)设置PLCK1时钟为SYSCLK的2分频;

(11)选择PLL输入源为HSE时钟经过1分频,并进行9倍频;

(12)使能PLL输出;

(13)等待PLL输出稳定;

(14)选择系统时钟源为PLL输出;

(15)等待系统时钟稳定;

上述代码中对时钟树的配置顺序为(对应图中标号):

3——11——14——15——7——21——8——9

通过对比发现,程序中对时钟树的配置顺序并不是依次从图中由左到右、由上到下配置的,这是为什么呢?事实上这个问题相信大部分读者都可以自己解释:电子设计世界的思维和操作方式,其顺序往往和日常生活是不一样的,比如人们经常先给电视机连接电源,再打开电视机开关;先把大水管的总闸打开,再打开小水龙头;总而言之是一种由“主”到“次”的顺序。

转移到最常见的51单片机的开发平台,开发人员往往先把定时器的分频数,重载值等参数配置好,最后才启动定时器计数;先把各个外设的中断打开,最后再打开总中断;这和人们的生活习惯其实恰好相反,是一种先“次”后“主”的顺序。

至此,理解STM32的时钟树就是轻而易举的事情了。