Stm32之寄存器列表

STM32_NVIC寄存器详解

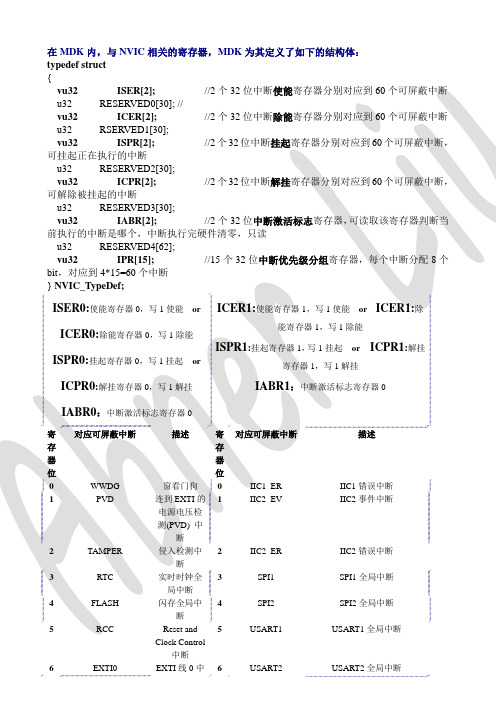

STM32_NVIC寄存器详解在MDK内,与NVIC相关的寄存器,MDK为其定义了如下的结构体:typedef struct{vu32 ISER[2]; //2个32位中断使能寄存器分别对应到60个可屏蔽中断u32 RESERVED0[30];vu32 ICER[2]; //2个32位中断除能寄存器分别对应到60个可屏蔽中断u32 RSERVED1[30];vu32 ISPR[2]; //2个32位中断挂起寄存器分别对应到60个可屏蔽中断,可挂起正在执⾏的中断u32 RESERVED2[30];vu32 ICPR[2]; //2个32位中断解挂寄存器分别对应到60个可屏蔽中断,可解除被挂起的中断u32 RESERVED3[30];vu32 IABR[2]; //2个32位中断激活标志寄存器,可读取该寄存器判断当前执⾏的中断是哪个,中断执⾏完硬件清零,只读u32 RESERVED4[62];vu32 IPR[15]; //15个32位中断优先级分组寄存器,每个中断分配8个bit,对应到4*15=60个中断} NVIC_TypeDef;IPR[15]15个32位中断优先级分组寄存器,每个中断分配8个bit,对应到4*15=60个中断。

但是并不是8个bit都被使⽤了,⽽是仅仅只⽤到了⾼四位,这样就可以得到5组16级的中断优先级。

⾼位的4个bit⼜分为抢占优先级和⼦优先级,抢占优先级在前,⼦优先级在后。

两种类型优先级占⽤的位数⼜可以通过SCB->AIRCR寄存器的bit[10:8]来配置。

数字越⼩优先级越⾼,⾼优先级的中断可以中断低优先级的中断,但是抢占优先级相同时⼦优先级⾼的⽆法中断⼦优先级低的中断。

结合实例说明⼀下:假定设置中断优先级组为2,然后设置中断28(Tim2中断)的抢占优先级为3,响应优先级为2。

中断6(外部中断0)的抢占优先级为4,响应优先级为0。

中断7(外部中断1)的抢占优先级为3,响应优先级为0。

stm32 定时器的相关寄存器

定时器在STM32F10xxx系列的32位MCU上,定时器资源十分丰富,包括高级控制定时器,通用定时器和基本定时器。

此外,还有能够实现定时功能的系统滴答定时器,实时时钟以及看门狗。

关于这些定时器的介绍,占据了STM32F10xxx 参考手册1/5的篇幅,可见其功能的强大。

在低容量和中容量的STM32F103xx产品,以及互联型产品STM32F105xx和STM32F107xx中,只有一个高级控制定时器TIM1。

而在高容量和超大容量的STM32F103xx产品中,有两个高级控制定时器TIM1和TIM8。

在所有STM32F10xxx系列产品中,都有通用定时器TIM2~TIM5,除非另有说明。

除此之外,在超大容量产品中,还有通用定时器TIM9~TIM14。

在高容量和超大容量的STM32F101xx和STM32F103xx产品,以及互联型产品STM32F105xx和STM32F107xx中,有两个基本定时器TIM6和TIM7。

其中,高级控制定时器的功能最为强大,可以实现所有其他定时器的所有功能。

TrailBreaker开发板使用的是高容量的STM32F103ZE,因此有两个高级控制定时器TIM1和TIM8。

下面我们就着重介绍这两个高级控制定时器。

TIM1和TIM8简介高级控制定时器(TIM1和TIM8)由一个16位的自动装载计数器组成,它由一个可编程的预分频器驱动。

它适合多种用途,包含测量输入信号的脉冲宽度(输入捕获),或者产生输出波形(输出比较、PWM、嵌入死区时间的互补PWM等)。

使用定时器预分频器和RCC时钟控制预分频器,可以实现脉冲宽度和波形周期从几个微秒到几个毫秒的调节。

关于实验中用到的LED部分原理图和GPIO跑马灯实验所用到的相同,在此不再多做介绍。

TIM1和TIM8定时器的功能包括:16位向上、向下、向上/下自动装载计数器16位可编程(可以实时修改)预分频器,计数器时钟频率的分频系数为1~65535之间的任意数值多达4个独立通道:─ 输入捕获─ 输出比较─ PWM生成(边缘或中间对齐模式) ─ 单脉冲模式输出死区时间可编程的互补输出使用外部信号控制定时器和定时器互联的同步电路允许在指定数目的计数器周期之后更新定时器寄存器的重复计数器刹车输入信号可以将定时器输出信号置于复位状态或者一个已知状态如下事件发生时产生中断/DMA:─ 更新:计数器向上溢出/向下溢出,计数器初始化(通过软件或者内部/外部触发)─ 触发事件(计数器启动、停止、初始化或者由内部/外部触发计数)─ 输入捕获─ 输出比较─ 刹车信号输入支持针对定位的增量(正交)编码器和霍尔传感器电路触发输入作为外部时钟或者按周期的电流管理高级定时器框图和时钟简介如框图中的红框所示,红框中的部分,也是时基单元(Time-base unit),对时基单元进行设置,就可以完成基础的定时器的使用设置。

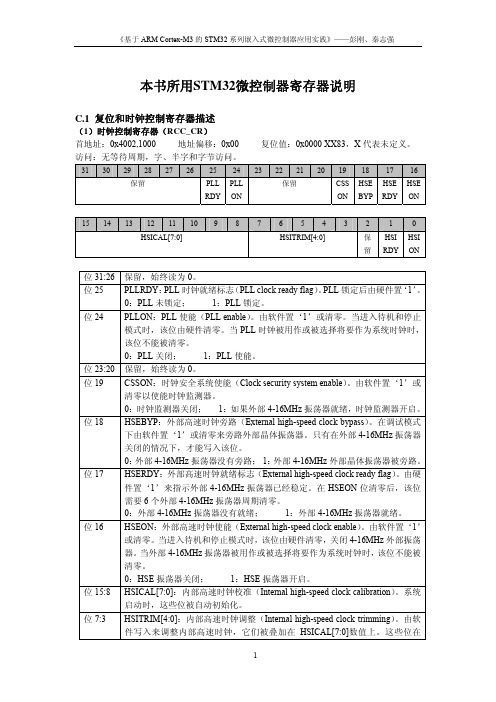

STM32微控制器寄存器说明

PLLXTPRE:HSE 分频器作为 PLL 输入(HSE divider for PLL entry)。由软件

置‘1’或清‘0’来分频 HSE 后作为 PLL 输入时钟。只能在关闭 PLL 时才能

写入此位。

0:HSE 不分频; 1:HSE 2 分频

PLLSRC:PLL 输入时钟源(PLL entry clock source)。由软件置‘1’或清‘0’

保 HSI HSI

留 RDY ON

位 31:26 位 25 位 24

位 23:20 位 19 位 18

位 17

位 16

位 15:8 位 7:3

保留,始终读为 0。 PLLRDY:PLL 时钟就绪标志(PLL clock ready flag)。PLL 锁定后由硬件置‘1’。 0:PLL 未锁定; 1:PLL 锁定。 PLLON:PLL 使能(PLL enable)。由软件置‘1’或清零。当进入待机和停止 模式时,该位由硬件清零。当 PLL 时钟被用作或被选择将要作为系统时钟时, 该位不能被清零。 0:PLL 关闭; 1:PLL 使能。 保留,始终读为 0。 CSSON:时钟安全系统使能(Clock security system enable)。由软件置‘1’或 清零以使能时钟监测器。 0:时钟监测器关闭; 1:如果外部 4-16MHz 振荡器就绪,时钟监测器开启。 HSEBYP:外部高速时钟旁路(External high-speed clock bypass)。在调试模式 下由软件置‘1’或清零来旁路外部晶体振荡器。只有在外部 4-16MHz 振荡器 关闭的情况下,才能写入该位。 0:外部 4-16MHz 振荡器没有旁路; 1:外部 4-16MHz 外部晶体振荡器被旁路。 HSERDY:外部高速时钟就绪标志(External high-speed clock ready flag)。由硬 件置‘1’来指示外部 4-16MHz 振荡器已经稳定。在 HSEON 位清零后,该位 需要 6 个外部 4-16MHz 振荡器周期清零。 0:外部 4-16MHz 振荡器没有就绪; 1:外部 4-16MHz 振荡器就绪。 HSEON:外部高速时钟使能(External high-speed clock enable)。由软件置‘1’ 或清零。当进入待机和停止模式时,该位由硬件清零,关闭 4-16MHz 外部振荡 器。当外部 4-16MHz 振荡器被用作或被选择将要作为系统时钟时,该位不能被 清零。 0:HSE 振荡器关闭; 1:HSE 振荡器开启。 HSICAL[7:0]:内部高速时钟校准(Internal high-speed clock calibration)。系统 启动时,这些位被自动初始化。 HSITRIM[4:0]:内部高速时钟调整(Internal high-speed clock trimming)。由软 件写入来调整内部高速时钟,它们被叠加在 HSICAL[7:0]数值上。这些位在

STM32中几个GPIO寄存器总结

OPA1632 全差动 I/O 音频放大器 音频放大器

OPA2604-Q1 汽车类双路 FET 输入低失真运算放大器 音频放大器

PCM1600 104dB SNR 6 通道音频 DAC 音频转换器

PCM1601 104dB SNR 6 通道音频 DAC 音频转换器

PCM1602 105dB SNR 6 通道音频 DAC 音频转换器

DSD1792 132dB SNR 最高性能立体声音频 DAC(软件控制) 音频转换器

DSD1792A 132dB SNR 最高性能立体声音频 DAC(软件控制) 音频转换器

DSD1793 113dB SNR 立体声音频 DAC(软件控制R 最高性能立体声音频 DAC(硬件控制) 音频转换器

PCM1609 105dB SNR 8 通道音频 DAC 音频转换器

PCM1609A 105dB SNR 8 通道音频 DAC 音频转换器

PCM1680 105dB SNR 8 通道音频 DAC 音频转换器

GPIOA->CRH&=0XFFFFFFF0;//清除该位原来的设置

GPIOA->CRH|=0X00000003;//PA8 推挽输出

GPIOA->ODR|=1<<8; //PA8 输出高

由以上代码看出,PA8设置成了推挽输出。大家都知道一个端口可以输出高电平,也可以输出低电平,而GPIOA->ODR|=1<<8; 这个表达式就把PA8设置成了在空闲的时候输出高电平;GPIOA->ODR|=0<<8; 这个表达式,把PA8设置成了在空闲的时候输出低电平。

一.CRH和CRL的使用:

CRH和CRL的使用基本相同,CRH用于控制GPIOX(X表示A---G)的高8位(Pin15---Pin8),而CRL用于控制GPIOX(X表示A---G)的低8位(Pin7----Pin0)。

stm32寄存器

stm32寄存器(一种算法,用以确认发送过程中是否出错)数据寄存器:CRC_DR可读写,复位值:0xFFFF FFFF;独立数据寄存器:CRC_IDR临时存放任何8位数据;控制寄存器:CRC_CR只零位可用,用于复位CRC,对其写1复位,由硬件清零;PWR电源控制(控制和管理电源)电源控制寄存器:PWR_CR控制选择系统的电源电源控制/状态寄存器:PWR_CSR睡眠或待机模式电源控制BKP备份寄存器(用以控制和管理备份数据)备份数据寄存器x:BKP_DRx (x = 1 … 10) 10个16位数据寄存器用以存储用户数据RTC时钟校准寄存器:BKP_RTCCR控制实时时钟的运行备份控制寄存器:BKP_CR控制选择清除备份数据的类型备份控制/状态寄存器:BKP_CSR对侵入事件的控制(时钟的选择、复位、分频)时钟控制寄存器(RCC_CR)各时钟状态显示时钟配置寄存器(RCC_CFGR)时钟分频时钟中断寄存器(RCC_CIR)控制就绪中断使能与否APB2外设复位寄存器(RCC_APB2RSTR) APB1外设复位寄存器(RCC_APB1RSTR) 复位APB各功能寄存器AHB外设时钟使能寄存器(RCC_AHBENR) AHB时钟使能控制APB2外设时钟使能寄存器(RCC_APB2ENR) APB1外设时钟使能寄存器(RCC_APB1ENR) APB1时钟使能控制备份域控制寄存器(RCC_BDCR)备份域时钟控制控制/状态寄存器(RCC_CSR)复位标志寄存器AHB外设时钟复位寄存器(RCC_AHBRSTR) 复位以太网MAC模块时钟配置寄存器2(RCC_CFGR2)时钟选择与分频(设置端口的功能)端口配置低寄存器(GPIOx_CRL) (x=A..E)端口配置高寄存器(GPIOx_CRH) (x=A..E)端口输入数据寄存器(GPIOx_IDR) (x=A..E)只读数据,读出IO口的状态端口输出数据寄存器(GPIOx_ODR) (x=A..E) 可读可写端口位设置/清除寄存器(GPIOx_BSRR) (x=A..E)端口位清除寄存器(GPIOx_BRR) (x=A..E)将某一端口清零端口配置锁定寄存器(GPIOx_LCKR) (x=A..E) 用于保护端口配值AFIO寄存器(将端口重映射到其它端口用以端口的第二功能)事件控制寄存器(AFIO_EVCR)选择时间输出端口与引脚复用重映射和调试I/O配置寄存器(AFIO_MAPR) 各寄存器功能引脚重映射选择外部中断配置寄存器1(AFIO_EXTICR1)外部中断配置寄存器2(AFIO_EXTICR2)外部中断配置寄存器3(AFIO_EXTICR3)外部中断配置寄存器4(AFIO_EXTICR4)外部中断引脚重映射选择EXTI 寄存器(外部中断控制器)中断屏蔽寄存器(EXTI_IMR)用于屏蔽或开放某一引脚的中断请求事件屏蔽寄存器(EXTI_EMR)用于屏蔽或开放某一引脚的事件上升沿触发选择寄存器(EXTI_RTSR)禁止或允许某一引脚的上升沿触发下降沿触发选择寄存器(EXTI_FTSR)禁止或允许某一引脚的下降沿触发软件中断事件寄存器(EXTI_SWIER)控制某引脚的软件中断挂起寄存器(EXTI_PR)显示某线的引脚有无触发请求DMA寄存器(脱离cpu的传输模式)DMA中断状态寄存器(DMA_ISR)中断情况标志器DMA中断标志清除寄存器(DMA_IFCR)手动清除标志位DMA通道x配置寄存器(DMA_CCRx)(x = 1…7)传输控制寄存器DMA通道x传输数量寄存器(DMA_CNDTRx)(x = 1…7)数据传输剩余数量存储器DMA通道x外设地址寄存器(DMA_CPARx)(x = 1…7)设置数据传输外设源或目标地址DMA通道x存储器地址寄存器(DMA_CMARx)(x = 1…7)设置存储器地址ADC寄存器(模数转换器)ADC状态寄存器(ADC_SR)AD转换标志寄存器ADC控制寄存器1(ADC_CR1)ADC控制寄存器2(ADC_CR2)设置AD转换的各种功能ADC采样时间寄存器1(ADC_SMPR1)ADC采样时间寄存器2(ADC_SMPR2)某通道选择固定的采样时间ADC注入通道数据偏移寄存器x (ADC_JOFRx)(x=1..4) 设置数据偏移量ADC看门狗高阀值寄存器(ADC_HTR)设置模拟看门狗的阀值高限ADC看门狗低阀值寄存器(ADC_LRT)设置模拟看门狗的阀值低限ADC规则序列寄存器1(ADC_SQR1)ADC规则序列寄存器2(ADC_SQR2)ADC规则序列寄存器3(ADC_SQR3)设置ADC顺序ADC注入序列寄存器(ADC_JSQR)ADC 注入数据寄存器x (ADC_JDRx) (x= 1..4)ADC数据结果寄存器ADC规则数据寄存器(ADC_DR)DAC寄存器(数模转换器)DAC控制寄存器(DAC_CR)DAC软件触发寄存器(DAC_SWTRIGR)DAC通道1的12位右对齐数据保持寄存器(DAC_DHR12R1) DAC 通道1的12位左对齐数据保持寄存器(DAC_DHR12L1) DAC通道1的8位右对齐数据保持寄存器(DAC_DHR8R1) DAC通道2的12位右对齐数据保持寄存器(DAC_DHR12R2) DAC通道2的12位左对齐数据保持寄存器(DAC_DHR12L2) DAC通道2的8位右对齐数据保持寄存器(DAC_DHR8R2)双DAC的12位右对齐数据保持寄存器(DAC_DHR12RD)双DAC的12位左对齐数据保持寄存器(DAC_DHR12LD)双DAC的8位右对齐数据保持寄存器(DAC_DHR8RD) DAC通道1数据输出寄存器(DAC_DOR1)DAC通道2数据输出寄存器(DAC_DOR2)TIM1和TIM8寄存器(高级的定时计数寄存器)TIM1和TIM8控制寄存器1(TIMx_CR1)TIM1和TIM8控制寄存器2(TIMx_CR2)TIM1和TIM8从模式控制寄存器(TIMx_SMCR)TIM1和TIM8 DMA/中断使能寄存器(TIMx_DIER) TIM1和TIM8状态寄存器(TIMx_SR)TIM1和TIM8事件产生寄存器(TIMx_EGR)TIM1和TIM8捕获/比较模式寄存器1(TIMx_CCMR1) TIM1和TIM8捕获/比较模式寄存器2(TIMx_CCMR2) TIM1和TIM8捕获/比较使能寄存器(TIMx_CCER) TIM1和TIM8计数器(TIMx_CNT) TIM1和TIM8预分频器(TIMx_PSC)TIM1和TIM8自动重装载寄存器(TIMx_ARR)TIM1和TIM8重复计数寄存器(TIMx_RCR)TIM1和TIM8捕获/比较寄存器1(TIMx_CCR1)TIM1和TIM8捕获/比较寄存器2(TIMx_CCR2)TIM1和TIM8捕获/比较寄存器3(TIMx_CCR3)TIM1和TIM8捕获/比较寄存器(TIMx_CCR4)TIM1和TIM8刹车和死区寄存器(TIMx_BDTR)TIM1和TIM8 DMA控制寄存器(TIMx_DCR)TIM1和TIM8连续模式的DMA地址(TIMx_DMAR)TIMx寄存器(控制定时器)控制寄存器1(TIMx_CR1)控制寄存器2(TIMx_CR2)从模式控制寄存器(TIMx_SMCR)DMA/中断使能寄存器(TIMx_DIER)状态寄存器(TIMx_SR)事件产生寄存器(TIMx_EGR)捕获/比较模式寄存器1(TIMx_CCMR1) 捕获/比较模式寄存器2(TIMx_CCMR2) 捕获/比较使能寄存器(TIMx_CCER)计数器(TIMx_CNT)预分频器(TIMx_PSC)自动重装载寄存器(TIMx_ARR)捕获/比较寄存器1(TIMx_CCR1)捕获/比较寄存器2(TIMx_CCR2)捕获/比较寄存器3(TIMx_CCR3)捕获/比较寄存器4(TIMx_CCR4)DMA控制寄存器(TIMx_DCR)连续模式的DMA地址(TIMx_DMAR)TIM6和TIM7寄存器(基本定时计数器)TIM6和TIM7控制寄存器1(TIMx_CR1)TIM6和TIM7控制寄存器2(TIMx_CR2)TIM6和TIM7 DMA/中断使能寄存器(TIMx_DIER)TIM6和TIM7状态寄存器(TIMx_SR)TIM6和TIM7事件产生寄存器(TIMx_EGR)TIM6和TIM7计数器(TIMx_CNT)TIM6和TIM7预分频器(TIMx_PSC)TIM6和TIM7自动重装载寄存器(TIMx_ARR)RTC寄存器(实时时钟)RTC控制寄存器高位(RTC_CRH)RTC控制寄存器低位(RTC_CRL)16.4.3 RTC预分频装载寄存器(RTC_PRLH/RTC_PRLL) 16.4.4 RTC 预分频器余数寄存器(RTC_DIVH / RTC_DIVL) RTC计数器寄存器(RTC_CNTH / RTC_CNTL)16.4.6 RTC闹钟寄存器(RTC_ALRH/RTC_ALRL)IWDG寄存器(独立看门狗,用以监督系统硬件的正常运行)键寄存器(IWDG_KR)预分频寄存器(IWDG_PR)重装载寄存器(IWDG_RLR)状态寄存器(IWDG_SR)窗口看门狗(WWDG)寄存器(用以监督软件的正常运行)控制寄存器(WWDG_CR)配置寄存器(WWDG_CFR)状态寄存器(WWDG_SR)FSMC寄存器(可变静态存储控制器)NOR闪存和PSRAM控制器寄存器SRAM/NOR闪存片选控制寄存器1…4 (FSMC_BCR1…4)SRAM/NOR闪存片选时序寄存器1…4 (FSMC_BTR1…4)SRAM/NOR闪存写时序寄存器1…4 (FSMC_BWTR1…4) NAND 闪存和PC卡控制器寄存器PC卡/NAND闪存控制寄存器2..4 (FSMC_PCR2..4)FIFO状态和中断寄存器2..4 (FSMC_SR2..4)通用存储空间时序寄存器 2..4 (FSMC_PMEM2..4)属性存储空间时序寄存器 2..4 (FSMC_PATT2..4)I/O空间时序寄存器4 (FSMC_PIO4)ECC结果寄存器2/3 (FSMC_ECCR2/3)SDIO寄存器(数据传输控制器)SDIO电源控制寄存器(SDIO_POWER) SDIO时钟控制寄存器(SDIO_CLKCR) SDIO参数寄存器(SDIO_ARG)SDIO命令寄存器(SDIO_CMD)SDIO命令响应寄存器(SDIO_RESPCMD) SDIO响应1..4寄存器(SDIO_RESPx)SDIO数据定时器寄存器(SDIO_DTIMER) SDIO数据长度寄存器(SDIO_DLEN)SDIO数据控制寄存器(SDIO_DCTRL SDIO数据计数器寄存器(SDIO_DCOUNT) SDIO状态寄存器(SDIO_STA)SDIO清除中断寄存器(SDIO_ICR)SDIO中断屏蔽寄存器(SDIO_MASK)SDIO FIFO计数器寄存器(SDIO_FIFOCNT) SDIO数据FIFO寄存器(SDIO_FIFO)USB寄存器(usb传输控制器)通用寄存器USB控制寄存器(USB_CNTR)USB中断状态寄存器(USB_ISTR)USB帧编号寄存器(USB_FNR)USB设备地址寄存器(USB_DADDR)USB分组缓冲区描述表地址寄存器(USB_BTABLE)端点寄存器USB 端点n寄存器(USB_EPnR), n=[0..7]缓冲区寄存器发送缓冲区地址寄存器n(USB_ADDRn_TX)发送数据字节数寄存器n(USB_COUNTn_TX)接收缓冲区地址寄存器n(USB_ADDRn_RX)接收数据字节数寄存器n(USB_COUNTn_RX)CAN 寄存器(邮箱控制寄存器)CAN控制和状态寄存器CAN主控制寄存器(CAN_MCR)CAN主状态寄存器(CAN_MSR)CAN发送状态寄存器(CAN_TSR)CAN接收FIFO 0寄存器(CAN_RF0R)CAN接收FIFO 1寄存器(CAN_RF1R)CAN中断使能寄存器(CAN_IER)CAN错误状态寄存器(CAN_ESR)CAN位时序寄存器(CAN_BTR)CAN邮箱寄存器发送邮箱标识符寄存器(CAN_TIxR) (x=0..2)发送邮箱数据长度和时间戳寄存器(CAN_TDTxR) (x=0..2)发送邮箱低字节数据寄存器(CAN_TDLxR) (x=0..2)发送邮箱高字节数据寄存器(CAN_TDHxR) (x=0..2)接收FIFO邮箱标识符寄存器(CAN_RIxR) (x=0..1)接收FIFO邮箱数据长度和时间戳寄存器(CAN_RDTxR) (x=0..1) 接收FIFO邮箱低字节数据寄存器(CAN_RDLxR) (x=0..1)接收FIFO邮箱高字节数据寄存器(CAN_RDHxR) (x=0..1)CAN过滤器寄存器CAN 过滤器主控寄存器(CAN_FMR)CAN 过滤器模式寄存器(CAN_FM1R)CAN 过滤器位宽寄存器(CAN_FS1R)CAN 过滤器FIFO关联寄存器(CAN_FFA1R)CAN 过滤器激活寄存器(CAN_FA1R)CAN 过滤器组i的寄存器x (CAN_FiRx) (互联产品中i=0..27,其它产品中i=0..13;x=1..2)SPI和I2S寄存器(串行外设接口控制器)SPI控制寄存器1(SPI_CR1)SPI控制寄存器2(SPI_CR2)SPI 状态寄存器(SPI_SR)SPI 数据寄存器(SPI_DR)SPI CRC多项式寄存器(SPI_CRCPR) SPI Rx CRC寄存器(SPI_RXCRCR)SPI Tx CRC寄存器(SPI_TXCRCR)SPI_I2S配置寄存器(SPI_I2S_CFGR) SPI_I2S预分频寄存器(SPI_I2SPR)I2C寄存器(数据传输寄存器)控制寄存器1(I2C_CR1)控制寄存器2(I2C_CR2)自身地址寄存器1(I2C_OAR1)自身地址寄存器2(I2C_OAR2)数据寄存器(I2C_DR)状态寄存器1(I2C_SR1)状态寄存器2 (I2C_SR2)时钟控制寄存器(I2C_CCR)TRISE寄存器(I2C_TRISE)USART寄存器(通用同步异步收发器)状态寄存器(USART_SR)数据寄存器(USART_DR)波特比率寄存器(USART_BRR)控制寄存器1(USART_CR1)控制寄存器2(USART_CR2)控制寄存器3(USART_CR3)保护时间和预分频寄存器(USART_GTPR) OTG_FS控制和状态寄存器(数据传输控制器)OTG_FS全局寄存器OTG_FS控制和状态寄存器(OTG_FS_GOTGCTL)OTG_FS中断寄存器(OTG_FS_GOTGINT)OTG_FS AHB配置寄存器(OTG_FS_GAHBCFG)OTG_FS_USB配置寄存器(OTG_FS_GUSBCFG)OTG_FS复位寄存器(OTG_FS_GRSTCTL)OTG_FS控制器中断寄存器(OTG_FS_GINTSTS)OTG_FS中断屏蔽寄存器(OTG_FS_GINTMSK)OTG_FS接收状态调试读/OTG状态读和POP寄存器(OTG_FS_GRXSTSR / OTG_FS_GRXSTSP)OTG_FS接收FIFO长度寄存器(OTG_FS_GRXFSIZ)OTG_FS非周期性TX FIFO长度寄存器(OTG_FS_GNPTXFSIZ)OTG_FS非周期性TX FIFO/请求队列状态寄存器(OTG_FS_GNPTXSTS)OTG_FS通用控制器配置寄存器(OTG_FS_GCCFG)OTG_FS控制器ID寄存器(OTG_FS_CID)OTG_FS主机周期性发送FIFO长度寄存器(OTG_FS_HPTXFSIZ) OTG_FS设备IN端点发送FIFO长度寄存器(OTG_FS_DIEPTXFx)(其中x是FIFO的编号,x=1…4)主机模式下的寄存器OTG_FS主机模式配置寄存器(OTG_FS_HCFG)OTG_FS主机帧间隔寄存器(OTG_FS_HFIR)OTG_FS主机帧号/帧时间剩余寄存器(OTG_FS_HFNUM)OTG_FS主机周期性发送FIFO/请求队列寄存器(OTG_FS_HPTXSTS)OTG_FS主机所有通道中断寄存器(OTG_FS_HAINT)OTG_FS主机所有通道中断屏蔽寄存器(OTG_FS_HAINTMSK)OTG_FS主机端口控制和状态寄存器(OTG_FS_HPRT)OTG_FS主机通道x特性寄存器(OTG_FS_HCCHARx)(此处x代码通道号,x = 0...7)OTG_FS主机通道x中断寄存器(OTG_FS_HCINTx)(其中x代表通道号,x=0...7,)OTG_FS主机通道x中断屏蔽寄存器(OTG_FS_HCINTMSKx)(其中x为通道号,x=0...7) OTG_FS主机通道x传输长度寄存器(OTG_FS_HCTSIZx)(其中x为通道号,x=0...7)设备模式下的寄存器OTG_FS设备配置寄存器(OTG_FS_DCFG)OTG_FS设备控制寄存器(OTG_FS_DCTL)OTG_FS设备状态寄存器(OTG_FS_DSTS)OTG_FS设备IN端点通用中断屏蔽寄存器(OTG_FS_DIEPMSK)OTG_FS设备OUT端点通用中断屏蔽寄存器(OTG_FS_DOEPMSK) OTG_FS设备所有端点中断寄存器(OTG_FS_DAINT)OTG_FS所有端点中断屏蔽寄存器(OTG_FS_DAINTMSK)OTG_FS设备V BUS放电时间寄存器(OTG_FS_DVBUSDIS)OTG_FS设备V BUS脉冲时间寄存器(OTG_FS_DVBUSPULSE)OTG_FS设备IN端点FIFO空中断屏蔽寄存器(OTG_FS_DIEPEMPMSK)OTG_FS设备控制IN端点0控制寄存器(OTG_FS_DIEPCTL0)OTG设备端点x控制寄存器(OTG_FS_DIEPCTLx)(其中x为端点号,x=1…3)OTG_FS设备控制OUT端点0控制寄存器(OTG_FS_DOEPCTL0) OTG_FS设备OUT端点x控制寄存器(OTG_FS_DOEPCTLx)(其中x为端点号,x=1…3) OTG_FS设备端点x中断寄存器(OTG_FS_DIEPINTx)(其中x为端点号,x=0…3)OTG_FS设备端点x中断寄存器(OTG_FS_DOEPINTx)(其中x为端点号,x=0…3)OTG_FS设备IN端点0传输长度寄存器(OTG_FS_DIEPTSIZ0)OTG_FS设备OUT端点0传输长度寄存器(OTG_FS_DOEPTSIZ0) OTG_FS设备端点x传输长度寄存器(OTG_FS_DIEPTSIZx)(其中x 为端点号,x=1…3) OTG_FS设备IN端点传输FIFO状态寄存器(OTG-FS_DTXFSTSx)(其中x为端点号,x=0…3)OTG_FS设备端点x传输长度寄存器(OTG_FS_DOEPTSIZx)(其中x 为端点号,x=1…3) OTG_FS电源和时钟门控寄存器(OTG_FS_PCGCCTL)以太网寄存器(通信传输控制器)MAC寄存器以太网MAC设置寄存器(ETH_MACCR)以太网MAC帧过滤器寄存器(ETH_MACFFR)以太网MAC Hash列表高寄存器(ETH_MACHTHR)以太网MAC Hash列表低寄存器(ETH_MACHTLR)以太网MAC MII地址寄存器(ETH_MACMIIAR)以太网MAC MII数据寄存器(ETH_MACMIIDR)以太网MAC流控寄存器(ETH_MACFCR)以太网MAC VLAN标签寄存器(ETH_MACVLANTR)以太网MAC远程唤醒帧过滤器寄存器(ETH_MACRWUFFR)以太网MAC PMT控制和状态寄存器(ETH_MACPMTCSR)以太网MAC中断状态寄存器(ETH_MACSR)以太网MAC中断屏蔽寄存器(ETH_MAIMR)以太网MAC地址0高寄存器(ETH_MACA0HR)以太网MAC地址0低寄存器(ETH_MACA0LR)以太网MAC地址1高寄存器(ETH_MACA1HR)以太网MAC地址1低寄存器(ETH_MACA1LR)以太网MAC地址2高寄存器(ETH_MACA2HR)以太网MAC地址2低寄存器(ETH_MACA2LR)以太网MAC地址3高寄存器(ETH_MACA3HR)以太网MAC地址3低寄存器(ETH_MACA3LR)MMC寄存器以太网MMC控制寄存器(ETH_MMCCR)以太网MMC接收中断寄存器(ETH_MMCRIR)以太网MMC发送中断寄存器(ETH_MMCTIR)以太网MMC接收中断屏蔽寄存器(ETH_MMCRIMR)以太网MMC发送中断屏蔽寄存器(ETH_MMCTIMR)以太网MMC1次冲突后发送”好”帧的计数器寄存器(ETH_MMCTGFSCCR)以太网MMC1次以上冲突后发送”好”帧的计数器寄存器(ETH_MMCTGFMSCCR)以太网MMC发送”好”帧的计数器寄存器(ETH_MMCTGFCR)以太网MMC CRC错误接收帧计数器寄存器(ETH_ MMCRFCECR) 以太网MMC对齐错误接收帧计数器寄存器(ETH_ MMCRFAECR) 以太网MMC接收帧”好”单播帧计数器寄存器(ETH_ MMCRGUFCR)27.8.3。

STM32L

STM32LSTM32L--GPIO分类: STM32L 2013-09-09 00:00 298人阅读评论(0) 收藏举报stm32STM32L GPIO1. 每个GPIO均有以下寄存器:•4个32位配置寄存器:GPIOx_MODER、GPIOx_OTYPER、GPIOx_OSPEEDR和GPIOx_PUPDRGPIOx_MODER :配置IO端口方向为输入/输出/AF/模拟GPIOx_OTYPER :选择输出类型:推挽/开漏GPIOx_OSPEEDR :选择IO速度(与IO端口方向无关)GPIOx_PUPDR :选择上拉/下拉电阻(与IO端口方向无关)•2个32位数据寄存器:GPIOx_IDR、GPIOx_ODR•1个32位置位/复位寄存器:GPIOx_BSRR(使用该寄存器读写寄存器可以避免在读写期间被IRQ中断,该读写操作属于一个原子操作)该寄存器允许置位/复位GPIOx_ODR上指定的一位,GPIOx_ODR上每位关联到两个控制位:GPIOx_BSRR:BSRR(i) [Bits 15:0]和 GPIOx_BSRR:BSRR(i+SIZE)[Bits31:16];往GPIOx_BSRR:BSRR(i) [Bits 15:0]写1 可以置位对应的ODR;往GPIOx_BSRR:BSRR(i) [Bits 31:16]写1 可以置位对应的ODR;往该寄存器写0不会产生任何影响•1个32位锁定寄存器:GPIOx_LCKR必需通过通过一个特殊的读写时序才能写入该寄存器,但时序正确时,bit16会置位(lock key active),bits[15:0]显示哪些IO端口被锁定了,端口被锁定之后直到下一个复位才能解锁,锁定之后以下寄存器将被冻结:GPIOx_MODER、GPIOx_OTYPER、GPIOx_OSPEEDR、GPIOx_PUPDR、GPIOx_AFRH、GPIOx_AFRL•2个复用功能寄存器:GPIOx_AFRH、GPIOx_AFRL2. 每个GPIO端口均可单独设置为以下模式:•输入+悬空•输入+上拉•输入+下拉•模拟(用作ADC、DAC输出或者捕获输入情况下)•输出+开漏+上拉/下拉(输出模式下GPIO的输出速度是可配置的)•输出+推挽+上拉/下拉•复用功能+推挽+上拉/下拉•复用功能+开漏+上拉/下拉下图为GPIO的架构图:3. GPIO一般用途1.默认情况或者刚复位后,所有IO端口被设置为输入+悬空模式,除了调试接口默认设置为了复用功能+上拉/下拉2.当端口被设置为输出的时候,修改GPIOx_ODR对应可改变输出高低电平(一般会使用推挽或者开漏输出(输出低电平时,只有N-MOS是接通的))3.当端口被设置为输入的时候,每个AHB总线时钟均会捕获端口上高低电平,并存放在GPIOx_IDR寄存器4.所有的GPIO端口均可通过配置寄存器使能或不使能内部弱上拉/弱下拉4 .I/O端口多路复用及映射IO端口通过一个内部的多路选择器以允许在同一时刻只使用一种复用功能,这样使得多个外围电路共享同样的IO端口每个IO端口可以通过配置GPIOx_AFRL和GPIOx_AFRH设置所使能的复用功能(AF0~AF15)•复位之后,所有的IO连接到复用功能0(AF0)•外围电路的复用功能映射到AF1~AF14•Cortex-M3 EVENTOUT映射到AF15以下说明如何使用复用功能:•System Function:配置IO端口使能的复用功能(JTAG/SWD,在复位之后对应端口会被调试器设置为调试功能下且不受GPIO寄存器的控制;RTC_50HZ,对应端口需要设置为输入+悬空;MCO,该端口必需配置在复用模式下)•GPIO:根据需要配置GPIOx_MODER设置IO端口工作模式(输入、输入/模拟)•Perpheral‘s Alternate Function:对于ADC/DAC,配置IO为模拟;对于其他外围功能,配置GPIOx_MODER、GPIOx_OTYPE、GPIOx_PUPDR、GPIOx_OSPEEDER•EVENTOUT:配置IO端口复用功能AF15,用于输出Cortex-M3 EVENTOUT信号•5. 外部中断/唤醒所有的IO端口均有外部中断功能,使用外部中断功能时,IO端口必需设置为输入模式6. 输入模式配置当IO端口配置为输入模式时:•输出模式被禁用•施密特触发器被激活•根据GPIOx_PUPDR寄存器使能上拉/下拉电阻•每个AHB时钟均会采样IO端口上的值存放到输入数据寄存器中•通过读取输入数据寄存器可以检测IO状态7. 输出模式配置当IO端口配置为输出模式时:•输出模式使能•施密特出发器被激活-- 开漏模式时:输出0时,N-MOS导通(P-MOS任何情况下不会导通)-- 推挽模式时:输出0时,N-MOS导通;输出1时,P-MOS导通•根据GPIOx_PUPDR寄存器使能弱上拉/下拉•每个AHB时钟均会采样IO端口上的值存放到输入数据寄存器中•通过读取输入数据寄存器可以检测IO状态•通过读取输出数据寄存器可以得到最后写入的值8. 复用功能配置当IO端口配置为复用功能时:•输出模式下可配置为开漏或推挽•复用功能的输出信号将驱动输出缓冲区•输入端的施密特触发器被激活•根据GPIOx_PUPDR寄存器使能弱上拉/下拉•每个AHB时钟均会采样IO端口上的值存放到输入数据寄存器中•通过读取输入数据寄存器可以检测IO状态9. 模拟模式配置当IO端口配置为模拟模式时:•输出模式被禁用•输入模式下的施密特触发器被激活(为每个IO口的模拟值提供零功耗,施密特触发器的输出端被强制输出为0)•弱上拉/下拉被禁用•读取输入寄存器获取到010. 外部时钟/外部晶振端口复用•没有使用LSE时,OSC32_IN和OSC32_OUT 可配置为一般用途的IO端口•没有使用HSE时,OSC_IN和OSC_OUT 可配置为一般用途的IO端口11. 选择RTC_AF1复用功能STM32L152XX拥有以下特性•两个GPIO端口可配置为唤醒源WKUP1和WKUP3•一个GPIO端口可配置为唤醒源WKUP2,可用于检测篡改、时间戳事件,输出RTC AFO_ALARM、AFO_CALIBRTC_AF1端口(PC13)可配置为以下功能:•唤醒源(WKUP2):配置PWR_CSR寄存器中的EWUP2位•RTC AFO_ALARM输出:根据RTC_CR寄存器中的OSEL[1:0]输出可配置为:RTC Alarm A、 RTC Alarm B、RTC Wakeup •RTC AFO_CALIB输出:配置RTC_CR寄存器中的COE[23]位•RTC AFI_TAMPER1 :篡改事件检测•时间戳事件检测12. 初始化GPIO端口例子[cpp]view plaincopy1.void Init_GPIOS(void){2.GPIO_InitTypeDef GPIO_InitStructure; //定义初始化结构体3.RCC_AHBPeriphClockCmd(RCC_AHBPeriph_GPIOB,ENABLE); //使能对应AHB总线时钟4.5.GPIO_InitStructure.GPIO_Pin = GPIO_Pin_6 | GPIO_Pin_7; //根据需求配置GPIO工作模式6.GPIO_InitStructure.GPIO_Mode = GPIO_Mode_OUT;7.GPIO_InitStructure.GPIO_OType = GPIO_OType_PP;8.GPIO_InitStructure.GPIO_Speed = GPIO_Speed_40MHz;9.GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_UP;10.GPIO_Init(GPIOB, &GPIO_InitStructure); //初始化GPIO端口11.}STM32L--GPIO分类: STM32L 2013-09-09 00:00 298人阅读评论(0) 收藏举报stm32STM32L GPIO1. 每个GPIO均有以下寄存器:•4个32位配置寄存器:GPIOx_MODER、GPIOx_OTYPER、GPIOx_OSPEEDR和GPIOx_PUPDRGPIOx_MODER :配置IO端口方向为输入/输出/AF/模拟GPIOx_OTYPER :选择输出类型:推挽/开漏GPIOx_OSPEEDR :选择IO速度(与IO端口方向无关)GPIOx_PUPDR :选择上拉/下拉电阻(与IO端口方向无关)•2个32位数据寄存器:GPIOx_IDR、GPIOx_ODR•1个32位置位/复位寄存器:GPIOx_BSRR(使用该寄存器读写寄存器可以避免在读写期间被IRQ中断,该读写操作属于一个原子操作)该寄存器允许置位/复位GPIOx_ODR上指定的一位,GPIOx_ODR上每位关联到两个控制位:GPIOx_BSRR:BSRR(i) [Bits 15:0]和 GPIOx_BSRR:BSRR(i+SIZE)[Bits31:16];往GPIOx_BSRR:BSRR(i) [Bits 15:0]写1 可以置位对应的ODR;往GPIOx_BSRR:BSRR(i) [Bits 31:16]写1 可以置位对应的ODR;往该寄存器写0不会产生任何影响•1个32位锁定寄存器:GPIOx_LCKR必需通过通过一个特殊的读写时序才能写入该寄存器,但时序正确时,bit16会置位(lock key active),bits[15:0]显示哪些IO端口被锁定了,端口被锁定之后直到下一个复位才能解锁,锁定之后以下寄存器将被冻结:GPIOx_MODER、GPIOx_OTYPER、GPIOx_OSPEEDR、GPIOx_PUPDR、GPIOx_AFRH、GPIOx_AFRL•2个复用功能寄存器:GPIOx_AFRH、GPIOx_AFRL2. 每个GPIO端口均可单独设置为以下模式:•输入+悬空•输入+上拉•输入+下拉•模拟(用作ADC、DAC输出或者捕获输入情况下)•输出+开漏+上拉/下拉(输出模式下GPIO的输出速度是可配置的)•输出+推挽+上拉/下拉•复用功能+推挽+上拉/下拉•复用功能+开漏+上拉/下拉下图为GPIO的架构图:3. GPIO一般用途1.默认情况或者刚复位后,所有IO端口被设置为输入+悬空模式,除了调试接口默认设置为了复用功能+上拉/下拉2.当端口被设置为输出的时候,修改GPIOx_ODR对应可改变输出高低电平(一般会使用推挽或者开漏输出(输出低电平时,只有N-MOS是接通的))3.当端口被设置为输入的时候,每个AHB总线时钟均会捕获端口上高低电平,并存放在GPIOx_IDR寄存器4.所有的GPIO端口均可通过配置寄存器使能或不使能内部弱上拉/弱下拉4 .I/O端口多路复用及映射IO端口通过一个内部的多路选择器以允许在同一时刻只使用一种复用功能,这样使得多个外围电路共享同样的IO端口每个IO端口可以通过配置GPIOx_AFRL和GPIOx_AFRH设置所使能的复用功能(AF0~AF15)•复位之后,所有的IO连接到复用功能0(AF0)•外围电路的复用功能映射到AF1~AF14•Cortex-M3 EVENTOUT映射到AF15以下说明如何使用复用功能:•System Function:配置IO端口使能的复用功能(JTAG/SWD,在复位之后对应端口会被调试器设置为调试功能下且不受GPIO寄存器的控制;RTC_50HZ,对应端口需要设置为输入+悬空;MCO,该端口必需配置在复用模式下)•GPIO:根据需要配置GPIOx_MODER设置IO端口工作模式(输入、输入/模拟)•Perpheral‘s Alternate Function:对于ADC/DAC,配置IO为模拟;对于其他外围功能,配置GPIOx_MODER、GPIOx_OTYPE、GPIOx_PUPDR、GPIOx_OSPEEDER •EVENTOUT:配置IO端口复用功能AF15,用于输出Cortex-M3 EVENTOUT信号•5. 外部中断/唤醒所有的IO端口均有外部中断功能,使用外部中断功能时,IO端口必需设置为输入模式6. 输入模式配置当IO端口配置为输入模式时:•输出模式被禁用•施密特触发器被激活•根据GPIOx_PUPDR寄存器使能上拉/下拉电阻•每个AHB时钟均会采样IO端口上的值存放到输入数据寄存器中•通过读取输入数据寄存器可以检测IO状态7. 输出模式配置当IO端口配置为输出模式时:•输出模式使能•施密特出发器被激活-- 开漏模式时:输出0时,N-MOS导通(P-MOS任何情况下不会导通)-- 推挽模式时:输出0时,N-MOS导通;输出1时,P-MOS导通•根据GPIOx_PUPDR寄存器使能弱上拉/下拉•每个AHB时钟均会采样IO端口上的值存放到输入数据寄存器中•通过读取输入数据寄存器可以检测IO状态•通过读取输出数据寄存器可以得到最后写入的值8. 复用功能配置当IO端口配置为复用功能时:•输出模式下可配置为开漏或推挽•复用功能的输出信号将驱动输出缓冲区•输入端的施密特触发器被激活•根据GPIOx_PUPDR寄存器使能弱上拉/下拉•每个AHB时钟均会采样IO端口上的值存放到输入数据寄存器中•通过读取输入数据寄存器可以检测IO状态9. 模拟模式配置当IO端口配置为模拟模式时:•输出模式被禁用•输入模式下的施密特触发器被激活(为每个IO口的模拟值提供零功耗,施密特触发器的输出端被强制输出为0)•弱上拉/下拉被禁用•读取输入寄存器获取到010. 外部时钟/外部晶振端口复用•没有使用LSE时,OSC32_IN和OSC32_OUT 可配置为一般用途的IO端口•没有使用HSE时,OSC_IN和OSC_OUT 可配置为一般用途的IO端口11. 选择RTC_AF1复用功能STM32L152XX拥有以下特性•两个GPIO端口可配置为唤醒源WKUP1和WKUP3•一个GPIO端口可配置为唤醒源WKUP2,可用于检测篡改、时间戳事件,输出RTC AFO_ALARM、AFO_CALIBRTC_AF1端口(PC13)可配置为以下功能:•唤醒源(WKUP2):配置PWR_CSR寄存器中的EWUP2位•RTC AFO_ALARM输出:根据RTC_CR寄存器中的OSEL[1:0]输出可配置为:RTC Alarm A、 RTC Alarm B、RTC Wakeup •RTC AFO_CALIB输出:配置RTC_CR寄存器中的COE[23]位•RTC AFI_TAMPER1 :篡改事件检测•时间戳事件检测12. 初始化GPIO端口例子[cpp]view plaincopy1.void Init_GPIOS(void){2.GPIO_InitTypeDef GPIO_InitStructure; //定义初始化结构体3.RCC_AHBPeriphClockCmd(RCC_AHBPeriph_GPIOB,ENABLE); //使能对应AHB总线时钟4.5.GPIO_InitStructure.GPIO_Pin = GPIO_Pin_6 | GPIO_Pin_7; //根据需求配置GPIO工作模式6.GPIO_InitStructure.GPIO_Mode = GPIO_Mode_OUT;7.GPIO_InitStructure.GPIO_OType = GPIO_OType_PP;8.GPIO_InitStructure.GPIO_Speed = GPIO_Speed_40MHz;9.GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_UP;10.GPIO_Init(GPIOB, &GPIO_InitStructure); //初始化GPIO端口11.}。

【6-05】Stm32寄存器--Com Interface

15位(BIDIMODE--BIDIrectional data MODE enable): 双向数据模式使能。定义:0(双线双向模式),1(单线双向模式)。 14位(BIDIOE--Output Enable in BIDIrectional mode):双向模式下的输出使能。和BIDIMODE位一起决定在“单线双向”模式下数据的传输方向。 定义:0(输出禁止(只收模式)),1(输出使能(只发模式))。这个“单线”数据线在主设备端为MOSI引脚,在从设备端为MISO引脚。 13位(CRCEN--Hardware CRC calculation ENable):硬件CRC校验使能。定义:0(禁止CRC计算),1(启动CRC计算)。 注:只有在禁止SPI时(SPE=0),才能写该位,否则出错。该位只能在全双工模式下使用。 12位(CRCNEXT--CRC transfer NEXT): 下一个发送CRC。定义:0(下一个发送的值来自发送缓冲区),1(下一个发送的值来自发送CRC寄存器)。 注:在SPI_DR寄存器写入最后一个数据后应马上设置该位。 11位(DFF--Data frame format): 数据帧格式。定义:0(使用8位数据帧格式进行发送/接收),1(使用16位数据帧)。 注:只有当SPI禁止(SPE=0)时,才能写该位,否则出错。

6位(OVR--Overrun flag): 溢出标志。如果前一个接收到的数据还没有读出,又接收到新的数据,即产生上溢,该标志位置1,如果SPI_CR2的ERRIE位为1,则产生中 指示发生了错误。 这时,接收缓存的内容,不会刷新为从发送端送来的新数据。对寄存器SPI_DR的读操作返回最后一个正确接收到的数据。其他所有在上溢发生后由发送 设备发出的16位数据都会丢失。通过先读SPI_SR再读SPI_DR,来清除该标志位。 定义:0(没有出现溢出错误),1(出现溢出错误)。 5位(MODF--Mode fault): 主模式错误。主模式故障仅发生在:在片选引脚硬件模式管理下,主设备的NSS脚被拉低;或者在片选引脚软件模式管理下,SSI位被复位 时;MODF 位被自动置位。清除MODF 位:当MODF 位被置位时,执行一次对SPI_SR的读或写操作 ,然后写SPI_CR1。 定义:0(没有出现模式错误),1(出现模式错误),该位由硬件置位,由软件序列复位。关于软件序列的详细信息,参考22.3.8节。

STM32中用到的- Cortex M3寄存器说明

vu32 VTOR;

vu32 AIRCR;

vu32 SCR;

vu32 CCR;

vu32 SHPR[3];

vu32 SHCSR;

vu32 CFSR;

vu32 HFSR;

vu32 DFSR;

vu32 MMFAR;

vu32 BFAR;

一、NVIC寄存器组

STM32的固件库中有如下定义:

typedef struct

{

vu32 ISER[2];

u32 RESERVED0[30];

vu32 ICER[2];

u32 RSERVED1[30];

vu32 ISPR[2];

u32 RESERVED2[30];

IABR = ACTIVE寄存器族(Interrupt Active Bit Register)

IPR = 中断优先级寄存器阵列(Interrupt Priority Registers)

二、系统控制寄存器组

STM32的固件库中有如下定义:

typedef struct

{

vuc32 CPUID;

CCR = 配置与控制寄存器 (Configuration Control Register)

SHPR = 系统异常优先级寄存器(System Handlers Priority Register)

SHCSR = 系统Handler控制及状态寄存器(System Handler Control and State Register)

STM32中用到的Cortex-M3寄存器说明

在STM32中用到了Cortex-M3定义的三组寄存器,有关这三组寄存器的说明不在STM32的技术手册中,需要参考ARM公司发布的Cortex-M3 Technical Reference Manual (r2p0)。

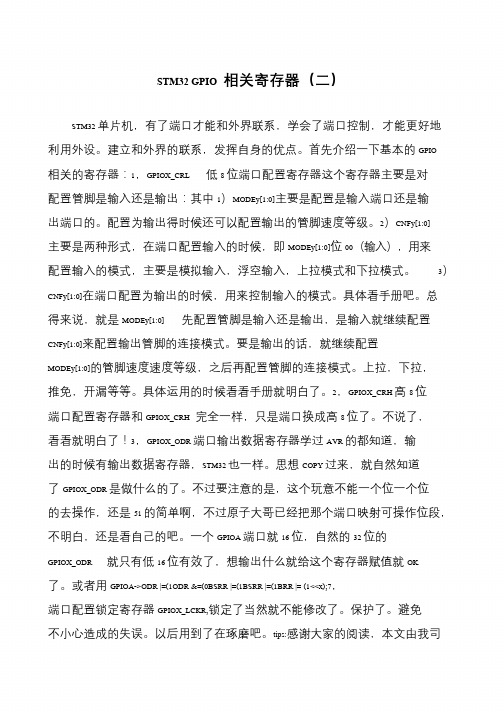

STM32 GPIO 相关寄存器(二)

STM32 GPIO 相关寄存器(二)STM32 单片机,有了端口才能和外界联系,学会了端口控制,才能更好地利用外设。

建立和外界的联系,发挥自身的优点。

首先介绍一下基本的GPIO相关的寄存器:1,GPIOX_CRL 低8 位端口配置寄存器这个寄存器主要是对配置管脚是输入还是输出:其中1)MODEy[1:0]主要是配置是输入端口还是输出端口的。

配置为输出得时候还可以配置输出的管脚速度等级。

2)CNFy[1:0]主要是两种形式,在端口配置输入的时候,即MODEy[1:0]位00(输入),用来配置输入的模式,主要是模拟输入,浮空输入,上拉模式和下拉模式。

3)CNFy[1:0]在端口配置为输出的时候,用来控制输入的模式。

具体看手册吧。

总得来说,就是MODEy[1:0] 先配置管脚是输入还是输出,是输入就继续配置CNFy[1:0]来配置输出管脚的连接模式。

要是输出的话,就继续配置MODEy[1:0]的管脚速度速度等级,之后再配置管脚的连接模式。

上拉,下拉,推免,开漏等等。

具体运用的时候看看手册就明白了。

2,GPIOX_CRH 高8 位端口配置寄存器和GPIOX_CRH 完全一样,只是端口换成高8 位了。

不说了,看看就明白了!3,GPIOX_ODR 端口输出数据寄存器学过AVR 的都知道,输出的时候有输出数据寄存器,STM32 也一样。

思想COPY 过来,就自然知道了GPIOX_ODR 是做什么的了。

不过要注意的是,这个玩意不能一个位一个位的去操作,还是51 的简单啊,不过原子大哥已经把那个端口映射可操作位段,不明白,还是看自己的吧。

一个GPIOA 端口就16 位,自然的32 位的GPIOX_ODR 就只有低16 位有效了,想输出什么就给这个寄存器赋值就OK 了。

或者用GPIOA->ODR |=(1ODR &=(0BSRR |=(1BSRR |=(1BRR |= (1<<x);7,端口配置锁定寄存器GPIOX_LCKR,锁定了当然就不能修改了。

STM32学习笔记(寄存器版本)

27

26

25

24

CNF7[1:0]

MODE7[1:0]

CNF6[1:0]

MODE6[1:0]

23

22

21

20

19

18

17

16

CNF5[1:0]

MODE5[1:0]

CNF4[1:0]

MODE4[1:0]

15

14

13

12

11

10

9

8

CNF3[1:0]

MODE3[1:0]

CNF2[1:0]

MODE2[1:0]

31

30

保留

23

22

USBRST I2C2RST

15

14

SPI3RST SPI2RST

7

6

保留

29

28

27

26

25

24

DACRST PWRRST BKPRST 保留

CANRST 保留

21

20

19

18

17

16

I2C1RST UART5RST UART4RST UART3RST UART2RST 保留

口 2 复位 ,其余串口复位操作以此类推。

(3)串口波特率设置

15

14

13

12

11

10

9

8

DIV_Mantissa[11:4]

7

6

5

4

3

2

1

0

DIV_Mantissa[3:0]

DIV_Fraction[3:0]

USART_BRR(波特比率寄存器)

该寄存器的 15-4 位:DIV_Mantissa[11:0]USARTDIV 的整数部分,这 12 位定义了

【6-02】Stm32寄存器--Clock and Timer

WDGTB[1:0]

提前唤醒中断使能。若置1,则当计数器值达到40h,即产生中断。此中断只能由硬件在复位后清除。

8-7位(WDGTB[1:0]--WatchDoG Timer Base): WWDG时基。预分频器的时基可以设置如下: ★00(CK计时器时钟(PCLK1/4096)除以1) ★01(/2) ★10(/4) ★11(/8)

WWDG (Window WatchDoG 窗口看门狗 寄存器)

WWDG_CR/CFR/SR--3

【1】 【2】 【3】 CR CFR SR

Control Register 控制寄存器 配置寄存器 ConFiguration Register Status Register

状态寄存器

1 31 30 29 28 27 26

WWDG_CR(控制寄存器) Address offset: 0x00 Reset value: 0x7F 25 24 保留 15 14 13 12 保留 11 10 9 8 7 WDGA 6 5 4 3 T[6:0] 2 1 23 22 21 20 19 18 17

7位(WDGA--WatchDoG Activation): 看门狗激活。仅能 软件置1,硬件复位清0。定义:0(禁止),1(启用)。当WDGA=1时,看门狗可以产生复位。

16

0

器值。每个PCLK1

制器使能

16

0

变)。

16

0 EWIF

6-0位(T[6:0]): 7位计数值。存储看门狗的计数器值(向下)。计数窗口取值:从0x7F-0x40(计数过程中,变化)。这些位用来存储看门狗的计数器值。每个PCL 周期(4096x2^WDGTB) 减1 。当计数器值从40h 变为3Fh 时(T6 被清0) ,产生看门狗复位。【T6相当于标志位】 WWDG时钟PCLK1由RCC时钟控制器使能 2 31 30 29 28 27 26 WWDG_CFR(配置寄存器) Address offset: 0x04 Reset value: 0x7F 25 24 保留 15 14 13 保留 9位(EWI--Early Wakeup Interrupt enable): 12 11 10 9 EWI 8 7 6 5 4 3 W[6:0] 2 1 23 22 21 20 19 18 17

stm32f103寄存器整理

313029282726252423222120191817161514131211109876543210DBP PVDE CSBF CWUF PDDS LPDS 313029282726252423222120191817161514131211109876543210EWUP PVDO SBF WUF 151413121110987654321015-0位:备份数据由用户来写数据。

注:BKP——DRx寄存器不会被系统复位,电源复位,待机唤醒所复位 它可以由备份域复位来复位或(如果入侵检测引脚TAMPER功能被开启时)由浸入引脚事件复位BKP BKP__RTCCR RTCCR((RTC RTC时钟校准寄存器时钟校准寄存器时钟校准寄存器))0位:WUF唤醒标志(该位由硬件设置,并只能由POR/PDR(上电/掉电复位)或设置电源控制寄存器(PWR_CR)的CWUF位清除) 定义:0(没有唤醒事件),1(在WKUP引脚上发生唤醒事件或出现RTC脑中事件) 注:当WKUP引脚已经是高电平时,在(通过设置EWUP位)使能WKUP引脚时,会检测到一个额外事件BKP——DRx BKP——DRx((x =1......101010)()()(备份数据寄存器备份数据寄存器备份数据寄存器)) 注:复位时清除这一位2位:PVDO-PVD输出(当PVD被PVDE位使能后该位才有效)定义:0(VDD/VDDA高于PLS[2-0]选定的PVD阀值),1(VDD/VDDA低于PLS[2-0]选定的PVD阀值) 注:在待机模式下PVD被停止,因此,待机模式后或复位后,直到设置PVDE位之前,该位为01位:SBF待机标志位(该位由硬件设置,并只能由POR/PDR(上电/掉电复位)或设置电源控制寄存器(PWR_CR)的CSBUF位清除)定义:0(不在待机)1(已待机)3位:CSBF清除待机位(始终输出为0)定义:0(无功效),1(清除SBF待机位(写)2位:CWUF清除唤醒位(始终输出为0)定义:0(无功效),1(2个系统时钟周期后清除WUF唤醒位(写)1位:PDDS掉电深睡眠(与LPDS位协同操作)定义:0(当CPU进入深睡眠时进入停机模式,调压器状态由LPDS位控制),1(CPU进入深睡眠时进入待机模式)8位:EWUP使能WKUP引脚。

【6-06】Stm32寄存器--ADC and DAC

4位(STRT--Regular channel Start flag):规则通道开始(硬件在开始转换时置位,软件清0)。定义:0(规则通道未开始转换),1(规则通道已开始转换) 3位(JSTRT--Injected channel Start flag):注入通道开始(硬件在开始转换时置位,软件清0)。定义:0(规则通道未开始转换),1(规则通道已开始转换) 2位(JEOC--Injected channel End of Conversion):注入通道转换结束(硬件在所有注入通道转换结束时设置,由软件清0)。 定义:0(转换未完成),1(转换完成) 1位(EOC--End of Conversion):转换结束。(该位由硬件在(规则或注入)通道组转换结束时设置,由软件清除或由读取ADC_DR时清除。 定义:0(转换未完成),1(转换完成) 0位(AWD--Analog watchdog flag):模拟看门狗标志,该位在硬件转换的电压值超出了ADC_LTR和ADC_HTR寄存器定义的范围时置位,由软件清0。 定义:0(没事件),1(有事件)

23位(TSVREFE--Temperature Sensor and V REFINT Enable): 温度传感器和V refint使能(手动)。在多余1个ADC的器件中该位仅出现在ADC1中。 定义:0(禁止),1(开启)。【注】Vrefint :Internal Reference Voltage = 内部参考电压。 22位(SWSTART--SoftWare Start conversion of regular channels): 开始转换规则通道。(软件启动该位,转换后硬件马上清除此位) 如果在EXTSEL[2:0]位中选择了SWSTART为触发事件,该位用于启动一组规则通道的转换。定义:0(复位状态),1(开始转换规则通道)

STM32串口寄存器

当RXNE仍然是’1’的时候,当前被接收在移位寄存器中的数据,需要传送至RDR寄存器时,硬 件将该位置位。如果USART_CR1中的RXNEIE为’1’的话,则产生中断。由软件序列将其清零 (先读USART_SR,然后读USART_CR)。

0:没有过载错误;

1:检测到过载错误。

注意:该位被置位时,RDR寄存器中的值不会丢失,但是移位寄存器中的数据会被覆盖。如果 设置了EIE位,在多缓冲器通信模式下,ORE标志置位会产生中断的。

TXEIE:发送缓冲区空中断使能 (TXE interrupt enable) 该位由软件设置或清除。 0:禁止产生中断; 1:当USART_SR中的TXE为’1’时,产生USART中断。

TCIE:发送完成中断使能 (Transmission complete interrupt enable) 该位由软件设置或清除。 0:禁止产生中断; 1:当USART_SR中的TC为’1’时,产生USART中断。

位2

NE: 噪声错误标志 (Noise error flag)

在接收到的帧检测到噪音时,由硬件对该位置位。由软件序列对其清玲(先读USART_SR,再 读USART_DR)。

0:没有检测到噪声;

1:检测到噪声。

注意:该位不会产生中断,因为它和RXNE一起出现,硬件会在设置RXNE标志时产生中断。 在多缓冲区通信模式下,如果设置了EIE位,则设置NE标志时会产生中断。

位12

位11

12 11 10 M WAKE PCE rw rw rw

9

8

7

6

5

4

3

PS

PEIE TXEIE TCIE

RXNE IE

IDLE IE

TE

stm32F103寄存器整理介绍

Stm32之寄存器列表

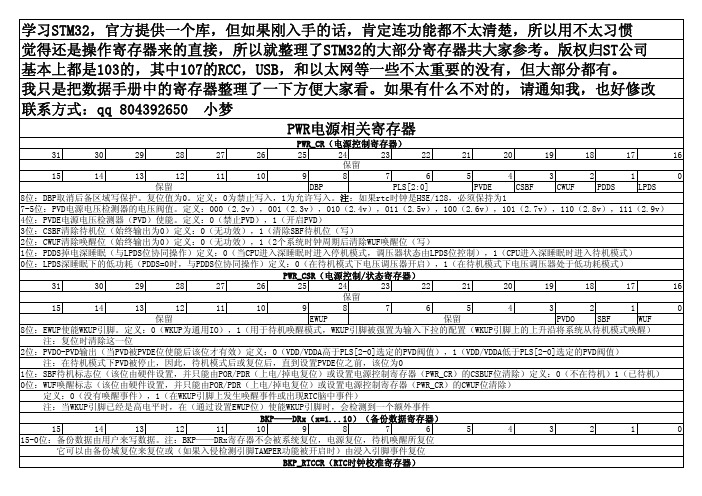

313029282726252423222120191817161514131211109876543210DBP PVDE CSBF CWUF PDDS LPDS313029282726252423222120191817161514131211109876543210EWUP PVDO SBF WUF151413121110987654321学习STM32,官方提供一个库,但如果刚入手的话,肯定连功能都不太清楚,所以用不太习惯觉得还是操作寄存器来的直接,所以就整理了STM32的大部分寄存器共大家参考。

版权归ST公司基本上都是103的,其中107的RCC,USB,和以太网等一些不太重要的没有,但大部分都有。

我只是把数据手册中的寄存器整理了一下方便大家看。

如果有什么不对的,请通知我,也好修改联系方式:qq 804392650 小梦PWR电源相关寄存器PWR_CR(电源控制寄存器)保留保留PLS[2:0]8位:DBP取消后备区域写保护。

复位值为0。

定义:0为禁止写入,1为允许写入。

注:如果rtc时钟是HSE/128,必须保持为17-5位:PVD电源电压检测器的电压阀值。

定义:000(2.2v),001(2.3v),010(2.4v),011(2.5v),100(2.6v),101(2.7v),110(2.8v),111(2.9v)4位:PVDE电源电压检测器(PVD)使能。

定义:0(禁止PVD),1(开启PVD)3位:CSBF清除待机位(始终输出为0)定义:0(无功效),1(清除SBF待机位(写)2位:CWUF清除唤醒位(始终输出为0)定义:0(无功效),1(2个系统时钟周期后清除WUF唤醒位(写)1位:PDDS掉电深睡眠(与LPDS位协同操作)定义:0(当CPU进入深睡眠时进入停机模式,调压器状态由LPDS位控制),1(CPU进入深睡眠时进入待机模式)0位:LPDS深睡眠下的低功耗(PDDS=0时,与PDDS位协同操作)定义:0(在待机模式下电压调压器开启),1(在待机模式下电压调压器处于低功耗模式)PWR_CSR(电源控制/状态寄存器)保留保留保留8位:EWUP使能WKUP引脚。

STM32手册中找不到的寄存器说明

STM32手册中找不到的寄存器说明在STM32中用到了Cortex-M3定义的三组寄存器,有关这三组寄存器的说明不在STM32的技术手册中,需要参考ARM公司发布的Cortex-M3 Technical Reference Manual (r2p0)。

在STM32的固件库中定义了三个结构体与这三个寄存器组相对应,这三个结构体与ARM手册中寄存器的对应关系如下:一、NVIC寄存器组STM32的固件库中有如下定义:typedef struct{vu32 ISER[2];u32 RESERVED0[30];vu32 ICER[2];u32 RSERVED1[30];vu32 ISPR[2];u32 RESERVED2[30];vu32 ICPR[2];u32 RESERVED3[30];vu32 IABR[2];u32 RESERVED4[62];vu32 IPR[11];} NVIC_TypeDef;它们对应ARM手册中的名称为ISER = Interrupt Set-Enable RegistersICER = Interrupt Clear-Enable RegistersISPR = Interrupt Set-Pending RegisterICPR = Interrupt Clear-Pending RegisterIABR = Active Bit RegisterIPR = Interrupt Priority Registers每个寄存器有240位,以Interrupt Set-Enable Registers说明,ISER[0]对应中断源0~31,ISER[1]对应中断源32~63,STM32只有60个中断源,所以没有ISER[2:7]。

参考STM32技术参考手册中的中断向量表,中断源的位置为:位置0 - WWDG = Window Watchdog interrupt位置1 - PVD = PVD through EXTI Line detection interrupt位置2 - TAMPER = Tamper interrupt......位置58 - DMA2_Channel3 = DMA2 Channel3 global interrupt位置59 - DMA2_Channel4_5 = DMA2 Channel4 and DMA2 Channel5 global interrupts二、系统控制寄存器组STM32的固件库中有如下定义:typedef struct{vuc32 CPUID;vu32 ICSR;vu32 VTOR;vu32 AIRCR;vu32 SCR;vu32 CCR;vu32 SHPR[3];vu32 SHCSR;vu32 CFSR;vu32 HFSR;vu32 DFSR;vu32 MMFAR;vu32 BFAR;vu32 AFSR;} SCB_TypeDef; /* System Control Block Structure */它们对应ARM手册中的名称为CPUID = CPUID Base RegisterICSR = Interrupt Control State RegisterVTOR = Vector Table Offset RegisterAIRCR = Application Interrupt/Reset Control Register SCR = System Control RegisterCCR = Configuration Control RegisterSHPR = System Handlers Priority RegisterSHCSR = System Handler Control and State Register CFSR = Configurable Fault Status RegistersHFSR = Hard Fault Status RegisterDFSR = Debug Fault Status RegisterMMFAR = Mem Manage Address RegisterBFAR = Bus Fault Address RegisterAFSR = Auxiliary Fault Status Register三、系统时钟寄存器组STM32的固件库中有如下定义:typedef struct{vu32 CTRL;vu32 LOAD;vu32 VAL;vuc32 CALIB;} SysTick_TypeDef;它们对应ARM手册中的名称为CTRL = SysTick Control and Status Register LOAD = SysTick Reload Value Register VAL = SysTick Current Value Register CALIB = SysTick Calibration Value Register。

STM32_NVIC寄存器详解

在 MDK 内,与 NVIC 相关的寄存器,MDK 为其定义了如下的结构体: typedef struct { vu32 ISER[2]; //2 个 32 位中断使能寄存器分别对应到 60 个可屏蔽中断 u32 RESERVED0[30]; // vu32 ICER[2]; //2 个 32 位中断除能寄存器分别对应到 60 个可屏蔽中断 u32 RSERVED1[30]; vu32 ISPR[2]; //2 个 32 位中断挂起寄存器分别对应到 60 个可屏蔽中断, 可挂起正在执行的中断 u32 RESERVED2[30]; vu32 ICPR[2]; //2 个 32 位中断解挂寄存器分别对应到 60 个可屏蔽中断, 可解除被挂起的中断 u32 RESERVED3[30]; vu32 IABR[2]; //2 个 32 位中断激活标志寄存器, 可读取该寄存器判断当 前执行的中断是哪个,中断执行完硬件清零,只读 u32 RESERVED4[62]; vu32 IPR[15]; //15 个 32 位中断优先级分组寄存器,每个中断分配 8 个 bit,对应到 4*15=60 个中断 } NVIC_TypeDef;ISER0:使能寄存器 0,写 1 使能orICER1:使能寄存器 1,写 1 使能 ISPR1:挂起寄存器 1, 写 1 挂起orICER1:除 ICPR1:解挂ICER0:除能寄存器 0,写 1 除能 ISPR0:挂起寄存器 0,写 1 挂起or能寄存器 1,写 1 除能 or寄存器 1,写 1 解挂ICPR0:解挂寄存器 0,写 1 解挂 IABR0:中断激活标志寄存器 0寄 存 器 位 0 1 对应可屏蔽中断 描述 寄 存 器 位 0 1IABR1:中断激活标志寄存器 0对应可屏蔽中断描述WWDG PVD2 3 4 5TAMPER RTC FLASH RCC6EXTI0窗看门狗 连到 EXTI 的 电源电压检 测(PVD) 中 断 侵入检测中 断 实时时钟全 局中断 闪存全局中 断 Reset and Clock Control 中断 EXTI 线 0 中IIC1_ER IIC2_EVIIC1 错误中断 IIC2 事件中断2 3 4 5IIC2_ER SPI1 SPI2 USART1IIC2 错误中断 SPI1 全局中断 SPI2 全局中断 USART1 全局中断6USART2USART2 全局中断7 8 9 10 11 12 13 14 15 16 17 18EXTI1 EXTI2 EXTI3 EXTI4 DMA1_channel1 DMA1_channel2 DMA1_channel3 DMA1_channel4 DMA1_channel5 DMA1_channel6 DMA1_channel7 ADC1/219USB_HIGH/CAN_TX20USB_LP/CAN_RX021 22 23 24 25 26 27 28CAN_RX1 CAN_SCE EXTI[9:5] TIM1_Break TIM1_Update TIM1_Trg/Com TIM1_CC TIM2断 EXTI 线 1 中 断 EXTI 线 2 中 断 EXTI 线 3 中 断 EXTI 线 4 中 断 DMA1 通道 1 全局中断 DMA1 通道 2 全局中断 DMA1 通道 3 全局中断 DMA1 通道 4 全局中断 DMA1 通道 5 全局中断 DMA1 通道 6 全局中断 DMA1 通道 7 全局中断 ADC1 和 ADC2 全局中 断 USB 高优先 级或 CAN 发 送中断 USB 低优先 级或 CAN 接 收 0 中断 CAN 接收 1 中断 CAN SCE 中 断 EXTI 线[9:5] 中断 TIM1 刹车中 断 TIM1 更新中 断 TIM1 触发和 通信中断 TIM1 捕获比 较中断 定时器 2 全局 中断7 8 9 10 11 12 13 14 15 16 17 18USART3 EXTI[10:15] RTC_Alarm USB_WakeUp Tim8_Break Tim8_Update Tim8_Trg/Com Tim8_CC Adc3 Fsmc Sdio Tim5USART3 全局中断 EXTI[10:15]中断 连接到 EXTI 的闹钟中断 连接到 EXTI 的 USB 待机唤醒 中断 定时器 8 刹车中断 定时器 8 更新中断 定时器 8 触发和通信中断 定时器 8 捕获比较捉弄中断 ADC3 全局中断 FSMC 全局中断 SDIO 全局中断 定时器 5 全局中断19Spi3SPI3 全局中断20Uart4Uart4 全局中断21 22 23 24 25 26 27 28Uart5 Tim6 Tim7 Dma2_Channel1 Dma2_Channel2 Dma2_Channel3 Dma2_Channel4/5 /Uart5 全局中断 定时器 6 全局中断 定时器 7 全局中断 DMA2 通道 1 全局中断 DMA2 通道 2 全局中断 DMA2 通道 3 全局中断 DMA2 通道和通道 5 全局中断 /29 30 31TIM3 TIM4 IIC1_EV定时器 3 全局 中断 定时器 4 全局 中断 IIC1 事件中 断29 30 31/ / // / /IPR[15] 15 个 32 位中断优先级分组寄存器,每个中断分配 8 个 bit,对应到 4*15=60 个中断。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

USGFAULTENA BUSFAULTENA MEMFAULTENA SVCALLPENDED

R/W R/W R/W R/W

0 0 0 0 R/W R/W R/W

Usage fault handler enable Bus fault handler enable Memory management fault enable SVC pended; SVCall was started but was replaced by a higher-priority exception 0 0 0 Bus fault pended; bus fault handler was started but was replaced by a higher-priority exception Memory management fault pended; memory management fault started but was replaced by a higher-priority exception Usage fault pended; usage fault started but was replaced by a higher-priority exception

5 31 30 29 28 27

NVIC_IABR 0/1(中断激活标志寄存器0/1)

26 25 24 23 22 21 20 19 18 17

IABR[31:16] 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

IABR[15:0]

IABR0/1[31:0]: 中断激活标志位。只读。如果为1,表示中断正在执行。 读 该寄存器可以知道当前正在执行的是哪一个中断,当中断执行完毕后,对应位自动硬件清0,

3 31 30 29 28 27 26

NVIC_ISPR 0/1(中断挂起寄存器0/1)

25 24 23 22 21 20 19 18 17

ISPR[31:16] 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

ISPR[15:0] ISPR0/1[31:0]:中断挂起位。对应ISER各位,当CPU响应其他中断时,对应中断被挂起。 定义:写1有效,写0无效。

4 31 30 29 28 27

NVIC_ICPR 0/1(中断挂起清除寄存器0/1)

26 25 24 23 22 21 20 19 18 17

ICPR[31:16] 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

ICPR[15:0] ICPR0/1[31:0]: 中断挂起清除位。对应ISPR各位,当写1的时候,被挂起的中断恢复回断点继续执行下面程序。定义:写1有效,写0无效。

IPRx+y[7:0],x=0-14,y=0-3: 中断优先级设置字。编号0-14个寄存器可为15*4=60个中断设置优先级。 每个可屏蔽中断占用8bits。每个字只用高4位进行设置优先级级别,而且4bits又可按规则来分出抢占优先级(在前)和响应优先级(在后)的所占的位数。 其各自位数由SCB->AIRC来决定:STM32把60个中断分为5组,为组0~4。分组的设置由AIRC的bit10~8 来决定,定义如下: 【组】 【AIRC[10:8]】 【IPRx+y[7:4]的分配情况】 【分配结果】 【备注】 0 组号与AIRC 111 0:4 0位抢占优先级,4位响应优先级 1 值是取反关 110 1:3 1位抢占优先级,3位响应优先级 2 系:优先级 101 2:2 2位抢占优先级,2位响应优先级(抢到某级别<人为设置>,然后按响应级别顺序响应) 3 组配置函数 100 3:1 3位抢占优先级,1位响应优先级(2^3=8级抢占级,2^1=2级响应级别) 有用 4 011 4:0 4位抢占优先级,0位响应优先级(级别值越小,响应级别越高) 说明:1.抢占级别不同:高的可以打断低的; 2.抢占级别相同,但响应级别不同:响应级别高的不可以打断响应级别低的中断。 3.抢占优先级和响应级都相同的中断:看谁先发生,就先响应谁。

2 31 30 29 28 27 26

NVIC_ICER 0/1(中断清除寄存器0/1)

25 24 23 22 21 20 19 18 17

ICER[31:16] 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

ICER[15:0]

ICER0/1[31:0]:中断清除位。与ISER配对使用(二者各个位一一对应)。定义:写1有效,写0无效。 作用:由于ISER各位不能写0,所以要设置ICER对应位来对ISER进行管理。

BUSFAULTPENDED MEMFAULTPENDED USGFAULTPENDED

11 10 8 7 3 1 0

SYSTICKACT PENDSVACT MONITORACT SVCALLACT USGFAULTACT BUSFAULTACT MEMFAULTACT

R/W R/W R/W 0 R/W R/W R/W R/W 0 0

6 31 30 29 28 27

NVIC_IPR 0-14 (中断优先级控制寄存器组)

26 保留 IPRx+3[7:0] 15 14 13 12 11 10 保留 IPRx+1[7:0] IPRx+0[7:0] 9 8 7 6 5 IPRx+2[7:0] 4 3 2 保留 1 25 24 23 22 21 20 19 18 保留 17

NVIC (嵌套向量中断控制 相关寄存器)

NVIC_ISER[0/1]/ICER[0/1]/ISPR[0/1]/ICPR[0/1]/IABR[0/1]/IPR[0-14]--6 NVIC: Nested Vectored Interrupt Control 嵌套向量中断控制寄存器 ★ISER 0/1: Interrupt Set Enable Register 0/1 中断使能寄存器0/1 ★ICER 0/1: Interrupt Clear Enable Register 0/1 中断清除寄存器0/1 ★ISPR 0/1: Interrupt Set Pending Register 0/1 中断挂起寄存器0/1 ★ICPR 0/1: Interrupt Clear Pending Enable Register 0/1 中断挂起清除寄存器0/1 ★IABR 0/1: Interrupt Active Bit Register 0/1 中断 激活标志位 寄存器 ★IPR 0-14: Interrupt Priority Register 0-14 中断优先级寄存器 NVIC的寄存器特性:只能写1,写0无效

28 27 26 25 24 23 22 21 20 19 18 17

VECTKEY[31:16] 15 ENDIANESS 14 13 保留 12 11 10 9 PRIGROUP[3:0] 8 7 6 5 保留 4 3 2

SYSRESET REQ

1

VECTCLR ACTIVE

VECTKEY[31:16]: 访问钥匙。当VECTKEY=0x05FA时,才能写该寄存器的其他位(写保护)。读操作,其值为0xFA05。 ENDIANESS:指示端设置。只读。定义:0(小端--低位在前),1(大端--高位在前)。其值由复位确认。 PRIGROUP[3:0]: 优先级分组。可读可写。参看NVIC_IPR。 SYSRESETREQ:请求芯片控制逻辑产生一次复位。只写不读。 VECTCLRACTIVE:清除NonMaskable Interrupt、故障、Maskabble Interrupt的所有状态信息。 通常只在调试时用,或在OS从错误中恢复时用。定义:0(不清除),1(清除) VECTRESET:复位内核(调试逻辑除外),复位不影响内核意外的电路。

SCB_( 寄存器)

24 23 22 21 20 19 18 17

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

16

0

16

0

16

0

16

0

16

0

16

0

占的位数。

)

16

0

VECTRESET

16

0

ception

16

0

0

Read as 1 if SYSTICK exception is active Read as 1 if PendSV exception is active Read as 1 if debug monitor exception is active Read as 1 if SVCall exception is active

1 31 30 29 28 27 26

NVIC_ISER 0/1(中断使能寄存器0/1)

25 24 23 22 21 20 19 18 17

ISER[31:16] 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

ISER[15:0] ISER0/1[31:0]:中断使能位。每位代表某一个中断信号使能标志。而ISER0/1可以提供64个可屏蔽中断信号。 STM32具有60个可屏蔽中断信号: ISER0对应中断向量表的0~31号中断。ISER1对应中断向量表的32~59号中断。 【参看STM32F10x_NVIC.h文档。下同】。这些位写0无效(所以要ISCR配合)。

SCB(System Control Base register 系统控制基本寄存器)

SCB_AIRCR/SHCSR/ICSR/VTOR/SCR/CCR/SHPR0-3/CFSR/HFSR/DFSR/BFAR/MMFAR--12

1 31 30 29

SCB_AIRC(Application Interrupt and Reset Control 应用中断和复位控制寄存器)