电子技术基础(数字部分)译码器74LS138功能验证实验

74LS138部份38译码器部份实验

74LS138部份38译码器部份实验38译码器是通过3条线来达到控制8条线的状态,即2的3次方。

在电路中,起到扩展IO资源用。

74LS138引脚定义:74LS138逻辑表:相关原理:程序运行照片:以下实验通过P1.0,P1.1,P1.2三条数据线通过74LS138译码作一个8路跑马灯实验。

接线方法:1、用4PIN数据排线插入CPU部份的JP44的P1.0-P1.3 口.另一端插入74LS138部份的JP22作为数据输入。

2、用一条8PIN数据排线,连接78LS138的输出口JP25到 8路指示灯的JP32,运行可看到跑马灯。

程序流程图:汇编语言参考程序:org 0000hajmp mainorg 0080h ;;定义P1.0,P1.1,P1.2 分别为AA,BB,CC 以便在程序中描述AA EQU P1.0BB EQU P1.1CC EQU P1.2MAIN:CLR CC ;状态1 A,B,C为000CLR BBCLR AACALL DELAY ;调用延时CLR CC ;状态2 A,B,C 为100 CLR BBSETB AACALL DELAY ;调用延时CLR CC ;状态2 A,B,C 为010 SETB BBCLR AACALL DELAYCLR CCSETB BBSETB AACALL DELAYSETB CCCLR BBCLR AACALL DELAYSETB CCCLR BBSETB AACALL DELAYSETB CCSETB BBCLR AACALL DELAYSETB CCSETB BBSETB AACALL DELAYJMP MAIN ;重新开始DELAY: ;延时子程序MOV R5,#255D3:MOV R2,#255D4: DJNZ R2,D4 DJNZ R5,D3RETEND。

实验三 3-8译码器的功能测试及仿真

实验三3-8译码器功能测试及仿真一、实验目的1、掌握中规模集成3-8译码器的逻辑功能和使用方法。

2、进一步掌握VHDL语言的设计。

二、预习要求复习有关译码器的原理。

三、实验仪器和设备1.数字电子技术实验台1台2.数字万用表1块3.导线若干4.MUX PLUSII软件5.74LS138集成块若干四、实验原理译码器是一个多输入、多输出的组合逻辑电路。

它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。

译码器在数字系统中有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配,存贮器寻址和组合控制信号等。

不同的功能可选用不同种类的译码器。

译码器分为通用译码器和显示译码器两大类。

前者又分为变量译码器和代码变换译码器。

1.变量译码器(又称二进制译码器)用以表示输入变量的状态,如2线-4线、3线-8线和4线-16线译码器。

若有n个输入变量,则有2n个不同的组合状态,就有2n个输出端供其使用。

而每一个输出所代表的函数对应于n个输入变量的最小项。

以3线-8线译码器74LS138为例进行分析,下图(a)、(b)分别为其逻辑图及引脚排列。

其中 A2、A1、A0为地址输入端,0Y~7Y为译码输出端,S1、2S、3S为使能端。

下表为74LS138功能表,当S1=1,2S+3S=0时,器件使能,地址码所指定的输出端有信号(为0)输出,其它所有输出端均无信号(全为1)输出。

当S1=0,2S+3S=X时,或 S1=X,2S+3S=1时,译码器被禁止,所有输出同时为1。

3-8线译码器74LS138逻辑图及引脚排列图74LS138功能表输入输出S12S+3S A2A1A00Y1Y2Y3Y4Y5Y6Y7Y1 0 0 0 0 0 1 1 1 1 1 1 11 0 0 0 1 1 0 1 1 1 1 1 11 0 0 1 0 1 1 0 1 1 1 1 11 0 0 1 1 1 1 1 0 1 1 1 11 0 1 0 0 1 1 1 1 0 1 1 11 0 1 0 1 1 1 1 1 1 0 1 11 0 1 1 0 1 1 1 1 1 1 0 11 0 1 1 1 1 1 1 1 1 1 1 00 ×××× 1 1 1 1 1 1 1 1× 1 ××× 1 1 1 1 1 1 1 1二进制译码器实际上也是负脉冲输出的脉冲分配器。

电子技术基础(数字部分)译码器74LS138功能验证实验

实验二译码器74LS138功能验证实验

实验目的:

验证译码器74LS138功能;掌握74LS138作为数据分配器时的应用。

实验器材:

数字逻辑实验箱一个;数字万用表一个;5V电源一个;导线若干;

(1)验证74LS138的功能:

74LS138为3-8译码器,实验原理图如下图所示:

LED

实验过程:分别在74LS138的A2、A1、A0、E3、/E2和/E1加上高、低不同的电平,用万用表测量出输出Y7-Y0电平,记录下来,验证逻辑关系是否正确

测量结果:

实验结论:当E3输入非高电平时,无论其他输入如何,电路输出都为高电

平,即译码器不处于工作状态;只有当E3输入为高电平,/E2和/E1同时为低电平时,译码器才处于工作状态,输出的低电平有效。

(2)验证74LS138作为数据分配器时的功能(设信号从/E1输入,从/Y5输出)。

电路原理如下:

实验过程如下:先将K1闭合,测量/E1引脚的电平关态和/Y5引脚的电平状态;再将先将K1断开,测量/E1引脚的电平关态和/Y5引脚的电平状态,没量结果如下:

结论: /E1引脚电平关态与/Y5引脚电平状态永远相同,说明接在/E1的信号被分配到/Y5输出。

LED。

实验三3-8译码器的功能测试及仿真

实验三3-8译码器的功能测试及仿真实验三3-8译码器功能测试及仿真⼀、实验⽬的1、掌握中规模集成3-8译码器的逻辑功能和使⽤⽅法。

2、进⼀步掌握VHDL语⾔的设计。

⼆、预习要求复习有关译码器的原理。

三、实验仪器和设备1.数字电⼦技术实验台1台2.数字万⽤表1块3.导线若⼲4.MUX PLUSII软件5.74LS138集成块若⼲四、实验原理译码器是⼀个多输⼊、多输出的组合逻辑电路。

它的作⽤是把给定的代码进⾏“翻译”,变成相应的状态,使输出通道中相应的⼀路有信号输出。

译码器在数字系统中有⼴泛的⽤途,不仅⽤于代码的转换、终端的数字显⽰,还⽤于数据分配,存贮器寻址和组合控制信号等。

不同的功能可选⽤不同种类的译码器。

译码器分为通⽤译码器和显⽰译码器两⼤类。

前者⼜分为变量译码器和代码变换译码器。

1.变量译码器(⼜称⼆进制译码器)⽤以表⽰输⼊变量的状态,如2线-4线、3线-8线和4线-16线译码器。

若有n个输⼊变量,则有2n个不同的组合状态,就有2n个输出端供其使⽤。

⽽每⼀个输出所代表的函数对应于n个输⼊变量的最⼩项。

以3线-8线译码器74LS138为例进⾏分析,下图(a)、(b)分别为其逻辑图及引脚排列。

其中 A2、A1、A0为地址输⼊端,0Y~7Y为译码输出端,S1、2S、3S为使能端。

下表为74LS138功能表,当S1=1,2S+3S=0时,器件使能,地址码所指定的输出端有信号(为0)输出,其它所有输出端均⽆信号(全为1)输出。

当S1=0,2S+3S=X时,或 S1=X,2S+3S=1时,译码器被禁⽌,所有输出同时为1。

3-8线译码器74LS138逻辑图及引脚排列图74LS138功能表输⼊输出S12S+3S A2A1A00Y1Y2Y3Y4Y5Y6Y7Y1 0 0 0 0 0 1 1 1 1 1 1 11 0 0 0 1 1 0 1 1 1 1 1 11 0 0 1 0 1 1 0 1 1 1 1 11 0 0 1 1 1 1 1 0 1 1 1 11 0 1 0 0 1 1 1 1 0 1 1 11 0 1 0 1 1 1 1 1 1 0 1 11 0 1 1 0 1 1 1 1 1 1 0 11 0 1 1 1 1 1 1 1 1 1 1 00 ×××× 1 1 1 1 1 1 1 1× 1 ××× 1 1 1 1 1 1 1 1⼆进制译码器实际上也是负脉冲输出的脉冲分配器。

(完整word版)实验四74HC138译码器实验

实验四 74HC138译码器实验一、实验目的与要求1、掌握74HC138译码器的工作原理,熟悉74HC138译码器的具体运用连接方法,了解74HC138是如何译码的。

2、认真预习本节实验内容,尝试自行编写程序,填写实验报告二、实验内容1、编写程序:使用82C55的PC0、PC1、PC2控制74HC138的数据输入端,通过译码产生8选1个选通信号,轮流点亮8个LED指示灯。

2、运行程序,验证译码的正确性。

1C3区C3区C3B4区:CS、A0、A1——A3区:CS1、A0、A12、调试程序,查看运行结果是否正确。

五、实验程序及流程图。

MODEL TINYCon_8255 EQU0F003H;8255控制口PC_8255 EQU 0F002H;8255 PC口.STACK 100.CODESTART:MOV DX,Con_8255MOV AL,80HOUT DX,AL;8255初始化,PC口作输出用MOV DX,PC_8255MOV AL,0START1:OUT DX,ALCALL DelayINC ALJMP START1Delay PROC NEAR;延时Delay1:XOR CX,CXLOOP $RETDelay ENDPEND START六、实验结果8个LED灯循环亮灭。

七、实验总结74HC138译码器通过将ABC三个口表示的十进制数转换为Y0-Y7显示的二进制数实现译码,并且可与控制端口一起实现对地址的选择。

还可以将74HC138译码器与8255的三个端口连在一起,实现对它的编程控制。

译码器74LS138应用电路

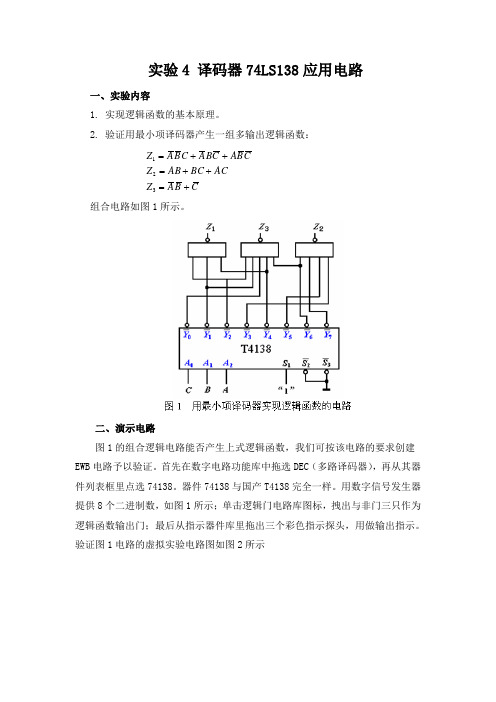

实验4 译码器74LS138应用电路一、实验内容1. 实现逻辑函数的基本原理。

2. 验证用最小项译码器产生一组多输出逻辑函数:C B A Z ACBC AB Z C B A C B A C B A Z +=++=++=321组合电路如图1所示。

二、演示电路图1的组合逻辑电路能否产生上式逻辑函数,我们可按该电路的要求创建EWB 电路予以验证。

首先在数字电路功能库中拖选DEC (多路译码器),再从其器件列表框里点选74138。

器件74138与国产T4138完全一样。

用数字信号发生器提供8个二进制数,如图1所示;单击逻辑门电路库图标,拽出与非门三只作为逻辑函数输出门;最后从指示器件库里拖出三个彩色指示探头,用做输出指示。

验证图1电路的虚拟实验电路图如图2所示图2 验证图1电路的虚拟实验电路图图3 数字信号发生器面板图4 逻辑转换器面板三、验证原理与步骤 1. 原理采用单步运行方式,数字信号发生器逐一输出8个三位二进制数据(000,001,010,011,100,101,110,111),与此同时,如在Z 1、Z 2、Z 3的输出端上为高电平即“1”时,彩色指示探头灯亮。

记录此刻的输入信号,它所对应的最小项就是输出函数表达式中的一项。

对应关系为:C B A m ==0000,C B A m ==1001,C B A m ==2010,BC A m ==3011,C B A m ==4100,C B A m ==5101,C AB m ==6110,ABC m ==7111。

2. 步骤单击数字信号发生器面板上的控制按钮Step ,采用单步运行方式。

观测结果是:接在Z 1输出端上的红灯亮了三次(m 1、m 2、m 4);接在Z 2输出端上的绿灯亮了四次(m 7、m 6、m 3 、m 5);接在Z 3输出端上的蓝灯亮了五次(m 0、m 1、m 4 、m 2、m 6)。

根据以上观测结果,写出输出函数Z 1、Z 2、Z 3的最小项表达式,它们是C AB C B A C B A C B A C B A m m m m m Z CB A BC A C AB ABC m m m m Z CB AC B A C B A m m m Z ++++=++++=+++=+++=++=++=642103765324211 化简后得C B A Z ACBC AB Z C B A C B A C B A Z +=++=++=321于是,验证了图1所示电路。

实验三 3-8译码器的功能测试及仿真

实验三3-8译码器功能测试及仿真一、实验目的1、掌握中规模集成3-8译码器的逻辑功能和使用方法。

2、进一步掌握VHDL语言的设计。

二、预习要求复习有关译码器的原理。

三、实验仪器和设备1.数字电子技术实验台1台2.数字万用表1块3.导线若干4.MUX PLUSII软件5.74LS138集成块若干四、实验原理译码器是一个多输入、多输出的组合逻辑电路。

它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。

译码器在数字系统中有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配,存贮器寻址和组合控制信号等。

不同的功能可选用不同种类的译码器。

译码器分为通用译码器和显示译码器两大类。

前者又分为变量译码器和代码变换译码器。

1.变量译码器(又称二进制译码器)用以表示输入变量的状态,如2线-4线、3线-8线和4线-16线译码器。

若有n个输入变量,则有2n个不同的组合状态,就有2n个输出端供其使用。

而每一个输出所代表的函数对应于n个输入变量的最小项。

以3线-8线译码器74LS138为例进行分析,下图(a)、(b)分别为其逻辑图及引脚排列。

其中 A2、A1、A0为地址输入端,0Y~7Y为译码输出端,S1、2S、3S为使能端。

下表为74LS138功能表,当S1=1,2S+3S=0时,器件使能,地址码所指定的输出端有信号(为0)输出,其它所有输出端均无信号(全为1)输出。

当S1=0,2S+3S=X时,或 S1=X,2S+3S=1时,译码器被禁止,所有输出同时为1。

3-8线译码器74LS138逻辑图及引脚排列图74LS138功能表二进制译码器实际上也是负脉冲输出的脉冲分配器。

若利用使能端中的一个输入端输入数据信息,器件就成为一个数据分配器(又称多路分配器),如图3-2所示。

若在S1输入端输入数据信息,2S=3S=0,地址码所对应的输出是S1数据信息的反码;若从2S端输入数据信息,令S1=1、3S=0,地址码所对应的输出就是2S端数据信息的原码。

实验五 74138译码器(基于FPGA)

实验五 74138译码器(基于FPGA)2014.11.19一、实验目的:1 、了解可编程数字系统设计的流程;2 、掌握Quartus II 9.0软件的使用方法;3 、掌握原理图输入方式设计数字系统的方法和流程;4、熟悉掌握集成译码器74LS138的应用。

二、实验设备:1、计算机:Quartus II 软件2、Altera DE0 多媒体开发平台3、集成电路:74LS138三、实验内容:74LS138译码器逻辑功能的测试:把译码器的输入接到拨码开关,输出端接8个LED灯,通过拨码开关改变输入的逻辑电平变化来观察LED输出情况,验证3线8线译码器的工作状态。

补充内容:a、74LS138 3-8线译码器b、引脚定义:C、74LS138逻辑功能表Quartus II 9.0编辑步骤:1、Creat a New Project(New Project Wizard)2、New Project Wizard:Directory,Name,Top_Level Entity3、New Project Wizard: Add Files4、New Project Wizard: Family & Device settings5、New Project Wizard: EDA Tool Settings6、Add new design file block diagram /schematic file7、Add new vector waveform file8、Input and output setting9、“Assignment”→“Setting10、“Processing”→“Start Simulation”之后进行FPGA芯片的编程与配置,将计算机与Altera DE0 多媒体开发平台通过数据线进行连接,通过拨码开关改变输入的逻辑电平变化来观察LED输出情况,验证3线8线译码器的工作状态。

译码器功能仿真实验【精选】

译码器功能仿真实验1. 仿真实验目的1) 通过仿真实验,熟悉译码器74LS138N 的逻辑功能。

2) 了解译码器74LS138N 的应用。

2. 元器件选取1) 电源:Place Source →POWER_SOURCES →DC_POWER,选取电源并设置电压为5V 。

2) 接地:Place Source →POWER_SOURCES →GROUND,选取电路中的接地。

3) 译码器:Place TTL →74LS,选取74LS138N 。

4) 逻辑探头:Place Indicators →PROBE,选取逻辑探头。

5) 数字信号发生器:从虚拟仪器工具栏调取XWG1。

6) 逻辑分析仪:从虚拟仪器工具栏调取XLA1。

3. 仿真电路图1所示是74LS138N 的仿真电路。

数字信号发生器的设置如图2所示。

图1 74LS138N 的仿真电路图2 数字信号发生器的设置4. 电路原理简述译码器是编码的逆过程。

译码器将输入的二进制代码转换成与代码对应的信号。

译码器输入的是n位二进制代码,则其输出端子数N≤2^n 。

N=2^n称为完全译码,N<2^n称为部分译码。

74LS138N是常用的集成3线-8线译码器。

图3是74LS138N的逻辑功能表。

图3 74LS138N的逻辑功能表5. 仿真分析1)搭建图1所示的74LS138N仿真电路,数字信号发生器按图2所示进行设置。

2)单击仿真开关,激活电路。

双击逻辑分析仪图标,打开其面板,即可显示74LS138N 的时序波形,如图4所示。

其中1、2、3显示的是74LS138N输入信号,4~11显示的是输出信号。

图4 74LS138N 的输入/输出波形3) 观察逻辑分析仪显示的输入/输出的波形,并在表1中填写74LS138N 的真值表。

表1 74LS138N 译码器真值表。

AB C Y0Y1Y2Y3Y4Y5Y6Y7001011111111111定必须”政治规矩,责任。

三、主要党支部为单位开展一谈信念,对照入党誓词找温入党志愿和入党誓词,交心组形式,定期组织集中学习,每月底组织一次党员集中学习。

任务一:测试3线—8线译码器74LS138逻辑功能。

2.1待开发软件的一般描述本软件旨在为图书馆系统管理员来管理图书馆书数目的增加、更新、删除、查询、对读者个人信息的查询、更改、删除;图书管理员可以借阅、归还图书;读者可以借阅、归还、预定图书、对个人信息的查询等。

2.2待开发软件的功能不通过图书馆管理系统密码管理图书查询图书借阅图书预定图书更新读者留言板系统维护身份验证重新验证退出正常退出2.3用户特征用户和访客具有基础计算机使用常识的人,图书管理人员对整个图书系统要有基本了解,并对计算机熟练操作,数据库较为熟练。

2.4运行环境(1)硬件环境客户机:普通pcCPU:P41.8GHz以上内存:256MB以上能够运行IE5.0以上或者Netscape4.0以上版本的机器分辨率:推荐使用1024*768像素Web服务器CPU: P41.0GHz内存:1G以上硬盘:80GB以上网卡:K Mb/s速度数据库服务器CPU: P42.0GHz内存:1GB以上硬盘:80GB以上(2)软件环境操作系统:UNIX/Linux/window2000或以上版本2.5条件与限制考虑到本软件使用的广泛性,在设计时应注意软件的可移植性,能方便地将其移植到手机,平板电脑等硬件平台。

因本软件管理的信息属于个人隐私信息,必须注意信息的安全防范。

同时应以标准的数据格式来实现,以方便数据的共享。

译码器实验报告

译码器实验报告

实验目的:掌握和理解译码器的工作原理和使用方法。

实验器材:

1. 译码器(例如74LS138)

2. 逻辑开关

3. 电源

4. 七段数码显示器

5. 连接线

实验原理:

译码器是一种数字电路,用于将输入的二进制信号转换为对应的输出信号。

译码器常用于将计算机的控制信号转换为具体的操作信号,例如将二进制数码转换为七段数码显示器的控制信号。

实验步骤:

1. 将译码器连接到电源上,确保接线正确。

2. 用逻辑开关设置输入信号。

3. 通过连接线将译码器的输出信号连接到七段数码显示器上。

4. 打开电源,观察七段数码显示器上显示的数字是否与输入信号对应。

5. 可以通过改变逻辑开关的状态来改变输入信号,观察七段数码显示器上显示的数字是否随之改变。

实验结果:

通过逻辑开关设置不同的输入信号,观察到七段数码显示器上

显示的数字与输入信号的对应关系,并且随着输入信号的改变而实时改变。

实验结论:

通过译码器的译码作用,可以将输入的二进制信号转换为对应的输出信号,实现数字信号的转换和显示。

译码器的使用大大简化了数字电路的设计和控制。

实验注意事项:

1. 在连接实验电路的过程中,注意正确接线,避免短路和接反等问题。

2. 实验中应当仔细观察七段数码显示器上的数字是否与输入信号对应,以验证译码器的正常工作。

3. 在实验结束后,应及时关闭电源,避免浪费电力和设备损坏的风险。

数字电路译码器实验报告

数字电路译码器实验报告

实验目的:通过实验,了解数字电路中译码器的原理和使用方法。

实验器材:数字电路实验箱、74LS138译码器、LED灯、开关。

实验原理:数字电路中,译码器是一种将输入信号转化为相应输出信号的电路。

它可将输入信号转换为对应的二进制代码,并输出到多个输出端口上。

通常,译码器用于将一个数字信号转换为另一个数字信号,用于控制逻辑电路的工作。

74LS138译码器是一种通用型译码器,在其中,通过三个输入端口来控制八个输出端口。

每一个输出端口上的输出信号都是一种互不相同的二进制数。

在使用中,只需要通过输入端口向译码器中输入一个信号即可控制相应的输出端口。

实验步骤:

2.按照实验箱的规定,将译码器的输入端口分别接入到开关上。

3.将译码器的输出信号分别接入到LED灯上,以进行输出信号的测试。

4.向开关中输入不同的信号,观察LED灯上的输出变化。

实验结果:通过实验,我们发现译码器在接入开关后能够将输入信号转化为对应的二进制代码,并输出到相应的输出端口上。

通过LED灯的输出,我们可以清晰的看到相应的二进制码,其输出结果与我们所预期的结果相符合。

实验结论:经过实验,我们深刻理解了数字电路中译码器的工作原理和使用方法。

译码器的作用在于将输入信号转化为相应的二进制信号,并使得逻辑电路能够正确的工作。

此次实验为我们深入理解数字电路的原理和应用提供了很好的机会,我们也将从中受益良多。

译码器_实验报告

一、实验目的1. 理解译码器的原理和功能。

2. 掌握译码器的应用和实现方法。

3. 培养动手能力和团队协作精神。

二、实验原理译码器是一种将二进制编码信号转换为特定信号的电路。

在数字系统中,译码器广泛应用于地址译码、数据译码、指令译码等方面。

本实验主要研究译码器的原理、设计和实现。

三、实验设备1. 74LS138译码器芯片;2. 数字实验箱;3. 逻辑电平测试仪;4. 线路板;5. 连接线。

四、实验内容1. 译码器原理分析;2. 译码器设计;3. 译码器电路搭建;4. 译码器功能测试。

五、实验步骤1. 译码器原理分析首先,分析译码器的工作原理。

译码器由编码器、译码电路和输出电路组成。

编码器将输入信号转换为二进制编码信号,译码电路根据编码信号输出对应的信号,输出电路将译码电路输出的信号转换为所需的信号。

2. 译码器设计根据实验要求,设计译码器电路。

本实验采用74LS138译码器芯片,该芯片具有3个输入端和8个输出端。

根据输入信号的不同组合,输出对应的信号。

3. 译码器电路搭建(1)将74LS138译码器芯片插入数字实验箱的相应位置。

(2)根据译码器电路原理图,将输入端和输出端连接到实验箱的相应位置。

(3)检查电路连接是否正确,确保无短路和断路现象。

4. 译码器功能测试(1)将译码器输入端连接到逻辑电平测试仪。

(2)设置输入端信号,观察输出端信号。

(3)验证译码器输出信号是否符合预期。

六、实验结果与分析1. 实验结果实验过程中,根据译码器原理和设计,成功搭建了译码器电路。

在输入端设置不同的信号组合,输出端信号符合预期。

2. 实验分析本实验验证了译码器的原理和功能。

通过实验,我们了解到译码器在数字系统中的应用和实现方法。

在实验过程中,我们学会了如何设计译码器电路,如何搭建电路,以及如何进行功能测试。

七、实验总结1. 通过本次实验,掌握了译码器的原理和功能。

2. 学会了译码器的设计方法和实现过程。

3. 培养了动手能力和团队协作精神。

74ls138功能测试实验报告

74ls138功能测试实验报告实验名称:74LS138功能测试实验实验目的:1.理解74LS138译码器的工作原理;2.学习使用74LS138实现多路选择功能;3.进行74LS138功能测试。

实验器材:1.74LS138译码器芯片;2.74LS00与非门芯片;3.逻辑开关;4.数码管;5.电源供应器;6.连接线。

实验原理:74LS138是一种常用的3-8译码器,它具有3个输入端(A,B,C)和8个输出端(Y0,Y1,Y2,Y3,Y4,Y5,Y6,Y7)。

输入端共有23=8种状态,输出端根据输入端的状态进行译码,只有一个输出为低电平,其他输出为高电平。

实验步骤:1.连接电路:将74LS138芯片与74LS00芯片、逻辑开关、数码管和电源供应器依次连接起来。

2.编写测试程序:根据74LS138的真值表,编写测试程序,使得数码管能正确显示输入端的状态。

3.上电测试:将电源供应器接通电源,观察数码管的显示情况,验证74LS138的功能是否正常。

4.更改输入端状态:随机更改输入端的状态,观察数码管的显示情况,进一步验证74LS138的功能是否正常。

实验结果:经过测试,实验结果如下:输入端(A,B,C)输出端(Y0,Y1,Y2,Y3,Y4,Y5,Y6,Y7)结论:通过实验,验证了74LS138译码器的功能正常,能够根据输入端的状态进行正确的译码,并将对应的输出端置为低电平,其他输出端为高电平。

实验结果与真值表相符。

实验总结:通过本次实验,我深入了解了74LS138译码器的工作原理,并学会了使用74LS138实现多路选择功能。

实验结果表明,74LS138译码器能够正确地译码,并根据输入端的状态进行输出。

这对于数字电路设计和逻辑控制具有重要的意义。

实验过程中,我还学会了编写测试程序,用于验证芯片的功能是否正常。

通过实验,我对数字电路译码器的原理和应用有了更深入的理解,为今后的学习和实践奠定了基础。

译码器实验报告

任务二:用3线—8线译码器74LS138和门电路产生如下多输出逻辑函数

A2 A1 A0

Z1 Z2 Z3

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0 0 1

0 1 1

0 0 0

0 0 0

0 1 0

1 0 0

0 1 0

1 1 1

2.实验方法提示

1)根据设计方法提示把Z1写成用译码器输出 ~ 表示的函数表达式;

2)根据函数表达式画出电路接线图并接好线,其中输入变量A2、A1、A0接至数字电路实验箱的任意3个电平开关的插孔,输出函数Z1、Z2和Z3分别接至数字电路实验箱电平显示器的任意3个LED。

3)自行设计的表格,记录所设计的电路的真值表。

4)通过真值表推出函数表达式,验证所设计电路的正确性。

四、数据处理分析

任务一:测试3线—8线译码器74LS138逻辑功能

表3-23线-8线译码器74LS138功能表

输入

输出

使能

选择

A2 A1 A0

X 1

0 X

1 0

1 0

1 0

1 0

1 0

1 0

1 0

1 0

X X X

X X X

0 0 0

0 0 1

0 1 0

根据实验数据归纳出74LS138芯片的功能。

表3-23线-8线译码器74LS138功能表

输入

输出

使能

选择

A2 A1 A0

X 1

0 X

1 0

1 0

1 0

1 0

1 0

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验二译码器74LS138功能验证实验

实验目的:

验证译码器74LS138功能;掌握74LS138作为数据分配器时的应用。

实验器材:

数字逻辑实验箱一个;数字万用表一个;5V电源一个;导线若干;

(1)验证74LS138的功能:

74LS138为3-8译码器,实验原理图如下图所示:

LED

实验过程:分别在74LS138的A2、A1、A0、E3、/E2和/E1加上高、低不同的电平,用万用表测量出输出Y7-Y0电平,记录下来,验证逻辑关系是否正确

测量结果:

实验结论:当E3输入非高电平时,无论其他输入如何,电路输出都为高电

平,即译码器不处于工作状态;只有当E3输入为高电平,/E2和/E1同时为低电平时,译码器才处于工作状态,输出的低电平有效。

(2)验证74LS138作为数据分配器时的功能(设信号从/E1输入,从/Y5输出)。

电路原理如下:

实验过程如下:先将K1闭合,测量/E1引脚的电平关态和/Y5引脚的电平状态;再将先将K1断开,测量/E1引脚的电平关态和/Y5引脚的电平状态,没量结果如下:

结论: /E1引脚电平关态与/Y5引脚电平状态永远相同,说明接在/E1的信号被分配到/Y5输出。

LED。