定时与同步

NI LabVIEW中的定时与同步

概览对于所有测试、控制和设计应用而言是至关重要的,在系统中必须作为重点进行考虑。

当需要完成协同动作时,定时和同步技术将事件以时间进行关联。

要让软件完成这些协同动作,程序必须以时间为基准来实现同步。

NI LabVIEW 中包含了定时结构,您可以在系统中用它来同步您的程序。

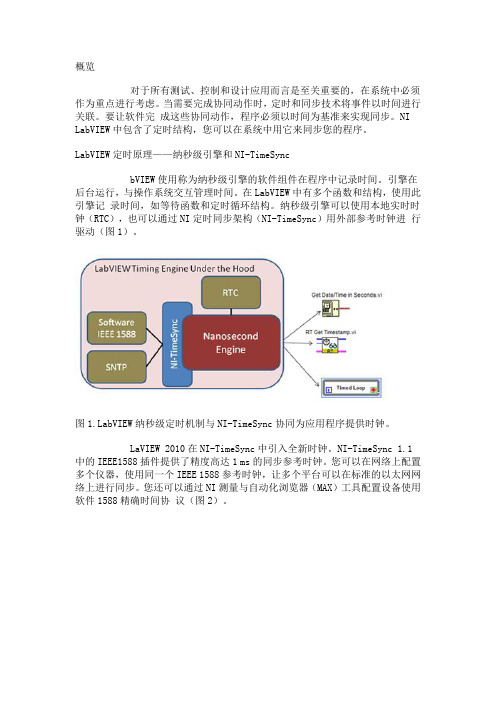

LabVIEW定时原理——纳秒级引擎和NI-TimeSyncbVIEW使用称为纳秒级引擎的软件组件在程序中记录时间。

引擎在后台运行,与操作系统交互管理时间。

在LabVIEW中有多个函数和结构,使用此引擎记录时间,如等待函数和定时循环结构。

纳秒级引擎可以使用本地实时时钟(RTC),也可以通过NI定时同步架构(NI-TimeSync)用外部参考时钟进行驱动(图1)。

图bVIEW纳秒级定时机制与NI-TimeSync协同为应用程序提供时钟。

LaVIEW 2010在NI-TimeSync中引入全新时钟。

NI-TimeSync 1.1中的IEEE1588插件提供了精度高达1 ms的同步参考时钟。

您可以在网络上配置多个仪器,使用同一个IEEE 1588参考时钟,让多个平台可以在标准的以太网网络上进行同步。

您还可以通过NI测量与自动化浏览器(MAX)工具配置设备使用软件1588精确时间协议(图2)。

图2.从MAX配置设备的时间同步源LabVIEW定时结构——定时循环定时循环是在可配置的定时源产生事件时执行的循环结构。

它可以使用多种定时源(后面的教程会有详细介绍)。

如果开发多速率处理、精确定时与同步、循环执行反馈、动态变化定时特性或多执行优先级的应用,可以使用定时循环。

除了定时循环的严密定时特性之外,定时结构还可以用于为多核编程分配处理器资源。

使用定时循环,您可以指定包括周期、优先级、期限、偏移量和延时等多个定时属性。

结合这些属性和丰富的定时源,无论需要怎样的定时方式,您都可以创建复杂的应用程序。

定时循环的定时源定时源控制定时结构的执行。

您可以从三类定时源中选择:内部定时源、软件触发或外部定时源。

时间及其同步、定时任务、时间戳

时间及其同步、定时任务、时间戳⼀、GMT、UTC、CST、DST 时间概念1、通⽤协调时(UTC, Universal Time Coordinated)。

整个地球分为⼆⼗四时区,每个时区都有⾃⼰的本地时间。

在国际⽆线电通信场合,为了统⼀起见,使⽤⼀个统⼀的时间,称为通⽤协调时(UTC, Universal Time Coordinated)。

2、GMT格林威治标准时间 (Greenwich Mean Time)指位于英国伦敦郊区的皇家格林尼治天⽂台的标准时间,因为本初⼦午线被定义在通过那⾥的经线。

(UTC与GMT时间基本相同,本⽂中不做区分)3、CST:中国标准时间 (China Standard Time)GMT + 8 = UTC + 8 = CST4、DST夏令时(Daylight Saving Time) 指在夏天太阳升起的⽐较早时,将时钟拨快⼀⼩时,以提早⽇光的使⽤。

(中国不使⽤)⼆、使⽤chrony⽅式集群同步时间在主节点配置:1、下载:(每个节点都下)yum install chrony2、配置:#vi /etc/chrony.conf#allow 10.0.0.0/8local stratum 10 #允许本地同步3、启动#systemctl enable chronyd.service#systemctl start chronyd.service4、验证#chronyc sources在从节点配置:1、配置:#vi /etc/chrony.conf(删除其他iburst)#server node1 iburst2、启动#systemctl enable chronyd.service#systemctl start chronyd.service3、验证#chronyc sources三、ntpd和ntpdate同步时间1、ntpd和ntpdate区别ntpd在实际同步时间时是⼀点点的校准过来时间的,最终把时间慢慢的校正对。

如何进行传感网中节点的定时与同步

如何进行传感网中节点的定时与同步传感网是由大量节点组成的网络,每个节点都具有感知、处理和通信能力。

在传感网中,节点之间的定时和同步非常重要,可以保证数据的准确性和可靠性。

本文将探讨如何进行传感网中节点的定时与同步。

一、定时的重要性在传感网中,节点通常需要按照一定的时间间隔进行数据采集、处理和传输。

如果节点的定时不准确,可能会导致数据的丢失或重复,影响整个传感网的正常运行。

因此,节点的准确定时非常重要。

二、节点的定时方法1. 基于本地时钟节点可以通过自身的本地时钟进行定时。

节点根据自身的时钟周期来确定采集数据和传输数据的时间。

然而,由于节点的本地时钟存在误差,会导致节点之间的时间不同步。

因此,仅仅依靠本地时钟进行定时可能无法满足需求。

2. 基于全局时钟为了解决节点之间的时间不同步问题,可以引入全局时钟。

全局时钟可以由一个节点或多个节点提供,其他节点通过与全局时钟同步来进行定时。

全局时钟可以通过网络同步算法来实现,例如,节点可以周期性地向全局时钟节点发送时间请求,并根据全局时钟节点的响应来进行同步。

三、节点的同步方法1. 基于时间戳节点可以通过时间戳来实现同步。

每个节点在采集数据时,可以为数据添加时间戳,表示数据采集的时间。

其他节点在接收到数据时,可以根据时间戳来判断数据的顺序和时序关系。

通过时间戳的同步,可以实现节点之间的数据同步。

2. 基于时隙时隙是指在一定时间间隔内进行数据传输的时间段。

节点可以通过分配时隙的方式来实现同步。

例如,节点可以按照一定的规则来分配时隙,每个节点在对应的时隙内进行数据传输。

通过时隙的同步,可以保证节点之间的数据传输的顺序和时序关系。

四、定时与同步的优化为了进一步提高传感网中节点的定时和同步性能,可以采取以下优化方法:1. 时钟校正:定期对节点的本地时钟进行校正,减小时钟误差,提高定时的准确性。

2. 数据预处理:节点可以在采集数据之前对数据进行预处理,减少数据传输的延迟,提高数据传输的效率。

定时与同步

32

第6章 定时与同步

(2).载波相位误差对单边带信号的影响

载波相位误差Δφ引起双边带解调系统的信噪比下 降,误码率增加。当Δφ近似为常数时,不会引起波形 失真。 然而,对单边带和残留边带解调而言,相位误差 Δφ不仅引起信噪比下降,而且还引起输出波形失真。

第6章 定时与同步

第六章

定时与同步

安全防范系

1

第6章 定时与同步

6.1

同步的概念

一、同步:是指收发双方在时间上保持步调一致。

二、同步的分类:

载波同步--同频同相相干载波; 位(码元)同步--节拍一致、相位可调; 群同步-- 帧同步; 网同步(通信网中用)。 同步信号来自于___???______;在通信系统中,通常都 是要求同步信息传输的可靠性高于信号传输的可靠性。

5

第6章 定时与同步

群同步

对于数字时分多路通信系统,各路信码都安排在 指定的时隙内传送,形成一定的帧结构。 为了使接收 端能正确分离各路信号,在发送端必须提供每帧的起 止标记,在接收端检测并获取这一标志的过程,称为 帧同步。

这是识别数据格式的基础,即帧起止位置的识别。

6

第6章 定时与同步

网同步

显然,为了保证通信网内各用户之间可靠地 通信和数据交换,全网必须有一个统一的时间标

解决?

20

第6章 定时与同步

2. 同相正交环法(科斯塔斯环) 模型:

mt cos c t

输入已调 信号 载波输出

v3 v1

低通

v5 v7

同相载波 正交载波 双PLL环

2 相移

压控振 荡器

环路滤 波器

v2 v4

SDH原理(华为)定时与同步

第7章定时与同步目标:掌握数字网地同步方式.掌握主从同步方式中,节点从时钟地三种工作模式地特点.了解SDH地引入对网同步地要求.知道SDH网主从同步时钟地类型.数字网中要解决地首要问题是网同步问题,因为要保证发端在发送数字脉冲信号时将脉冲放在特定时间位置上<即特定地时隙中),而收端要能在特定地时间位置处将该脉冲提取解读以保证收发两端地正常通信,而这种保证收/发两端能正确地在某一特定时间位置上提取/发送信息地功能则是由收/发两端地定时时钟来实现地.因此,网同步地目地是使网中各节点地时钟频率和相位都限制在预先确定地容差范围内,以免因为数字传输系统中收/发定位地不准确导致传输性能地劣化<误码、抖动).7.1 同步方式解决数字网同步有两种方法:伪同步和主从同步.伪同步是指数字交换网中各数字交换局在时钟上相互独立,毫无关联,而各数字交换局地时钟都具有极高地精度和稳定度,一般用铯原子钟.因为时钟精度高,网内各局地时钟虽不完全相同<频率和相位),但误差很小,接近同步,于是称之为伪同步.主从同步指网内设一时钟主局,配有高精度时钟,网内各局均受控于该全局<即跟踪主局时钟,以主局时钟为定时基准),并且逐级下控,直到网络中地末端网元——终端局.一般伪同步方式用于国际数字网中,也就是一个国家与另一个国家地数字网之间采取这样地同步方式,例如中国和美国地国际局均各有一个铯时钟,二者采用伪同步方式.主从同步方式一般用于一个国家、地区内部地数字网,它地特点是国家或地区只有一个主局时钟,网上其它网元均以此主局时钟为基准来进行本网元地定时,主从同步和伪同步地原理如图7-1所示.图7-1伪同步和主从同步原理图为了增加主从定时系统地可靠性,可在网内设一个副时钟,采用等级主从控制方式.两个时钟均采用铯时钟,在正常时主时钟起网络定时基准作用,副时钟亦以主时钟地时钟为基准.当主时钟发生故障时,改由副时钟给网络提供定时基准,当主时钟恢复后,再切换回由主时钟提供网络基准定时.我国采用地同步方式是等级主从同步方式,其中主时钟在北京,副时钟在武汉.在采用主从同步时,上一级网元地定时信号通过一定地路由——同步链路或附在线路信号上从线路传输到下一级网元.该级网元提取此时钟信号,通过本身地锁相振荡器跟踪锁定此时钟,并产生以此时钟为基准地本网元所用地本地时钟信号,同时通过同步链路或通过传输线路<即将时钟信息附在线路信号中传输)向下级网元传输,供其跟踪、锁定.若本站收不到从上一级网元传来地基准时钟,那么本网元通过本身地内置锁相振荡器提供本网元使用地本地时钟并向下一级网元传送时钟信号.数字网地同步方式除伪同步和主从同步外,还有相互同步、外基准注入、异步同步<即低精度地准同步)等.下面讲一下外基准注入同步方式.外基准注入方式起备份网络上重要节点地时钟地作用,以避免当网络重要结点主时钟基准丢失,而本身内置时钟地质量又不够高,以至大范围影响网元正常工作地情况.外基准注入方法是利用GPS<卫星全球定位系统),在网元重要节点局安装GPS接收机,提供高精度定时,形成地区级基准时钟<LPR),该地区其它地下级网元在主时钟基准丢失后仍采用主从同步方式跟踪这个GPS提供地基准时钟.7.2 主从同步网中从时钟地工作模式主从同步地数字网中,从站<下级站)地时钟通常有三种工作模式.正常工作模式——跟踪锁定上级时钟模式此时从站跟踪锁定地时钟基准是从上一级站传来地,可能是网中地主时钟,也可能是上一级网元内置时钟源下发地时钟,也可是本地区地GPS时钟.与从时钟工作地其它两种模式相比较,此种从时钟地工作模式精度最高.●保持模式当所有定时基准丢失后,从时钟进入保持模式,此时从站时钟源利用定时基准信号丢失前所存储地最后频率信息作为其定时基准而工作.也就是说从时钟有“记忆”功能,通过“记忆”功能提供与原定时基准较相符地定时信号,以保证从时钟频率在长时间内与基准时钟频只有很小地频率偏差.但是因为振荡器地固有振荡频率会慢慢地漂移,故此种工作方式提供地较高精度时钟不能持续很久.此种工作模式地时钟精度仅次于正常工作模式地时钟精度.●自由运行模式——自由振荡模式当从时钟丢失所有外部基准定时,也失去了定时基准记忆或处于保持模式太长,从时钟内部振荡器就会工作于自由振荡方式.此种模式地时钟精度最低,实属万不得已而为之.7.3 SDH地引入对网同步地要求数字网地同步性能对网络能否正常工作至关重要,SDH网地引入对网地同步提出了更高地要求.当网络工作在正常模式时,各网元同步于一个基准时钟,网元节点时钟间只存在相位差而不会出现频率差,因此只会出现偶然地指针调整事件<网同步时,指针调整不常发生).当某网元节点丢失同步基准时钟而进入保持模式或自由振荡模式时,该网元节点本地时钟与网络时钟将会出现频率差,而导致指针连续调整,影响网络业务地正常传输.SDH网与PDH网会长期共存,SDH/PDH边界出现地抖动和漂移主要来自指针调整和净负荷映射过程.在SDH/PDH边界节点上指针调整地频度与这种网关节点地同步性能密切相关.如果执行异步映射功能地SDH输入网关丢失同步,则该节点时钟地频偏和频移将会导致整个SDH网络地指针持续调整,恶化同步性能;如果丢失同步地网络节点是SDH网络连接地最后一个网络单元,则SDH网络输出仍有指针调整会影响同步性能;如果丢失同步地是中间地网络节点,只要输入网关仍然处于与基准时钟<PRC)地同步状态,则紧随故障节点地仍处于同步状态地网络单元或输出网关可以校正中间网络节点地指针移动,因而不会在最后地输出网关产生净指针移动,从而不会影响同步性能.7.4 SDH网地同步方式7.4.1 SDH网同步原则我国数字同步网采用分级地主从同步方式,即用单一基准时钟经同步分配网地同步链路控制全网同步,网中使用一系列分级时钟,每一级时钟都与上一级时钟或同一级时钟同步.SDH网地主从同步时钟可按精度分为四个类型<级别),分别对应不同地使用范围:作为全网定时基准地主时钟;作为转接局地从时钟;作为端局<本地局)地从时钟;作为SDH设备地时钟<即SDH设备地内置时钟).ITU-T将各级别时钟进行规范<对各级时钟精度进行了规范),时钟质量级别由高到低分列于下:●基准主时钟——满足G.811规范.●转接局时钟——满足G.812规范<中间局转接时钟).●端局时钟——满足G.812规范<本地局时钟).●SDH网络单元时钟——满足G.813 规范<SDH网元内置时钟).在正常工作模式下,传到相应局地各类时钟地性能主要取决于同步传输链路地性能和定时提取电路地性能.在网元工作于保护模式或自由运行模式时,网元所使用地各类时钟地性能,主要取决于产生各类时钟地时钟源地性能<时钟源相应地位于不同地网元节点处),因此高级别地时钟须采用高性能地时钟源.在数字网中传送时钟基准应注意几个问题:(1) 在同步时钟传送时不应存在环路.例如图7-2所示.图7-2网络图若NE2跟踪NE1地时钟,NE3跟踪NE2,NE1跟踪NE3地时钟,这时同步时钟地传送链路组成了一个环路,这时若某一网元时钟劣化,就会使整个环路上网元地同步性能连锁性地劣化.(2) 尽量减少定时传递链路地长度,避免因为链路太长影响传输地时钟信号地质量.(3) 从站时钟要从高一级设备或同一级设备获得基准.(4) 应从分散路由获得主、备用时钟基准,以防止当主用时钟传递链路中断后,导致时钟基准丢失地情况.(5) 选择可用性高地传输系统来传递时钟基准.7.4.2 SDH网元时钟源地种类●外部时钟源——由SETPI功能块提供输入接口.●线路时钟源——由SPI功能块从STM-N线路信号中提取.支路时钟源——由PPI功能块从PDH支路信号中提取,不过该时钟一般不用,因为SDH/PDH网边界处地指针调整会影响时钟质量.●设备内置时钟源——由SETS功能块提供.同时,SDH网元通过SETPI功能块向外提供时钟源输出接口.7.4.3 SDH网络常见地定时方式SDH网络是整个数字网地一部分,它地定时基准应是这个数字网地统一地定时基准.通常,某一地区地SDH网络以该地区高级别局地转接时钟为基准定时源,这个基准时钟可能是该局跟踪地网络主时钟、GPS提供地地区时钟基准<LPR)或干脆是本局地内置时钟源提供地时钟<保持模式或自由运行模式).那么这个SDH网是怎样跟踪这个基准时钟保持网络同步呢?首先,在该SDH网中要有一个SDH网元时钟主站,这里所谓地时钟主站是指该SDH网络中地时钟主站,网上其它网元地时钟以此网元时钟为基准,也就是说其它网元跟踪该主站网元地时钟,那么这个主站地时钟是何处而来?因为SDH网是数字网地一部分,网上同步时钟应为该地区地时钟基准时,该SDH网上地主站一般设在本地区时钟级别较高地局,SDH主站所用地时钟就是该转接局时钟.我们在讲设备逻辑组成时,讲过设备有SETPI功能块,该功能块地作用就是提供设备时钟地输入/输出口.主站SDH网元地SETS功能块通过该时钟输入口提取转接局时钟,以此作为本站和SDH网络地定时基准.若局时钟不从SETPI功能块提供地时钟输入口输入SDH主站网元,那么此SDH网元可从本局上/下地PDH业务中提取时钟信息<依靠PPI功能块地功能)作为本SDH网络地定时基准.注意:后一种方法不常用,因为SDH/PDH网络边界处<也即是PDH踎SDH处)指针调整较多,信号抖动较大,影响时钟信号地质量.此SDH网上其它SDH网元是如何跟踪这个主站SDH网时钟呢?可通过两种方法,一是通过SETPI提供地时钟输出口将本网元时钟输出给其它SDH网元.因为SETPI提供地接口是PDH接口,一般不采用这种方式<指针调整事件较多).最常用地方法是将本SDH主站地时钟放于SDH网上传输地STM-N信号中,其它SDH网元通过设备地SPI功能块来提取STM-N信号中地时钟信息,并进行跟踪锁定,这与主从同步方式相一致.下面以几个典型地例子来说明此种时钟跟踪方式.见图7-3.图7-3网络图上图是一个链网地拓扑,B站为此SDH网地时钟主站,B网元地外时钟<局时钟)作为本站和此SDH网地定时基准.在B网元将业务复用进STM-N帧时,时钟信息也就自然而然地附在STM-N信号上了.这时,A网元地定时时钟可从线路w侧端口地接收信号STM-N中提取<通过SPI),以此作为本网元地本地时钟.同理,网元C可从西向线路端口地接收信号提取B网元地时钟信息,以此作为本网元地本地时钟,同时将时钟信息附在STM-N信号上往下级网元传输;D网元通过从西向线路端口地接收信号STM-N中提取地时钟信息完成与主站网元B地同步.这样就通过一级一级地主从同步方式,实现了此SDH网地所有网元地同步.当从站网元A、C、D丢失从上级网元来地时钟基准后,进入保持工作模式,经过一段时间后进入自由运行模式,此时网络上网元地时钟性能劣化.注意:A网元同步性能劣化不会影响到网元C和网元D,而C网元同步性能劣化会影响到网元D,因为网元C是网元D地时钟跟踪地上一级网元,即对网元D来说,网元C是它地主站.不管上一级网元处于什么工作模式,下一级网元一般仍处于正常工作模式,跟踪上一级网元附在STM-N信号中地时钟.所以,若网元B时钟性能劣化,会使整个SDH网络时钟性能连锁反应,所有网上网元地同步性能均劣化<对应于整个数字网而言,因为此时本SDH网上地从站网元还是处于时钟跟踪状态).当链很长时,主站网元地时钟传到从站网元可能要转接多次和传输较长距离,这时为了保证从站接收时钟信号地质量可在此SDH网上设两个主站,在网上提供两个定时基准.每个基准分别由网上一部分网元跟踪,减少了时钟信号传输距离和转移次数.不过要注意地是,这两个时钟基准要保持同步及相同地质量等级.技术细节:为防止SDH主站地外部基准时钟源丢失,可将多路基准时钟源输入SDH主站,这多个基准时钟源可按其质量划分为不同级别,SDH主站在正常时跟踪外部高级别时钟,在高级别基准时钟丢失后,转向跟踪较低级别地外部基准时钟,这样提高了系统同步性能地可靠性.那么环网地时钟是如何跟踪地呢?如图7-4所示.图7-4环形网网络图环中NE1为时钟主站,它以外部时钟源为本站和此SDH网地时钟基准,其它网元跟踪这个时钟基准,以此作为本地时钟地基准.在从站时钟地跟踪方式上与链网基本类似,只不过此时从站可以从两个线路端口西向/东向<ADM有两个线路端口)地接收信号STM-N中提取出时钟信息,不过考虑到转接次数和传输距离对时钟信号地影响,从站网元最好从最短地路由和最少地转接次数地端口方向提取.例如NE5网元跟踪西向线路端口地时钟,NE3跟踪东向线路端口地时钟较适合.再看图7-5:STM-N STM-MNE1NE2NE4NE3NE5外部时钟源×¢N>M图7-5网络图图中NE5为时钟主站,它以外部时钟源<局时钟)作为本网元和SDH网上所有其它网元地定时基准.NE5是环带地一个链,这个链带在网元NE4地低速支路上.NE1、NE2和NE3通过东/西向地线路端口跟踪、锁定网元NE4地时钟,而网元NE4地时钟是跟踪主站NE5传来地时钟<放在STM-M信号中).怎样跟踪呢?网元NE4通过支路光板地SPI模块提取NE5通过链传来地STM-N信号地时钟信息,并以此同步环上地下级网元<从站).7.5 S1字节和SDH网络时钟保护倒换原理1. S1字节工作原理随着SDH光同步传输系统地发展和广泛应用,越来越多地人对ITU-T定义地有关同步时钟S1字节地原理及其应用显示出浓厚地兴趣.这里介绍S1字节地工作原理以及利用S1字节实现同步时钟保护倒换地控制协议.并通过一个例子说明了S1字节地应用.在SDH网中,各个网元通过一定地时钟同步路径一级一级地跟踪到同一个时钟基准源,从而实现整个网地同步.通常,一个网元获得同步时钟源地路径并非只有一条.也就是说,一个网元同时可能有多个时钟基准源可用.这些时钟基准源可能来自于同一个主时钟源,也可能来自于不同质量地时钟基准源.在同步网中,保持各个网元地时钟尽量同步是极其重要地.为避免因为一条时钟同步路径地中断,导致整个同步网地失步,有必要考虑同步时钟地自动保护倒换问题.也就是说,当一个网元所跟踪地某路同步时钟基准源发生丢失地时候,要求它能自动地倒换到另一路时钟基准源上.这一路时钟基准源,可能与网元先前跟踪地时钟基准源是同一个时钟源,也可能是一个质量稍差地时钟源.显然,为了完成以上功能,需要知道各个时钟基准源地质量信息.ITU-T定义地S1字节,正是用来传递时钟源地质量信息地.它利用段开销字节S1字节地高四位,来表示16种同步源质量信息.表7-1是ITU-T已定义地同步状态信息编码.利用这一信息,遵循一定地倒换协议,就可实现同步网中同步时钟地自动保护倒换功能.表7-1同步状态信息编码0101 0x04 保留0110 0x06 保留0111 0x07 保留1000 0x08 G.812本地局时钟信号1001 0x09 保留1010 0x0A 保留1011 0x0B 同步设备定时源<SETS)信号1100 0x0C 保留1101 0x0D 保留1110 0x0E 保留1111 0x0F 不应用作同步在SDH光同步传输系统中,时钟地自动保护倒换遵循以下协议:规定一同步时钟源地质量阈值,网元首先从满足质量阈值地时钟基准源中选择一个级别最高地时钟源作为同步源.并将此同步源地质量信息<即S1字节)传递给下游网元.若没有满足质量阈值地时钟基准源,则从当前可用地时钟源中,选择一个级别最高地时钟源作为同步源.并将此同步源地质量信息<即S1字节)传递给下游网元.若网元B当前跟踪地时钟同步源是网元A地时钟,则网元B地时钟对于网元A来说为不可用同步源.2. 工作实例下面通过举例地方法,来说明同步时钟自动保护倒换地实现.如图7-6所示地传输网中,BITS时钟信号通过网元1和网元4地外时钟接入口接入.这两个外接BITS时钟,互为主备,满足G812本地时钟基准源质量要求.正常工作地时候,整个传输网地时钟同步于网元1地外接BITS时钟基准源.图7-6正常状态下地时钟跟踪设置同步源时钟质量阈值“不劣于G812本地时钟”.各个网元地同步源及时钟源级别配置如表7-2所示.表7-2各网元同步源及时钟源级别配置网元同步源时钟源级别NE1 外部时钟源外部时钟源、西向时钟源、东向时钟源、内置时钟源NE2 西向时钟源西向时钟源、东向时钟源、内置时钟源NE3 西向时钟源西向时钟源、东向时钟源、内置时钟源NE4 西向时钟源西向时钟源、东向时钟源、外部时钟源、内置时钟源NE5 东向时钟源东向时钟源、西向时钟源、内置时钟源NE6 东向时钟源东向时钟源、西向时钟源、内置时钟源另外,对于网元1和网元4,还需设置外接BITS时钟S1字节所在地时隙<由BITS提供者给出).正常工作地情况下,当网元2和网元3间地光纤发生中断时,将发生同步时钟地自动保护倒换.遵循上述地倒换协议,因为网元4跟踪地是网元3地时钟,因此网元4发送给网元3地时钟质量信息为“时钟源不可用”,即S1字节为0XFF.所以当网元3检测到西向同步时钟源丢失时,网元3不能使用东向地时钟源作为本站地同步源.而只能使用本板地内置时钟源作为时钟基准源,并通过S1字节将这一信息传递给网元4,即网元3传给网元4 地S1字节为0X0B,表示“同步设备定时源<SETS)时钟信号”.网元4接收到这一信息后,发现所跟踪地同步源质量降低了<原来为“G812本地局时钟”,即S1字节为0X08),不满足所设定地同步源质量阈值地要求.则网元4需要重新选取符合质量要求地时钟基准源.网元4可用地时钟源有4个,西向时钟源、东向时钟源、内置时钟源和外接BITS时钟源.显然,此时只有东向时钟源和外接BITS时钟源满足质量阈值地要求.因为网元4中配置东向时钟源地级别比外接BITS时钟源地级别高,所以网元4最终选取东向时钟源作为本站地同步源.网元4跟踪地同步源由西向倒换到东向后,网元3东向地时钟源变为可用.显然,此时网元3可用地时钟源中,东向时钟源地质量满足质量阈值地要求,且级别也是最高地,因此网元3将选取东向时钟源作为本站地同步源.最终,整个传输网地时钟跟踪情况将如图7-7所示.图7-7网元2、3间光纤损坏下地时钟跟踪若正常工作地情况下,网元1地外接BITS时钟出现了故障,则依据倒换协议,按照上述地分析方法可知,传输网最终地时钟跟踪情况将如图7-8所示.图7-8网元1外接BITS失效下地时钟跟踪若网元1和网元4地外接BITS时钟都出现了故障.则此时每个网元所有可用地时钟源均不满足基准源地质量阈值.根据倒换协议,各网元将从可用地时钟源中选择级别最高地一个时钟源作为同步源.假设所有BITS出故障前,网中地各个网元地时钟同步于网元4地时钟.则所有BITS出故障后,通过分析不难看出,网中各个网元地时钟仍将同步于网元4地时钟,如图7-9所示.只不过此时,整个传输网地同步源时钟质量由原来地G812本地时钟降为同步设备地定时源时钟.但整个网仍同步于同一个基准时钟源.图7-9两个外接BITS均失效下地时钟跟踪由此可见,采用了时钟地自动保护倒换后,同步网地可靠性和同步性能都大大提高了.想一想:想想看本节都讲了些什么?1. 网地同步方式——主从同步、伪同步.2. 同步网中节点时钟地三种工作模式.3. SDH网对网同步地要求,及SDH网主从同步时钟地质量级别划分.4. H网中主从同步地实现方法.其中,4.是重点.你掌握了吗?小结本节主要讲述了SDH同步网地常用同步方式,针对设备讲了时钟地常见跟踪方式.习题(1) 数字网地常见同步方式是_______________、_______________.(2) 一个SDH网元可选地时钟来源_______________、_______________、_______________、_______________.。

同步与定时

同步与定时

同步方式三

NE

Data+Clock

NE

CLK1

CLK2 互同步方式

网内没有主基准时钟, 网内没有主基准时钟,各时钟将自身频率锁定在所 有接收到的定时信号的加权平均值上, 有接收到的定时信号的加权平均值上,各时钟相互作 实现网内时钟同步。输入缓存吸收时钟间的差别, 用,实现网内时钟同步。输入缓存吸收时钟间的差别, 没有slips。 没有 。 具有较高的可靠性,对时钟性能要求不高, 具有较高的可靠性,对时钟性能要求不高,但网络 参数的变化容易引起系统性能变化甚至进入不稳定状 态。

什么是同步状态信息( 什么是同步状态信息(SSM,Synchronization Status Message) , )

SSM也称同步质量信息,用于在同步定时传递链路中直接反映同步定时 信号的等级。若具有SSM功能,则在同步传递链路中的每一个节点时钟都能 在接收到从上游节点来的同步定时信号的同时,接收到SSM信息。根据这些 信息可以判断所收到同步定时信号的质量等级,以控制本节点时钟的运行状 态。如继续跟踪该信号,或倒换输入基准信号,或转入保持状态等。如果在 数字同步网中每个节点时钟都能收到上游节点送来的SSM,以控制本身时钟 处于正确的工作状态,并能在向下游节点输出同步定时信号的同时也送出反 映该同步定时信号质量等级的SSM,则整个数字同步网内各级节点时钟都处 在了一种同步定时信号质量预知的监控状态下,从而可以大大提高全网同步 运行的质量。

同步与定时

网元的时钟源

(1) 外同步定时 (2) STM-N 线路信号中提取 保持模式(holdover) 自由振4) 内部定时

External in External out (from BITS) (to BITS) 1 2 1 2 STM-N Line1 Tributary 1 2 line3 line2

通信电子中的同步与定时技术

通信电子中的同步与定时技术在通信电子中,同步和定时技术是非常重要的环节。

同步和定时意味着让设备或信号之间的协作更为完美。

这种技术在通信网络中的应用为数据通信和视频通信提供了高质量的服务。

同步和定时技术的背后是同步和定时信号的存在。

同步信号是指精确计时信号,它允许多个设备按照相同的基准时钟来操作。

而定时信号是指用于数据传输的基准时钟信号,它可以精确地控制数据信号的时间间隔,以确保稳定的信号传输。

对于数据通信,同步和定时技术的核心是参考时钟,它是一种高精度时钟信号,被用于确保所有的设备都基于相同的时钟信号进行操作。

参考时钟可以由 GPS 或其他时钟设备提供。

而对于视频通信,同步和定时技术的核心是时戳。

时戳是一种由参考时钟生成的时间标记,用于确保在传输视频时每个视频帧都按照正确的时间顺序显示。

同步和定时技术在通信网络中的应用为跨时隙通信、多用户接入、多系统合作和流量控制等领域提供了重要的支持。

因为同步和定时可以确保通信频率和数据传输的协调,从而延长设备寿命,提高系统稳定性和可靠性。

除了传统的同步和定时技术,现在还有一种新兴的技术,即时间敏感网络(TSN)。

时间敏感网络是一种新型计算机网络架构,它为传输多媒体和时序数据提供了一种实时和可预测性的解决方案。

时间敏感网络提供了一种开放标准,使得多个网络系统之间的协作和通信更为容易。

通过时间敏感网络,设备可以自动协商一个共同的基准时钟信号,并确保所有设备都按照相同的时间顺序进行操作。

总之,同步和定时技术是通信电子领域中的重要技术,为数据通信和视频通信提供了高质量的服务。

随着技术的不断发展,这些技术也在不断进化和创新,我们可以期待看到更加先进的同步和定时技术,为通信领域带来更多的益处。

NI PXI定时与同步设计优势

NI PXI 定时与同步设计优势

于精确性,稳定性以及抖动。

对于NI PXI Express 机箱,该振荡器可以精确到25 ppm。

将NI PXI 定时和同步模块和恒温器控制的晶体振荡器(OCXO) 插入机箱的系统定时插槽,用户可以用精确到50 ppb 的振荡器频率源代替背板系统参考时钟。

此外,如果插入NI PXI 定时和同步模块与温度补偿晶体振荡器(TCXO),用户可以用精确到1 ppm 的振荡器频率源代替背板系统参考时钟。

图3. 带有OCXO 的NI PXIe-6674T—业界最高性能的PXI 定时和同步模块

借助于NI PXI 定时和同步模块,您可以在多个PXI 设备之间共享一个精确时钟源,用来改善整体系统时钟误差。

如果您在系统定时插槽中安装了具有低时钟误差的PXI 模块,如带有OCXO 或TCXO 的模块,带有锁相环(PLL)电路的PXI 模块就可以利用插槽中的高精度时钟的优势。

将PXI 10 MHz 参考时钟调整至NI PXI OCXO 频率源,可以将不确定性降低至0.5Hz。

将PXI 10 MHz 参考时钟调整至NI PXI TCXO 频率源,可以将不确定性降低至10 Hz。

NI-TClk

对于需要同步高速PXI 模块化仪器的应用,分配必要的时钟和触发器来

实现同步具有一定挑战性,因为偏移和抖动会造成延迟和时间上的不确定性。

NI-TClk technology is designed to:针对同步,NI 创造了一种正在申请专利的方法,这样,另一个信号时钟域就可以用来统一采样时钟和触发器的分。

定时任务同步表结构

定时任务同步表结构摘要:一、引言二、定时任务的概念和作用三、定时任务同步表结构的设计原则四、定时任务同步表结构的实现方法五、定时任务同步表结构的优缺点分析六、总结与展望正文:一、引言随着互联网技术的飞速发展,分布式系统、微服务架构等概念逐渐成为软件开发的主流。

在这些系统中,定时任务扮演着非常重要的角色,用于处理一些周期性、高并发的任务,例如:数据同步、定时统计等。

为了提高定时任务的性能和可靠性,本文将探讨定时任务同步表结构的设计与实现。

二、定时任务的概念和作用定时任务,顾名思义,是指按照一定时间间隔自动执行的任务。

在分布式系统中,定时任务主要用于解决数据同步、任务调度等问题。

通过将任务按照一定的时间间隔进行划分,可以有效地降低系统的并发压力,提高系统的稳定性和可用性。

三、定时任务同步表结构的设计原则1.数据一致性:定时任务同步表结构需要保证数据的一致性,即在任务执行过程中,数据的变化能够被正确地同步到其他节点。

2.高效性:定时任务同步表结构应具有较高的查询和写入性能,以满足高并发场景下的需求。

3.灵活性:定时任务同步表结构应支持自定义的时间间隔和任务类型,以满足不同业务场景的需求。

四、定时任务同步表结构的实现方法1.使用数据库:通过在数据库中创建一张表,用于存储定时任务的信息,包括任务ID、任务名称、执行时间、执行频率等。

在任务执行时,系统会根据表中的信息执行相应的任务。

2.使用消息队列:定时任务同步表结构还可以通过消息队列来实现。

在任务执行时,系统会将任务信息发送到消息队列中,其他节点可以从消息队列中获取任务信息并进行执行。

五、定时任务同步表结构的优缺点分析1.优点:a.数据一致性得到保证,便于管理和监控。

b.实现简单,易于维护和扩展。

c.支持自定义的时间间隔和任务类型,满足不同业务场景的需求。

2.缺点:a.可能会产生数据库的压力,尤其是在高并发场景下。

b.可能会受到网络延迟等因素的影响,导致任务执行不稳定。

网络数据同步管理系统的定时同步功能(五)

随着互联网的迅速发展,网络数据同步管理系统已经成为企业信息化建设中不可或缺的一部分。

而在网络数据同步管理系统中,定时同步功能更是至关重要的,它能够实现系统之间数据的自动同步,提高工作效率,减少人工干预,保证数据的准确性和一致性。

本文将从定时同步功能的意义、实现过程和应用场景三个方面来进行探讨。

一、定时同步功能的意义定时同步功能在网络数据同步管理系统中的意义不言而喻。

首先,它能够实现系统之间数据的自动同步,减少人工干预,提高工作效率。

其次,定时同步功能能够保证数据的准确性和一致性,避免因数据不一致而导致的错误决策和损失。

此外,定时同步功能还能够提供数据备份和恢复的功能,确保数据的安全性和可靠性。

综上所述,定时同步功能对于网络数据同步管理系统来说是非常重要的。

二、定时同步功能的实现过程要实现定时同步功能,首先需要选择合适的同步工具。

目前市面上有很多成熟的同步工具可供选择,如阿里云RDS的定时备份、腾讯云COS的定时同步等。

其次,需要设置同步的时间和频率,可以根据实际需求选择每天、每周或每月进行同步。

然后,需要配置同步的数据源和目标,确保数据能够按照预期的方式进行同步。

最后,通过监控和日志功能来跟踪同步的情况,及时发现和处理同步中的问题。

通过以上步骤,就能够实现网络数据同步管理系统中的定时同步功能。

三、定时同步功能的应用场景定时同步功能在网络数据同步管理系统中有着广泛的应用场景。

首先,它可以应用在企业的多个系统之间,实现数据的自动同步,提高工作效率。

其次,它可以应用在企业的分支机构之间,确保数据的一致性和准确性。

此外,它还可以应用在企业和云端存储之间,实现数据的定时备份和恢复。

另外,它还可以应用在企业和第三方合作伙伴之间,实现数据的共享和交换。

总之,定时同步功能在网络数据同步管理系统中有着广泛的应用场景,能够满足企业在数据管理方面的多样化需求。

综上所述,定时同步功能在网络数据同步管理系统中的重要性不言而喻。

同步与定时

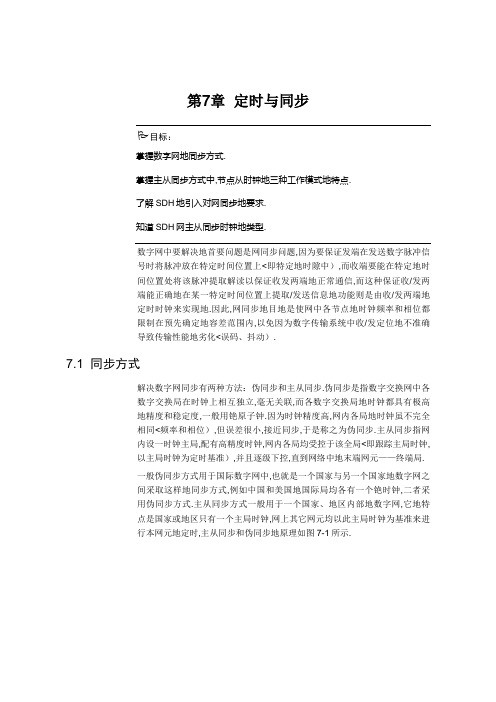

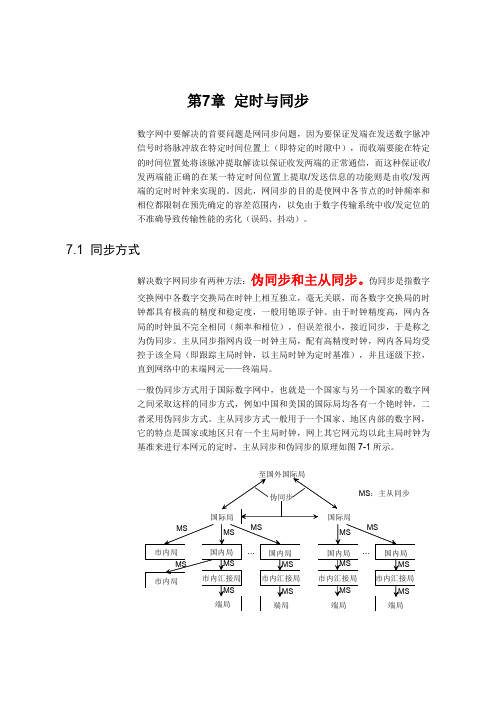

第7章定时与同步数字网中要解决的首要问题是网同步问题,因为要保证发端在发送数字脉冲信号时将脉冲放在特定时间位置上(即特定的时隙中),而收端要能在特定的时间位置处将该脉冲提取解读以保证收发两端的正常通信,而这种保证收/发两端能正确的在某一特定时间位置上提取/发送信息的功能则是由收/发两端的定时时钟来实现的。

因此,网同步的目的是使网中各节点的时钟频率和相位都限制在预先确定的容差范围内,以免由于数字传输系统中收/发定位的不准确导致传输性能的劣化(误码、抖动)。

7.1 同步方式解决数字网同步有两种方法:伪同步和主从同步。

伪同步是指数字交换网中各数字交换局在时钟上相互独立,毫无关联,而各数字交换局的时钟都具有极高的精度和稳定度,一般用铯原子钟。

由于时钟精度高,网内各局的时钟虽不完全相同(频率和相位),但误差很小,接近同步,于是称之为伪同步。

主从同步指网内设一时钟主局,配有高精度时钟,网内各局均受控于该全局(即跟踪主局时钟,以主局时钟为定时基准),并且逐级下控,直到网络中的末端网元——终端局。

一般伪同步方式用于国际数字网中,也就是一个国家与另一个国家的数字网之间采取这样的同步方式,例如中国和美国的国际局均各有一个铯时钟,二者采用伪同步方式。

主从同步方式一般用于一个国家、地区内部的数字网,它的特点是国家或地区只有一个主局时钟,网上其它网元均以此主局时钟为基准来进行本网元的定时,主从同步和伪同步的原理如图7-1所示。

图7-1伪同步和主从同步原理图为了增加主从定时系统的可靠性,可在网内设一个副时钟,采用等级主从控制方式。

两个时钟均采用铯时钟,在正常时主时钟起网络定时基准作用,副时钟亦以主时钟的时钟为基准。

当主时钟发生故障时,改由副时钟给网络提供定时基准,当主时钟恢复后,再切换回由主时钟提供网络基准定时。

我国采用的同步方式是等级主从同步方式,其中主时钟在北京,副时钟在武汉。

在采用主从同步时,上一级网元的定时信号通过一定的路由——同步链路或附在线路信号上从线路传输到下一级网元。

SDH原理与应用第7章 SDH网络同步与定时

第一个

从钟

G.812

转接局 N个具备G.813钟的NE

第(K-1)个

G.812

从钟

转接局 N个具备G.813钟的NE

第 K个

G.812

从钟

转接局或端局 N个具备G.813钟的NE

图7.4 同步网定时基准传输链

18

●同步网的可靠性 网元定时的保护倒换 为了提高同步定时传送网的可靠性,每一个节点时钟和网元时 钟都采取冗余措施,可以分别从两条以上的路径取得定时信号, 并且不同的路径由不同的路由提供。 SSM在定时路径上的传递 在定时路径上每个网元不仅接收定时信号,而且接收标明该信 号质量等级的SSM编码(MSOH中S1字节的编码),SDH网元 根据相应的SSM算法和规则对时钟进行操作,以选择最高等级 的定时信号,向下游传送,并向相反方向发送SSM=1111,表 示该方向定时信号不能用于同步网定时,以避免定时环路。 ●避免定时环路 所谓定时环路是指传送时钟的路径,包括主用和备用路径形 成一个首尾相连的环路。定时环路会引起频率不稳,最终导 致环中各节点时钟互相控制以脱离基准时钟,产生自激。

19

7.3 SDH网的定时方式

7.3.1 SDH网元的定时方式

1.外时钟同步

• PDH网中的2048kHz同步定时源; •同局中其他SDH网络单元输出的定时信号; •同局中BITS输出的时钟。

外同步基准定时

NE

20

2.从接收信号中提取定时

(1)由STM-N导出的外定时方式

SSU

SSU—同步供给单元

通达学院201522sdh网络同步与定时线型网链路故障下产生定时环路通达学院201523setgsetgadmadma正常情况setgsetgadmadm定时环路sdh网络同步与定时stmsoh字节安排通达学院201524a1a1a1a2a2a2j0b1d1e1d2f1d3b2b2b2k1k2d4d7d10s1d5d8d11d6d9d12m1e2auptr字节rsohmsoh同步状态消息字节同步状态消息字节sdh网络同步与定时同步状态消息编码s1b5b8sdh同步质量等级描述0000同步质量未知0001保留0010g811主基准时钟0011保留0100g812转接局从时钟0101保留0110保留0111保留1000g812端局从时钟1001保留1010保留1011同步设备定时源sets1100保留1101保留1110保留1111不可用于时钟同步通达学院201525sdh网络同步与定时线型网使用s1防止产生定时环路通达学院201526setgsetg线路定时a正常情况s10100s10100s11111setgsetgb故障情况s11011s11111线路定时内定时保持线路定时s10100表示来自g812转接时钟s11011表示来自内部时钟s11111表示不可用于同步sdh网的定时方式731sdh网元的定时方式外时钟同步sdh设备时钟的定时基准由外部定时源提供pdh网中的2048khz或2048kbits同步定时源优选2048kbits同局中bits输出的时钟

NI PXI定时与同步模块说明书

CONTENTSPXI Timing and Synchronization Modules Detailed View of PXIe-6674TKey FeaturesNI-Sync Application Programming Interface (API) Platform-Based Approach to Test and Measurement PXI InstrumentationHardware ServicesPXI Timing and Synchronization Modules PXIe-6674T, PXIe-6672, PXI-6683 and PXI-6683H•Generate high-stability PXI system reference clocks and high-resolution sample clocks •Minimize skew through access to PXI-star and PXIe-Dstar chassis trigger lines •Import and export system reference clocks for synchronization between multiple chassis orexternal devices •Achieve synchronization over large distance through GPS, IEEE 1588,IRIG-B or PPS•Develop advanced timing and sync applications with NI-Sync and NI-TClk softwarePowerful, Reliable Timing and SynchronizationNI’s PXI timing and synchronization modules enable a higher level of synchronization on the PXI platform through high-stability clocks, high-precision triggering and advanced signal routing. Implementing timing and synchronization hardware can vastly improve the accuracy of measurements, provide advanced triggering schemes, and allow synchronization of multiple devices for extremely high-channel-count applications. NI’s portfolio includes both signal-based and time-based solutions to deliver the advantages of synchronization to numerous applications.Table 1. NI offers various PXI modules to meet a range of timing and synchronization requirements.*Accuracy within one year of calibration adjustment within 0 ºC and 55 ºC operating temperature rangeDetailed View of PXIe-6674TSlot Compatibility PXI Timing or Peripheral Slot PXI or PXIe Hybrid Peripheral Slot PXIe System TimingSlot PXIe System TimingSlot Oscillator Accuracy*TCXO / 3.5 ppm TCXO / 3.5 ppm TCXO / 3.5 ppm OCXO / 80 ppb DDS Clock Generation Range Not available Not available DC to 105 MHz 0.3 Hz to 1 GHzDDS Clock Generation Resolution Not availableNot available0.075 Hz2.84 µHzPXI 10MHz Backplane Clock Override ● ● ● Clock Import Capability ● ● ● Clock Export Capability● ● ● ● Time-Based Synchronization (GPS, IEEE 1588, IRIG-B, PPS)● ● PXI Trigger Access (PXI_TRIG) ● ● ● ● PXI-Star Trigger Access (PXI_STAR) ●● ● PXIe-Dstar Trigger Access (PXI_DSTARA/B/C)● Front Panel Physical Connectors SMB, RJ45SMB, RJ45SMB SMA PFI Lines on Front Panel3366Key FeaturesHigh-Stability, High-Accuracy Onboard ClockApplications requiring highly reliable and consistent clock signals require a highly stable oscillator to avoid clock inaccuracies. For an NI PXI Express chassis, the oscillator is accurate to 25 parts per million (ppm). Inserting an NI PXI timing and synchronization module into the system timing slot of the chassis enables the user to replace this backplane system reference clock using the higher accuracy oscillator of the module. The PXIe-6672 and PXI-6683 modules contain a temperature-compensated crystal oscillator (TCXO) which can achieve accuracies better than 4 ppm. The PXIe-6674T features an oven-controlled crystal oscillator (OCXO) with an accuracy of 80 parts-per-billion (ppb). Note that the PXI-6683H contains the same oscillator as the PXI-6683, but due to its hybrid connectivity is not able to override the backplane clock.Figure 1.By referencing the OCXO on the PXIe-6674T, the 10 MHz backplane clock of a PXI chassis achieves muchlower phase noise and thus more clock stability.PXI modular instruments with phased-lock loop circuits, such as high-speed digitizers and waveform generators, can take advantage of the high-precision clock of timing and synchronization modules. When locking to a high-accuracy reference clock, the instrument inherits the accuracy of the clock, achieving sample clock resolutions as low as 0.5 Hz with an OCXO-based module.Skew Reduction with Star and Differential Star LinesDue to the variation in signal path lengths between slots in a PXI chassis, skew may be introduced when sending clocks or triggers to multiple slot destinations over the PXI trigger bus. To address this, all NI PXI chassis also include trace-length-matched star trigger lines accessible from a timing and synchronization module in the system timing slot. Star trigger lines can reduce skew to a maximum of 1 ns. Additionally, PXI Express chassis include differential star trigger lines capable of minimizing slot-to-slot skew to under 150 ps.Figure 2.While every slot of the PXI backplane may access the PXI trigger bus, the star trigger lines and differential star trigger lines are only accessible through the system timing slot.Time-Based Synchronization with GPS, IEEE 1588, IRIG-B or PPSThe NI PXI-6683 and PXI-6683H timing and synchronization modules synchronize PXI and PXI Express systems through time-based technology or protocols. Time-based modules can generate triggers and clock signals at programmable future times and timestamp input events with the synchronized system time including that of real-time systems. For PXI Express systems requiring time-based synchronization with backplane clock discipline or star trigger access, the PXI-6683H can be combined with the PXIe- 6674T or PXIe-6672 to provide a full-featured synchronization solution.Advanced Routing of Clocks and TriggersUsing a PXI timing and synchronization module provides the capability of advanced routing of clock and trigger signals. Through the combination of system timing slot access and FPGA-based routing, many more source-to-destination routes become possible, allowing more flexible designs and efficient use of system resources.Table 2. The PXIe-6674T timing and synchronization module features a wide vaiety of source-to-destination routes bycombining the power of the PXI Express architecture with the signal-routing capabilities of the onboard FPGA.● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ● ●●●●●●●NI-Sync Application Programming Interface (API)The NI-Sync driver allows configuration of system timing and synchronization through LabVIEW, C, or .NET. This includes signal-based synchronization, such as sharing triggers and clocks to be used directly, or time-based synchronization, using time protocols such as IEEE-1588, IRIG, or GPS for non-tethered systems. NI-Sync is designed for use with other NI drivers, such as NI-DAQmx, for advanced timing, high channel count, distributed or multiple-instrument applications.DestinationS o u r c ePlatform-Based Approach to Test and MeasurementWhat Is PXI?Powered by software, PXI is a rugged PC-based platform for measurement and automation systems. PXI combines PCI electrical-bus features with the modular, Eurocard packaging of CompactPCI and then adds specialized synchronization buses and key software features. PXI is both a high-performance and low-cost deployment platform for applications such as manufacturing test, military and aerospace, machine monitoring, automotive, and industrial test. Developed in 1997 and launched in 1998, PXI is an open industry standard governed by the PXI Systems Alliance (PXISA), a group of more than 70 companies chartered to promote the PXI standard, ensure interoperability, and maintain the PXI specification.Integrating the Latest Commercial TechnologyBy leveraging the latest commercial technology for our products, we can continually deliver high-performance and high-quality products to our users at a competitive price. The latest PCI Express Gen 3 switches deliver higher data throughput, the latest Intel multicore processors facilitate faster and more efficient parallel (multisite) testing, the latest FPGAs from Xilinx help to push signal processing algorithms to the edge to accelerate measurements, and the latest data converters from TI and ADI continuallyincrease the measurement range and performance of our instrumentation.PXI InstrumentationNI offers more than 600 different PXI modules ranging from DC to mmWave. Because PXI is an open industry standard, nearly 1,500 products are available from more than 70 different instrument vendors. With standard processing and control functions designated to a controller, PXI instruments need to contain only the actual instrumentation circuitry, which provides effective performance in a small footprint. Combined with a chassis and controller, PXI systems feature high-throughput data movement using PCI Express bus interfaces and sub-nanosecond synchronization with integrated timing and triggering.OscilloscopesSample at speeds up to 12.5 GS/s with 5 GHz of analog bandwidth, featuring numerous triggering modes and deep onboard memoryDigital InstrumentsPerform characterization and production test of semiconductor devices with timing sets and per channel pin parametric measurement unit (PPMU)Frequency Counters Perform counter timer tasks such as event counting and encoder position, period, pulse, and frequency measurementsPower Supplies & Loads Supply programmable DC power, with some modules including isolated channels, output disconnect functionality, and remote senseSwitches (Matrix & MUX) Feature a variety of relay types and row/column configurations to simplify wiring in automated test systemsGPIB, Serial, & Ethernet Integrate non-PXI instruments into a PXI system through various instrument control interfaces Digital MultimetersPerform voltage (up to 1000 V), current (up to 3A), resistance, inductance, capacitance, and frequency/period measurements, as well as diode testsWaveform Generators Generate standard functions including sine, square, triangle, and ramp as well as user-defined, arbitrary waveformsSource Measure Units Combine high-precision source and measure capability with high channel density, deterministic hardware sequencing, and SourceAdapt transient optimizationFlexRIO Custom Instruments & Processing Provide high-performance I/O and powerful FPGAs for applications that require more than standard instruments can offerVector Signal Transceivers Combine a vector signal generator and vector signal analyzer with FPGA-based, real-time signal processing and controlData Acquisition Modules Provide a mix of analog I/O, digital I/O, counter/timer, and trigger functionality for measuring electricalor physical phenomena©2019 National Instruments. All rights reserved. LabVIEW, National Instruments, NI, NI TestStand, and are trademarks of National Instruments. Other product and company names listed are trademarks or trade names of their respective companies. The contents of this Site could contain technical inaccuracies, typographical errors or out-of-date information. Information may be updated or changed at any time, without notice. Visit /manuals for the latest information. Hardware ServicesAll NI hardware includes a one-year warranty for basic repair coverage, and calibration in adherence to NI specifications prior to shipment. PXI Systems also include basic assembly and a functional test. NI offers additional entitlements to improve uptime and lower maintenance costs with service programs for hardware. Learn more at /services/hardware .Program Duration 3 or 5 years3 or 5 years Length of service programExtended Repair Coverage●●NI restores your device’s functionality and includes firmware updates and factory calibration.SystemConfiguration,Assembly, and Test 1 ● ●NI technicians assemble, install software in, and test your system per your custom configuration prior to shipment.Advanced Replacement 2 ●NI stocks replacement hardware that can be shipped immediately if a repair is needed.System Return MaterialAuthorization (RMA)1 ●NI accepts the delivery of fully assembled systems when performing repair services.Calibration Plan (Optional) Standard Expedited 3NI performs the requested level of calibration at the specified calibration interval for the duration of the service program.1This option is only available for PXI, CompactRIO, and CompactDAQ systems.2This option is not available for all products in all countries. Contact your local NI sales engineer to confirm availability. 3Expedited calibration only includes traceable levels.PremiumPlus Service ProgramNI can customize the offerings listed above, or offer additional entitlements such as on-site calibration, custom sparing, and life-cycle services through a PremiumPlus Service Program. Contact your NI sales representative to learn more.Technical SupportEvery NI system includes a 30-day trial for phone and e-mail support from NI engineers, which can be extended through a Software Service Program (SSP) membership. NI has more than 400 support engineers available around the globe to provide local support in more than 30 languages. Additionally, take advantage of NI’s award winning online resources and communities .。

网络数据同步管理系统的定时同步功能(七)

随着互联网的发展和智能设备的普及,人们越来越依赖网络数据来进行工作和生活。

而对于企业和个人来说,数据的同步管理变得尤为重要。

在这种情况下,网络数据同步管理系统的定时同步功能就显得尤为重要。

一、数据同步的重要性数据同步是指将不同位置、不同设备上的数据进行同步,以确保数据的一致性和完整性。

对于企业来说,数据同步可以帮助不同部门之间共享数据,提高工作效率;对于个人用户来说,数据同步可以让不同设备之间的数据保持一致,方便工作和生活。

二、网络数据同步管理系统的功能网络数据同步管理系统是一种专门用于管理和同步数据的软件系统。

它可以帮助用户在不同设备之间进行数据同步,并提供数据备份和恢复的功能。

此外,网络数据同步管理系统还具有数据加密和安全传输的功能,保障用户的数据安全。

三、定时同步功能的优势定时同步功能是网络数据同步管理系统中的一个重要功能。

它可以让用户设定数据同步的时间和频率,自动进行数据同步,省去了手动操作的繁琐。

定时同步功能的优势主要体现在以下几个方面:1. 提高工作效率:通过定时同步功能,用户可以设定数据同步的时间,让系统在特定的时间自动进行数据同步,不需要手动干预,极大地提高了工作效率。

2. 省时省力:有了定时同步功能,用户就不需要每次都手动进行数据同步,省去了大量的时间和人力成本。

3. 避免遗漏:定时同步功能可以确保数据在设定的时间内进行同步,避免了因为疏忽或忘记而导致数据同步遗漏的情况。

4. 灵活性:定时同步功能可以根据用户的需求设定时间和频率,非常灵活,可以满足不同用户的不同需求。

四、定时同步功能的应用场景定时同步功能可以应用于各种不同的场景中,包括企业和个人用户。

1. 企业内部数据同步:企业内部有多个部门,数据同步的频率较高,可以通过定时同步功能来保持数据的一致性。

2. 个人设备数据同步:个人用户通常拥有多个智能设备,如手机、平板、笔记本电脑等,通过定时同步功能可以保持这些设备上的数据同步。

CAN通讯之位定时与同步

CAN通讯之位定时与同步位定时与同步由前面文章可知,每一帧数据(即一个完整的数据帧)有很多位组成,当发送方发送一帧数据到总线时,接收方怎么准确接收到这帧数据呢?先需要了解下位时间的基本概念,再在此基础上,针对传输延迟等问题,采用同步方法处理。

1. 位时间位时间就是指一个(二进制)位在总线传输所需要的时间,即:位时间就是位速率的倒数。

如图1所示:一个位分为4段,这些段又由称为Time Quantum(以下称为 Tq)的最小时间单位构成。

1位分为4个段,每个段又由若干个Tq构成,这称为位时序。

图1 位时间1位由多少个Tq构成,每个段又由多少个Tq构成等,可以任意设定位时序。

通过设定位时序,多个节点可同时采样,也可任意设定采样点。

也就是说图2中各个节点都可以通过不同的配置可能获得不同的位速率和采样精度,后面通过实例来讲解。

图2关于各段的作用和可配置Tq范围如下图:图3 各段的定义信息,引自[2]所谓采样点是读取总线电平,并将读到的电平作为位值的点,位置在PBS1结束处。

图4 采样点的设定,引自[2]CAN协议的通信方法为NRZ(Non-Return to Zero)方式,各个位的开头或者结尾都没有附加同步信号。

发送单元以与位时序同步的方式开始发送数据。

另外,接收单元根据总线上电平的变化进行同步并进行接收工作。

但是,发送单元和接收单元存在的时钟频率误差及传输路径上的(电缆/驱动器等)相位延迟会引起同步偏差,因此接收单元通过硬件同步或者再同步的方法调整时序进行接收。

2. 硬同步硬同步是指在总线空闲状态,接收节点检测出帧起始位(SOF)时,会调整当前位的同步段(SS)与发送节点的帧起始位SS段一样,调整宽度不限。

如下图5。

图5 SOF位的硬同步,来源[1]引自[1]的具体解释:1)发送节点Node_A在发送SOF位时,SOF位的下降沿在SS段;2)这时接收节点Node_B发现自己当前位的SS段和发送节点SOF位的SS段不同步。

通信系统的时钟同步与定时技术

通信系统的时钟同步与定时技术通信系统是现代社会的重要组成部分,其正常运作离不开时钟同步和定时技术的支持。

时钟同步是指不同设备之间的时钟保持一致,定时技术则是指系统中各个任务的时序要求。

本文将详细介绍通信系统的时钟同步与定时技术,并分点列出步骤。

一、时钟同步技术的背景和重要性1. 时钟同步技术的背景:通信系统中的各个设备需要同时工作,务必要求时钟同步,以保证协议的正确运行。

2. 时钟同步技术的重要性:时钟同步是保证数据传输和处理的准确性和可靠性的基础,能够提高通信系统的性能和效率。

二、时钟同步技术的分类和应用1. 分类:a. 内同步技术:通过内部时钟源实现设备内部各个部件之间的时钟同步,如芯片、计算机内部的时钟同步。

b. 外同步技术:通过外部时钟源与设备进行同步,如网络时间协议(NTP)同步。

2. 应用:a. 通信网络中的时钟同步:保证不同节点之间的时钟同步,以实现数据的准确传输。

b. 数据中心的时钟同步:保证数据中心内部各个设备之间的时钟同步,从而提高数据处理效率。

三、时钟同步的方法和协议1. 方法:a. 基于物理层的同步:利用物理特性实现同步,如使用IEEE 1588协议,通过传输介质上的同步信号实现时钟同步。

b. 基于协议的同步:通过协议传输时钟同步信息,如NTP协议、Precision Time Protocol(PTP)协议。

2. 协议:a. NTP:通过互联网进行时钟同步,采用客户端/服务器模式,基于UDP传输,可根据需求选择不同的时钟源进行同步。

b. PTP:支持高精度时钟同步,在以太网中进行时钟同步,采用主-从模式,可实现微秒级的同步精度。

四、定时技术的背景和应用1. 定时技术的背景:通信系统中的各个任务需要按照特定的时序要求执行,保证系统正常运行。

2. 定时技术的应用:用于实时通信、数据采集、数据处理等领域,确保任务按时执行。

五、定时技术的方法和实现1. 方法:a. 简单定时:根据任务特点和需求,确定任务周期和执行时间。

CAN总线位定时与同步机制的研究

CAN总线位定时与同步机制的研究定时机制是指在CAN总线上进行通信时,每个节点如何进行数据的发送和接收。

在CAN总线中,每个节点都有一个定时器来确定它发送消息的时间。

当所有节点的定时器结束倒计时并触发发送消息时,消息将以广播的方式发送到总线上。

如果两个节点的消息同时发送,总线上将会发生冲突,这时需要通过CAN总线的冲突检测和回滚机制来解决冲突。

同步机制是指在CAN总线上进行数据传输时各个节点之间如何达到同步状态。

在CAN总线中,每个节点都有一个接收定时器来检测总线上的数据传输是否正常。

当节点接收到数据时,它将计算数据传输的时间差,并将这个时间差作为自己的接收时间戳存储起来。

通过比较不同节点的接收时间戳,可以判断节点之间的时间差,从而达到同步状态。

为了研究CAN总线的定时与同步机制,需要考虑以下几个方面:1.网络拓扑结构:不同的网络拓扑结构对CAN总线的定时与同步机制有不同的影响。

例如,总线拓扑结构可以是线性的、环形的或者树形的,每种拓扑结构都需要针对不同的传输延迟和冲突检测来设计定时与同步机制。

2. 时钟精度:定时机制和同步机制的精度取决于节点的时钟精度。

为了保证系统的可靠性和实时性,需要设计高精度的时钟同步机制,例如使用全局时钟同步协议(Global Clock Synchronization Protocol)或网络时钟同步协议(Network Clock Synchronization Protocol)。

3.冲突检测和回滚机制:当两个节点同时发送数据时,会发生冲突,这时需要通过冲突检测和回滚机制来解决冲突。

冲突检测可以通过CAN总线的仲裁机制来实现,当发生冲突时,具有较高优先级的节点将会胜出,而较低优先级的节点将会回滚并等待下一个发送窗口。

4. 错误检测和纠错机制:CAN总线使用了一种具有冗余检测功能的错误检测和纠错机制,称为CRC(Cyclic Redundancy Check)校验。

Lora网络的时钟同步与定时器配置策略

Lora网络的时钟同步与定时器配置策略引言:Lora(Long Range)作为一种低功耗、长距离无线通信技术,近年来在物联网应用领域得到了广泛的应用。

然而,随着物联网设备数量的增多和覆盖范围的扩大,如何保证不同设备之间的时钟同步和定时器的准确性成为了一个亟待解决的问题。

本文将探讨Lora网络中的时钟同步和定时器配置策略。

1. 概述Lora网络的时钟同步问题Lora网络中的时钟同步是指不同设备之间的时钟频率和相位的高度一致性,以及时钟漂移的最小化。

时钟同步对于Lora网络的数据通信和协调工作至关重要,因为它直接影响到信号接收和发送的准确性,尤其是在多个设备同时工作的情况下。

目前,研究人员提出了各种各样的时钟同步方法,包括基于GPS的全局时钟同步、基于从节点的自适应时钟同步等。

2. GPS同步在Lora网络中的应用一种常见的解决方案是使用GPS同步来实现Lora网络中的时钟同步。

GPS同步可以通过接收卫星发射的定位信息,从而获得高精度的全局时钟。

在这种方案中,Lora设备可以通过与GPS模块进行硬件连接或软件接口来获取GPS的时间信息,并以此同步其本地时钟。

利用GPS同步的方法能够实现高度准确的时钟同步,但同时也带来了一定的成本和复杂性。

3. 基于从节点的自适应时钟同步除了GPS同步,基于从节点的自适应时钟同步也被广泛应用于Lora网络中的时钟同步。

在这种方案中,设备之间通过周期性交换时间信息来实现时钟同步。

具体而言,一个设备作为主节点,周期性地广播自己的时间信息,其他设备则作为从节点,接收主节点的时间信息,并根据接收到的时间信息来调整本地时钟,从而实现同步。

这种方法的好处是不需要额外的硬件支持,且成本较低,但在实际应用中需要注意时延和丢包对时钟同步的影响。

4. Lora网络中的定时器配置策略对于Lora网络中的设备,合理的定时器配置策略能够提高网络的性能和稳定性。

定时器的配置涉及到设备的休眠和唤醒时间、传输窗口的设置以及数据发送的时机等。

PXI定时与同步技术详解

37

/china

外部源

/china

板卡1 板卡2 板卡3

9

时间

定时误差来源

• 抖动(Jitter)

− 抖动是时钟周期之间(两次采 样之间)的微小差别

− 在时钟路径上添加各种元器件 均会导致抖动

• 稳定性

− 易受温度、老化等变化因素影 响

• 精度

− 振荡器产生的频率不是绝对精 确的频率

− 评价单位有ppm(百万分之一) 和ppb(十亿分之一)

− 操作同时发生,但无须严格同步

• 同步测量

− 测量是相关的

/china

3

为什么需要同步?

• 保证测量的精度

• 多通道间的相位误差要求 • 高速的激励-响应测试 • 后续处理中需要进行数据关联性分析

• 实现复杂的分布式测量和控制应用

• 分布式的I/O • 分布式的控制

/china

4

需要同步的典型应用

• 结构健康监测 (SHM)

• 在大型结构/建筑的多个区域测量和记 录振动(应变)等信号

• 在后续的处理需要分析数据的关联性 • 10 Hz带宽的振动信号要求大约毫秒级

的同步

• 噪声源定位

• 麦克风阵列 • 多通道、分布式的同步采集 • 纳秒级的同步需求和专用的定时硬件

/china

PXI-6652 PXIe-6672

IEEE-1588

(PXI-6683 PXI-6683H)

GPS

(PXI-6683/6683H)

<10-4m 10-2m

100m

101m 102m 地域跨度

NTP (Standard Ethernet)

103m 104m 105m

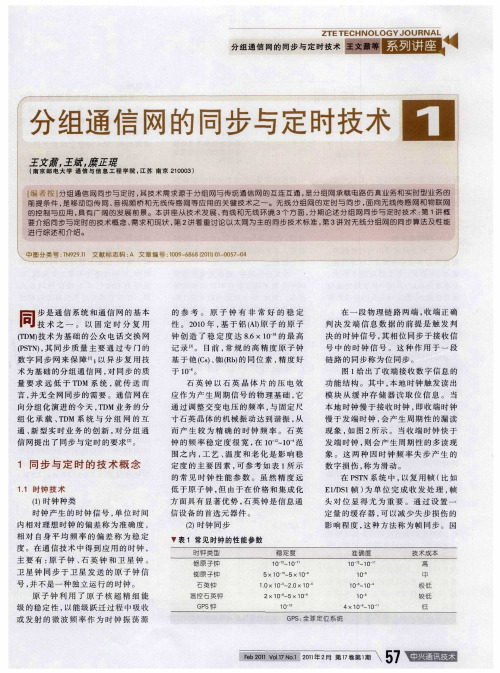

分组通信网的同步与定时技术(1)

方 面具 有 显 著 优 势 , 英 钟 是 信 息 通 石

信 设 备 的 首选 元 器 件 。 () 钟 同步 2时

V表 1 常见 时钟 的 性 能参 数

度 。在 通 信 技 术 中得 到 应 用 的 时钟 , 主要 有 : 子钟 、 英 钟 和卫 星钟 。 原 石 卫 星 钟 同 步 于 卫 星 发 送 的 原 子 钟 信

0 I

堡 竺 塑:

兰 !! ! ! : : 二竺! !竺 竺! ! : :

/ /

步 是 通 信 系 统 和通 信 网 的 基 本 技 术 之 一 。 以 固 定 时 分 复 用

(D 技 术 为基 础 的公 众 电 话 交 换 网 T M)

的 参 考 。 原 子 钟 有 非 常 好 的 稳 定

分 组 通 信 网 的 同 步 与 定

分组通信 网的同步与定时技术

王文鼐。 王斌 。 糜正琨

( 京 邮 电大 学 通信 与 信 息 工 程 学 院 . 南 江苏 南 京 2 0 0 1 0 3)

} 救 j 组 通信 网 同步 与 定 时 , 技术 需 求 源 于 分 组 网 与 传 统 通 信 网 的互 连 互 通 , 分 组 网承 载 电路 仿 真业 务 和 实 时 型业 务 的 分 其 是

前 提条 件 , 移 动 回 传 网 、 视 频 桥 和 无 线 传 感 网 等 应 用 的 关 键 技 术 之 ~ 。无 线 分 组 网 的 定时 与 同步 , 向 无线 传 感 网 和 物 联 网 是 音 面 的 控制 与 应 用 , 有 厂 阔 的 发 展 前 景 。 本 讲座 从 技 术发 展 、 线 和 无 线 环 境 3个 方 面 , 期论 述 分组 网 同 步与 定时 技 术 : 1 概 具 有 分 第 讲 要介 绍 同步 与 定 时 的技 术 概 念 、 求 和 现状 , 2 着 重 讨 论 以 太 网 为 主 的 同步 技 术 标 准 , 3讲 对无 线 分组 网 的 同 步 算 法 及性 能 需 第 讲 第

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

在数字通信系统中,发端按照确定的时 间顺序,逐个传输数码脉冲序列中的每个码 元。

而在接收端必须有准确的抽样判决时刻 才能正确判决所发送的码元,因此,接收端 必须提供一个确定抽样判决时刻的定时脉冲 序列。

这个定时脉冲序列的重复频率必须与发 送的数码脉冲序列一致,同时在最佳判决时 刻(或称为最佳相位时刻)对接收码元进行 抽样判决。

2.精度(相位误差)

精度是指提取的同步载波与载波标准比 较,它们之间的相位误差大小。

例如需要的同步载波为cosct,提取的 同步载波为cos(ct+),就是相位误差, 应尽量小。

通常习惯地将这种误差分为稳态相位误 差和随机相位误差。

3.同步建立时间ts

对ts的要求是越短越好,这样同步建立

得快。

4.同步保持时间tc

可以把在接收端产生这样的定时脉冲序 列称为码元同步,或称位同步。

实现位同步的方法和载波同步类似,也 有直接法(自同步法)和插入导频法(外同 步法)两种,而在直接法中也分为滤波法和 锁相法。

8.3.1 插入导频法

为了得到码元同步的定时信号,首先要 确定接收到的信息数据流中是否包含有位定 时的频率分量。

学习重点

定时与同步的概念 三种同步的相互关系 载波同步的概念及工作原理 位同步的概念及工作原理 帧同步的概念及工作原理 网同步的概念及作用

同步是通信系统中一个重要的技术问题。 通信系统能否有效地、可靠地工作,在很大 程度上依赖于良好的同步系统。

同步问题是进行数字通信的前提和基础, 同步性能的好坏直接影响通信系统的性能。

下面分两种情况讨论。

(1)模拟调制信号 (2)数字调制信号

图8-2 数字信号的导频插入方式(只考虑正向频谱)

图8-3 导频插入与发送端、接收端框图

2.时域插入导频法

除了在频域插入导频的方法以外,还可 以在时域插入导频以传送和提取同步载波。

时域插入导频法中对被传输的数据信号 和导频信号在时间上加以区别,具体分配情 况如图8-4(a)所示。

图8-10 滤波法原理框图 图8-11 波形变换后的波形

2.采用锁相法提取位同步

与载波同步的提取类似,把采用锁相环 来提取位同步信号的方法称为锁相法。

在数字通信中,这种锁相电路常采用数 字锁相环来实现。

采用锁相法提取位同步原理方框图如图 8-12所示,它由高稳定度振荡器(晶振)、 分频器、相位比较器和控制电路组成。

8.2.2 直接法(自同步法)

有些信号(如抑制载波的双边带信号等) 虽然本身不包含载波分量,但对该信号进行 某些非线性变换以后,就可以直接从中提取 出载波分量来,这就是直接法提取同步载波 的方法。

下面介绍几种直接提取载波的方法。

1.平方变换法

由式(8-2)可以看出,虽然前面假设

x(t)中无直流分量,但x2(t)却一定有直流分 量,这是因为x2(t)必为大于等于0的数,因 此,x2(t)的均值必大于0,而这个均值就是 x2(t)的直流分量,这样r(t)的第二项中就包

这些信号本身不含载频或含有载频不易 取出,对于这些信号可以用插入导频法。

插入导频是在已调信号的频谱中再加入 一个低功率的频谱(其对应的正弦波即为导 频信号)。

在接收端可以利用窄带滤波器把它提取 出来,经过适当的处理形成接收端的相干载 波。

插入导频的方法很多,但基本原理都是 相似的。

插入导频的位置应该在信号频谱为零, 否则导频与信号频谱成分重叠,接收时不易 取出。

含2fc频率的分量。

图8-5 平方变换法提取载波

2.平方环法

为了改善平方变换的性能,可以在平方 变换法的基础上,把窄带滤波器用锁相环替 代,构成如图8-6所示的框图,这样就实现了 平方环法提取载波。

由于锁相环具有良好的跟踪、窄带滤波 和记忆性能,因此平方环法比一般的平方变 换法具有更好的性能,因而得到广泛的应用。

4.网同步

现代通信需要在多点之间相互连接构成 通信网。

在一个通信网中,往往需要把各个方向 传来的信息,按不同目的进行分路、合路和 交换。

为了有效地完成这些功能,必须实现网 同步。

随着数字通信的发展,特别是计算机通 信的发展,多点(或多用户)之间的通信和 数据交换构成了数字通信网。

为了保证数字通信网稳定可靠地进行通 信和交换,整个数字通信网内交换必须有一 个统一的时间标准,即整个网络必须同步地 工作,这就是网同步需要讨论的问题。

第8章 定时与同步

8.1 数字通信系统中同步的作用 8.2 载波同步 8.3 位同步 8.4 帧同步 8.5 网同步 本章内容小结

学习要点

定时与同步的基本概念 同步在通信系统的位置 载波同步的概念、特点及工作原理 位同步的概念、特点及工作原理 帧同步的概念、特点及工作原理 网同步的概念及方法

2.插入导频法的优缺点

(1)有单独的导频信号,一方面可以提 取同步载波,另一方面可以利用它作为自动 增益控制。

(2)有些不能用直接法提取同步载波的 调制系统只能用插入导频法。

(3)插入导频法要多消耗一部分不带信 息的功率。

与直接法比较,在总功率相同条件下实 际信噪功率比要小一些。

8.3 位同步

8.3.1 插入导频法 8.3.2 自同步法 8.3.3 位同步系统的性能指标

除了按照功用来区分同步外,还可以按 照传输同步信息方式的不同,把同步分为外 同步法(插入导频法)和自同步法(直接法) 两种。

外同步法是指发送端发送专门的同步信 息,接收端把这个专门的同步信息检测出来 作为同步信号的方法;自同步法是指发送端 不发送专门的同步信息,而在接收端设法从 收到的信号中提取同步信息的方法。

如果存在此分量,就可以利用滤波器从 信息数据流中把位定时信息提取出来。

若基带信号为随机的二进制不归零码序 列,这种信号本身不包含位同步信号,为了 获得位同步信号需在基带信号中插入位同步 的导频信号,或者对该基带信号进行某种码 型变换以得到位同步信息。

插入导频法与载波同步时的插入导频法 类似,它也是在基带信号频谱的零点插入所 需的导频信号,如图8-8(a)所示。

8.1.2 同步在数字通信系统中的位置

当通信在点对点之间完成了载波同步、 位同步和帧同步之后,就可以进行可靠的通 信了。

为了较深刻地认识这三种同步在数字通 信系统中的位置,图8-1所示给出了两路数字 电话通信系统框图,图8-1(a)所示为发送 部分,图8-1(b)所示为接收部分。

图8-1 两路数字电话系统

对tc的要求是越短越好,这样一旦建立

同步以后可以保持较长的时间。

8.2.4 两种载波同步方法的比较

1.直接法的优缺点

(1)不占用导频功率,信噪功率比可以 大一些。

(2)可以防止插入导频法中导频和信号 间由于滤波不好而引起的互相干扰,也可以 防止信道不理想引起导频相位的误差。

(3)有的调制系统不能用直接法(如 SSB系统)。

1.采用滤波法提取位同步

根据基带信号的谱分析可知,对于不归 零的随机二进制序列,不能直接从其中滤出 位同步信号。

但是,若对该信号进行某种变换,例如 变成单极性归零脉冲后,则该序列中就有

f = 1/Tb的位同步信号分量,经一个窄带滤

波器,可滤出此信号分量,再将它通过一移 相器调整相位后,就可以形成位同步脉冲, 这种方法的方框图如图8-10所示。

在发送部分,假设时钟为192kHz,两路

抽样(图中的SL1,SL2)频率均为8kHz,每个 抽样信号编码为8bit(D1,D2),各占1个时

隙(TS1,TS2)。 为了保证帧同步,采用连贯式插入法在

时隙TS0处插入帧同步码(FS):1110010。

经过复接后的An为一个时分复用基带PCM

信号,码元速率为192kbit/s,帧长为125s, 然后,再经过差分编码、2PSK调制,就可以

同步的种类很多,按照同步的功用来分, 数字通信系统中的同步可以分为载波同步、 位同步(码元同步)、群同步(帧同步)和 网同步(数字通信网中用)四种,下面分别 加以说明。

1.载波同步

当采用同步解调或相干检测时,接收端 需要提供一个与发射端调制载波同频同相的 相干载波,而这个相干载波的获取就称为载 波同步(或载波提取)。

2.位同步

位同步又称为码元同步。 不论是基带传输,还是频带传输,都需 要位同步。 因为在数字通信系统中,信息是一串相 继的信号码元的序列,解调时常需要知道每 个码元的起止时刻,以便判决。 例如用取样判决器对信号进行取样判决 时,均应对准每个码元最大值的位置。

因此,需要在接收端产生一个“码元定 时脉冲序列”,这个定时脉冲序列的重复频 率要与发送端的码元速率相同,相位(位置) 要对准最佳取样判决位置(时刻)。

若经某种相关编码处理后的基带信号,入 导频信号就应在1/2Tb处,如图8-8(b)所示。

图8-8 插入导频法频谱图

图8-9 位同步插入导频法方框图

8.3.2 自同步法

当系统的位同步采用自同步方法时,发 端不需要专门发送导频信号,而直接从数字 信号中提取位同步信号,这种方法在数字通 信中经常采用,而自同步法具体又可分为滤 波法和锁相法。

这样的一个码元定时脉冲序列就被称为 “位同步脉冲”(或“码元同步脉冲”), 而把位同步脉冲的取得称为位同步提取。

3.帧同步

数字通信中的信息数字流,总是用若干 码元组成一个“字”,又用若干“字”组成 一“句”。

因此,在接收这些数字流时,同样也必 须知道这些“字”、“句”的起止时刻。

而在接收端产生与“字”、“句”起止 时刻相一致的定时脉冲序列,就被称为“字” 同步和“句”同步,统称为帧同步(或群同 步)。

载波同步的实现方案与采用的数字调制 方式有一定的关系。

8.2.1 插入导频法(外同步法)

插入导频法分为两种:一种是在发送信 息的频谱中或频带外插入相关的导频信号, 称为频域插入导频法;另一种是在一定的时 段上传送载波信息,称为时域导频法。