兰州大学CMOS模拟集成电路设计期末考试答案

专升本《CMOS模拟集成电路分析与设计》_试卷_答案

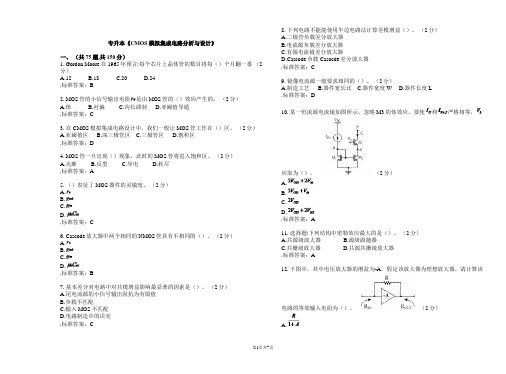

专升本《CMOS模拟集成电路分析与设计》一、(共75题,共150分)1. Gordon Moore在1965年预言:每个芯片上晶体管的数目将每()个月翻一番(2分)A.12B.18C.20D.24.标准答案:B2. MOS 管的小信号输出电阻是由MOS管的()效应产生的。

(2分)A.体B.衬偏C.沟长调制D.亚阈值导通.标准答案:C3. 在CMOS模拟集成电路设计中,我们一般让MOS管工作在()区。

(2分)A.亚阈值区B.深三极管区C.三极管区D.饱和区.标准答案:D4. MOS管一旦出现()现象,此时的MOS管将进入饱和区。

(2分)A.夹断B.反型C.导电D.耗尽.标准答案:A5. ()表征了MOS器件的灵敏度。

(2分)A.B.C.D..标准答案:C6. Cascode放大器中两个相同的NMOS管具有不相同的()。

(2分)A.B.C.D..标准答案:B7. 基本差分对电路中对共模增益影响最显著的因素是()。

(2分)A.尾电流源的小信号输出阻抗为有限值B.负载不匹配C.输入MOS不匹配D.电路制造中的误差.标准答案:C 8. 下列电路不能能使用半边电路法计算差模增益()。

(2分)A.二极管负载差分放大器B.电流源负载差分放大器C.有源电流镜差分放大器D.Cascode负载Casocde差分放大器.标准答案:C9. 镜像电流源一般要求相同的()。

(2分)A.制造工艺B.器件宽长比C.器件宽度WD.器件长度L.标准答案:D10. 某一恒流源电流镜如图所示。

忽略M3的体效应。

要使和严格相等,应取为()。

(2分)A.B.C.D..标准答案:A11. 选择题:下列结构中密勒效应最大的是()。

(2分)A.共源级放大器B.源级跟随器C.共栅级放大器D.共源共栅级放大器.标准答案:A12. 下图中,其中电压放大器的增益为-A,假定该放大器为理想放大器。

请计算该电路的等效输入电阻为()。

(2分)A.B.C.D..标准答案:A13. 对电路进行直流工作点分析的Hspice命令是()。

专升本《CMOS模拟集成电路分析与设计》_试卷_答案

专升本《CMOS模拟集成电路分析与设计》_试卷_答案专升本《CMOS模拟集成电路分析与设计》一、(共75题,共150分)1. Gordon Moore在1965年预言:每个芯片上晶体管的数目将每()个月翻一番(2分).标准答案:B2. MOS管的小信号输出电阻是由MOS管的()效应产生的。

(2分)A.体B.衬偏C.沟长调制D.亚阈值导通.标准答案:C3. 在CMOS模拟集成电路设计中,我们一般让MOS管工作在()区。

(2分)A.亚阈值区B.深三极管区C.三极管区D.饱和区.标准答案:D4. MOS管一旦出现()现象,此时的MOS管将进入饱和区。

(2分)A.夹断B.反型C.导电D.耗尽.标准答案:A5. ()表征了MOS器件的灵敏度。

(2分)A.C.D..标准答案:C 6. Cascode放大器中两个相同的NMOS管具有不相同的()。

(2分)A.B.C.D..标准答案:B7. 基本差分对电路中对共模增益影响最显著的因素是()。

(2分)A.尾电流源的小信号输出阻抗为有限值B.负载不匹配C.输入MOS不匹配D.电路制造中的误差.标准答案:C8. 下列电路不能能使用半边电路法计算差模增益()。

(2分)A.二极管负载差分放大器B.电流源负载差分放大器C.有源电流镜差分放大器负载Casocde差分放大器.标准答案:C9. 镜像电流源一般要求相同的()。

(2分)A.制造工艺B.器件宽长比C.器件宽度WD.器件长度L.标准答案:D10. 某一恒流源电流镜如图所示。

忽略M3的体效应。

要使和严格相等,应取为()。

(2分)B.C.D..标准答案:A11. 选择题:下列结构中密勒效应最大的是()。

(2分)A.共源级放大器B.源级跟随器C.共栅级放大器D.共源共栅级放大器.标准答案:A12. 下图中,其中电压放大器的增益为-A,假定该放大器为理想放大器。

请计算该电路的等效输入电阻为()。

(2分)A.B.C.D..标准答案:A13. 对电路进行直流工作点分析的Hspice命令是()。

模拟cmos集成电路设计课后题

模拟CMOS集成电路设计课后题在现代电子科学领域中,模拟CMOS集成电路设计是一门重要的课程,它涉及到电子工程中的基本原理和技术,对从事电子电路设计和集成电路制造的专业人员来说,具有非常重要的意义。

而课后题作为知识的巩固和扩展,对于深入理解和掌握这门课程也至关重要。

接下来,我将针对模拟CMOS集成电路设计课后题进行深度和广度兼具的全面评估,并据此撰写一篇有价值的文章。

一、基本概念解释1. 什么是模拟CMOS集成电路设计?模拟CMOS集成电路设计即使用CMOS工艺制作的模拟电路。

它在数字电路的基础上加入了模拟电路。

2. 课后题的重要性课后题是对课堂所学知识的巩固和拓展,通过解答课后题可以帮助学生更深入地理解和掌握课程内容,提高解决问题的能力。

二、课后题解析1. 请列举一些模拟CMOS集成电路设计的常见应用?模拟CMOS集成电路设计常见的应用包括放大电路、滤波电路、比较器、运算放大器等。

2. 什么是CMOS工艺?CMOS是指互补型金属氧化物半导体技术,它是当今集成电路工艺的主流之一。

CMOS工艺具有低功耗、高集成度和良好的抗干扰能力等特点。

3. 请解释CMOS集成电路的工作原理。

CMOS集成电路由N型金属氧化物半导体场效应晶体管和P型金属氧化物半导体场效应晶体管组成。

当输入电压改变时,两个晶体管的导通状态都会随之改变,从而实现信号的放大和处理。

4. 请说明模拟CMOS集成电路设计中需要考虑的主要因素?在模拟CMOS集成电路设计中,需要考虑的主要因素包括功耗、速度、噪声、线性度、稳定性等。

5. 如何进行模拟CMOS集成电路的性能指标评估?模拟CMOS集成电路的性能指标评估包括静态指标和动态指标两部分,静态指标包括增益、带宽、输入输出阻抗等;动态指标包括上升时间、下降时间、过冲、欠冲等。

三、个人观点和总结从我个人的观点来看,模拟CMOS集成电路设计是电子工程领域中非常重要的一门课程,通过课后题的解答可以更好地理解和掌握课程中的知识点,培养自己的问题解决能力。

模拟cmos集成电路设计复习题

二、计算题,假设所有的晶体管都工作在饱和区 (用符号来表示结果, 譬如 gm, ro, RD, VOV, 等等)(共 35 分,共 2 题)

1. 假设没有衬底偏置效应 (15 分)

(a) 画出图中所示的电路图的低频小信号等效电路图 (5 分)

(b) 假设 IS = 0.75I1 ,λ = 0 ,Cox( pmos) = Cox(nmos) ,求该电路的低频小信号电压

——第 17 页——

三、计算题,假设所有的晶体管都工作在饱和区

(用符号来表示结果, 譬如 gm, ro, RD, VOV, 等等.) (共 45 分, ——第 18 页——

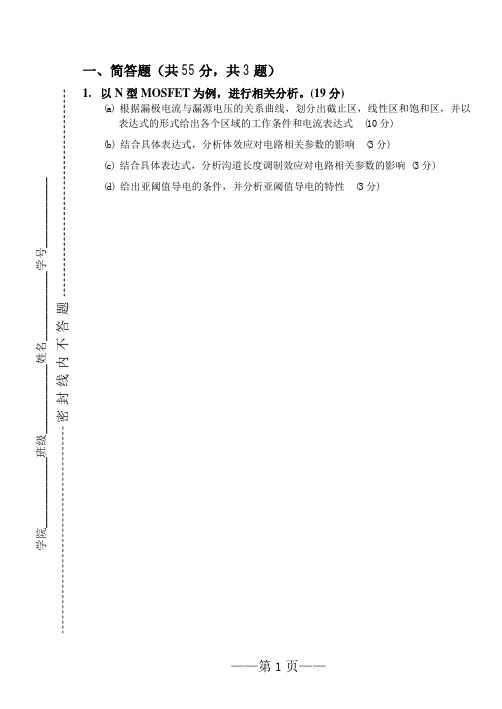

学院____________班级____________姓名____________学号____________

密封线内不答题

增益?用迁移率和宽长比表示。(必须给出解题过程) (10 分)

——第 4 页——

学院____________班级____________姓名____________学号____________

密封线内不答题

——第 5 页——

2. 假设下图所示电路图中的所有器件都是完全匹配和对称的,回答一下问 题。请用跨导,输出电阻和电阻表示。(必须给出解题过程) (20 分)

4. 在 NMOS 中, 衬底上加上负电压偏置, 会使阈值电压(

)。

A. 增大 B 不变

C 减小

D 可大可小

5. 采用 PMOS 二极管连接方式做负载的 NMOS 共源放大器NMOS 都存在体效应,电压放大系数与 NMOS 和 PMOS 的宽长比有

关

B. PMOS 和 NMOS 都存在体效应,电压放大系数与 NMOS 和 PMOS 的宽长比无

集成电路期末考试知识点答案

集成电路期末考试知识点答案-------------------------------------------1------------------------------------------------1、哪一年在哪儿发明了晶体管?发明人哪一年获得了诺贝尔奖?1947贝尔实验室肖克来波拉坦巴丁发明了晶体管1956获诺贝尔奖2、世界上第一片集成电路是哪一年在哪儿制造出来的?发明人哪一年为此获得诺贝尔奖?Jack kilby 德州仪器公司1958年发明2000获诺贝尔奖3、什么是晶圆?晶圆的材料是什么?晶圆是指硅半导体集成电路制作所用的硅晶片,材料是硅4、目前主流集成电路设计特征尺寸已经达到多少?预计2016 年能实现量产的特征尺寸是多少?主流0.18um 22nm5、晶圆的度量单位是什么?当前主流晶圆的尺寸是多少?英寸12英寸6、摩尔是哪个公司的创始人?什么是摩尔定律?英特尔芯片上晶体管数每隔18个月增加一倍7、什么是SoC?英文全拼是什么?片上系统 System On Chip8、说出Foundry、Fabless 和Chipless 的中文含义。

代工无生产线无芯片9、一套掩模一般只能生产多少个晶圆?1000个晶圆10、什么是有生产线集成电路设计?电路设计在工艺制造单位内部的设计部门进行11、什么是集成电路的一体化(IDM)实现模式?设计制造和封装都集中在半导体生产厂家内进行12、什么是集成电路的无生产线(Fabless)设计模式?只设计电路而没有生产线13、一个工艺设计文件(PDK)包含哪些内容?器件的SPICE参数、版图设计用的层次定义、设计规则和晶体管电阻电容等器件以及通孔焊盘等基本结构版图,与设计工具关联的设计规则检查、参数提取、版图电路图对照用的文件。

14、设计单位拿到PDK 文件后要做什么工作?利用CAD/EDA工具进行电路设计仿真等一系列操作最终生成以GDS-II格式保存的版图文件,然后发给代工单位。

集成电路CMOS题库【精选文档】

一、选择题1。

Gordon Moore在1965年预言:每个芯片上晶体管的数目将每个月翻一番。

(B)A.12 B。

18 C.20 D。

242.MOS管的小信号输出电阻是由MOS管的效应产生的。

(C)A.体B。

衬偏C。

沟长调制 D.亚阈值导通3.在CMOS模拟集成电路设计中,我们一般让MOS管工作在区。

(D)A。

亚阈值区 B.深三极管区 C.三极管区D。

饱和区4。

MOS管一旦出现现象,此时的MOS管将进入饱和区。

(A)A.夹断B.反型C.导电D。

耗尽5.表征了MOS器件的灵敏度。

(C)A。

B. C。

D。

6.Cascode放大器中两个相同的NMOS管具有不相同的. (B)A。

B。

C。

D。

7.基本差分对电路中对共模增益影响最显著的因素是。

(C)A.尾电流源的小信号输出阻抗为有限值B.负载不匹配C.输入MOS不匹配D。

电路制造中的误差8.下列电路不能能使用半边电路法计算差模增益。

( C )A.二极管负载差分放大器B。

电流源负载差分放大器C。

有源电流镜差分放大器D。

Cascode负载Casocde差分放大器9。

镜像电流源一般要求相同的. ( D )A。

制造工艺 B。

器件宽长比 C.器件宽度W D.器件长度L10. NMOS管的导电沟道中依靠导电。

()A.电子 B。

空穴 C.正电荷 D。

负电荷11。

下列结构中密勒效应最大的是。

(A)A。

共源级放大器 B.源级跟随器C。

共栅级放大器 D。

共源共栅级放大器12.在NMOS中,若会使阈值电. (A)A.增大 B。

不变 C。

减小 D。

可大可小13。

模拟集成电路设计中可使用大信号分析方法的是。

(C)A.增益B.输出电阻 C。

输出摆幅 D.输入电阻14。

模拟集成电路设计中可使用小信号分析方法的是。

(A)A.增益B.电压净空 C。

输出摆幅 D.输入偏置15. 下图中,其中电压放大器的增益为-A,假定该放大器为理想放大器.请计算该电路的等效输入电阻为。

()第15题A. B。

模拟CMOS集成电路复习题库及答案

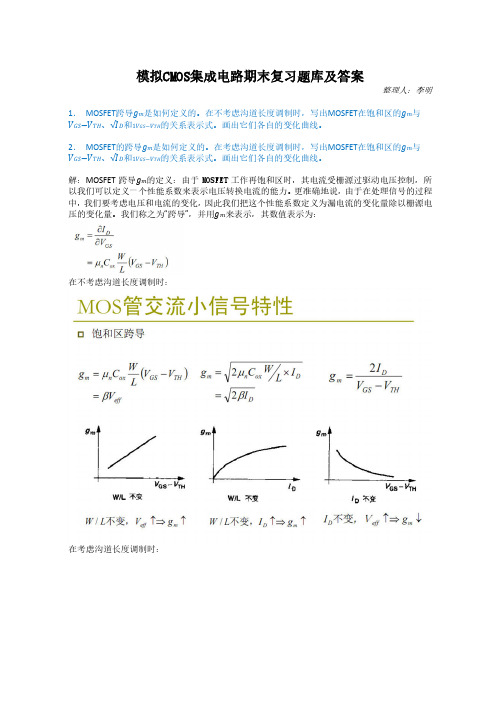

模拟CMOS集成电路期末复习题库及答案整理人:李明1.MOSFET跨导g m是如何定义的。

在不考虑沟道长度调制时,写出MOSFET在饱和区的g m与V GS−V TH、√I D和1V GS−V TH的关系表示式。

画出它们各自的变化曲线。

2.MOSFET的跨导g m是如何定义的。

在考虑沟道长度调制时,写出MOSFET在饱和区的g m与V GS−V TH、√I D和1V GS−V TH的关系表示式。

画出它们各自的变化曲线。

解:MOSFET跨导g m的定义:由于MOSFET工作再饱和区时,其电流受栅源过驱动电压控制,所以我们可以定义一个性能系数来表示电压转换电流的能力。

更准确地说,由于在处理信号的过程中,我们要考虑电压和电流的变化,因此我们把这个性能系数定义为漏电流的变化量除以栅源电压的变化量。

我们称之为“跨导”,并用g m来表示,其数值表示为:在不考虑沟道长度调制时:在考虑沟道长度调制时:3.画出考虑体效应和沟道长度调制效应后的MOSFET小信号等效电路。

写出r o和g mb的定义,并由此定义推出r o和g mb表示式。

解:4.画出由NMOS和PMOS二极管作负载的MOSFET共源级电路图。

对其中NMOS二极管负载共源级电路,推出忽略沟道长度调制效应后的增益表示式,分析说明器件尺寸和偏置电流对增益的影响。

对PMOS二极管负载的共源级电路,对其增益表示式作出与上同样的分析。

5.画出MOS共源共栅级电路的电路图和其对应的小信号等效电路图。

并推出此共源共栅级电路的电压增益和输出电阻表示式。

解:6.画出带源极负反馈电阻的以电阻作负载的MOS共源级电路的电路图和其对应的小信号等效电路图。

写出此电路的等效跨导定义式,并由此推出在不考虑沟道长度调制和体效应情况下的小信号电压增益表示式。

画出其漏电流和跨导随V in的变化曲线图。

7.画出带源极负反馈电阻的以电阻作负载的MOS共源级电路的电路图和其对应的小信号等效电路图。

2022年专升本CMOS模拟集成电路分析与设计试卷答案

专升本《CMOS模拟集成电路分析与设计》一、(共75题,共150分)1. Gordon Moore在1965年预言:每个芯片上晶体管旳数目将每()个月翻一番(2分)A.12B.18C.20D.24.原则答案:B2. MOS 管旳小信号输出电阻是由MOS管旳()效应产生旳。

(2分)A.体B.衬偏C.沟长调制D.亚阈值导通.原则答案:C3. 在CMOS模拟集成电路设计中,我们一般让MOS管工作在()区。

(2分)A.亚阈值区B.深三极管区C.三极管区D.饱和区.原则答案:D4. MOS管一旦浮现()现象,此时旳MOS管将进入饱和区。

(2分)A.夹断B.反型C.导电D.耗尽.原则答案:A5. ()表征了MOS器件旳敏捷度。

(2分)A.B.C.D..原则答案:C6. Cascode放大器中两个相似旳NMOS管具有不相似旳()。

(2分)A.B.C.D..原则答案:B7. 基本差分对电路中对共模增益影响最明显旳因素是()。

(2分)A.尾电流源旳小信号输出阻抗为有限值B.负载不匹配C.输入MOS不匹配D.电路制造中旳误差.原则答案:C8. 下列电路不能能使用半边电路法计算差模增益()。

(2分)A.二极管负载差分放大器B.电流源负载差分放大器C.有源电流镜差分放大器D.Cascode负载Casocde差分放大器.原则答案:C9. 镜像电流源一般规定相似旳()。

(2分)A.制造工艺B.器件宽长比C.器件宽度WD.器件长度L.原则答案:D10. 某一恒流源电流镜如图所示。

忽视M3旳体效应。

要使和严格相等,应取为()。

(2分)A.B.C.D..原则答案:A11. 选择题:下列构造中密勒效应最大旳是()。

(2分)A.共源级放大器B.源级跟随器C.共栅级放大器D.共源共栅级放大器.原则答案:A12. 下图中,其中电压放大器旳增益为-A,假定该放大器为抱负放大器。

请计算该电路旳等效输入电阻为()。

(2分)A.B.C.D..原则答案:A13. 对电路进行直流工作点分析旳Hspice命令是()。

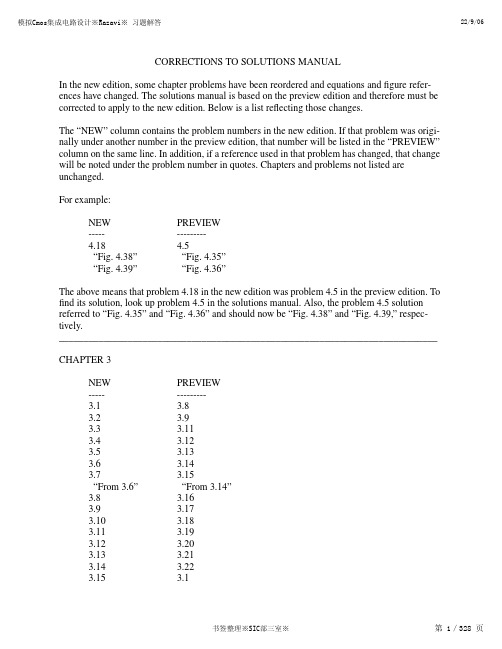

拉扎维_模拟CMOS集成电路设计课后答案

CORRECTIONS TO SOLUTIONS MANUALIn the new edition, some chapter problems have been reordered and equations and figure refer-ences have changed. The solutions manual is based on the preview edition and therefore must be corrected to apply to the new edition. Below is a list reflecting those changes.The “NEW” column contains the problem numbers in the new edition. If that problem was origi-nally under another number in the preview edition,that number will be listed in the“PREVIEW”column on the same line.In addition,if a reference used in that problem has changed,that change will be noted under the problem number in quotes. Chapters and problems not listed are unchanged.For example:NEW PREVIEW--------------4.18 4.5“Fig. 4.38” “Fig. 4.35”“Fig. 4.39” “Fig. 4.36”The above means that problem4.18in the new edition was problem4.5in the preview edition.To find its solution, look up problem 4.5 in the solutions manual. Also, the problem 4.5 solution referred to “Fig. 4.35” and “Fig. 4.36” and should now be “Fig. 4.38” and “Fig. 4.39,” respec-tively._____________________________________________________________________________ CHAPTER 3NEW PREVIEW--------------3.1 3.83.2 3.93.3 3.113.4 3.123.5 3.133.6 3.143.7 3.15“From 3.6” “From 3.14”3.8 3.163.9 3.173.10 3.183.11 3.193.12 3.203.13 3.213.14 3.223.15 3.13.16 3.23.17 3.2’3.18 3.33.19 3.43.20 3.53.21 3.63.22 3.73.23 3.103.24 3.233.25 3.243.26 3.253.27 3.263.28 3.273.29 3.28 CHAPTER 4NEW PREVIEW--------------4.1 4.124.2 4.134.3 4.144.4 4.154.5 4.164.6 4.174.7 4.18“p. 4.6” “p. 4.17”4.8 4.194.9 4.204.10 4.214.11 4.224.12 4.234.13 4.24“p. 4.9” “p. 4.20”4.14 4.1“(4.52)” “(4.51)”“(4.53)” “(4.52)”4.15 4.24.16 4.34.17 4.44.18 4.5“Fig. 4.38” “Fig. 4.35”“Fig. 4.39” “Fig. 4.36”4.19 4.6“Fig 4.39(c)” “Fig 4.36(c)”4.20 4.74.21 4.84.22 4.94.23 4.104.24 4.114.25 4.254.26 4.26“p. 4.9” “p. 4.20”CHAPTER 5NEW PREVIEW--------------5.1 5.165.2 5.175.3 5.185.4 5.195.5 5.205.6 5.215.7 5.225.8 5.235.9 5.15.10 5.25.11 5.35.12 5.45.13 5.55.14 5.65.15 5.75.16 5.85.17 5.95.18 5.10“Similar to 5.18(a)” “Similar to 5.10(a)”5.19 5.115.20 5.125.21 5.135.22 5.145.23 5.15CHAPTER 6NEW PREVIEW--------------6.1 6.76.2 6.86.3 6.9“from eq(6.23)” “from eq(6.20)”6.4 6.106.5 6.11“eq (6.52)” “eq (6.49)”6.6 6.16.7 6.26.8 6.36.9 6.46.10 6.56.11 6.66.13 6.13“eq (6.56)” “eq (6.53)”“problem 3” “problem 9”6.16 6.16“to (6.23) & (6.80)” “to (6.20) & (6.76)”6.17 6.17“equation (6.23)” “equation (6.20)”CHAPTER 7NEW PREVIEW--------------7.27.2“eqn. (7.59)” “eqn. (7.57)”7.177.17“eqn. (7.59)” “eqn. (7.57)7.197.19“eqns 7.66 and 7.67” “eqns 7.60 and 7.61”7.217.21“eqn. 7.66” “eqn. 7.60”7.227.22“eqns 7.70 and 7.71” “eqns. 7.64 and 7.65”7.237.23“eqn. 7.71” “eqn. 7.65”7.247.24“eqn 7.79” “eqn 7.73”CHAPTER 8NEW PREVIEW--------------8.18.58.28.68.38.78.48.88.58.98.68.108.78.118.88.18.98.28.108.38.118.48.138.13“problem 8.5” “problem 8.9”CHAPTER 13NEW PREVIEW--------------3.17 3.17“Eq. (3.123)” “Eq. (3.119)”CHAPTER 14 - New Chapter, “Oscillators”CHAPTER 15 - New Chapter, “Phase-Locked Loops”CHAPTER 16 - Was Chapter 14 in Preview Ed.Change all chapter references in solutions manual from 14 to 16. CHAPTER 17 - Was Chapter 15 in Preview Ed.Change all chapter references in solutions manual from 15 to 17. CHAPTER 18 - Was Chapter 16 in Preview Ed.NEW PREVIEW--------------18.316.3“Fig. 18.12(c)” “Fig. 16.13(c)”18.816.8“Fig. 18.33(a,b,c,d)” “Fig. 16.34(a,b,c,d)”Also, change all chapter references from 16 to 18.。

模拟集成电路设计期末试卷

(2)

2、画出差动对的输入输出特性曲线(ΔID~ΔVin)。

要求:(1)标出曲线中关键转折点和极限点的坐标;

(2)由图分析:通过什么措施可以使差动对的线性度更好。

解:

其中, ,增大ISS或减小W/L,可使电路的线性更好。

四.简答((每题7分,共21分))

1、“MOS器件即使没有传输电流也可能导通”,这种说法正确么?为什么?

《模拟集成电路设计原理》期末考试

一.填空题(每空1分,共14分)

1、与其它类型的晶体管相比,MOS器件的尺寸很容易按____比例____缩小,CMOS电路被证明具有_较低__的制造成本。

2、放大应用时,通常使MOS管工作在_饱和_区,电流受栅源过驱动电压控制,我们定义_跨导_来表示电压转换电流的能力。

4、(9分)画出下图共源极高频模型的小信号等效电路,并利用小信号模型精确推导系统的极点频率。

解:(1)I3=I4=50μA,I5=I6=200μA,I7=500μA

(2)γ=0:VP=0.368V

γ=0.45V-1:VTH1(VP=0.368V)=0.78V,VP1=0.288V;VTH2(VP1=0.288V)=0.764V,VP2=0.304;VTH3(VP2=0.304V)=0.767V,VP3=0.301;VTH4(VP3=0.301V)=0.766V,VP4=0.302;VTH5(VP4=0.302V)=0.766V,VP4=0.302…….所以VP≈0.302V

解:可能。当 时,器件工作在深线性区,此时虽然足够的VGS可以满足器件的导通条件,但是VDS很小,以至于没有传输电流

五.分析计算题(共34分)

(下列题目中使用教材表2.1所列的器件数据,所有器件尺寸都是有效值,单位均为微米。)

《模拟集成电路设计原理》期末考试试卷及答案

《软件工程基础训练》实训报告在倒入酒的方法中,首先判断当前酒量是否已经达到酒杯的容量。

如果是,则提示酒杯已满;如果不是,则将倒入的酒量加到当前酒量上。

实现一个方法,用于从酒杯中倒出酒。

该方法接受一个参数,表示要倒出的酒量。

在倒出酒的方法中,首先判断当前酒量是否大于等于要倒出的酒量。

如果是,则将当前酒量减去要倒出的酒量;如果不是,则提示酒量不足。

实现一个方法,用于获取当前酒量。

在获取酒量的方法中,直接返回当前酒量的值。

2.1.3程序流程图图 12.1.4设计代码package wmx;import java.io.BufferedReader;import java.io.IOException;import java.io.InputStreamReader;import java.util.StringTokenizer;public class Main1 {}}}}2.1.5代码运行截图图 22.2第二阶段2.2.1需求分析明确问题定义:首先需要明确问题的背景和涉及的实体,例如旅行者、手电筒、桥等。

同时,需要确定问题的目标,即如何让所有人尽快过桥。

确定约束条件:根据问题的描述,我们知道有一些约束条件,例如每个人过桥的速度不同,手电筒不能扔掉,只能两个人同时过桥等。

这些约束条件将影响解决方案的设计。

分析时间需求:由于目标是尽快让所有人过桥,因此需要分析每个人过桥所需的时间。

这将影响如何分配手电筒和如何安排过桥的顺序。

制定策略:基于上述分析,需要制定一个有效的策略来最大化过桥的速度。

这可能涉及到如何分配手电筒,如何安排过桥的顺序,以及如何返回等。

评估和优化:最后,需要对所制定的策略进行评估和优化。

这可能涉及到对策略的模拟、测试和比较,以便找到最优的解决方案。

2.2.2设计思路这是一个经典的过桥问题,通常称为“蒙提霍尔问题”。

在这个问题中,目标是让所有人尽快过桥。

根据题目的条件,每个人单独过桥的时间是已知的,但是两个人一起过桥的时间是较慢的那个人所需的时间。

模电期末考试答案及解析

模电期末考试答案及解析一、选择题(每题2分,共20分)1. 在放大电路中,静态工作点的确定是为了()。

A. 避免截止失真B. 避免饱和失真C. 避免截止和饱和失真D. 以上都不是答案:C解析:静态工作点的确定是为了确保放大电路在输入信号的整个范围内都能够正常工作,避免截止和饱和失真。

2. 共发射极放大电路中,输出电压与输入电压相位()。

A. 相同B. 相反C. 不确定D. 以上都不是答案:B解析:在共发射极放大电路中,输出电压与输入电压相位相反,因为晶体管的集电极电流与基极电流相位相反。

3. 晶体三极管的放大作用是通过()来实现的。

A. 改变集电极电流B. 改变基极电流C. 改变发射极电流D. 以上都是答案:A解析:晶体三极管的放大作用是通过改变集电极电流来实现的,因为集电极电流与基极电流之间存在比例关系。

4. 理想运算放大器的输入电阻是()。

A. 0B. ∞C. 1D. 0.1答案:B解析:理想运算放大器的输入电阻是无穷大,这意味着它不会从输入信号源吸取电流。

5. 负反馈可以()放大电路的放大倍数。

A. 增加B. 减少C. 不影响D. 以上都不是答案:B解析:负反馈可以减少放大电路的放大倍数,因为它通过将输出信号的一部分反馈到输入端来稳定电路的工作。

6. 场效应管的控制方式是()。

A. 电压控制B. 电流控制C. 温度控制D. 以上都不是答案:A解析:场效应管的控制方式是电压控制,通过改变栅极电压来控制漏极电流。

7. 差分放大电路中,差模信号是()。

A. 两个输入信号的差B. 两个输入信号的和C. 两个输入信号的平均值D. 以上都不是答案:A解析:差分放大电路中,差模信号是两个输入信号的差,它能够放大两个输入信号之间的差异。

8. 功率放大器的主要任务是()。

A. 提高电压B. 提高电流C. 提高电压和电流D. 以上都不是答案:C解析:功率放大器的主要任务是提高电压和电流,以便能够驱动负载。

9. 正弦波振荡电路的振荡条件是()。

模拟cmos集成电路设计课后答案中文

模拟cmos集成电路设计课后答案中文【篇一:北邮模拟cmos集成电路设计实验报告】=txt>姓名学院专业班级学号班内序号实验一:共源级放大器性能分析一、实验目的1、掌握synopsys软件启动和电路原理图(schematic)设计输入方法;2、掌握使用synopsys电路仿真软件custom designer对原理图进行电路特性仿真;3、输入共源级放大器电路并对其进行dc、ac分析,绘制曲线;4、深入理解共源级放大器的工作原理以及mos管参数的改变对放大器性能的影响二、实验要求1、启动synopsys,建立库及cellview文件。

2、输入共源级放大器电路图。

3、设置仿真环境。

4、仿真并查看仿真结果,绘制曲线。

三、实验结果1、电路图2、仿真图四、实验结果分析器件参数:nmos管的宽长比为10,栅源之间所接电容1pf,rd=10k。

实验结果:输入交流电源电压为1v,所得增益为12db。

由仿真结果有:gm=496u,r=10k,所以增益av=496*10/1000=4.96=13.91 db实验二:差分放大器设计一、实验目的1.掌握差分放大器的设计方法;2.掌握差分放大器的调试与性能指标的测试方法。

二、实验要求1.确定放大电路;2.确定静态工作点q;3.确定电路其他参数。

4.电压放大倍数大于20db,尽量增大gbw,设计差分放大器;5.对所设计电路进行设计、调试;6.对电路性能指标进行测试仿真,并对测量结果进行验算和误差分析。

三、实验结果随着r的增加,增益也增加。

但从仿真特性曲线我们可以知道,这会限制带宽的特性,w/l增大时,带宽会下降。

为保证带宽,选取w/l=30,r=30k的情况下的数值,保证了带宽,可以符合系统的功能特性,实验结果见下图。

1.电路图【篇二:集成电路设计王志功习题答案1-5章】划分,集成电路的发展已经经历了哪几代?它的发展遵循了一条业界著名的定律,请说出是什么定律?晶体管-分立元件-ssi-msi-lsi-vlsi-ulsi-gsi-soc。

模电期末试题及答案6

模电期末试题及答案6一、选择题(每题2分,共40分)1. 在半导体材料中,以下哪个不属于杂质?A. 锗B. 砷C. 碳D. 锡答案:C2.以下哪个元件属于非线性元件?A. 电阻B. 电容C. 二极管D. 钳位放大器答案:C3. 在三极管的等效电路模型中,以下哪个元件代表输入电阻?A. REB. RBC. RCD. Rπ答案:D4. 一台功率为200W的音响系统,其电源电压为50V,求电流的大小。

A. 2AB. 4AC. 6AD. 8A答案:B5. 在半导体器件中,p型材料的掺杂元素是以下哪个?A. 硼B. 磷C. 砷D. 锑答案:A6. 以下哪个是电路分析中常用的方法?A. 罗尔定律B. 布尔定律C. 奥姆定律D. 欧姆定律答案:C7. 以下哪个是三极管的常用封装类型?A. TO-92B. DIP-8C. SOT-23D. QFN-32答案:A8. 在半导体材料中,正常工作状态下,n型材料中的电子浓度应该比空穴浓度:A. 大B. 小C. 相等D. 无法确定答案:A9. 以下哪个元件属于旁路元件?A. 电感B. 电容C. 三极管D. 电阻答案:B10. 以下哪个是示波器的主要参数?A. 峰值电压B. 峰-峰值电压C. 时间基准D. 平均值电压答案:C二、填空题(每题2分,共20分)1. 二极管的符号中,箭头指向___________电流的方向。

答案:正向2. 三极管的共射放大电路中,输入电阻由__________表示。

答案:Rπ3. 在放大器的输出电容充电过程中,由于有反馈作用,输出电容的电压先__________上升,然后__________下降。

答案:缓慢,急剧4. 在直流稳压电源中,稳压管将输入电压稳定在大约__________。

答案:0.7V5. 麦克斯韦方程组中的法拉第电磁感应定律描述了__________。

答案:电磁感应现象6. 在电容充电的过程中,电容电压遵循__________的规律。

模拟集成电路设计期末试卷word精品

《模拟集成电路设计原理》期末考试一•填空题(每空1分,共14分)1、与其它类型的晶体管相比,MOS器件的尺寸很容易按________ 比例____ 缩小,CMOS电路被证明具有_较低—的制造成本。

2、放大应用时,通常使MOS管工作在_饱和一区,电流受栅源过驱动电压控制,我们定义—跨导_来表示电压转换电流的能力。

3、入为沟长调制效应系数,对于较长的沟道,入值____ 较小 _ (较大、较小)。

4、源跟随器主要应用是起到___电压缓冲器—的作用。

5、共源共栅放大器结构的一个重要特性就是_输出阻抗_很高,因此可以做成―恒定电流源_。

6、由于_尾电流源输出阻抗为有限值_或_电路不完全对称_等因素,共模输入电平的变化会引起差动输出的改变。

7、理想情况下,_电流镜_结构可以精确地复制电流而不受工艺和温度的影响,实际应用中,为了抑制沟长调制效应带来的误差,可以进一步将其改进为—共源共栅电流镜—结构。

&为方便求解,在一定条件下可用—极点一结点关联一法估算系统的极点频率。

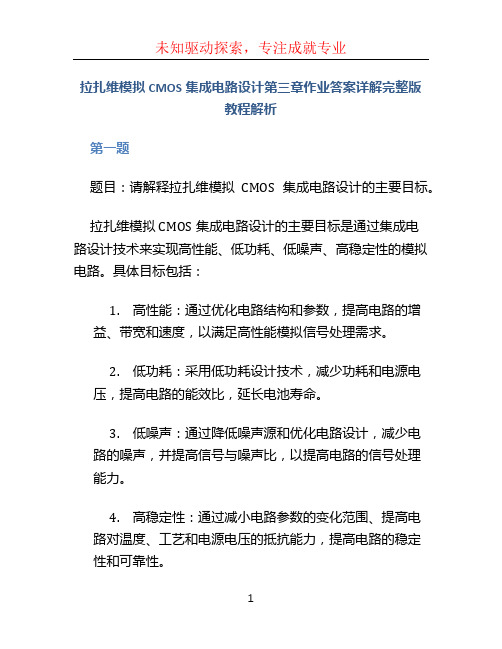

9、与差动对结合使用的有源电流镜结构如下图所示,电路的输入电容C in为—C F(1 - A)__。

10、入为沟长调制效应系数,入值与沟道长度成—反比__ (正比、反比)。

二.名词解释(每题3分,共15分)1、阱解:在CMOS工艺中,PMOS管与NMOS管必须做在同一衬底上,其中某一类器件要做在一个“局部衬底”上,这块与衬底掺杂类型相反的“局部衬底”叫做阱。

2、亚阈值导电效应解:实际上,V GS=V TH时,一个“弱”的反型层仍然存在,并有一些源漏电流,甚至当V GS<V TH时,I D也并非是无限小,而是与V GS呈指数关系,这种效应叫亚阈值导电效应。

3、沟道长度调制解:当栅与漏之间的电压增大时,实际的反型沟道长度逐渐减小,也就是说, 这种效应称为沟道长度调制。

4、等效跨导Gm6、N 阱:解:CMOS 工艺中,PMOS 管与NMOS 管必须做在同一衬底上,若衬底为 P 型,贝U PMOS 管要做在个N 型的“局部衬底”上,这块与衬底掺杂类型相反的N 型“局部衬底”叫做 N 阱。

拉扎维模拟CMOS集成电路设计第三章作业答案详解完整版教程解析 (2)

拉扎维模拟CMOS集成电路设计第三章作业答案详解完整版教程解析第一题题目:请解释拉扎维模拟CMOS集成电路设计的主要目标。

拉扎维模拟CMOS集成电路设计的主要目标是通过集成电路设计技术来实现高性能、低功耗、低噪声、高稳定性的模拟电路。

具体目标包括:1.高性能:通过优化电路结构和参数,提高电路的增益、带宽和速度,以满足高性能模拟信号处理需求。

2.低功耗:采用低功耗设计技术,减少功耗和电源电压,提高电路的能效比,延长电池寿命。

3.低噪声:通过降低噪声源和优化电路设计,减少电路的噪声,并提高信号与噪声比,以提高电路的信号处理能力。

4.高稳定性:通过减小电路参数的变化范围、提高电路对温度、工艺和电源电压的抵抗能力,提高电路的稳定性和可靠性。

综合上述目标,拉扎维模拟CMOS集成电路设计致力于设计出符合实际需求,并具有良好性能、可靠性和可实施性的模拟电路。

第二题题目:什么是负载效应?在拉扎维模拟CMOS集成电路中如何考虑负载效应?负载效应是指当负载改变时,电路的工作条件和性能表现发生变化的现象。

在拉扎维模拟CMOS集成电路中,考虑负载效应是非常重要的。

拉扎维模拟CMOS集成电路中,电路的输入和输出之间会存在阻抗差异,从而导致在连接电路之间引入额外的电容和电阻负载。

这些负载对电路的工作状态产生影响,可能导致增益降低、频率响应偏移、功耗增加等问题。

为了考虑负载效应,在拉扎维模拟CMOS集成电路设计中,需要进行以下步骤:1.电路参数分析:通过计算和仿真,分析电路的输入和输出阻抗,确定电路的负载情况。

2.负载效应补偿:根据负载效应分析结果,采取一系列补偿措施来消除或减小负载效应对电路性能的影响。

例如,可以通过优化电路的结构或参数来改变电路的负载特性,使其更符合设计要求。

3.电路稳定性分析:在设计过程中,还需要对电路的稳定性进行分析。

如果负载效应较大,可能会导致电路的振荡或不稳定现象。

通过稳定性分析,可以预测和避免这些问题的发生。