设计课题4:用两片4位全加器74LS83和门电路设计一位8421BCD码加法器

设计一个一位十进制加减法++数字电路课程设计报告

课程设计报告课程:微机系统与接口课程设计学号:姓名:班级:教师:******大学计算机科学与技术学院设计名称:设计一个一位十进制加减法器日期:2010年1月 23日设计内容:1、0-9十个字符和“+”“-”分别对应一个按键,用于数据输入。

2、用一个开关控制加减法器的开关状态。

3、要求在数码显示管上显示结果。

设计目的与要求:1、学习数字逻辑等电路设计方法,熟知加减法器、编码器、译码显示的工作原理及特点;2、培养勤奋认真、分析故障和解决问题的能力。

设计环境或器材、原理与说明:环境:利用多功能虚拟软件Multism8进行电路的制作、调试,并生成文件。

器材:74LS283或者4008, 4个异或门(一片74LS86)(减法);74LS08,3输入或门(加法)设计原理:图1二进制加减运算原理框图分析:如图1所示,第一步置入两个四位二进制数(要求置入的数小于1010),如(1001)2和(0111)2,同时在两个七段译码显示器上显示出对应的十进制数9和7;第二步通过开关选择运算方式加或者减;第三步,若选择加运算方式,所置数送入加法运算电路进行运算,同理若选择减运算方式,则所置数送入减法运算电路运算;第四步,前面所得结果通过另外两个七段译码器显示。

设计过程(步骤)或程序代码:实验电路:1:减法电路的实现:(1):原理:如图1所示(如下),该电路功能为计算A-B。

若n位二进制原码为N原,则与它相对应的补码为N补=2n-N原,补码与反码的关系式为N补=N反+1,A-B=A+B补-2n=A+B反+1-2n(2):因为B○+1= B非,B○+0=B,所以通过异或门74LS86对输入的数B求其反码,并将进位输入端接逻辑1以实现加1,由此求得B的补码。

加法器相加的结果为:A+B反+1,(3):由于2n=24=(10000)2,相加结果与相2n减只能由加法器进位输出信号完成。

当进位输出信号为1时,它与2n的差为0;当进位输出信号为0时,它与2n差值为1,同时还要发出借位信号。

8421BCD码加法器

电子线路课程设计(报告)题目8421BCD码加法器院系物理与电子工程学院专业光电信息科学与工程班级Z052132 学号052513212学生姓名李晓刚指导教师徐竞日期2015年6月目录一题目要求与方案论证 (1)1.1 8421BCD码加法器 (1)1.1.1题目要求 (1)1.1.2 方案论证 (1)二电子线路设计与实现 (3)2.1 8421BCD码加法器的设计 (3)三结果与分析 (8)3.1 8421BCD码加法器的实现 (8)四总结与体会 (10)参考文献 (11)附录 (12)一题目要求与方案论证1.1 8421BCD码加法器1.1.1题目要求通过开关J1~J8分别设置2个4位8421BCD码输入,通过全加器,实现相加后的输出,结果采用数码管观察。

主要芯片:2个全加器(4008BD)、开关、数码管(2个),其他元件、门电路任选1.1.2 方案论证表1.1 4008BD功能表表1.2 74HC85AD的真值表表1.3 74LS48功能表由真值表可知:两个四位8421BCD码通过4008BD全加器相加后得到的是一个四位的8421码或五位的168421码,故不能直接通过两个数码管来显示出运算结果,所以要把计算结果转换为10进制,然后将个位和十位的数字分别由对应的8421BCD码通过译码器芯片74LS48,把运算结果用数码管显示出来。

如下表所示:表1.4 数制转换二电子线路设计与实现2.1 8421BCD码加法器的设计一、数据的产生与输入通过J1~J8八个单刀双掷开关在+5V和GND之间的切换来产生两个4位8421BCD码作为输入的数据,当开关打到+5V时输入数据1,打到GND时输入数据0。

其中J1~J4分别为数据A0~A3,J5~J8分别为数据B0~B3,且A3~A0、B3~B0的位权依次降低。

其电路图如下所示:图2.1.1 数据产生电路二、加法电路把上面得到的两个四位8421BCD码分别输入4008BD全加器的输入端A3~A0、B3~B0,同时CIN输入端接低电平。

4位加减法并行运算电路(包括拓展8位)

4位加减法并行运算电路(包括拓展8位)二○一二~二○一三学年第一学期电子信息工程系脉冲数字电路课程设计报告书班级:电子信息工程(DB)1004班课程名称:脉冲数字电路课程设计学时: 1 周学生姓名:学号:指导教师:廖宇峰二○一二年九月一、设计任务及主要技术指标和要求➢ 设计目的1. 掌握加/减法运算电路的设计和调试方法。

2. 学习数据存储单元的设计方法。

3. 熟悉集成电路的使用方法。

➢ 设计的内容及主要技术指标1. 设计4位并行加/减法运算电路。

2. 设计寄存器单元。

3. 设计全加器工作单元。

4. 设计互补器工作单元。

5. 扩展为8位并行加/减法运算电路(选作)。

➢ 设计的要求1. 根据任务,设计整机的逻辑电路,画出详细框图和总原理图。

2. 选用中小规模集成器件(如74LS 系列),实现所选定的电路。

提出器材清单。

3. 检查设计结果,进行必要的仿真模拟。

二、方案论证及整体电路逻辑框图➢ 方案的总体设计步骤一因为参与运算的两个二进制数是由同一条数据总线分时串行传入,而加法运算的时候需要两个数的并行输入。

所以需要两个寄存器分别通过片选信号,依次对两个二进制进行存储,分别在寄存器的D c B A Q Q Q Q 端口将两个4位二进制数变成并行输出; 步骤二 为了便于观察置入两个4位二进制数的数值大小,根据人们的习惯,在寄存器的输出端,利用两个七段译码器将二进制数转化为十进制数; 步骤三通过开关选择加/减运算方式;步骤四若选择加法运算方式,对所置入数送入加法运算电路进行运算;即:9)1001()0110()0011(222==+ 【十进制:963=+】又或:15)1111()0100()1011(222==+ 【十进制:15511=+】步骤五若选择减法运算方式,对所置入数送入减法运算电路进行运算;即:2)0010()0101()0111(222==- 【十进制:257=-】又或:10)1010()1101()0011(222=-=- 【十进制:10133-=-】步骤六为了便于观察最后的计算结果,以及对最后的计算结果的正确性能做出快速的判断,根据人们的习惯,同上,将计算出的结果输入七段译码器进行译码显示。

组合逻辑课程设计4位二进制全加器全减器原创

关键字 74LS283 全加器、四位二进制、迭代电路、并行进位、串行进位、VHDL

摘要

加法器是数字系统中产生数的和的装置。加数和被加数为输入,和数与进 位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进

...

.

..

..

位为输出则为全加器。例如:为了节省资源,减法器和硬件乘法器都可以用加法 器来构成。但宽位加法器的设计是很耗资源的,因此在实际的设计和相关饿得设 计与开发中需要注意资源的利用率和进位速度两方面的问题,多位加法器的构成 主要有两种:并行进位和串行进位。并行进位加法器设有并行进位产生逻辑,运 行速度比串行进位快;串行进位是将全加器采取并行级联或菊花链式级联构成多 位加法器。加法器也是常用作计算机算术逻辑部件,执行逻辑操作、移位与指令 调用。此外还可以用来表示各种数值,如:BCD、加三码,主要的加法器是以二 进制作运算。

1 0 0100 11011000

1 0 0101 00011010

1 0 0001 10011100

1 0 0001 10111110

1 0 1010 01000111

1 0 1010 01101001

1 0 0010 01000011

1 0 0010 01100101

... ... ... ... ... ... ... ... ... ... ... ... ... ...

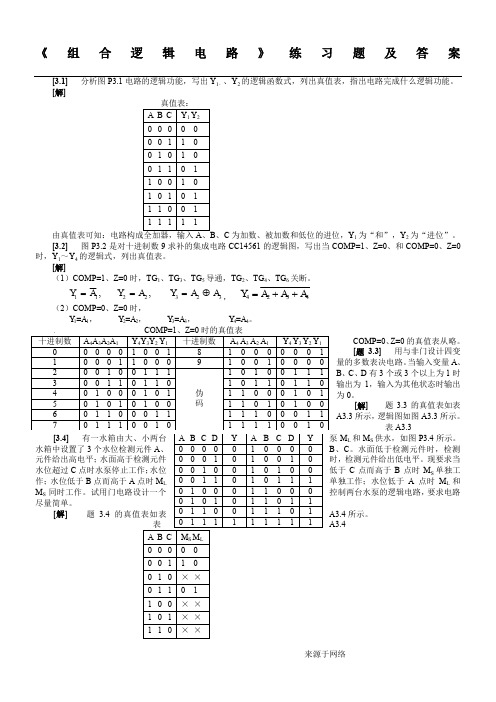

【数电】组合逻辑电路习题(含答案)

《组合逻辑电路》练习题及答案[3.1]分析图P3.1电路的逻辑功能,写出Y1、、Y2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

[解]、Z=0A、1时A3.3所示。

P3.4所示。

M S单独工点时M L和要求电路真值表中的C A 、C B A 、C B A 、C AB 为约束项,利用卡诺图图A3.4(a)化简后得到:C B A M S +=, B M L =(M S 、M L的1状态表示工作,0状态表示停止)。

逻辑图如图A3.4(b)。

[3.5] 设计一个代码转换电路,输入为4位二进制代码,输出为4位循环码。

可以采用各种逻辑功能的门电路来实现。

[解] 题3.5的真值表如表A3.5所示。

D 4、D 3与足上述控制要求的逻辑电路,给出控制四个指示灯状态的高、低电平信号。

74LS148的逻辑图如图P3.7所示,其功能表如表P3.7所示。

表 P3.7 74LS148的功能表A 、B 、C 、L 1、0为0000~2)工作,P3.10输 入21O 123用外加与非门实现之,如图A3.10所示。

[3.11] 画出用4线-16线译码器74LS154(参见题3.9)和门电路产生如下多输出逻辑函数的逻辑图。

[解]电路图如图A3.11所示。

[3.12] 用3线-8线译码器74LS138和门电路设计1位二进制全减器电路。

输入为被减数、减数和来自低位的借位;输出为两数之差及向高位的借位信号。

[解] 设a i 为被减数,b i 为减数,c i-1为来自低位的借位,首先列出全减器真值表,然后将Di ,Ci 表达式写成非-与非形式。

最后外加与非门[3.13] 74LS153[解] [3.14]如表P3.14 [解][3.15][解] [3.16] [解] 与4选1[3.17][解] 则 D =41507632 如图A3.17所示。

[3.18] 用8选1数据选择器CC4512(参见题3.14)产生逻辑函数[解] 将Y 变换成最小项之和形式。

四位二进制加法器 课程设计报告

《电工与电子技术基础》课程设计报告题目 4位二进制加法器学院(部)专业班级学生姓名学号5月日至 6月日共周目录技术要求·2摘要·2第一章系统概述1、总体设计思想·22、系统框图·33、工作原理·3第二章单元电路设计及分析1、加法器的选择·42、译码器Ⅰ的选择·83、译码器Ⅱ的选择·114、数码管的选择·13第三章系统综述及总体电路图1、系统综述·142、总体电路图·153、仿真结果·15第四章结束语收获与体会·16鸣谢·17附录1、元件材料清单·172、部分元器件引脚图·17参考文献··174位二进制加法器课题名称与技术要求课题名称:四位二进制加法器设计技术要求:1)四位二进制加数与被加数输入2)二位数码管显示摘要本设计通过八个数据开关将A4,A3,A2,A1和B4,B3,B2,B1信号作为加数和被加数输入四位二进制并行进位加法器相加,将输出信号S4,S3,S2,S1和向高位的进位C4通过译码器Ⅰ译码,再将输出的X4,X3,X2,X1和Y4,Y3,Y2,Y1各自分别通过一个 74248J译码器,最后分别通过数码管HVH实现二位显示。

本设计中译码器Ⅰ由三部分组成,包括一个2输入四与非门(74LS08D)、一个4位二进制全加器(74LS283N)和一个3输入或门(4075BD_5V)。

信号S4,S3,S2,S1和向高位的进位C4输入译码器Ⅰ,将得到的两组4位BCD码输出,将这两组4位BCD码分别输入BCD-7段译码/升压输出驱动器(74248J),使电路的后续部分得以执行。

第一章系统概述1、总体设计思想设计思路:两个4位二进制数的输入可用八个数据开关实现,这两个二进制数经全加器求和后最多可以是5位二进制数。

而本题要求用两位数码管分别显示求和结果的十进制十位和各位,因此需要两个译码器Ⅱ分别译码十位和个位。

组合逻辑电路课后答案

组合逻辑电路课后答案第4章[题].分析图电路的逻辑功能,写出输出的逻辑函数式,列出真值表,说明电路逻辑功能的特点。

图P4.1B YAP 56P P =图解:(1)逻辑表达式()()()5623442344232323232323Y P P P P P CP P P P CP P P C CP P P P C C P P P P C P PC ===+=+=++=+ 2311P P BP AP BABAAB AB AB ===+ ()()()2323Y P P C P P CAB AB C AB ABC AB AB C AB AB CABC ABC ABC ABC=+=+++=+++=+++(2)真值表(3)功能从真值表看出,这是⼀个三变量的奇偶检测电路,当输⼊变量中有偶数个1和全为0时,Y =1,否则Y=0。

[题] 分析图电路的逻辑功能,写出Y 1、、Y 2的逻辑函数式,列出真值表,指出电路完成什么逻辑功能。

图P4.3B1Y 2[解]解: 2Y AB BC AC =++12Y ABC A B C Y ABC A B C AB BC AC ABC ABC ABC ABC =+++=+++++=+++()())由真值表可知:、C 为加数、被加数和低位的进位,Y 1为“和”,Y 2为“进位”。

[题] 图是对⼗进制数9求补的集成电路CC14561的逻辑图,写出当COMP=1、Z=0、和COMP=0、Z=0时,Y 1~Y 4的逻辑式,列出真值表。

图P4.4[解](1)COMP=1、Z=0时,TG1、TG3、TG5导通,TG2、TG4、TG6关断。

,(2)COMP=0、Z=0时,Y1=A1,Y2=A2,Y3=A3,Y4=A4。

、COMP=1、Z=0时的真值表、Z=0的真值表从略。

[题] ⽤与⾮门设计四变量的多数表决电路。

当输⼊变量A、B、C、D有3个或3个以上为1时输出为1,输⼊为其他状态时输出为0。

[解] 题的真值表如表所⽰,逻辑图如图(b)所⽰。

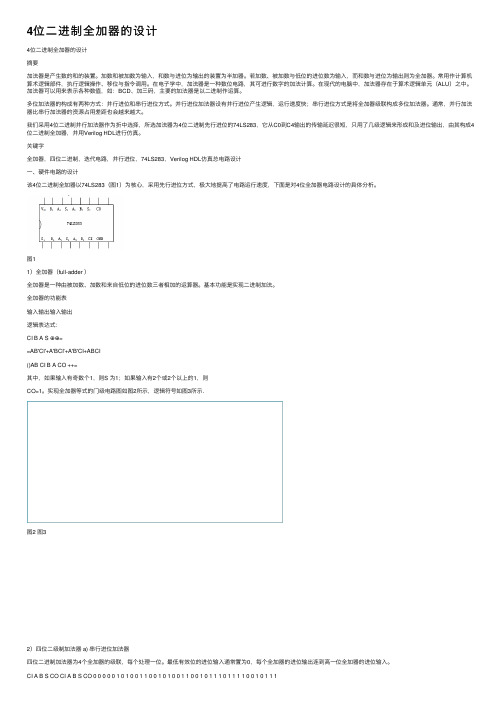

4位二进制全加器的设计

4位⼆进制全加器的设计4位⼆进制全加器的设计摘要加法器是产⽣数的和的装置。

加数和被加数为输⼊,和数与进位为输出的装置为半加器。

若加数、被加数与低位的进位数为输⼊,⽽和数与进位为输出则为全加器。

常⽤作计算机算术逻辑部件,执⾏逻辑操作、移位与指令调⽤。

在电⼦学中,加法器是⼀种数位电路,其可进⾏数字的加法计算。

在现代的电脑中,加法器存在于算术逻辑单元(ALU)之中。

加法器可以⽤来表⽰各种数值,如:BCD、加三码,主要的加法器是以⼆进制作运算。

多位加法器的构成有两种⽅式:并⾏进位和串⾏进位⽅式。

并⾏进位加法器设有并⾏进位产⽣逻辑,运⾏速度快;串⾏进位⽅式是将全加器级联构成多位加法器。

通常,并⾏加法器⽐串⾏加法器的资源占⽤差距也会越来越⼤。

我们采⽤4位⼆进制并⾏加法器作为折中选择,所选加法器为4位⼆进制先⾏进位的74LS283,它从C0到C4输出的传输延迟很短,只⽤了⼏级逻辑来形成和及进位输出,由其构成4位⼆进制全加器,并⽤Verilog HDL进⾏仿真。

关键字全加器,四位⼆进制,迭代电路,并⾏进位,74LS283,Verilog HDL仿真总电路设计⼀、硬件电路的设计该4位⼆进制全加器以74LS283(图1)为核⼼,采⽤先⾏进位⽅式,极⼤地提⾼了电路运⾏速度,下⾯是对4位全加器电路设计的具体分析。

图11)全加器(full-adder )全加器是⼀种由被加数、加数和来⾃低位的进位数三者相加的运算器。

基本功能是实现⼆进制加法。

全加器的功能表输⼊输出输⼊输出逻辑表达式:CI B A S ⊕⊕==AB'CI'+A'BCI'+A'B'CI+ABCI()AB CI B A CO ++=其中,如果输⼊有奇数个1,则S 为1;如果输⼊有2个或2个以上的1,则CO=1。

实现全加器等式的门级电路图如图2所⽰,逻辑符号如图3所⽰.图2 图32)四位⼆级制加法器 a) 串⾏进位加法器四位⼆进制加法器为4个全加器的级联,每个处理⼀位。

8421BCD码加法器

电子线路课程设计(报告)题目8421BCD码加法器系别物理与电子科学系专业电子科学与技术班级08电科(4)班学号*********学生姓名吴迪指导教师徐竞日期2010.7.10~2010.7.15目录一题目要求与方案论证 (2)1.1设计题目 (2)1.1.1题目要求 (2)1.1.2 方案论证 (2)二电子线路设计与实现 (4)2.18421BCD加法器的设计 (4)2.28421BCD加法器的构成 (5)三结果与分析 (9)3.1两个四位8421BCD码加法的实现 (9)3.2调试注意事项 (10)四总结与体会 (11)参考文献 (12)附录 (13)一题目要求与方案论证1.1设计题目8421BCD码加法器1.1.1题目要求通过开关J1~J8分别设置2个4位8421BCD码输入,通过全加器,实现相加后的输出,结果采用数码管观察。

主要芯片:2个全加器(4008BD)、开关、数码管(2个),其他元件、门电路任选1.1.2 方案论证表1.1 4008BD功能表表1.2 74HC4511功能表有真值表可知:两个四位8421BCD码相加后得到的是一个四位或五位的二进制数,不好直接通过两个数码管来显示运算结果,所以要考虑用两个4008BD全加器来把计算结果转换为8421BCD码来输入显示译码器,从而实现把运算结果用数码管显示出来。

如下表所示:表1.3 数制转换二电子线路设计与实现2.1 8421BCD加法器的设计一、根据题目要求得到其功能表如下:二、由表我们可以算出Y的表达式由前16项有(1)3210321032103210321032103231Y S S S S S S S S S S S S S S S S S S S S S S S S S S S S =+++++=+(2)由后10项有1O Y C ==由(1)(2)有Y=C O +S 3S 2+S 3S 1三、理论图图2.1 逻辑电路图2.2 8421BCD 加法器的构成一、数据的产生与输入通过J1~J8八个单刀双掷开关在+5V 和GND 之间的切换来产生两个4位8421BCD 码作为输入的数据,当开关打到+5V 时输入数据1,打到GND 时输入数据0。

实验4 组合逻辑电路设计

实验四组合逻辑电路研究(设计性实验)一、实验目的1.掌握用SSI器件实现组合逻辑电路的方法。

2.熟悉各种MSI组合逻辑器件的工作原理和引脚功能。

3.掌握用MSI组合逻辑器件实现组合逻辑电路的方法。

4.进一步熟悉测试环境的构建和组合逻辑电路的测试方法。

二、实验所用仪器设备1.Multisim10中的虚拟仪器2.Quartus II中的功能仿真工具3.GW48-EDA实验开发系统三、实验说明1. 组合逻辑电路的设计一般可按以下步骤进行(1)逻辑抽象:将文字描述的逻辑命题转换成真值表。

(2)选择器件类型:根据命题的要求和器件的功能决定采用哪种器件。

(3)根据真值表和所选用的逻辑器件写出相应的逻辑表达式:当采用SSI集成门电路设计时,为了使电路最简,应将逻辑表达式化简,并变换成与门电路相对应的最简式;当采用MSI组合逻辑器件设计时,则不用化简,只需将由最小项构成的函数式变换成MSI器件所需要的函数形式。

(4)根据化简或变换后的逻辑表达式及选用的逻辑器件画出逻辑电路图。

2. 常见的SSI和MSI的型号(1)常见的SSI:四2输入异或门74LS86,四2输入与非门74LS00,六非门74LS04,二4输入与非门74LS20,四2输入或非门74LS02,四2输入与门74LS08等。

(2)常见的MSI:二2-4译码器74LS139,3-8译码74LS138,4-16译码器74LS154,8-3线优先编码器74LS148,七段字符译码器74LS248,四位全加器74LS283,四2选1数据选择器74LS157,双4选1数据选择器74LS153,8选1数据选择器74LS151,16选1数据选择器74LS150等。

四、实验内容(一)基本命题1.设计一个多输出的逻辑网络,它的输入是8421BCD码,它的输出定义为:(1)F1:检测到输入数字能被3整除。

(2)F2:检测到输入数字大于或等于4。

(3)F3:检测到输入数字小于7。

BCD码加法器

+ 7 → + 0111

………… …………

13 1011

1101在8421BCD码中是非法码,结果错误,如果加6修正后,则产生了进位信号,且本位

1101

+ 0110

…………

1,0011

“0011”也是正确的。

③若和产生进位,则结果错误,也需加6修正。如

8 1000

+ 9 → + 1001

卓越工程师班第一次大作业

用四位全加器构成

一位BCD码加法器

班级:001111

作者:00111116 江新远

实现方式一:器件

一、问题

用四位二进制全加器74LS283构成一位8421BCD码加法电路

二、74LS283介绍

74LS283是TTL双极型并行4位全加器,,特点是先行禁卫,因此运算速度很快,其外形为双列直插。它有两组4位二进制数输入 ,一位低位向本位的进位输入 ,有一组二进制输出 ,一个最高位的进位输出,改器件所完成的4位二进制加法如图所示。

由于S是二进制的,所以最后取S的后四位加6就好。但是为防止S的后四位加6,仍然大于10,故先用S1等于S的后四位加6,然后再取S1的后四位。

附代码:

library ieee;

use fhomework1 is

port(a,b:in std_logic_vector(3 downto 0);

c:outbit;

………… …………

17 1,0001

虽产生了进位,但本位和不正确,若加6修正

1,0001

+ 0110

…生错误的原因是8421BCD码为十进制,逢十进一,而四位二进制数是逢十六进一,故二者进位关系不同。其中刚好相差6,故需加6进行修正。

74LS83简介及应用举例

74LS83简介及应用举例

目录

74LS83简介 (1)

74LS83推荐使用条件 (1)

74LS83引脚介绍 (2)

74LS83功能详细介绍 (2)

74LS83应用举例(设计BCD码加法器) (3)

电路讲解 (4)

电路验算: (7)

74LS83简介

74LS83可以实现两个4位二进制数带进位的加法运算。

在进行加法的同时,还可以增加低位进位的计算。

该芯片还可以反映加法计算结果是否有进位。

该芯片的典型功耗是95mW。

74LS83推荐使用条件

74LS83引脚介绍

74LS83芯片的俯视图如图1所示。

该芯片共16个引脚。

5号引脚为电源端VCC,12号引脚为电源端GND。

芯片其余引脚名称以及介绍如表1所示。

图1

表1

备注:表中1个TTL的驱动能力为,高电平40uA,低电平1.6mA。

74LS83功能详细介绍

74LS83可以实现两个4位二进制数的加法。

其中一个加数通过A1-A4输入至芯片,另外一个加数通过B1-B4输入芯片,计算结果通。

4位二进制加法器课程设计

长安大学电工与电子技术课程设计题目:4位二进制加法器学院:汽车学院专业:汽车运用工程班级:姓名:学号:指导老师:李三财目录一、课题名称与技术要求···························二、摘要·········································三、总体设计方案论证及选择·······················1、方案论证与选择······························2、加法器的选取································3、译码器的选取································4、数码管的选取································四、设计方案的原理框图、总体电路原理图及说明·····1、原理框图····································2、总体电路原理图······························3、说明········································五、单元电路设计、主要元器件选择及电路参数计算···1、单元电路设计································2、主要元器件选择······························六、收获与体会及存在的问题·······················七、参考文献·····································八、附件·········································一、课题名称及技术要求1、课题名称:四位二进制加法器2、技术要求:a、四位二进制加数与被加数输入b、二位数码管显示二、摘要本加法器要实现能够输入加数和被加数,并且还能够将最终结果用二位数码管显示出来的功能。

4位二进制全加器的设计

4位二进制全加器的设计摘要加法器是产生数的和的装置。

加数和被加数为输入,和数与进位为输出的装置为半加器。

若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

在电子学中,加法器是一种数位电路,其可进行数字的加法计算。

在现代的电脑中,加法器存在于算术逻辑单元(ALU)之中。

加法器可以用来表示各种数值,如:BCD、加三码,主要的加法器是以二进制作运算。

多位加法器的构成有两种方式:并行进位和串行进位方式。

并行进位加法器设有并行进位产生逻辑,运行速度快;串行进位方式是将全加器级联构成多位加法器。

通常,并行加法器比串行加法器的资源占用差距也会越来越大。

我们采用4位二进制并行加法器作为折中选择,所选加法器为4位二进制先行进位的74LS283,它从C0到C4输出的传输延迟很短,只用了几级逻辑来形成和及进位输出,由其构成4位二进制全加器,并用Verilog HDL进行仿真。

关键字全加器,四位二进制,迭代电路,并行进位,74LS283,Verilog HDL仿真总电路设计一、硬件电路的设计该4位二进制全加器以74LS283(图1)为核心,采用先行进位方式,极大地提高了电路运行速度,下面是对4位全加器电路设计的具体分析。

图11)全加器(full-adder )全加器是一种由被加数、加数和来自低位的进位数三者相加的运算器。

基本功能是实现二进制加法。

输入输出输入输出CI B A S ⊕⊕==AB'CI'+A'BCI'+A'B'CI+ABCI()AB CI B A CO ++=其中,如果输入有奇数个1,则S 为1;如果输入有2个或2个以上的1,则CO=1。

实现全加器等式的门级电路图如图2所示,逻辑符号如图3所示.图2 图32)四位二级制加法器 a) 串行进位加法器四位二进制加法器为4个全加器的级联,每个处理一位。

四位二进制8421BCD码加法器

课程设计报告设计题目:四位二进制8421BCD码加法器学院: 理学院专业: 09电子信息科学与技术班级: 1班学号: 200931120102; 200931120103; 200931120105 姓名:陈俊宇陈明源邓坤勇电子邮件: 1205335255@qq。

com 时间: 2011年12月8日成绩:指导教师: 刘丹华南农业大学理学院应用物理系课程设计(报告)任务书题目四位二进制加法器任务与要求:运用电子器件和一些IC芯片设计一个四位二进制8421BCD码加法器。

用以实现两个四位二进制数8421BCD码的加法通过数码管显示相加所得的两位十进制数。

用八个开关的开闭控制电平的高低,用高电平表示1;用低电平表示0。

将输入的高电平接入74LS283加法器进行运算。

得到的结果,分别将高低位输入74LS248译码器输出到两个七段数码管.由数码管显示加法结果得到的BCD码。

学会数字信号芯片的原理和在实际中的应用.开始时间:2011年12月1日;结束时间:2011年12月13日四位二进制8421BCD码加法器学生:陈俊宇,陈明源,邓坤勇;指导老师:刘丹摘要:本设计通过八个开关将A3,A2,A1,A0和B3,B2,B1,B0信号作为加数和被加数输入四位串行进位加法器相加,将输出信号S3,S2,S1,S0和向高位的进位C3各自分别通过一个 74LS248译码器,最后分别通过数码管实现二位BCD码显示。

关键词:加法器,译码器,数码管,BCD码显示。

Abstract: the design through eight switch will A3, A2, A1, A0 and B3, B2, B1, B0 signal as addend and BeiJiaShu input four serial carry adder addition, will output signal S3, S2, S1, to carry high and S0 C3 their respective through a 74 LS248 decoder, finally, through the digital tube realize two BCD display。

4位二进制全加器的设计

4位二进制全加器的设计摘要加法器是产生数的和的装置。

加数和被加数为输入,和数与进位为输出的装置为半加器。

假设加数、被加数与低位的进位数为输入,而和数与进位为输出那么为全加器。

经常使用作运算机逻辑部件,执行逻辑操作、移位与挪用。

在电子学中,加法器是一种数位电路,其可进行数字的加法计算。

在现代的电脑中,加法器存在于(ALU)当中。

加法器能够用来表示各类数值,如:BCD、加三码,要紧的加法器是以二进制作运算。

多位加法器的组成有两种方式:并行进位和串行进位方式。

并行进位加法器设有并行进位产生逻辑,运行速度快;串行进位方式是将全加器级联组成多位加法器。

通常,并行加法器比串行加法器的资源占用差距也会愈来愈大。

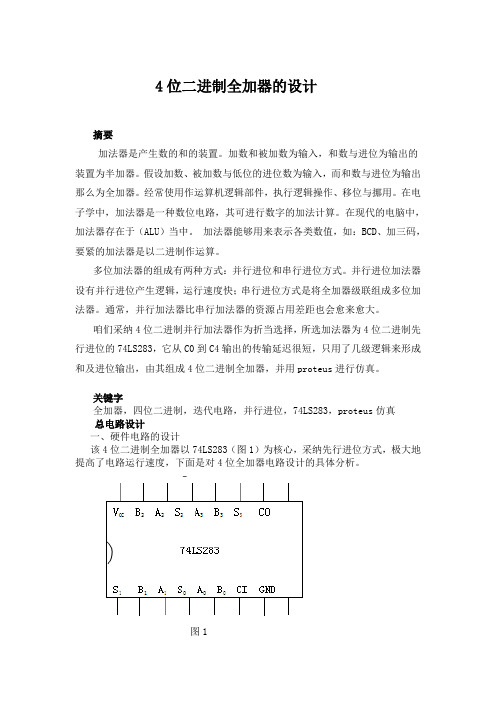

咱们采纳4位二进制并行加法器作为折当选择,所选加法器为4位二进制先行进位的74LS283,它从C0到C4输出的传输延迟很短,只用了几级逻辑来形成和及进位输出,由其组成4位二进制全加器,并用proteus进行仿真。

关键字全加器,四位二进制,迭代电路,并行进位,74LS283,proteus仿真总电路设计一、硬件电路的设计该4位二进制全加器以74LS283(图1)为核心,采纳先行进位方式,极大地提高了电路运行速度,下面是对4位全加器电路设计的具体分析。

图11)全加器(full-adder )全加器是一种由被加数、加数和来自低位的进位数三者相加的运算器。

大体功能是实现二进制加法。

CIBAS⊕⊕==AB'CI'+A'BCI'+A'B'CI+ABCI()ABCIBACO++=其中,若是输入有奇数个1,那么S为1;若是输入有2个或2个以上的1,那么CO=1。

实现全加器等式的门级电路图如图2所示,逻辑符号如图3所示.图2 输入输出输入输出CI A B S CO CI A B S CO0 0 00 0 10 1 00 1 10 01 01 00 11 0 01 0 11 1 01 1 11 00 10 11 1图32)四位二级制加法器 a) 串行进位加法器四位二进制加法器为4个全加器的级联,每一个处置一名。

8421BCD码加法器

电子线路课程设计(报告)题目8421BCD码加法器院系物理与电子工程学院专业光电信息科学与工程班级Z052132 学号052513212学生姓名李晓刚指导教师徐竞日期2015年6月目录一题目要求与方案论证 (1)1.1 8421BCD码加法器 (1)1.1.1题目要求 (1)1.1.2 方案论证 (1)二电子线路设计与实现 (3)2.1 8421BCD码加法器的设计 (3)三结果与分析 (8)3.1 8421BCD码加法器的实现 (8)四总结与体会 (10)参考文献 (11)附录 (12)一题目要求与方案论证1.1 8421BCD码加法器1.1.1题目要求通过开关J1~J8分别设置2个4位8421BCD码输入,通过全加器,实现相加后的输出,结果采用数码管观察。

主要芯片:2个全加器(4008BD)、开关、数码管(2个),其他元件、门电路任选1.1.2 方案论证表1.1 4008BD功能表表1.2 74HC85AD的真值表表1.3 74LS48功能表由真值表可知:两个四位8421BCD码通过4008BD全加器相加后得到的是一个四位的8421码或五位的168421码,故不能直接通过两个数码管来显示出运算结果,所以要把计算结果转换为10进制,然后将个位和十位的数字分别由对应的8421BCD码通过译码器芯片74LS48,把运算结果用数码管显示出来。

如下表所示:表1.4 数制转换二电子线路设计与实现2.1 8421BCD码加法器的设计一、数据的产生与输入通过J1~J8八个单刀双掷开关在+5V和GND之间的切换来产生两个4位8421BCD码作为输入的数据,当开关打到+5V时输入数据1,打到GND时输入数据0。

其中J1~J4分别为数据A0~A3,J5~J8分别为数据B0~B3,且A3~A0、B3~B0的位权依次降低。

其电路图如下所示:图2.1.1 数据产生电路二、加法电路把上面得到的两个四位8421BCD码分别输入4008BD全加器的输入端A3~A0、B3~B0,同时CIN输入端接低电平。