M3启动文件.tmp

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

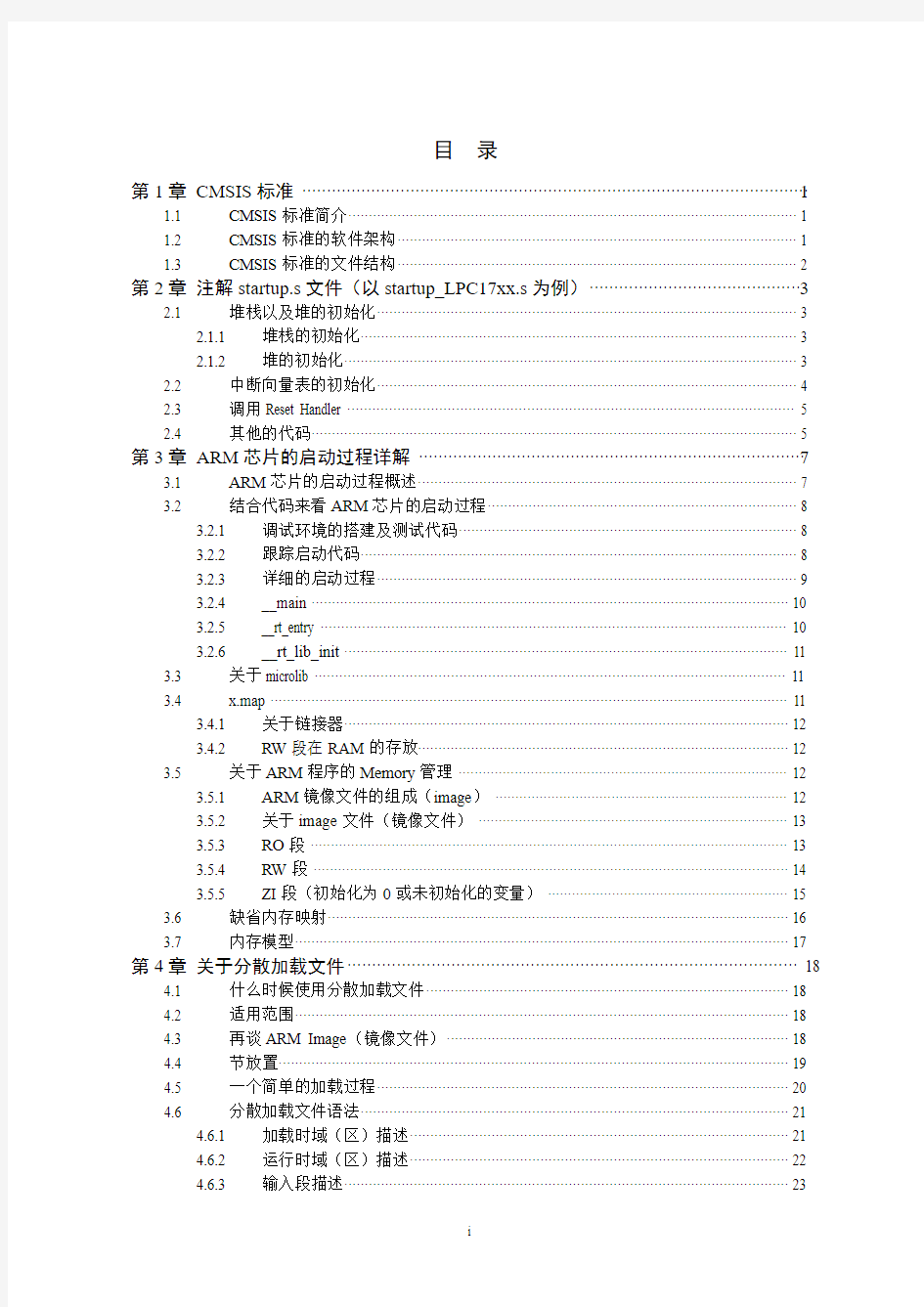

目录

第1章CMSIS标准 (1)

1.1 CMSIS标准简介 (1)

1.2 CMSIS标准的软件架构 (1)

1.3 CMSIS标准的文件结构 (2)

第2章注解startup.s文件(以startup_LPC17xx.s为例) (3)

2.1 堆栈以及堆的初始化 (3)

2.1.1 堆栈的初始化 (3)

2.1.2 堆的初始化 (3)

2.2 中断向量表的初始化 (4)

2.3 调用Reset Handler (5)

2.4 其他的代码 (5)

第3章ARM芯片的启动过程详解 (7)

3.1 ARM芯片的启动过程概述 (7)

3.2 结合代码来看ARM芯片的启动过程 (8)

3.2.1 调试环境的搭建及测试代码 (8)

3.2.2 跟踪启动代码 (8)

3.2.3 详细的启动过程 (9)

3.2.4 __main (10)

3.2.5 __rt_entry (10)

3.2.6 __rt_lib_init (11)

3.3 关于microlib (11)

3.4 x.map (11)

3.4.1 关于链接器 (12)

3.4.2 RW段在RAM的存放 (12)

3.5 关于ARM程序的Memory管理 (12)

3.5.1 ARM镜像文件的组成(image) (12)

3.5.2 关于image文件(镜像文件) (13)

3.5.3 RO段 (13)

3.5.4 RW段 (14)

3.5.5 ZI段(初始化为0或未初始化的变量) (15)

3.6 缺省内存映射 (16)

3.7 内存模型 (17)

第4章关于分散加载文件 (18)

4.1 什么时候使用分散加载文件 (18)

4.2 适用范围 (18)

4.3 再谈ARM Image(镜像文件) (18)

4.4 节放置 (19)

4.5 一个简单的加载过程 (20)

4.6 分散加载文件语法 (21)

4.6.1 加载时域(区)描述 (21)

4.6.2 运行时域(区)描述 (22)

4.6.3 输入段描述 (23)

4.7 实战测试(一个简单的例程) (24)

4.8 实战分散加载 (26)

4.8.1 多块RAM的分散加载文件配置 (27)

4.8.2 多块Flash的分散加载文件配置 (28)

第5章编写自己的启动代码(基于LPC17xx) (32)

5.1 最简单的启动代码(Startup.s Version-1.0) (32)

5.1.1 启动代码必须完成的三项工作 (32)

5.1.2 程序实现(Startup.s Version-1.0) (32)

5.1.3 指定加载方式让程序跑起来 (33)

5.1.4 V ersion-1.0的缺点 (33)

5.2 一个实用的启动代码(Startup.s V ersion-2.0) (33)

5.2.1 设计描述 (33)

5.2.2 程序实现(Startup.s) (34)

5.2.3 向量表V ectors.h和V ectors.c (34)

5.2.4 指定加载方式 (37)

第1章CMSIS标准

1.1 CMSIS标准简介

ARM公司于2008年11月12日发布了ARMCortex微控制器软件接口标准CMSIS 1.0。CMSIS是独立于供应商的Cortex-M处理器系列硬件抽象层,为芯片厂商和中间件供应商提供了简单的处理器软件接口,简化了软件复用工作,降低了Cortex-M上操作系统的移植难度,并减少了新入门的微控制器开发者的学习曲线和新产品的上市时间。

根据近期的调查研究,软件开发已经被嵌入式行业公认为最主要的开发成本。因此,ARM 与Atmel、IAR、KEIL、Luminary Micro、Micrium、NXP、SEGGER和ST等诸多芯片和软件工具厂商合作,将所有Cortex芯片厂商的产品的软件接口标准化,制定了CMSIS标准。此举意在降低软件开发成本,尤其针对进行新设备项目开发或将已有的软件移植到其他芯片厂商提供的基于Cortex处理器的微控制器的情况。有了该标准,芯片厂商就能够将他们的资源专注于对其产品的外设特性进行差异化,并且能够消除对微控制器进行编程时需要维持的不同的、互相不兼容的标准的需求,从而达到降低开发成本的目的。

1.2 CMSIS标准的软件架构

图1.1 基于CMSIS标准的软件架构

从图1.1 基于CMSIS标准的软件架构中可以看到,基于CMSIS标准的软件架构主要分为以下四层:用户应用层,操作系统层,CMSIS层以及硬件寄存器层。其中CMSIS层起着承上启下的作用,一方面该层对硬件寄存器层进行了统一的实现,屏蔽了不同厂商对Cortex-M系列微处理器核内外设寄存器的不同定义,另一方面又向上层的操作系统和应用层提供接口,简化了应用程序开发的难度,使开发人员能够在完全透明的情况下进行一些应用程序的开发。也正是如此,CMSIS层的实现也相对复杂,下面将对CMSIS层次结构进行剖析。

CMSIS层主要分为以下3个部分:

l核内外设访问层(CPAL,Core Peripheral Access Layer):该层由ARM负责实现包括对寄存器名称、地址的定义,对核寄存器、NVIC、调试子系统的访问接口定义以及

对特殊用途寄存器的访问接口(例如:CONTROL,xPSR)定义。由于对特殊寄存

器的访问以内联方式定义,所以针对不同的编译器ARM统一用__INLINE来屏蔽差

异。该层定义的接口函数均是可重入的。

l片上外设访问层(DPAL, Device Peripheral Access Layer):该层由芯片厂商负责实现。

该层的实现与CPAL类似,负责对硬件寄存器地址以及外设访问接口进行定义。该

层可调用CPAL层提供的接口函数同时根据设备特性对异常向量表进行扩展,以处

理相应外设的中断请求。

l外设访问函数(AFP , Access Functions for Peripherals):该层也由芯片厂商负责实现,主要是提供访问片上外设的访问函数,这一部分是可选的。

对一个Cortex-M微控制系统而言,CMSIS通过以上三个部分实现了:l定义了访问外设寄存器和异常向量的通用方法;

l定义了核内外设的寄存器名称和核异常向量的名称;

l为RTOS核定义了与设备独立的接口,包括Debug通道。

这样芯片厂商就能专注于对其产品的外设特性进行差异化,并且消除他们对微控制器进行编程时需要维持的不同的、互相不兼容的标准需求,以达到低成本开发的目的。

1.3 CMSIS标准的文件结构

图1.2 CMSIS的文件基本组织结构

如上图5.2中core_cm

Startup_

而system_