电子科技大学-集成电路原理实验-CMOS模拟集成电路设计与仿真

CMOS 模拟集成电路课件完整

VTHN VTHN0

2qsi Na Cox

VGS 1 0 1.0 VDS 2 0 5

.op .dc vds 0 5 .2 Vgs 1 3 0.5 .plot dc -I(vds) .probe

*model .MODEL MNMOS NMOS VTO=0.7 KP=110U +LAMBDA=0.04 GAMMA=0.4 PHI=0.7

.end

Systems

Ch13 开关电容电路

Ch14 DAC/ADC

complex Ch10 运算放大器 Ch7 频率响应

Ch11 稳定性和频 率补偿

Ch8 噪声

Ch12 比较器 Ch9 反馈

Ch3 电流源电流镜 simple Ch4 基准源 Circuits

Devices

Ch5 单级放大器 ch2 MOS器件

*Output Characteristics for NMOS M1 2 1 0 0 MNMOS w=5u l=1.0u

VGS 1 0 1.0 VDS 2 0 5

设计

属性/规范

系统/电路1

系统/电路2 系统/电路3

……

一般产品描述、想法 系统规范要求的定义

系统设计 电路模块规范定义

电路实现 电路仿真

否

是否满足系统规范

是 物理(版图)设计

物理(版图)验证

寄生参数提取及后仿真

否

是否满足系统规范

CMOS模拟集成电路分析与设计 ppt课件

如果栅电压为负,则耗尽层变薄,栅 与衬底间电容增大。

对于大的负偏置,则电容接近于CGC。

PPT课件

24

1.2 MOS管的极间电容(1)

G

S

C1

C2 C4

C3

Cbs

反型层 耗尽层

d

L

d

p型衬底

D

Cbd

PPT课件

25

1.2 MOS管的极间电容(2)

栅与沟道之间的栅氧电容:

C2=WLCox,其中Cox为单位面积栅氧电容εox/tox;

CMOS模拟集成电路分析与设计

主讲教师:吴建辉 Tel:83795677

E-mail:wjh@

PPT课件

1

教材及参考书

教材:

吴建辉编著:“CMOS模拟集成电路分析与设 计”(第二版),电子工业出版社。

参考书:

Razavi B: Design of analog CMOS integrated circuits

11

1、有源器件

主要内容:

1.1 几何结构与工作原理 1.2 极间电容 1.3 电学特性与主要的二次效应 1.4 低频及高频小信号等效模型 1.5 有源电阻

PPT课件

12

1.1 MOS管几何结构与工作原理(1)

B p+

G

tox

S

D

G D

n+

n+

p+

n阱 p型衬底

(a)

S

B

p+

n+

W

多晶

d p+接触孔

PPT课件

3

模拟电路与模拟集成电路

分立元件音频放大电路

晶体管数 匹配性 电阻值 电容值 寄生效应影响

电子科技大学 集成电路原理实验模拟集成电路版图设计与验证 王向展

实验报告课程名称:集成电路原理实验名称:模拟集成电路版图设计与验证小组成员:实验地点:科技实验大楼606实验时间:2017年6月19日2017年6月19日微电子与固体电子学院一、实验名称:模拟集成电路版图设计与验证二、实验学时:4三、实验原理1、电路设计与仿真实验2内容,根据电路的指标和工作条件,然后通过模拟计算,决定电路中各器件的参数(包括电参数、几何参数等),EDA软件进行模拟仿真。

2、工艺设计根据电路特点结合所给的工艺,再按电路中各器件的参数要求,确定满足这些参数的工艺参数、工艺流程和工艺条件。

3、版图设计按电路设计和确定的工艺流程,把电路中有源器件、阻容元件及互连以一定的规则布置在Candence下的版图编辑器内。

并优化版图结构。

四、实验目的本实验是基于微电子技术应用背景和《集成电路原理》课程设置及其特点而设置,为IC设计性实验。

其目的在于:1、根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路版图设计,掌握基本的IC版图布局布线技巧。

2、学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行版图的的设计与验证。

通过该实验,使学生掌握CMOS模拟IC版图设计的流程,加深对课程知识的感性认识,增强学生的设计与综合分析能力。

五、实验内容1、UNIX操作系统常用命令的使用,Cadence EDA仿真环境的调用。

2、根据实验2所得参数,自主完成版图设计,并掌握布局布线的基本技巧。

3、整理版图生成文件,总结、撰写并提交实验报告。

六、实验仪器设备(1)工作站或微机终端一台(2)EDA仿真软件1套七、实验步骤1、根据实验指导书掌握Cadence EDA仿真环境的调用。

熟悉版图编辑器Layout Editor的使用。

了解基本的布局布线方法及元器件的画法。

2、根据实验2所计算验证的两级共源CMOS运放的元器件参数如表1所示,在版图设计器里画出相应的元器件,对V+、V-、V out、V DD、GND的压焊点位置合理化放置,通过金属画线将各个元器件按实验2的电路图合理连接,避免跳线。

cmos集成电路设计教案

cmos集成电路设计教案写作主题:CMOS集成电路设计教案文章序号:1引言:CMOS(Complementary Metal-Oxide-Semiconductor)集成电路设计是现代电子工程中的一个重要领域。

它涉及到数字电路、模拟电路和混合信号电路的设计与实现。

设计一份高质量的CMOS集成电路设计教案对于培养电子工程师的技能和知识至关重要。

本文将深入探讨CMOS集成电路设计教案的多个方面,包括教学目标、教学内容、教学方法、教学评估和实践应用等。

文章序号:2教学目标:CMOS集成电路设计教案的教学目标是帮助学生全面理解CMOS集成电路的原理和设计方法,培养他们的设计能力和实践能力。

具体而言,教学目标包括:1. 理解CMOS集成电路的基本原理和工作方式。

2. 掌握CMOS集成电路设计中的关键概念和方法。

3. 熟悉CMOS集成电路设计工具和流程。

4. 能够进行CMOS集成电路的模拟和数字仿真。

5. 能够设计和实现简单的CMOS集成电路。

文章序号:3教学内容:CMOS集成电路设计教案的教学内容应包括以下方面:1. CMOS原理和工作方式的介绍- N沟道和P沟道MOSFET的结构和特性- CMOS逻辑门电路的实现和特点2. CMOS集成电路设计基础知识- 逻辑门电路和时序电路的设计- 模拟电路的设计和仿真- 时钟和时序设计3. CMOS集成电路设计工具和流程- EDA工具的介绍和使用方法- CMOS电路的布局和布线规则- 物理设计和验证4. CMOS集成电路实践应用- 集成电路的应用领域和发展趋势- 嵌入式系统设计与应用- 特定应用领域的案例分析文章序号:4教学方法:为了实现教学目标,采用多种教学方法是必要的。

在CMOS集成电路设计教案中,可以采用以下教学方法:1. 理论讲解:通过课堂讲解,向学生介绍CMOS集成电路的基本原理和设计方法。

重点讲解关键概念和方法。

2. 实验实践:组织学生进行一系列的实验实践,包括模拟仿真和数字逻辑实现。

电子科技大学-集成电路原理实验-CMOS模拟集成电路设计与仿真

实验报告课程名称:集成电路原理实验名称:CMOS模拟集成电路设计与仿真一、实验名称:CMOS模拟集成电路设计与仿真二、实验学时:4三、实验原理1、转换速率(SR):也称压摆率,单位是V/μs。

运放接成闭环条件下,将一个阶跃信号输入到运放的输入端,从运放的输出端测得运放的输出上升速率。

2、开环增益:当放大器中没有加入负反馈电路时的放大增益称为开环增益。

3、增益带宽积:放大器带宽和带宽增益的乘积,即运放增益下降为1时所对应的频率。

4、相位裕度:使得增益降为1时对应的频率点的相位与-180相位的差值。

5、输入共模范围:在差分放大电路中,二个输入端所加的是大小相等,极性相同的输入信号叫共模信号,此信号的范围叫共模输入信号范围。

6、输出电压摆幅:一般指输出电压最大值和最小值的差。

图1两级共源CMOS运放电路图实验所用原理图如图1所示。

图中有多个电流镜结构,M1、M2构成源耦合对,做差分输入;M3、M4构成电流镜做M1、M2的有源负载;M5、M8构成电流镜提供恒流源;M8、M9为偏置电路提供偏置。

M6、M7为二级放大电路,Cc为引入的米勒补偿电容。

其中主要技术指标与电路的电气参数及几何尺寸的关系:转换速率:第一级增益:第二级增益:单位增益带宽:输出级极点:零点:正CMR:负CMR:饱和饱和电压:饱和功耗:四、实验目的本实验是基于微电子技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,为IC设计性实验。

其目的在于:∙根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路设计,掌握基本的IC设计技巧。

∙学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行电路的模拟仿真。

五、实验内容1、根据设计指标要求,针对CMOS两级共源运放结构,分析计算各器件尺寸。

2、电路的仿真与分析,重点进行直流工作点、交流AC和瞬态Trans分析,能熟练掌握各种分析的参数设置方法与仿真结果的查看方法。

3、电路性能的优化与器件参数调试,要求达到预定的技术指标。

电子科大集成电路原理实验报告-CMOS模拟集成电路设计与仿真标准实验报告

电子科大集成电路原理实验报告-CMOS模拟集成电路设计与仿真标准实验报告电子科技大学微电子与固体电子学院集成电路原理与设计CMOS模拟集成电路设计与仿真电子科技大学实验报告实验地点:211楼606 实验时间:2014.6.7一、实验室名称:微电子技术实验室二、实验项目名称:CMOS模拟集成电路设计与仿真三、实验学时:4四、实验原理参照实验指导书。

五、实验目的本实验是基于微电子技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,为IC设计性实验。

其目的在于:根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路设计,掌握基本的IC设计技巧。

学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行电路的模拟仿真。

六、实验内容1、UNIX操作系统常用命令的使用,Cadence EDA仿真环境的调用。

2、设计一个运算放大器电路,要求其增益大于40dB, 相位裕度大于60?,功耗小于10mW。

3、根据设计指标要求,选取、确定适合的电路结构,并进行计算分析。

4、电路的仿真与分析,重点进行直流工作点、交流AC分析、瞬态Trans分析、建立时间小信号特性和压摆率大信号分析,能熟练掌握各种分析的参数设置方法。

5、电路性能的优化与器件参数调试,要求达到预定的技术指标。

6、整理仿真数据与曲线图表,撰写并提交实验报告。

七、实验仪器设备(1)工作站或微机终端一台(2)局域网2(3)EDA仿真软件 1套八、实验步骤1、根据实验指导书熟悉UNIX操作系统常用命令的使用,掌握Cadence EDA仿真环境的调用。

2、根据设计指标要求,设计出如下图所示的电路结构。

并进行计算分析,确定其中各器件的参数。

3、电路的仿真与分析,重点进行直流工作点、交流AC分析、瞬态Trans分析,能熟练掌握各种分析的参数设置方法。

4、电路性能的优化与器件参数调试,要求达到预定的技术指标。

具体计算步骤如下:(参见模拟CMOS集成电路设计)1. 通过额定功耗和片外电容C计算偏置电路电流以及流进M6,M8电流,再通过相关试验得到相关pmos,nmos的Vth和k和λ,得到m6,m8,m9宽长比并计算密勒电容Cc2. 通过cmr计算m4和m0的宽长比3. 通过GB和Cc求出m2和m5宽长比4. 由m6,m8的Ids电流计算m7宽长比5. 进行电路仿真,观察电路是否符合各方面要求。

电子科技大学CMOS模拟集成设计Hspice仿真

以下用实例说明 Hspice 的输入电路程序。 的输入电路程序。

1

NMOS II-V Characteristic 测试电路: 测试电路:

图 1-1 NMOS I-V 特性测试电路 ------------------------------------------------------------------------------------------------------------------

图 1-8 Hspice InstallShield Wizard

2. 选择安装目录。Click“Next”选择 default 目录,如图 1-9 所示。 C:\synopsys\Hspice_A-2008.03-SPI 是 default 的目录。

7

图 1-9 InstallShield Wizard 选择安装目录

饱和状态下 NMOS 电压电流关系公式[1-1]中的参数Kn, VT 和 λn是 CMOS 工艺参数,理想状态下是常数。 针对一具体 CMOS 工艺技术, 通过仿真求取以上工艺参数是模拟电路设计的第 一步。

4. 实验步骤: 实验步骤: 练习一: 练习一: 下载/安装/ 安装/设置 Hspice 仿真软件 步骤一:在本机的桌面建一子目录 2008Hspice。 步骤一 步骤二:从指定的机器和目录中,下载图 1-5 中 23 个压缩文件到本机的子目录 步骤二 2008Hspice 下。 文件 _Hspice.pቤተ መጻሕፍቲ ባይዱrt01 到 _Hspice.part22 是 Hspice 的 setup 文件的压缩, _Hspice.2008-03 是 Hspice 2008 版的 license 文件的压缩。

实验目录

实验一: 实验一:EDA 仿真软件 Hspice 及 CMOS 工艺技术参数 实验二: 实验二:CMOS Differential Amplifier Design 差分放大器设计 实验三: 实验三:CMOS Operational Amplifier Design 运算放大器设计 实验四: 实验四:CMOS AnalogAnalog-toto-Digital Converter 模数转换器( 模数转换器(ADC) ADC)设计

cmos模拟集成电路设计-实验报告

cmos模拟集成电路设计-实验报告————————————————————————————————作者:————————————————————————————————日期:北京邮电大学实验报告实验题目:cmos模拟集成电路实验姓名:何明枢班级:2013211207班内序号:19学号:2013211007指导老师:韩可日期:2016 年 1 月16 日星期六目录实验一:共源级放大器性能分析 (1)一、实验目的 (1)二、实验内容 (1)三、实验结果 (1)四、实验结果分析 (3)实验二:差分放大器设计 (4)一、实验目的 (4)二、实验要求 (4)三、实验原理 (4)四、实验结果 (5)五、思考题 (6)实验三:电流源负载差分放大器设计 (7)一、实验目的 (7)二、实验内容 (7)三、差分放大器的设计方法 (7)四、实验原理 (7)五、实验结果 (9)六、实验分析 (10)实验五:共源共栅电流镜设计 (11)一、实验目的 (11)二、实验题目及要求 (11)三、实验内容 (11)四、实验原理 (11)五、实验结果 (15)六、电路工作状态分析 (15)实验六:两级运算放大器设计 (17)一、实验目的 (17)二、实验要求 (17)三、实验内容 (17)四、实验原理 (22)五、实验结果 (23)六、思考题 (24)七、实验结果分析 (25)实验总结与体会 (26)一、实验中遇到的的问题 (26)二、实验体会 (26)三、对课程的一些建议 (27)实验一:共源级放大器性能分析一、实验目的1、掌握synopsys软件启动和电路原理图(schematic)设计输入方法;2、掌握使用synopsys电路仿真软件custom designer对原理图进行电路特性仿真;3、输入共源级放大器电路并对其进行DC、AC分析,绘制曲线;4、深入理解共源级放大器的工作原理以及mos管参数的改变对放大器性能的影响二、实验内容1、启动synopsys,建立库及Cellview文件。

模拟cmos集成电路设计研究生课程实验报告

模拟cmos集成电路设计研究生课程实验报告模拟CMOS集成电路设计研究生课程实验报告1. 引言在现代电子工程领域中,模拟CMOS集成电路设计一直是一个备受关注的研究领域。

本文将对模拟CMOS集成电路设计研究生课程实验进行全面评估,并撰写一份有价值的实验报告。

通过这篇文章,我们将深入探讨模拟CMOS集成电路设计的原理、方法和实践,为读者带来深刻而全面的理解。

2. 实验内容本次课程实验旨在通过实际操作,让学生深入理解模拟CMOS集成电路设计的基本原理和流程。

实验包括了对CMOS集成电路的基本认识、基于SPICE仿真工具的电路模拟设计、以及实际电路的布局与布线等内容。

在实验中,学生需要掌握CMOS集成电路的工作原理、信号传输特性、电路设计的基本流程以及布局与布线的关键技术。

3. 深度评估通过对实验内容的深度评估,我们可以认识到模拟CMOS集成电路设计的复杂性和重要性。

学生需要理解CMOS技术在集成电路设计中的核心地位,以及其在实际电路中的应用。

SPICE仿真工具在电路设计中的作用和优势也是本次实验的重要内容。

电路的布局与布线对于电路性能的影响不可忽视,学生需要深入理解布局布线的原理和方法。

4. 文章撰写在文章的撰写过程中,我们将按照知识的文章格式进行,使用序号标注,并在内容中多次提及模拟CMOS集成电路设计这一主题。

在文章的开头,我们将对模拟CMOS集成电路设计的重要性和实验的背景进行介绍,为读者带来对主题的直观了解。

我们将从CMOS集成电路的基本原理和工作特性入手,逐步展开对实验内容的深入解析。

在文章的结尾,我们将总结实验的收获和体会,共享对模拟CMOS集成电路设计的个人观点和理解。

5. 总结与展望通过本文的撰写和深度评估,我们不仅对模拟CMOS集成电路设计研究生课程实验进行了全面解析,同时也为读者带来了对这一领域的深刻理解和启发。

未来,希望能进一步探讨模拟CMOS集成电路设计的前沿技术和发展趋势,为电子工程领域的学术研究和技术应用提供更多有价值的内容。

实验二CMOS模拟集成电路设计与仿真

实验二CMOS模拟集成电路设计与仿真实验二 CMOS 模拟集成电路设计与仿真CMOS(Complementary Metal-Oxide-Semiconductor)模拟集成电路(Analog Integrated Circuits)是一种基于金属-氧化物-半导体结构的集成电路技术。

在本实验中,我们将学习并实践CMOS模拟集成电路的设计和仿真,以加深对其原理和应用的理解。

通过此实验,我们将能够熟练掌握CMOS模拟集成电路设计与仿真的基本流程与方法。

一、实验目的本实验旨在通过设计和仿真CMOS模拟集成电路,加深对其工作原理的理解,掌握电路设计与仿真的基本方法。

二、实验原理CMOS模拟集成电路是一种基于n型和p型MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)的电路。

通过调节不同MOS管的工作状态,可以实现不同的电路功能。

其中,n型MOS管的主要特点是电导率高,适用于放大增益较大的部分;p型MOS管的主要特点是电导率低,适用于控制电流流动的部分。

三、实验步骤1. 电路设计:根据实际需求,确定设计所需的CMOS模拟集成电路。

在设计前,应先详细了解电路的功能、性能及工作原理,确定所需的器件数目和性能参数。

2. 电路布局:根据设计要求,将设计的各个电路模块在模拟集成电路上进行布局,合理安排电路的位置和空间,以保证电路的稳定性和性能。

3. 电路连接:按照布局图,将所需的电路模块进行连接,确保各个模块之间信号的正确传输和电路功能的正常实现。

4. 电路仿真:使用专业的仿真软件,将设计好的CMOS模拟集成电路进行仿真,验证其电路性能和功能。

在仿真过程中,应注意选择合适的仿真参数和验证方法,以保证仿真结果的准确性和可靠性。

5. 仿真分析:根据仿真结果,对电路的性能和功能进行分析和评估。

如果发现问题或改进的空间,可以根据分析结果进行相应的调整和优化。

6. 总结与展望:根据实验结果和分析,总结实验过程中的经验和教训,提出可能的改进和未来的研究方向。

集成电路设计基础课程设计 单级CMOS放大电路的设计与仿真

单级CMOS放大电路的设计与仿真摘要:本文对单击CMOS放大器电路进行设计和仿真。

首先将对CMOS管进行简单介绍和进行特性分析,并对单级CMOS放大电路的设计原理做了简单介绍。

然后根据设计要求,通过Hspice软件仿真系统对单级CMOS放大电路进行仿真,包括直流工作点的分析,瞬态分析,傅里叶分析。

并对其静态工作点和交流小信号分析做出阐述。

从而使我们了解到模拟CMOS集成电路的一般设计方法和思路,以及Hspice软件的一些基本操作和防真功能。

通过实际操作进一步了解CMOS的特性以及在我们的实际生活中具有什么样的地位。

关键词:直流工作点分析、单级CMOS放大电路、仿真操作、CMOS晶体管、瞬态分析、傅里叶分析、HspiceAbstract:The click CMOS amplifier circuit design and simulation. The first of CMOS tube was introduced and the characteristics are analyzed, and on the single stage CMOS amplifying circuit design principle was briefly introduced. Then according to design requirements, through the Hspice software simulation system on single CMOS amplification circuit simulation, including DC operating point analysis, transient analysis, Fourier analysis. And the static working point and make the small signal analysis. In order to make us understand the analog CMOS integrated circuit design method and train of thought, as well as the Hspice software of some of the basic operation and function of preventing it.Through the actual operation to further understand the characteristics of CMOS and our real life have what kind of positionKey word.Analysis of DC, single stage CMOS amplification circuit, simulation operation, CMOS transistor, transient analysis, Fourier analysis, Hspice1.综述:金属氧化物半导体场效应晶体管,简称金氧半场效应晶体管。

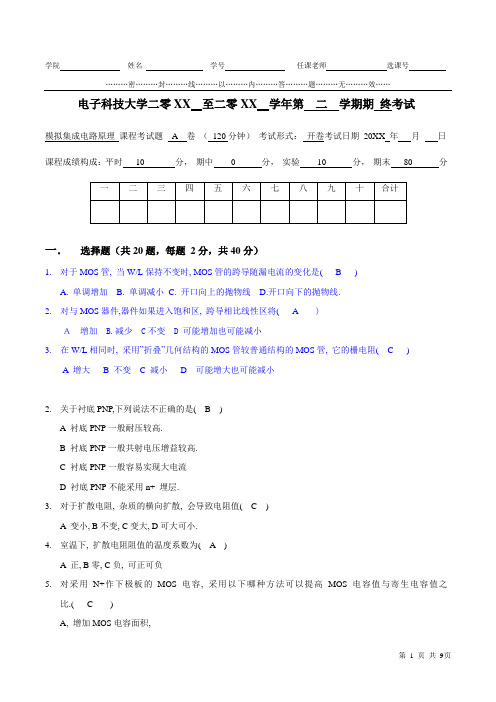

电子科技大学大二微电子专业模拟集成电路试卷及答案 (2)

………密………封………线………以………内………答………题………无………效……电子科技大学二零XX 至二零XX 学年第X 学期期终考试模拟集成电路原理课程考试题 A 卷(120分钟)考试形式:开卷考试日期20XX 年月日课程成绩构成:平时10 分,期中0 分,实验10 分,期末80 分一二三四五六七八九十合计一.选择题(共20题,每题2分,共40分)1.对于MOS管, 当W/L保持不变时, MOS管的跨导随漏电流的变化是( B )A. 单调增加B. 单调减小C. 开口向上的抛物线D.开口向下的抛物线.2. 对与MOS器件,器件如果进入饱和区, 跨导相比线性区将( A )A增加 B.减少 C不变 D 可能增加也可能减小3. 在W/L相同时, 采用”折叠”几何结构的MOS管较普通结构的MOS管, 它的栅电阻( C )A 增大B 不变C 减小D 可能增大也可能减小4. 关于衬底PNP,下列说法正确的是( A )A.所有衬底PNP集电极电压必须相同.B.所有衬底PNP发射极电压必须相同.C.所有衬底PNP基极电压必须相同.D.所有衬底PNP各个电极电压可以任意设定5. 对于扩散电阻, 其宽度越大, 则电阻值越易做得( A )A 精确, B误差大, C 误差可大可小, D电阻间的相对误差大.6. 室温下, 扩散电阻阻值的温度系数为( A )A 正, B零, C负, 可正可负7.在集成电路中决定互联线宽度的因素有( A )A.大电流密度限制.B.Si-Al互熔问题.C.互联线的温度系数………密………封………线………以………内………答………题………无………效……D.是否形成欧姆接触.8. 套筒式共源共栅运放和折叠式共源共栅运放相比, 它的( B )较大些A. 最大电压输出摆幅B. 差模增益C. 极点频率D.功耗9.在版图设计上, 采用比例电阻和比例电容的设计可以( C )A. 提高电阻或电容自身的绝对精度,B. 提高电阻或电容自身的相对精度,C. 减小电阻或电容间的比例误差D. 无影响10.差分对中, 不影响其共模抑制比的因素为( C )A.差分管的对称性B.电流源的交流阻抗C.输入电压幅度D.电阻R C1和R C2的对称性11. Cascode电流镜的最小输出电压V MIN(out)的值为( C )A.V ON+V TN B.2(V ON+V TN) C. 2V ON+V TN D. V ON+2V TN12.对于ED NMOS基准电压源电路, 其中的两个NMOS的工作状态为( A )A, 都是饱和区B. 一个是饱和区, 一个是线性区C 都是线性区D都是亚阈值区13正偏二级管正向压降具有( B )温度特性.A . 零 B. 负 C. 正 D. 可正可负14. MOS共栅放大器的特点是( D )A.放大器输入输出反相, 输入阻抗高B.放大器输入输出同相, 输入阻抗高………密………封………线………以………内………答………题………无………效……C.放大器输入输出反相, 输入阻抗低D.放大器输入输出同相, 输入阻抗低15. 电路的主极点是( D )A离原点最远的极点, 它对应电路的-3dB带宽B 离原点最远的极点, 它对应电路的单位增益带宽C离原点最近的极点, 它对应电路的单位增益带宽D.离原点最近的极点, 它对应电路的-3dB带宽16.在CMOS差分输入级中, 下面的做法哪个对减小输入失调电压有利( C )A.增大有源负载管的宽长比.B.提高静态工作电流..C.增大差分对管的沟道长度和宽度D.提高器件的开启(阈值)电压17.在差分电路中, 可采用恒流源替换”长尾”电阻. 这时要求替换”长尾”的恒流源的输出电阻( A )A.越高越好, B.越低越好 C. 没有要求D. 可高可低18. 和共源极放大器相比较, 共源共栅放大器的密勒效应要( A )A.小得多B相当, C 大得多. D不确定19.在版图设计上, 采用比例电阻和比例电容的设计可以( C )A. 提高电阻或电容自身的绝对精度,B. 提高电阻或电容自身的相对精度,C. 减小电阻或电容间的比例误差D. 无影响20.对于差分对的版图设计下列( D )图最优.………密………封………线………以………内………答………题………无………效……二. 简答题(共5题,每题4分, 共20分)1. 画出共源共栅放大器基本结构, 简述其工作原理及特点.答:基本原理:M1为输入器件,M2为共源共栅器件,共源级M1将输入电压信号Vin 转换为电流信号g m Vin ,该电流信号流入M2漏端,从其源端输入到负载。

实验一 COMS电流电压电路仿真实验-(空白)

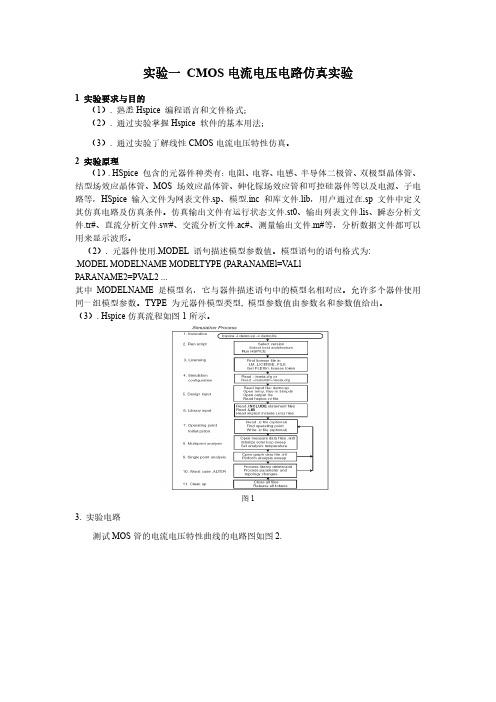

实验一CMOS电流电压电路仿真实验1 实验要求与目的(1). 熟悉Hspice 编程语言和文件格式;(2). 通过实验掌握Hspice 软件的基本用法;(3). 通过实验了解线性CMOS电流电压特性仿真。

2 实验原理(1). HSpice 包含的元器件种类有:电阻、电容、电感、半导体二极管、双极型晶体管、结型场效应晶体管、MOS 场效应晶体管、砷化镓场效应管和可控硅器件等以及电源、子电路等,HSpice 输入文件为网表文件.sp、模型.inc 和库文件.lib,用户通过在.sp 文件中定义其仿真电路及仿真条件。

仿真输出文件有运行状态文件.st0、输出列表文件.lis、瞬态分析文件.tr#、直流分析文件.sw#、交流分析文件.ac#、测量输出文件.m#等,分析数据文件都可以用来显示波形。

(2). 元器件使用.MODEL 语句描述模型参数值。

模型语句的语句格式为:.MODEL MODELNAME MODELTYPE (PARANAMEl=V ALlPARANAME2=PV AL2 ...其中MODELNAME 是模型名,它与器件描述语句中的模型名相对应。

允许多个器件使用同一组模型参数。

TYPE 为元器件模型类型, 模型参数值由参数名和参数值给出。

(3). Hspice仿真流程如图1所示。

图13. 实验电路测试MOS管的电流电压特性曲线的电路图如图2.图2 MOS管输出特性曲线4 实验步骤(1)Hspice仿真SP文件如下:.title MOS IV characters**************model NMOS************************ .MODEL NMOS NMOS (+LEVEL=1 VT0=0.7 GAMMA=0.45 PHI=0.9+NSUB=9e+14 LD=0.08e-6 U0=350 LAMBDA=0.1 +TOX=9e-9 PB=0.9 CJ=0.56e-3 CJSW=0.35e-11 +MJ=0.45 MJSW=0.2 CGDO=0.4e-9 JS=1.0e-8)**************model PMOS************************ .MODEL PMOS PMOS (+LEVEL=1 VT0=-0.8 GAMMA=0.4 PHI=0.8+NSUB=5e+14 LD=0.09e-6 U0=100 LAMBDA=0.2 +TOX=9e-9 PB=0.9 CJ=0.94e-3 CJSW=0.32e-11 +MJ=0.5 MJSW=0.3 CGDO=0.3e-9 JS=0.5e-8)************************************************ **************netlist***************************M1 DN GN SN BN NMOS W=1u L=0.5uM2 DP GP SP BP PMOS W=1u L=0.5u**************source**************************** VDSN DN SN 0VGSN GN SN 0VSN SN 0 0VBN BN 0 0VSDP SP DP 0VSGP SP GP 0VSP SP 0 3.3VBP BP 0 3.3**************analysis**************************.DC VDSN 0 3.3 0.05 sweep VGSN 0 3 0.5 .DC VSDP 3.3 0 0.05 sweep VGSN 0 3 0.5 .probe i(M1) i(M2) lx7(M1) lx7(M2).end(2)仿真过程a.NMOS漏电流b.NMOS跨导c.沟道长度设置为1u, 漏电流特性曲线仿真图d. NMOS的栅源电压为1.2VHspice仿真SP文件.title MOS IV characters**************model NMOS************************ .MODEL NMOS NMOS (+LEVEL=1 VT0=0.7 GAMMA=0.45 PHI=0.9+NSUB=9e+14 LD=0.08e-6 U0=350 LAMBDA=0.1 +TOX=9e-9 PB=0.9 CJ=0.56e-3 CJSW=0.35e-11 +MJ=0.45 MJSW=0.2 CGDO=0.4e-9 JS=1.0e-8)**************model PMOS************************ .MODEL PMOS PMOS (+LEVEL=1 VT0=-0.8 GAMMA=0.4 PHI=0.8+NSUB=5e+14 LD=0.09e-6 U0=100 LAMBDA=0.2 +TOX=9e-9 PB=0.9 CJ=0.94e-3 CJSW=0.32e-11 +MJ=0.5 MJSW=0.3 CGDO=0.3e-9 JS=0.5e-8)************************************************ **************netlist***************************M1 DN GN SN BN NMOS W=1u L=0.5uM2 DP GP SP BP PMOS W=1u L=0.5u**************source**************************** VDSN DN SN 0VGSN GN SN 1.2VSN SN 0 0VBN BN 0 0VSDP SP DP 0VSGP SP GP 1.2VSP SP 0 3.3VBP BP 0 3.3.DC VDSN 0 3.3 0.05.DC VSDP 3.3 0 0.05 .probe i(M1) i(M2) .end仿真图5. 实验结果分析。

CMOS模拟集成电路设计与仿真实验指导书

CMOS模拟集成电路设计与仿真实验指导书模拟集成电路原理实验指导书二零一二年五月实验1 集成电路版图识别与提取一、实验目的随着IT产业的迅速发展,集成电路在国民经济和国防建设中的地位日益突出。

IC设计技术尤显重要。

版图识别与提取是微电子IC逆向设计的关键技术。

一方面可借鉴并消化吸收先进、富有创意的版图设计思想、结构。

建立自己的版图库;另一方面通过分析、优化已有版图可将原有芯片的性能加以改进提高。

本实验是基于微电子技术应用背景和《模拟集成集成电路》课程设置及其特点而设置,目的在于:1增加对塑封、陶瓷封装等不同封装形式的感性认识;2 增加对硅圆片、芯片的感性认识;3 学习并掌握集成电路版图的图形识别、电路拓扑结构提取。

4能对提取得到的电路进行功能分析、确定,并可运用EDA软件展开模拟仿真。

二、实验原理本实验重点放在版图识别、电路拓扑提取、版图编辑三大模块,实验流程如下:三、实验内容1.观察典型集成电路的封装形式;2.观察集成电路成品剖片的电路结构;3.观察硅圆片与未封装的芯片;4.在芯片上找出划片槽、测试单管、分布在芯片边缘的压焊点、对位标记,并测出有关图形的尺寸和间距。

仔细观察芯片图形的总体布局,找出电源线、地线、输入端、输出端以及相应的压焊点;6.判断集成电路的工艺类别;7.根据以上判断、提取芯片上图形所示电路图的拓扑结构;复查、修正,并进行仿真验证。

四、实验步骤1.观察典型集成电路的封装形式;2.对集成电路成品剖片的电路结构进行观察;3.观察测试单管。

仔细观察芯片的布局布线,找出电源线和地线。

4.确定芯片工艺类别,分清单个的元件结构,提取版图电路拓扑结构五、实验报告1.版图识别与提取过程总结2.绘出所提版图的电路拓扑结构六、附:版图照片(含铝线照片):金属1层去铝线照片衬底层课下思考练习: 金属1层去铝线照片衬底层实验2CMOS模拟集成电路设计与仿真一、实验目的与意义随着IT产业的迅猛发展,微电子集成电路在通讯、计算机及其他消费类电子产品中的重要地位日益突出,而IC的生产和设计技术水平是决定IC芯片性能的两大要素。

电子科技大学大二微电子专业模拟集成电路试卷及答案 (1)

………密………封………线………以………内………答………题………无………效……电子科技大学二零XX 至二零XX 学年第二学期期终考试模拟集成电路原理课程考试题 A 卷(120分钟)考试形式:开卷考试日期20XX 年月日课程成绩构成:平时10 分,期中0 分,实验10 分,期末80 分一二三四五六七八九十合计一.选择题(共20题,每题2分,共40分)1.对于MOS管, 当W/L保持不变时, MOS管的跨导随漏电流的变化是( B )A. 单调增加B. 单调减小C. 开口向上的抛物线D.开口向下的抛物线.2. 对与MOS器件,器件如果进入饱和区, 跨导相比线性区将( A )A增加 B.减少 C不变 D 可能增加也可能减小3. 在W/L相同时, 采用”折叠”几何结构的MOS管较普通结构的MOS管, 它的栅电阻( C )A 增大B 不变C 减小D 可能增大也可能减小2.关于衬底PNP,下列说法不正确的是( B )A 衬底PNP一般耐压较高.B 衬底PNP一般共射电压增益较高.C 衬底PNP一般容易实现大电流D 衬底PNP不能采用n+ 埋层.3.对于扩散电阻, 杂质的横向扩散, 会导致电阻值( C )A 变小, B不变, C变大, D可大可小.4.室温下, 扩散电阻阻值的温度系数为( A )A 正, B零, C负, 可正可负5.对采用N+作下极板的MOS电容, 采用以下哪种方法可以提高MOS电容值与寄生电容值之比.( C )A, 增加MOS电容面积,………密………封………线………以………内………答………题………无………效……B. 减小MOS电容面积.C 增加衬底的反向偏压.D 减小衬底的反向偏压.6.在版图设计中, 电学规则检查称为( B )A. EXTRACTB. ERCC. DRCD. LVS7.随着微电子工艺水平提高, 特征尺寸不断减小, 这时电路的工作电压会( D )A不断提高 B. 不变 C. 可大可小 D. 不断降低8.对CMOS PTAT源,器件是工作在( D )A.饱和区和线性区 B. 都是饱和区 C.线性区和亚阈区 D. 饱和区和亚阈区9.下图示出的剖面图( C )ABA.A是纵向pnp, B是纵向pnpB.A是横向pnp, B是纵向pnpC.A是纵向pnp, B是横向pnpD.A是横向pnp, B是横向pnp10.对于电流镜的要求, 那种说法正确( C )A. 输出阻抗高B输出阻抗低C交流输出阻抗高D直流输出阻抗高11.Cascode电流镜的最小输出电压V MIN(out)的值为( C )A.V ON+V TN B.2(V ON+V TN) C. 2V ON+V TN D. V ON+2V TN12.差分放大器差模电压增益为( B )A.-g m R c B. g m R c C. -2g m R c D. 2g m R c………密………封………线………以………内………答………题………无………效……13.在下列防止CMOS IC中闩锁效应的办法中,( C )不可采用。

模拟CMOS集成电路SEL仿真验证研究

模拟CMOS 集成电路作为一种重要的基础器件被广 泛地应用于航天电子装备中袁 大多数模拟 CMOS 集成电路对空间辐照环境非常敏感袁 辐射环境对 集成电路的性能会产生不同程度的负面影响袁 甚 至会使其彻底失效遥

收稿日期院 2018-08-30 作者简介院 罗俊 渊1982-冤袁 男袁 四川南充人袁 中国电子科技集团公司第二十四研究所检测中心副主任尧 高级工程师袁 博士袁

电子产品可靠性与环境试验 耘蕴耘悦栽砸韵晕陨悦 孕砸韵阅哉悦栽 砸耘L陨粤月陨蕴I栽再 粤晕阅 耘晕灾陨R韵晕酝耘晕栽粤蕴 栽耘杂栽陨晕郧

仿真建模与分析

模拟 CMOS 集成电路 SEL 仿真验证研究

罗俊

渊中国电子科技集团公司第二十四研究所袁 重庆 400060冤

摘 要院 为了解决航天用模拟 CMOS 集成电路的单粒子闩锁效应的评估问题袁 结合一种基于失效物理的半导

体器件仿真方法袁 提出了基于失效物理的模拟 CMOS 集成电路单粒子闩锁仿真验证方法袁 并在此基础上袁 以某

型 8 位抗辐照 AD 转换器芯片为研究对象袁 通过对该 CMOS 单元器件的抗单粒子闩锁能力高于 75 MeV/mg窑cm2袁 与实际的试验结果一致遥

从事宽禁带半导体材料与器件尧 半导体集成电路可靠性技术方面的研究和管理工作遥

阅陨粤晕在陨 悦匀粤晕孕陨晕 运耘运粤韵X陨晕郧 再哉 匀哉粤晕允I晕郧 杂匀陨再粤晕

47

电子产品可靠性与环境试验

2019 年

航天应用时袁 空间中的高能离子入射到集成 电路时袁 如果在入射路径沉积的能量足够引起集 成电路的性能下降甚至功能丧失袁 我们称其为单 粒子效应袁 对模拟 CMOS 集成电路的影响较大袁 也是最常关注的主要是单粒子闩锁 渊SEL院 Single Event Latchup冤 效应 遥 [1-4] 为了评估研制器件的抗 SEL 能力袁 通常需要进行地面单粒子效应模拟实 验袁 目前抗辐射器件的研制通常是 野设计-制造试验冶 的反复过程袁 代价非常昂贵袁 而且一次反 复的设计周期很长遥 并且袁 由于进行实验的离子 加速器十分昂贵袁 国内有能力进行单粒子效应模 拟实验的单位不多袁 而需要进行单粒子试验的抗 辐射器件研制的企业有很多袁 这就导致抗辐射器 件的研制周期更加不可控遥 采用基于失效物理的 模拟 CMOS 集成电路 SEL 仿真验证技术为解决器 件研制过程中的抗单粒子效应能力评估提供了一 条新的思路 遥 [5-7] 本文采用了 Synopsys 公司出品的 Sentaurus TCAD 仿真软件进行模拟 CMOS 集成电 路 SEL 仿真模拟遥

电子科技大学集成电路实验报告――模拟集成电路

电子科技大学集成电路实验报告――模拟集成电路CMOS模拟集成电路设计及HSPICE使用实验学时:4学时实验一CMOS工艺参数测量一、实验目的:学习和掌握EDA仿真软件Hspice;了解CMOS工艺技术及元器件模型,掌握MOSFET工作原理及其电压电流特征;通过仿真和计算,获得CMOS中NMOS和PMOS的工艺参数kp,kn, p, n,Vtp,Vtn,为后续实验作准备。

二、实验内容:1)通过Hspice仿真,观察NMOS和PMOS管子的I-V特性曲线;2)对于给定长宽的MOSFET,通过Hspice仿真,测得几组栅-源电压、漏-源电压和漏-源电流数据,代入公式IDSn1WKn()n(VGS Vtn)2(1 nVDS),求得对应的工艺参数2Lkp,kn, p, n,Vtp,Vtn 。

三、实验结果:本实验中所测试的NMOS管、PMOS管L=1u,W由学号确定。

先确定W。

W等于学号的最后一位,若学号最后一位=0,则W=10u。

所以,本实验中所测试的NMOS管、PMOS管的尺寸为:(1)测0.5um下NMOS和PMOS管的I-V特性曲线所用工艺模型是TSMC 0.50um。

所测得的Vgs=1V时,NMOS管Vds从0V到2.5V变化时的I-V特性曲线为:所测得的Vds=1.2V时,NMOS管Vgs从0V到2.5V变化时的I-V特性曲线为:所测得的Vsg=1V时,PMOS管Vsd从0V到2.5V变化时的I-V特性曲线为:所测得的Vsd=1.2V时,PMOS管Vsg从0V到2.5V变化时的I-V特性曲线为:(2)计算TSMC 0.50um工艺库下mos管对应的工艺参数测试NMOS管相关参数,Hspice中仿真用源文件(.sp文件)为:NOMS I-V Characteristic M1 OUT IN 0 0 CMOSn L=1U W=8U VIN IN 0 1 VOUT OUT 0 1.2.***** LIST NODE POST *.DC VOUT 0 2.5 0.1 .DC VIN 0 2.5 0.1*.DC VOUT 0 2.5 0.1 VIN 0.8 1.0 0.2 .PRINT DC I(M1).LIB “C:\synopsys\project\tsmc_050um_model.lib"CMOS_MODELS .END所测得的NMOS管电流曲线为:所测的数据如下表:根据公式IDSn1Kn()n(VGS Vtn)2(1 nVDS),计算kn, n,Vtn,分别为:2Lkn 119 10-6, n 0.028,Vtn 1.37测试PMOS管相关参数,Hspice中仿真用源文件(.sp文件)为:POMS I-V CharacteristicM1 OUT IN Vdd Vdd CMOSP L=1U W=8UVIN Vdd IN 1 VOUT Vdd OUT 1.2.***** LIST NODE POST *.DC VOUT 0 2.5 0.1 .DC VIN 0 2.5 0.1*.DC VOUT 0 2.5 0.1 VIN 0.8 1.0 0.2.PRINT DC I(M2).LIB "C:\synopsys\project\tsmc_050um_model.lib"CMOS_MODELS .END所测得的PMOS管电流曲线为:所测的数据如下表:计算TSMC 0.50um 工艺中pmos 参数pptp,分别为:Kp 54.89 10-6, p 0.017,Vtp 0.927综上所述,可得:四、思考题2)不同工艺,p, n不同。

模拟CMOS集成电路设计课程设计实验报告(二级放大器的设计)

模拟CMOS集成电路设计课程设计报告--------二级运算放大器的设计信息科学技术学院电子与科学技术系一、概述:运算放大器是一个能将两个输入电压之差放大并输出的集成电路。

运算放大器是模拟电子技术中最常见的电路,在某种程度上,可以把它看成一个类似于BJT 或FET 的电子器件。

它是许多模拟系统和混合信号系统中的重要组成部分。

它的主要参数包括:开环增益、单位增益带宽、相位阈度、输入阻抗、输入偏流、失调电压、漂移、噪声、输入共模与差模范围、输出驱动能力、建立时间与压摆率、CMRR、PSRR以及功耗等。

二、设计任务:设计一个二级运算放大器,使其满足下列设计指标:工艺Smic40nm电源电压 1.1v负载100fF电容增益20dB 至少40dB3dB带宽20MHz输入小信号幅度5uV 共模电平自己选取输出共模电平自己选取电路结构两级放大器相位裕度60~70度功耗无要求三、电路分析:1.电路结构:最基本的二级运算放大器如下图所示,主要包括四部分:第一级放大电路、第二级放大电路、偏置电路和相位补偿电路。

2.电路描述:输入级放大电路由PM2、PM0、PM1和NM0、NM1组成。

PM0和PM1构成差分输入对,使用差分对可以有效地抑制共模信号干扰;NM0和NM1构成电流镜作为有源负载;PM2作为恒流源为放大器第一级提供恒定的偏置电流。

第二级放大电路由NM2和PM3构成。

NM2为共源放大器;PM3为恒流源作负载。

相位补偿电路由电阻R0和电容C0构成,跨接在第二级输入输出之间,构成RC米勒补偿。

此外从电流电压转换角度来看,PM0和PM1为第一级差分跨导级,将差分输入电压转换为差分电流。

NM0和NM1为第一级负载,将差模电流恢复为差模电压。

NM2为第二级跨导级,将差分电压信号转换为电流,而PM3再次将电流信号转换成电压信号输出。

偏置电压由V0和V2给出。

3.静态特性对第一级放大电路:构成差分对的PM0和PM1完全对称,故有G m1=g mp0=g mp1 (1)第一级输出电阻R out1=r op1||r on1 (2)则第一级电压增益A1=G m1Rout1=g mp0,1(r op1||r on1) (3) 对第二级放大电路:电压增益A2=G m2R out2= -g mn2(r on2||r op3) (4) 故总的直流开环电压增益A0=A1A2= -g mp0,1g mn2(r op1||r on1)(r on2||r op3) (5)由于所有的管子都工作在饱和区,所以对于gm 我们可以用公式 g m =D I L W )/(Cox 2μ (6) 进行计算;而电阻r o 可由下式计算 r o =DI 1λ (7)其中λ为沟道长度调制系数且λ∝1/L 。

电子科技大学微固学院集成电路原理实验报告

(2)数字双踪示波器* 一台

(3)信号发生器 一台

(4)实验测试板及连接线 一套

(5)常见通用运算放大器IC样品 一块

八、实验步骤:

1、首先熟悉数字双踪示波器和信号源的使用,根据指导书要求搭建各参数的测试电路。注意所选电阻、电容的值,不能确定时要用万用表测量;在测试板上连接测试电路时应注意各运放集成块各管脚的功能,以免连接错误。

1K

得

十、实验结论:

结合课程所学的知识,对A741双极运算放大器的主要参数进行了测试,熟悉了数字双踪示波器等常用仪器的使用技巧,掌握了通用运算放大器的测试方法,同时对课程中相关的理论知识有了更深入的认识。

十一、总结及心得体会:

通过本次实验,熟悉了数字双踪示波器等常用仪器的使用技巧,掌握了通用运算放大器的测试方法,加深了对所学理论知识的感性认识,增强了自身的实验与综合分析能力,进而为今后从事科研、开发工作打下良好基础。

输入失调电压的测量原理如图3所示。图中直流电路通过 RI 和 RF 接成闭合环路。通常RI的取值不超过 100, RF 》 RI。

(3)共模抑制比kCMR

运放应对共模信号有很强的抑制能力。表征这种能力的参数叫共模抑制比,用kCMR表示。它定义为差模电压增益 AVD 和共模电压增益AVC之比,即

图4 共模抑制比测试原理图

十二、对本实验过程及方法、手段的改进建议:

无。

一、实验室名称:微电子技术实验室

二、实验项目名称:CMOS模拟集成电路设计与仿真

三、实验学时:4

四、实验原理

参照实验指导书。

五、实验目的

本实验是基于微电子技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,为IC设计性实验。其目的在于:

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验报告课程名称:集成电路原理实验名称:CMOS模拟集成电路设计与仿真一、实验名称:CMOS模拟集成电路设计与仿真二、实验学时:4三、实验原理1、转换速率(SR):也称压摆率,单位是V/μs。

运放接成闭环条件下,将一个阶跃信号输入到运放的输入端,从运放的输出端测得运放的输出上升速率。

2、开环增益:当放大器中没有加入负反馈电路时的放大增益称为开环增益。

3、增益带宽积:放大器带宽和带宽增益的乘积,即运放增益下降为1时所对应的频率。

4、相位裕度:使得增益降为1时对应的频率点的相位与-180相位的差值。

5、输入共模范围:在差分放大电路中,二个输入端所加的是大小相等,极性相同的输入信号叫共模信号,此信号的范围叫共模输入信号范围。

6、输出电压摆幅:一般指输出电压最大值和最小值的差。

图1两级共源CMOS运放电路图实验所用原理图如图1所示。

图中有多个电流镜结构,M1、M2构成源耦合对,做差分输入;M3、M4构成电流镜做M1、M2的有源负载;M5、M8构成电流镜提供恒流源;M8、M9为偏置电路提供偏置。

M6、M7为二级放大电路,Cc为引入的米勒补偿电容。

其中主要技术指标与电路的电气参数及几何尺寸的关系:转换速率:SR=I5I I第一级增益:I I1=−I I2I II2+I II4=−2I I1I5(I2+I3)第二级增益:I I2=−I I6I II6+I II7=−2I I6I6(I6+I7)单位增益带宽:GB=I I2I I输出级极点:I2=−I I6I I零点:I1=I I6I I正CMR:I II,III=I II−√I5I3−|I Iℎ3|(III)+I Iℎ1,III负CMR:I II,III=√I5I1+III5,饱和+I Iℎ1,III+I II饱和电压:I II,饱和=√2I III功耗:I IIII=(I8+I5+I7)(I II+I II)四、实验目的本实验是基于微电子技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,为IC设计性实验。

其目的在于:•根据实验任务要求,综合运用课程所学知识自主完成相应的模拟集成电路设计,掌握基本的IC设计技巧。

•学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行电路的模拟仿真。

五、实验内容1、根据设计指标要求,针对CMOS两级共源运放结构,分析计算各器件尺寸。

2、电路的仿真与分析,重点进行直流工作点、交流AC和瞬态Trans分析,能熟练掌握各种分析的参数设置方法与仿真结果的查看方法。

3、电路性能的优化与器件参数调试,要求达到预定的技术指标。

4、整理仿真数据与曲线图表,撰写并提交实验报告。

5、运放指标要求:•驱动负载电容C L为1.5pF;•开环增益Av≥65dB;•增益带宽积GB≥60MHz;•转换速率SR≥20V/μs;•输入共模范围0.6V到2.8V;•输出电压摆幅大于2.3V;•相位裕度45°≤PM≤75°。

六、实验仪器设备(1)工作站或微机终端一台(2)EDA仿真软件1套七、实验步骤1、参数计算:由umc18工艺得对应的一些基本参数:V thn=0.59,V thp=0.72,u n=341,u p=81,t ox=7e-9,L min=3.4e-7,通过计算得出参数:K n=1.68e-4,K p=4e-5(1)计算最小补偿电容Cc根据指标要求,在此预设相位裕度为60°,则由零点Z1和第二极点P2对补偿电容的要求,得:(P2>2.2GB)I I>2.210⋅I I=2.210×1.5=0.33II保守做法,取Cc为0.5pF。

(2)由SR 、Cc 求出偏置电流I 5:I 5=I I ⋅II =0.5×10−12×20×106=10II此为最小I 5,取I 5=20uA 。

(3)用CMR 计算(W/L)3:(I I )3=2I 3I 3[III −I II ,III −|I I ℎ3|III +I I ℎ1,III ]2=20×10−64×10−5×(3.3−2.8−0.72+0.59)2=3.65 (4)由GB 、C C 求出g m1、g m2I I1=II ⋅I I =2I ×60×106×0.5×10−12=188.5II(I I )1=(I I )2=I I12I 1⋅I 5=(188.5)2168×20=10.57 (5)计算(W/L)6I I6=2.2⋅I I2⋅I I I I =2.2∙(188.5×10−6)⋅1.50.5=1244.1III I4=√2I II ⋅I ⋅II I II =54II(I I )6=(I I )4I I6I I4=3.65×1244.154=84.1 I 6=I I622⋅I 6⋅(I I )6=(1244.1×10−6)22×4×10−5×84.1=230II(6)计算(W/L)7(I I )7=(I I )5⋅I 6I 5=(I I )5⋅23020=11.5(I I )5(7)剩余参数的确定M9和M8构成偏置电路给M5提供栅压,M8和M5又构成电流镜,由于M5工作在饱和区间,所以由经验取(W/L)9=1.2,(W/L)8=10。

(8)利用计算所得参数对电路进行仿真,根据仿真结果再进行细调参数。

根据实验原理和设计指标要求,最终各个元器件的参数如表1所示;Candence 下电路图如图2所示。

表1 运放各器件版图参数器件W(μm)L(μm)M1 40 2M2 40 2M3 3.9 1M4 3.9 1M5 6 0.5 M6 60 0.5 M7 44 0.35 M8 5 0.5 M9 1.2 1C L 1.5pFCc 0.6pF图2两级运放电路图2 共模输入范围ICMR仿真对输入信号在0~V DD范围内进行DC分析,测试输出电压能够跟随输入电压的的范围,即为运放的共模输入范围。

测得的V out随输入的变化波形如图3,从图中可知ICMR在0.18V到2.9V之间的情况下,运放都能工作。

满足设计指标要求。

图3共模输入范围曲线3 输出摆幅仿真输出摆幅的测试方法在0~V DD范围内,对电路进行DC分析。

观察V o点波形,测试输出电压的线性跟踪范围,即为输出动态范围。

测得的V out随输入的变化波形如图4所示,可以从图中看到输出摆幅约在0 V到3V之间。

大于2.3V,满足设计要求。

图4输出摆幅曲线4 Av和GB及相位裕度仿真进行AC分析,取两个输入正弦信号V+和V-的直流偏置为1.5V,AC magnitude 为1V,Amplitude为0.1mV,Frequency为100Hz,相位差180°。

测得的输出V out的AC 20dB波形如图5所示,可知低频(小于200Hz)增益Av=77.3dB>65dB,GB=65.41MHz>60MHz满足要求。

可以看出在65.41MHz处(0dB带宽处)的相位裕度为50.63°,满足设计要求45°≤PM≤75°。

图5幅频相频特性曲线5 转换速率SR的测试建立时间是表示大信号工作时运放性能的一个重要参数,输入阶跃大信号,输出电压从开始响应到稳定值为止的时间。

稳定值的误差范围一般为0.1%Vout,建立时间既反映了运放的转换速率,又表征了其阻尼特性。

仿真建立时间需要进行TRAN分析,测得的波形如图6所示,可以看到在70ns内完成了3.14V的建立,所以SR=3.14/0.070 = 44.9V/μs > 20V/μs,满足设计要求。

图6转换速率曲线八、实验数据及结果分析1、通过本次实验掌握了UNIX操作系统常用命令的使用,Cadence EDA仿真环境的调用。

达到了实验目的。

2、根据设计指标要求,设计两级共源CMOS运算放大器,并进行了参数优化,最终增益、带宽、相位裕度满足要求(见图5),3、实验过程中,通过理论值到实际值的过程,清楚了运放中各个管对整个运放功能的影响。

随着运算放大器的功能在个人通信和数据处理尤其是笔记本电脑、移动通信等便携式设备中扮演着越来越重要的角色,所以本次对于运放设计的实验有着重要的学习应用价值。

九、实验心得与体会通过这次实验,首先促使了自己更加深入地学习Cadence的相关使用方法,学会了如何使用Cadence较为娴熟地构造电路,然后结合自己所学知识,计算出电路中各个元器件的相关理论参数;然后在Cadence中对电路进行仿真,通过合理调整各个元器件的相关参数,使得仿真结果满足要求。

虽然这个过程较为漫长和枯燥,但是让自己明白了电路中一个小小参数的变化也能对整个电路产生较大的影响,也让自己明白了理论与实践结合的重要性和必要性。

在修改器件相关参数,进行各种仿真,得到需要的仿真结果,这时方知要成为一名科研工作者所需付出的辛勤努力。

在整个实验中的收获,为我们在未来的科研学习、工作打下了良好的实践基础。

十、实验分工由搭建初始电路,听讲老师相关讲解;由二人各自计算电路的相关参数,然后对比、总结,确定初始的电路参数;由调整电路参数以得到指定的电路功能;由最终微调电路参数,得到指定的仿真结果;由二者共同完成该实验报告。

报告评分:指导教师签字:。