任务一:测试3线—8线译码器74LS138逻辑功能。

74LS138译码器

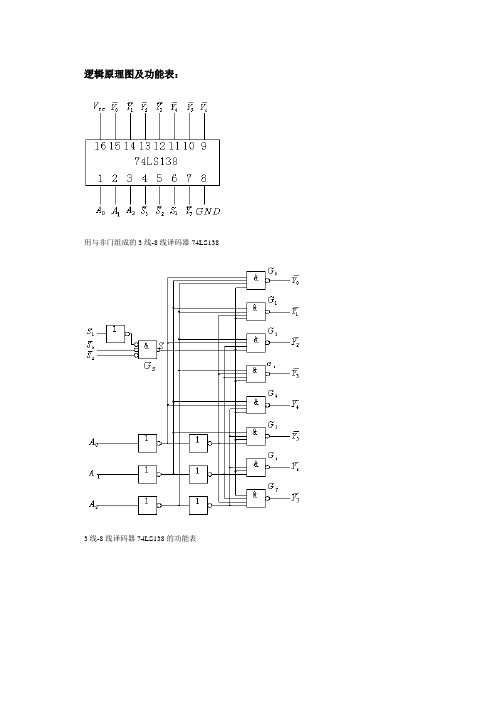

逻辑原理图及功能表:用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

解:由图3.3.8可见,74LS138仅有3个地址输入端。

如果想对4位二进制代码,只能利用一个附加控制端(当中的一个)作为第四个地址输入端。

取第(1)片74LS138的和作为它的第四个地址输入端(同时令),取第(2)片的作为它的第四个地址输入端(同时令),取两片的、、,并将第(1)片的和接至,将第(2)片的接至,如图3.3.9所示,于是得到两片74LS138的输出分别为图3.3.9 用两片74LS138接成的4线-16线译码器式(3.3.8)表明时第(1)片74LS138工作而第(2)片74LS138禁止,将的0000~0111这8个代码译成8个低电平信号。

实验三译码器数据选择器及其应用

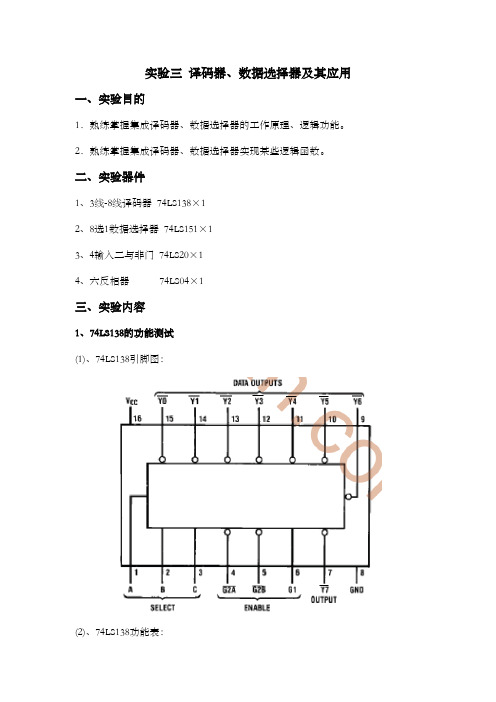

实验三译码器、数据选择器及其应用一、实验目的1.熟练掌握集成译码器、数据选择器的工作原理、逻辑功能。

2.熟练掌握集成译码器、数据选择器实现某些逻辑函数。

二、实验器件1、3线-8线译码器74LS138×12、8选1数据选择器74LS151×13、4输入二与非门74LS20×14、六反相器74LS04×1三、实验内容1、74LS138的功能测试(1)、74LS138引脚图:(2)、74LS138功能表:注:2G =G 2A +G 2B 2、74LS138用作逻辑函数发生器(1)、用74LS138和门电路实现逻辑函数 F=AB+AC+BC 实验步骤:将逻辑函数转化为最小项逻辑表达式 画卡诺图:由卡诺图得到:F=A BC+A B C+AB C +ABC=Σm (3,5,6,7) =7.6.5.3m m m m =7.6.5.3Y Y Y Y用一片74LS138和一片74LS20搭建电路:BC A 00 01 11 10 01 1111(2)、用74LS138和门电路实现逻辑函数F=A BC+A B C+AB C(判偶电路)(3)、用74LS138和门电路设计一个全加器3、74LS151功能测试(1)、74LS151引脚图:(2)、74LS151功能表:4、74LS151和门电路实现逻辑函数(1)、用74LS151和门电路实现逻辑函数 F=AB+AC+BC 实验步骤:将逻辑函数转化为最小项逻辑表达式 画卡诺图:由卡诺图得到:F=A BC+A B C+AB C +ABC=Σm (3,5,6,7)=m 0.0+m 1.0+m 2.0+m 3.1+m 4.0+m 5.1+m 6.1+m 7.1 74LS151输出Y=m 0.D 0+m 1.D 1+m 2.D 2+m 3.D 3+m 4.D 4+m 5.D 5+m 6.D 6+m 7.D 7 若令F=Y ,A=C ,B=B ,C=A 则D 0= D 1= D 2= D 4=0 D 3= D 5= D 6= D 7=1 根据以上分析,画出电路图:BC A 00 01 11 10 01 1111(2)、用数据选择器74LS151实现函数F=Σm (0,2,7,8,13)。

实验三 3-8译码器的功能测试及仿真

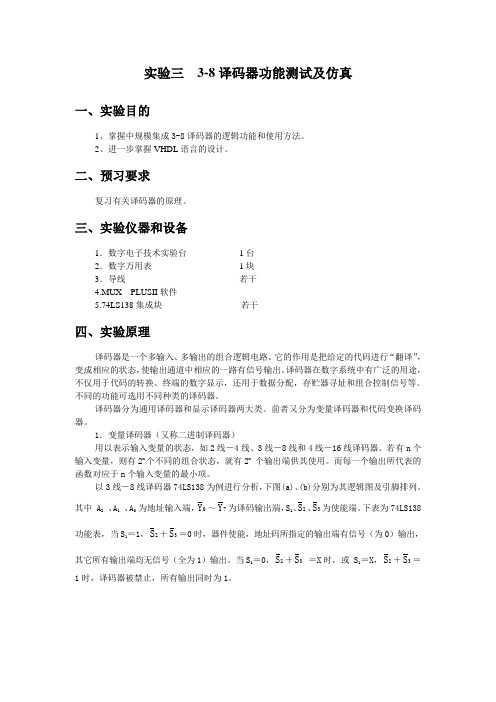

实验三3-8译码器功能测试及仿真一、实验目的1、掌握中规模集成3-8译码器的逻辑功能和使用方法。

2、进一步掌握VHDL语言的设计。

二、预习要求复习有关译码器的原理。

三、实验仪器和设备1.数字电子技术实验台1台2.数字万用表1块3.导线若干4.MUX PLUSII软件5.74LS138集成块若干四、实验原理译码器是一个多输入、多输出的组合逻辑电路。

它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。

译码器在数字系统中有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配,存贮器寻址和组合控制信号等。

不同的功能可选用不同种类的译码器。

译码器分为通用译码器和显示译码器两大类。

前者又分为变量译码器和代码变换译码器。

1.变量译码器(又称二进制译码器)用以表示输入变量的状态,如2线-4线、3线-8线和4线-16线译码器。

若有n个输入变量,则有2n个不同的组合状态,就有2n个输出端供其使用。

而每一个输出所代表的函数对应于n个输入变量的最小项。

以3线-8线译码器74LS138为例进行分析,下图(a)、(b)分别为其逻辑图及引脚排列。

其中 A2、A1、A0为地址输入端,0Y~7Y为译码输出端,S1、2S、3S为使能端。

下表为74LS138功能表,当S1=1,2S+3S=0时,器件使能,地址码所指定的输出端有信号(为0)输出,其它所有输出端均无信号(全为1)输出。

当S1=0,2S+3S=X时,或 S1=X,2S+3S=1时,译码器被禁止,所有输出同时为1。

3-8线译码器74LS138逻辑图及引脚排列图74LS138功能表输入输出S12S+3S A2A1A00Y1Y2Y3Y4Y5Y6Y7Y1 0 0 0 0 0 1 1 1 1 1 1 11 0 0 0 1 1 0 1 1 1 1 1 11 0 0 1 0 1 1 0 1 1 1 1 11 0 0 1 1 1 1 1 0 1 1 1 11 0 1 0 0 1 1 1 1 0 1 1 11 0 1 0 1 1 1 1 1 1 0 1 11 0 1 1 0 1 1 1 1 1 1 0 11 0 1 1 1 1 1 1 1 1 1 1 00 ×××× 1 1 1 1 1 1 1 1× 1 ××× 1 1 1 1 1 1 1 1二进制译码器实际上也是负脉冲输出的脉冲分配器。

数字电路实验

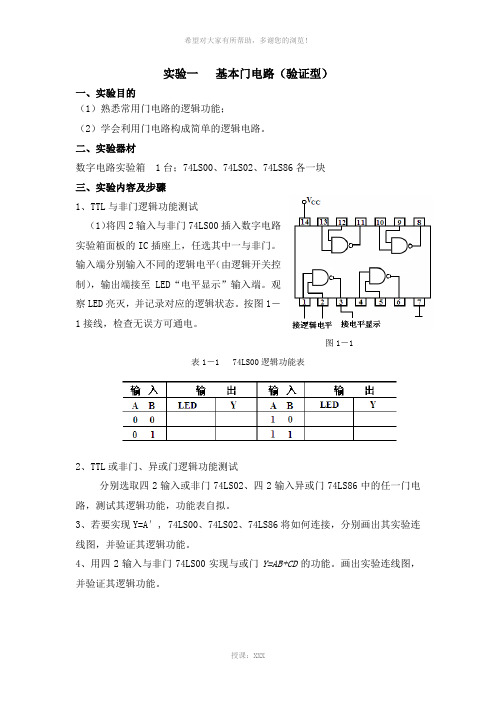

实验一基本门电路(验证型)一、实验目的(1)熟悉常用门电路的逻辑功能;(2)学会利用门电路构成简单的逻辑电路。

二、实验器材数字电路实验箱 1台;74LS00、74LS02、74LS86各一块三、实验内容及步骤1、TTL与非门逻辑功能测试(1)将四2输入与非门74LS00插入数字电路实验箱面板的IC插座上,任选其中一与非门。

输入端分别输入不同的逻辑电平(由逻辑开关控制),输出端接至LED“电平显示”输入端。

观察LED亮灭,并记录对应的逻辑状态。

按图1-1接线,检查无误方可通电。

图1-1表1-1 74LS00逻辑功能表2、TTL或非门、异或门逻辑功能测试分别选取四2输入或非门74LS02、四2输入异或门74LS86中的任一门电路,测试其逻辑功能,功能表自拟。

3、若要实现Y=A′, 74LS00、74LS02、74LS86将如何连接,分别画出其实验连线图,并验证其逻辑功能。

4、用四2输入与非门74LS00实现与或门Y=AB+CD的功能。

画出实验连线图,并验证其逻辑功能。

四、思考题1.TTL与非门输入端悬空相当于输入什么电平?2.如何处理各种门电路的多余输入端?附:集成电路引出端功能图实验二组合逻辑电路(设计型)一、实验目的熟悉简单组合电路的设计和分析过程。

二、实验器材数字电路实验箱 1台,74LS00 三块,74LS02、74LS04、74LS08各一块三、实验内容及步骤1、设计一个能比较一位二进制A与 B大小的比较电路,用X1、X2、X3分别表示三种状态:A>B时,X1=1;A<B时X2=1;A=B时X3=1。

(用74LS04、74LS08和74LS02实现)要求:(1)列出真值表;(2)写出函数逻辑表达式;(3) 画出逻辑电路图,并画出实验连线图;(4)验证电路设计的正确性。

2、测量组合电路的逻辑关系:(1)图3-2电路用3块74LS00组成。

按逻辑图接好实验电路,输入端A、B、C 分别接“逻辑电平”,输出端D、J接LED“电平显示”;图3-2 表3-2(2)按表3-2要求,将测得的输出状态和LED显示分别填入表内;(3)根据测得的逻辑电路真值表,写出电路的逻辑函数式,判断该电路的功能。

数电检测题1-3及答案

数电检测题1及答案一、填空题(20分)1.数字信号只有 和 两种取值。

2.十进制123的二进制数是 ;八进制数是 ;十六进制数是 。

3.设同或门的输入信号为A 和B ,输出函数为F 。

若令B=0,则F= 若令B=1,则F=4.三态门的输出有 、 、 三种状态。

5.设JK 触发器的起始状态Q=1 若令J=1,K=0,则=+1n Q 。

若令J=1,K=1,则=-1n Q 。

6.BCD 七段翻译码器输入的是 位 码,输出有 个。

7.一个N 进制计数器也可以称为 分频器。

8.有一个6位D/A 转换器,设满度输出为6.3V ,输入数字量为110111,则输出模拟电压为 。

9.设ROM 容量为256字×8位,则它应设置地址线 条,输出线 条。

10.用256字×4位RAM ,扩展容量为1024字×8位RAM ,则需要 片。

二 、选择题(20分)1. 离散的,不连续的信号,称为( ) A 、模拟信号 B 、数字信号2. 组合逻辑电路通常由( )组合而成。

A 、门电路 B 、触发器 C 、计数器3. 十六路数据选择器的地址输入(选择控制)端有( )个 A 、16 B 、2 C 、4 D 、84. 一位8421BCD 码译码器的数据输入线与译码输出线的组合是( ) A 、4:6 B 、1:10 C 、4:10 D 、2:4 5. 能实现脉冲延时的电路是( )A 、多谐振荡器B 、单稳态触发器C 、施密特触发器6.8线—3线优先编码器的输入为70I I - ,当优先级别最高的7I 有效时,其输出012Y Y Y 的值是( )A 、111B 、010C 、000D 、1017.JK 触发器在CP 作用下,若状态必须发生翻转,则应使( ) A 、J=K=0 B 、J=K=1 C 、J=O ,K=18.有一个左移位寄存器,当预先置入1011后,其串行固定接0,在4个移位脉冲CP 作用下,四位数据的移位过程是( )A 、1011—0110—1100—1000—0000B 、1011—0101—0010—0001—0000 9.有一位二进制数码需要暂时存放起来,应选用( )A、触发器B、2选1数据选择器C、全加器10.EPROM是指()A、随机读写存储器B、可编程逻辑阵列可编程只读存储器 D、可擦除可编程只读存储器三、判断题(10分)1、n个变量的逻辑函数,其全部最小项共有n个。

数字电子技术基础—精彩试题—解答-电子技术化简与或式

三、逻辑函数化简(每题5分,共10分)1、用代数法化简为最简与或式Y= A +1、Y=A+B2、用卡诺图法化简为最简或与式 Y= + C +A D,约束条件:A C + A CD+AB=02、用卡诺图圈0的方法可得:Y=( +D)(A+ )( + )四、分析下列电路。

(每题6分,共12分)1、写出如图4所示电路的真值表及最简逻辑表达式。

图 41、该电路为三变量判一致电路,当三个变量都相同时输出为1,否则输出为0。

2、写出如图5所示电路的最简逻辑表达式。

2、B =1,Y = A ,B =0 Y 呈高阻态。

五、判断如图 6所示电路的逻辑功能。

若已知 u B =-20V,设二极管为理想二极管,试根据 u A 输入波形,画出 u 0 的输出波形(8分)t图 6五、 u 0 = u A · u B ,输出波形 u 0 如图 10所示:图 10六、用如图 7所示的8选1数据选择器CT74LS151实现下列函数。

(8分)Y(A,B,C,D)=Σm(1,5,6,7,9,11,12,13,14)图 7 答:七、用 4位二进制计数集成芯片CT74LS161采用两种方法实现模值为10的计数器,要求画出接线图和全状态转换图。

(CT74LS161如图8所示,其LD端为同步置数端,CR为异步复位端)。

(10分)图 8七、接线如图 12所示:图 12全状态转换图如图 13 所示:( a )( b )图 13八、电路如图 9所示,试写出电路的激励方程,状态转移方程,求出Z 1 、Z 2 、Z 3 的输出逻辑表达式,并画出在CP脉冲作用下,Q 0 、Q 1 、Z 1 、Z 2 、Z 3 的输出波形。

(设 Q 0 、Q 1 的初态为0。

)(12分)八、,,波形如图 14所示:三、将下列函数化简为最简与或表达式(本题 10分)1. (代数法)2、F 2 ( A,B,C,D)=∑m (0,1,2,4,5,9)+∑d (7,8,10,11,12,13)(卡诺图法)三、1. 2.四、分析如图 16所示电路,写出其真值表和最简表达式。

数电期中考试试题和答案

数电期中测试题 参考答案系别 班级 学号一、单项选择题(本大题共7小题,每小题2分,共14分)在每小题列出的四个备选项中只有一个是符合题目要求的,请将其代码填写在题后的括号。

错选、多选或未选均无分。

1.十进制数25用8421BCD 码表示为(B )A.10101B.0010 0101C.100101D.110012.函数B A ABC ABC F //++=的最简与或式是(D )A.F=A+BB.//C A F +=C.F=B+CD.F=B3.若将一个同或门(输入端为A,B )当作反相器使用,则A 、B 端应(C )A.A 或B 中有一个接1;B.A 和B 并联使用;C. A 或B 中有一个接0;D.同或门无法转换为反相器4.符合下面真值表的门电路是(C )A.与门B.或门C.同或门D.异或门 5.下列代码属于8421BCD 码的是(C )A.1010B.1100C.0111D.1101 6.最小项''A BC D 的逻辑相邻最小项是(B )A .''AB CD B .'''A BCD C .'ABCD D .'AB CD 7.函数F=AB+BC ,使F=1的输入ABC 组合为(D)A .ABC=000B .ABC=010C .ABC=101D .ABC=110二、填空题(本大题共10小题,每小题2分,共20分) 请在每小题的空格中填上正确答案。

错填、不填均无分。

1.基本逻辑运算有_______、 、 3种。

与、或、非 2.描述逻辑函数各个变量取值组合和函数值对应关系的表格叫_真值表。

3.函数Y=AB+AC的最小项之和表达式为________。

(ABC ABC C AB Y ++=//)4.3线-8线译码器74LS138处于译码状态时,当输入A 2A 1A 0=001时,输出/0/7~Y Y =______。

111111015.能够将1个输入数据,根据需要传送到m 个输出端的任何一个输出端的电路叫_______。

实验一基本门电路的逻辑功能测试

实验一基本门电路的逻辑功能测试一、实验目的1、测试与门、或门、非门、与非门、或非门与异或门的逻辑功能。

2、了解测试的方法与测试的原理。

二、实验原理实验中用到的基本门电路的符号为:在要测试芯片的输入端用逻辑电平输出单元输入高低电平,然后使用逻辑电平显示单元显示其逻辑功能。

三、实验设备与器件1、数字逻辑电路实验箱。

2、数字逻辑电路实验箱扩展板。

3、相应74LS系列芯片若干。

四、实验内容测试TTL门电路的逻辑功能:a)测试74LS08(与门)的逻辑功能。

b)测试74LS32(或门)的逻辑功能。

c)测试74LS04(非门)的逻辑功能。

d)测试74LS00(与非门)的逻辑功能。

e)测试74LS02(或非门)的逻辑功能。

f)测试74LS86(异或门)的逻辑功能。

五、实验步骤1、按照芯片的管脚分布图接线(注意高低电平的输入和高低电平的显示)。

2、测试各个芯片的逻辑功能六、实验报告要求1.画好各门电路的真值表表格,将实验结果填写到表中。

2.根据实验结果,写出各逻辑门的逻辑表达式,并判断逻辑门的好坏。

实验二编码器及其应用一、实验目的1.掌握一种门电路组成编码器的方法。

2.掌握8 -3线优先编码器74LS148,10 -4线优先编码器74LS147的功能。

二、实验原理1、8-3线优先编码器74LS148编码器74LS148的作用是将输入I0~I78个状态分别编成二进制码输出,它的功能表见表6-2,它的逻辑图见图6-2。

它有8个输入端,3个二进制码输出端,输入使能端EI,输出使能端7至I0递减。

输入输出EI 0 1 2 3 4 5 6 7 A2A1A0GS EOH ××××××××H H H H HL H H H H H H H H H H H H LL ×××××××L L L L L HL ××××××L H L L H L HL ×××××L H H L H L L HL ××××L H H H L H H L HL ×××L H H H H H L L L HL ××L H H H H H H L H L HL ×L H H H H H H H H L L HL L H H H H H H H H H H L H3、10-4线优先编码器74LS14774LS147的输出为8421BCD码,它的逻辑图见图6-3,其功能表为:输入输出5 6 7 8 9 D C B A GS1 2 34H H H H H H H H H H H H H 0××××××××L L H H L 1×××××××L H L H H H 1××××××L H H H L L L 1×××××L H H H H L L H 1××××L H H H H H L H L 1×××L H H H H H H L H H 1××L H H H H H H H H L L 1×L H H H H H H H H H L H 1L H H H H H H H H H H H L 174LS147逻辑图三、实验设备与器材1、数字逻辑电路实验箱。

电子技术基础(数字部分)译码器74LS138功能验证实验

试验二译码器74LS138功效验证试验

试验目标:

验证译码器74LS138功效;掌握74LS138作为数据分配器时应用。

试验器材:

数字逻辑试验箱一个;数字万用表一个;5V电源一个;导线若干;

(1)验证74LS138功效:

74LS138为3-8译码器,试验原理图以下图所表示:

LED

试验过程:分别在74LS138A2、A1、A0、E3、/E2和/E1加上高、低不一样电平,用万用表测量出输出Y7-Y0电平,统计下来,验证逻辑关系是否正确

测量结果:

试验结论:当E3输入非高电平时,不管其它输入怎样,电路输出全部为高电平,即译码器不处于工作状态;只有当E3输入为高电平,/E2和/E1同时为低电平时,译码器才处于工作状态,输出低电平有效。

(2)验证74LS138作为数据分配器时功效(设信号从/E1输入,从/Y5输出)。

电路原理以下:

试验过程以下:先将K1闭合,测量/E1引脚电平关态和/Y5引脚电平状态;再将先将K1断开,测量/E1引脚电平关态和/Y5引脚电平状态,没量结果以下:

结论: /E1引脚电平关态和/Y5引脚电平状态永远相同,说明接在/E1信号被分配到/Y5输出。

LED。

级《数字逻辑电路》实验指导书

课程名称:数字逻辑电路实验指导书课时:8学时集成电路芯片一、简介数字电路实验中所用到的集成芯片都是双列直插式的,其引脚排列规则如图1-1所示。

识别方法是:正对集成电路型号<如74LS20)或看标记<左边的缺口或小圆点标记),从左下角开始按逆时针方向以1,2,3,…依次排列到最后一脚<在左上角)。

在标准形TTL集成电路中,电源端V一般排在左上CC,7脚为端,接地端GND一般排在右下端。

如74LS20为14脚芯片,14脚为VCCGND。

若集成芯片引脚上的功能标号为NC,则表示该引脚为空脚,与内部电路不连接。

二、TTL集成电路使用规则1、接插集成块时,要认清定位标记,不得插反。

2、电源电压使用范围为+4.5V~+5.5V之间,实验中要求使用Vcc=+5V。

电源极性绝对不允许接错。

3、闲置输入端处理方法(1> 悬空,相当于正逻辑“1”,对于一般小规模集成电路的数据输入端,实验时允许悬空处理。

但易受外界干扰,导致电路的逻辑功能不正常。

因此,对于接有长线的输入端,中规模以上的集成电路和使用集成电路较多的复杂电路,所有控制输入端必须按逻辑要求接入电路,不允许悬空。

<也可以串入一只1~10KΩ的固定电阻)或接至某一 (2> 直接接电源电压VCC固定电压(+2.4≤V≤4.5V>的电源上,或与输入端为接地的多余与非门的输出端相接。

(3> 若前级驱动能力允许,可以与使用的输入端并联。

4、输入端通过电阻接地,电阻值的大小将直接影响电路所处的状态。

当R ≤680Ω时,输入端相当于逻辑“0”;当R≥4.7 KΩ时,输入端相当于逻辑“1”。

对于不同系列的器件,要求的阻值不同。

5、输出端不允许并联使用<集电极开路门(OC>和三态输出门电路(3S>除外)。

否则不仅会使电路逻辑功能混乱,并会导致器件损坏。

6、输出端不允许直接接地或直接接+5V电源,否则将损坏器件,有时为,一般取R 了使后级电路获得较高的输出电平,允许输出端通过电阻R接至Vcc=3~5.1 KΩ。

实验二编码器和译码器的应用

实验二编码器和译码器的应用一.实验目的:1.学会正确使用中规模集成组合逻辑电路。

掌握编码器、译码器、BCD七段译码器、数码显示器的工作原理和使用方法。

2.掌握译码器及其应用, 学会测试其逻辑功能。

二.实验仪器及器件:1. TPE—D6Ⅲ型数字电路实验箱 1台2.数字万用表 1块3.器件:74LS20 二4输入与非门 1片74LS04 六反相器 1片74LS147 10线—4线优先编码器 1片74LS138 3线—8线译码器 1片74LS139 双2线—4线译码器 1片74LS47 七段显示译码器 1片三.实验预习:1.复习编码器、译码器、BCD七段译码器、数码显示器的工作原理。

2.熟悉编码器74LS147及译码器74LS138、74LS139各引脚功能和使用方法,列出74LS138、74LS139的真值表,画出所要求的具体实验线路图。

四.实验原理:在数字系统中,常常需要将某一信息变换为特定的代码,有时又需要在一定的条件下将代码翻译出来作为控制信号,这分别由编码器和译码器来实现。

1.编码:用一定位数的二进制数来表示十进制数码、字母、符号等信息的过程。

编码器:实现编码功能的电路。

编码器功能:从m个输入中选中一个,编成一组n位二进制代码并行输出。

编码器特点:(1)多输入、多输出组合逻辑电路。

(2)在任何时候m个输入中只有一个输入端有效(高电平或低电平)对应有一组二进制代码输出。

编码器分类:二进制、二─十进制、优先编码器。

2.译码:是编码的反过程,是将给定的二进制代码翻译成编码时赋予的原意。

译码器:实现译码功能的电路。

译码器特点:(1)多输入、多输出组合逻辑电路。

(2)输入是以n位二进制代码形式出现,输出是与之对应的电位信息。

译码器分类:通用译码器:二进制、二─十进制译码器。

显示译码器:TTL共阴显示译码器(用高电平点燃共阴显示器)、TTL共阳显示译码器(用低电平点燃共阳显示器)、CMOS显示译码器。

译码器应用:用于代码的转换、终端的数字显示、数据分配、存贮器寻址组合信号控制等。

2020年智慧树知道网课《数字电子技术(山东联盟--泰山学院)》课后章节测试满分答案

第一章测试1【单选题】(10分)十六进制数(7C)16转换为等值的十进制、二进制和八进制数分别为()。

A.(123)10(1111100)2(173)8B.(124)10(1111100)2(173)8C.(123)10(1111101)2(174)8D.(124)10(1111100)2(174)82【单选题】(10分)最小项A′BC′D的逻辑相邻最小项是()。

A.A′BCD′B.AB′CDC.ABCD′D.A′BCD3【单选题】(10分)已知下面的真值表,写出逻辑函数式为()。

A.Y=A′B+ABB.Y=A′B+AB′C.Y=AB+A′BD.Y=A′B′+AB4【判断题】(10分)因为逻辑表达式A+B+AB=A+B成立,所以AB=0成立。

()A.对B.错5【单选题】(10分)4个不同进制的数376.125D、567.1O、110000000B、17A.2H,按大小排列的次序为A.17A.2H>110000000B>576.1O>376.125DB.376.125D>567.1O>110000000B>17A.2HC.567.1O>110000000B>17A.2H>376.125DD.110000000B>17A.2H>376.125D>576.1O6【单选题】(10分)示波器测得的波形如图所示,以下哪个真值表符合该波形A.B.C.D.7【单选题】(10分)示波器测得的波形如图所示,以下哪个函数式符合该波形A.F=(A+B)’B.F=(AB)’C.F=ABD.F=A+B8【单选题】(10分)用卡诺图将下式化简为最简与或函数式,正确的是Y(A,B,C,D)=∑m(2,3,7,8,11,14)+∑d(0,5,10,15)A.Y=CD+B'D'+ACB.Y=CD+B'C'D'+ACD'+A'B'CC.Y=CD+ACD'+A'B'C+AB'CD.Y=CD+CD'+A'B'C9【多选题】(10分)已知逻辑函数F=AC+BC'+A'B,以下叙述正确的有A.逻辑函数的最简与或式为F=AC+BB.逻辑函数的与非式为F=((AC)'(BC')'(A'B)')'C.逻辑函数的反函数表达式为F'=(A'+C')∙(B'+C)∙(A+B')D.逻辑函数的最简与或式为F=AC+A'B10【多选题】(10分)逻辑函数Y=A'B'C'D+A'BD'+ACD+AB',其最小项之和的形式正确的是A.Y=A'B'C'D+A'BC'D'+A'BCD'+AB'CD+ABCD+AB'C'D+AB'C'D'B.Y=∑(1,4,6,8,9,10,11,15)C.Y=m1+m4+m6+m8+m9+m10+m11+m15D.Y=A'B'C'D+A'BC'D'+A'BCD'+AB'CD+ABCD+AB'CD'+AB'C'D+AB'C'D'第二章测试1【判断题】(10分)组合逻辑电路通常由门电路和寄存器组合而成。

(完整版)数字电子技术试题及答案(题库)

数字电子技术基础试题(一)一、填空题 : (每空1分,共10分)1. (30.25) 10 = ( ) 2 = ( ) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为条、数据线为条。

二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 )1.设图1中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:()图。

图 12.下列几种TTL电路中,输出端可实现线与功能的电路是()。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是()。

A、通过大电阻接地(>1.5KΩ)B、悬空C、通过小电阻接地(<1KΩ)D、通过电阻接V CC4.图2所示电路为由555定时器构成的()。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路()。

图2A、计数器B、寄存器C、译码器D、触发器6.下列几种A/D转换器中,转换速度最快的是()。

图2A、并行A/D转换器B、计数型A/D转换器C、逐次渐进型A/D转换器D、双积分A/D转换器7.某电路的输入波形 u I 和输出波形 u O 如图 3所示,则该电路为()。

图3A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用()。

A、10级施密特触发器B、10位二进制计数器C、十进制计数器D、10位D/A转换器9、已知逻辑函数与其相等的函数为()。

A、B、C、D、10、一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。

A、4B、6C、8D、16三、逻辑函数化简(每题5分,共10分)1、用代数法化简为最简与或式Y= A +2、用卡诺图法化简为最简或与式Y= + C +A D,约束条件:A C + A CD+AB=0四、分析下列电路。

实验三 3-8译码器的功能测试及仿真

实验三3-8译码器功能测试及仿真一、实验目的1、掌握中规模集成3-8译码器的逻辑功能和使用方法。

2、进一步掌握VHDL语言的设计。

二、预习要求复习有关译码器的原理。

三、实验仪器和设备1.数字电子技术实验台1台2.数字万用表1块3.导线若干4.MUX PLUSII软件5.74LS138集成块若干四、实验原理译码器是一个多输入、多输出的组合逻辑电路。

它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。

译码器在数字系统中有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配,存贮器寻址和组合控制信号等。

不同的功能可选用不同种类的译码器。

译码器分为通用译码器和显示译码器两大类。

前者又分为变量译码器和代码变换译码器。

1.变量译码器(又称二进制译码器)用以表示输入变量的状态,如2线-4线、3线-8线和4线-16线译码器。

若有n个输入变量,则有2n个不同的组合状态,就有2n个输出端供其使用。

而每一个输出所代表的函数对应于n个输入变量的最小项。

以3线-8线译码器74LS138为例进行分析,下图(a)、(b)分别为其逻辑图及引脚排列。

其中 A2、A1、A0为地址输入端,0Y~7Y为译码输出端,S1、2S、3S为使能端。

下表为74LS138功能表,当S1=1,2S+3S=0时,器件使能,地址码所指定的输出端有信号(为0)输出,其它所有输出端均无信号(全为1)输出。

当S1=0,2S+3S=X时,或 S1=X,2S+3S=1时,译码器被禁止,所有输出同时为1。

3-8线译码器74LS138逻辑图及引脚排列图74LS138功能表输入输出S12S+3S A2A1A00Y1Y2Y3Y4Y5Y6Y7Y1 0 0 0 0 0 1 1 1 1 1 1 11 0 0 0 1 1 0 1 1 1 1 1 11 0 0 1 0 1 1 0 1 1 1 1 11 0 0 1 1 1 1 1 0 1 1 1 11 0 1 0 0 1 1 1 1 0 1 1 11 0 1 0 1 1 1 1 1 1 0 1 11 0 1 1 0 1 1 1 1 1 1 0 11 0 1 1 1 1 1 1 1 1 1 1 00 ×××× 1 1 1 1 1 1 1 1× 1 ××× 1 1 1 1 1 1 1 1二进制译码器实际上也是负脉冲输出的脉冲分配器。

GDOU广东海洋大学数字电路试题集

海洋大学 —— 学年第 学期《 数字电子技术基础 》课程试题课程号: 16632205√ 考试 √ A 卷 √ 闭卷一、填空题(每空1分,共10分)1.如果采用二进制代码为200份文件顺序编码,最少需用 位。

2.和二进制数(1010.01)2等值的十进制数为 。

3.二进制数(+0000110)2的原码为 、反码为补码为 。

4.逻辑函数式A ⊕0的值为 。

5.逻辑函数式Y = A ′ BC ′ + AC ′ + B ′C 的最小项之和的形式为 。

6. 组合逻辑电路的特点是 。

7.若存储器的容量为512K ×8位,则地址代码应取 位。

8.D/A 转换器的主要技术指标是转换精度和 。

二、单项选择题(每小题2分,共10分) 1.逻辑代数中的三种基本运算指( c )。

(a)加、减运算 (b)乘、除运算 (c)与、或、非运算 (d)优先级运算 2.若两个逻辑式相等,则它们的对偶式( d )。

班级:姓名:学号:试题共页加白纸张密封线GDOU-B-11-302(a)不一定相等 (b)可能为0 (c) 可能为1 (d) 一定相等 3.正逻辑的高电平表示为( b )。

(a) 0 (b)1 (c)原变量 (d)反变量 4.三态门电路的输出可以为高电平、低电平及( c )。

(a)0 (b)1 (c)高阻态 (d)导通状态 5.随着计数脉冲的不断输入而作递增计数的计数器称为( a )。

(a)加法计数器 (b)减法计数器 (c)可逆计数器 (d)加/减计数器 三、分析题(每小题10分,共40分)1.已知逻辑函数Y 1 和Y 2的真值表如表1所示,试写出Y 1 和Y 2的逻辑函数式。

表12.分析图1所示时序电路的逻辑功能,写出电路的驱动方程、状态方程和输出方程,画出电路的状态转换图和时序图。

图13.写出如图2A B C Y 0 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 1Y 121 11 00 10 01 11 00 11 0F=ABC+ABC+ABA图24.由两个三态门组成的逻辑电路如图3所示,试分析其逻辑功能。

数字电子技术基础题库及答案

试题库及答案试卷一一.基本概念题(一)填空题(共19分,每空1分)1.按逻辑功能的不同特点,数字电路可分为和两大类。

2.在逻辑电路中,三极管通常工作在和状态。

3.(406)10=()8421BCD4.一位数值比较器的逻辑功能是对输入的数据进行比较,它有、、三个输出端。

5.TTL集成JK触发器正常工作时,其d R和d S端应接电平。

6.单稳态触发器有两个工作状态和,其中是暂时的。

7.一般ADC的转换过程由、、和4个步骤来完成。

8.存储器的存储容量是指。

某一存储器的地址线为A14~A0,数据线为D3~D0,其存储容量是。

(二)判断题(共16分,每题2分)1.TTL或非门多余输入端可以接高电平。

()2.寄存器属于组合逻辑电路。

()3.555定时器可以构成多谐振荡器、单稳态触发器、施密特触发器。

()4.石英晶体振荡器的振荡频率取决于石英晶体的固有频率。

( )5.PLA 的与阵列和或阵列均可编程。

( )6.八路数据分配器的地址输入(选择控制)端有8个。

( )7.关门电平U OFF 是允许的最大输入高电平。

( )8.最常见的单片集成DAC 属于倒T 型电阻网络DAC 。

( )(三) 选择题(共16分,每题2分)1.离散的,不连续的信号,称为( )。

A .模拟信号 B.数字信号2.组合逻辑电路通常由( )组合而成。

A .门电路 B.触发器 C.计数器3.8线—3线优先编码器的输入为I 0—I 7 ,当优先级别最高的I 7有效时,其输出012Y Y Y ••的值是( )。

A .111 B.010 C.000 D.1014.十六路数据选择器的地址输入(选择控制)端有( )个。

A .16 B.2 C.4 D.85.一位8421BCD 码译码器的数据输入线与译码输出线的组合是( )。

A .4:6 B.1:10 C.4:10 D.2:46.常用的数字万用表中的A/D 转换器是( )。

A .逐次逼近型ADC B.双积分ADC C.并联比较型ADC7.ROM 属于( )。

74ls138功能测试实验报告

74ls138功能测试实验报告实验名称:74LS138功能测试实验实验目的:1.理解74LS138译码器的工作原理;2.学习使用74LS138实现多路选择功能;3.进行74LS138功能测试。

实验器材:1.74LS138译码器芯片;2.74LS00与非门芯片;3.逻辑开关;4.数码管;5.电源供应器;6.连接线。

实验原理:74LS138是一种常用的3-8译码器,它具有3个输入端(A,B,C)和8个输出端(Y0,Y1,Y2,Y3,Y4,Y5,Y6,Y7)。

输入端共有23=8种状态,输出端根据输入端的状态进行译码,只有一个输出为低电平,其他输出为高电平。

实验步骤:1.连接电路:将74LS138芯片与74LS00芯片、逻辑开关、数码管和电源供应器依次连接起来。

2.编写测试程序:根据74LS138的真值表,编写测试程序,使得数码管能正确显示输入端的状态。

3.上电测试:将电源供应器接通电源,观察数码管的显示情况,验证74LS138的功能是否正常。

4.更改输入端状态:随机更改输入端的状态,观察数码管的显示情况,进一步验证74LS138的功能是否正常。

实验结果:经过测试,实验结果如下:输入端(A,B,C)输出端(Y0,Y1,Y2,Y3,Y4,Y5,Y6,Y7)结论:通过实验,验证了74LS138译码器的功能正常,能够根据输入端的状态进行正确的译码,并将对应的输出端置为低电平,其他输出端为高电平。

实验结果与真值表相符。

实验总结:通过本次实验,我深入了解了74LS138译码器的工作原理,并学会了使用74LS138实现多路选择功能。

实验结果表明,74LS138译码器能够正确地译码,并根据输入端的状态进行输出。

这对于数字电路设计和逻辑控制具有重要的意义。

实验过程中,我还学会了编写测试程序,用于验证芯片的功能是否正常。

通过实验,我对数字电路译码器的原理和应用有了更深入的理解,为今后的学习和实践奠定了基础。

(二)集成3线—8线译码器74LS138[共2页]

![(二)集成3线—8线译码器74LS138[共2页]](https://img.taocdn.com/s3/m/68945b51bceb19e8b9f6ba1f.png)

二、相关知识

(一)二进制译码器

将输入的 n 位二进制代码译成相应的 2 n 个输出信号的电路,称为二进制译码器。

2 线—4 线译码器的真值表见表 8-17。

表 8-17

2 线—4 线译码器的真值表

输入

输出

A1

A0

Y3

Y2

Y1

Y0

0

0

0

0

0

1

0

1

0

0

1

0

1

0

0

1

0

0

1

1

1

0

0

0

2 线—4 线译码器的逻辑电路如图 8-37 所示,输入端 EI 为使能控制端,低电平有效。

0

1

0

1

1

1

0

1

1

1

1

1

1

0

1

1

0

1

0

1

1

1

1

1

1

1

0

1

1

1

0

1

1

1

1

1

1

1

(3)引脚功能介绍。A2、A1、A0 为二进制译码输入端, Y7 ~Y0 为译码输出端(低电平有效), S1、S2 、S3 为选通控制端。当 S1 = 1 ,S2 +S3 =0 时,译码器处于译码状态;当 S1=0 ,S2 +S3 =1时, 译码器处于禁止状态。

(二)集成 3 线—8 线译码器 74LS138

(1)集成译码器 74LS138 的引脚排列及逻辑功能示意图如图 8-38 所示。

图 8-37 2 线—4 线译码器逻辑图

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2.1待开发软件的一般描述

本软件旨在为图书馆系统管理员来管理图书馆书数目的增加、更新、删除、查询、对读者个人信息的查询、更改、删除;图书管理员可以借阅、归还图书;读者可以借阅、归还、预定图书、对个人信息的查询等。

2.2待开发软件的功能

不通过

图书馆管理系统

密码管理图

书

查

询

图

书

借

阅

图

书

预

定

图

书

更

新

读

者

留

言

板

系

统

维

护

身份验证

重新验证

退出

正常退出

2.3用户特征

用户和访客具有基础计算机使用常识的人,图书管理人员对整个图书系统要有基本了解,并对计算机熟练操作,数据库较为熟练。

2.4运行环境

(1)硬件环境

客户机:普通pc

CPU:P41.8GHz以上

内存:256MB以上

能够运行

IE5.0以上或者Netscape4.0以上版本的机器

分辨率:推荐使用1024*768像素

Web服务器

CPU: P41.0GHz

内存:1G以上

硬盘:80GB以上

网卡:K Mb/s速度

数据库服务器

CPU: P42.0GHz

内存:1GB以上

硬盘:80GB以上

(2)软件环境

操作系统:UNIX/Linux/window2000或以上版本

2.5条件与限制

考虑到本软件使用的广泛性,在设计时应注意软件的可移植性,能方便地将其移植到手机,平板电脑等硬件平台。

因本软件管理的信息属于个人隐私信息,必须注意信息的安全防范。

同时应以标准的数据格式来实现,以方便数据的共享。