IBIS模型与高速PCB设计分析

基于Cadence_Allegro的高速PCB设计信号完整性分析与仿真

基于Cadence_Allegro的高速PCB设计信号完整性分析与仿真覃婕;阎波;林水生【摘要】信号完整性问题已成为当今高速PCB设计的一大挑战,传统的设计方法无法实现较高的一次设计成功率,急需基于EDA软件进行SI仿真辅助设计的方法以解决此问题.在此主要研究了常见反射、串扰、时序等信号完整性问题的基础理论及解决方法,并基于IBIS模型,采用Cadence_Allegro软件的Specctraquest和Sigxp组件工具对设计的高速14位ADC/DAC应用系统实例进行了SI仿真与分析,验证了常见SI问题解决方法的正确性.%Signal Integrity (SI) problem has became one of the greatest challenge in high-speed PCB design area, the traditional design method is hard to realize high once-through design success, SI simulation aided design method based on EDA software is demanded to solve this problem. The basic theory and solutions of some normal SI problems such as reflection,crosstalk and timing are researched. SI analysis and simulation of a high-speed 14bits ADC/DAC application system based on Specctraquest and Sigxp in Cadence_Allegrospb 16. 0 are designed, the validity of the solutions to the SI problems is verified.【期刊名称】《现代电子技术》【年(卷),期】2011(034)010【总页数】4页(P169-171,178)【关键词】高速PCB设计;信号完整性;反射;串扰;时序;SI分析及仿真【作者】覃婕;阎波;林水生【作者单位】电子科技大学通信与信息工程学院,四川成都,611731;电子科技大学通信与信息工程学院,四川成都,611731;电子科技大学通信与信息工程学院,四川成都,611731【正文语种】中文【中图分类】TN919-340 引言随着半导体工艺的迅猛发展以及人们对信息高速化、宽带化的需求,高速PCB 设计已经成为电子产品研制的一个重要环节,信号完整性( Signal Integrity,SI)问题(包括反射、串扰、定时等)也逐渐发展成为高速PCB设计中难以避免的难题,若不能较好地解决信号完整性设计问题,将有可能造成高速PCB设计的致命错误,浪费财力物力,延长开发周期,降低生产效率。

高速pcb设计与电路板分析课程讲义3

高速设计分析技术Agenda 课程安排High Speed Trends 高速设计趋势y gSynchronous Design 同步系统设计Source Synchronous Design 源同步系统设计-DDR2-DDR3Serial Link Design 高速串行设计-Interconnect consideration 互连考虑I t t id ti-Technologies 设计技术-8b/10b Encoding 8b/10b编码Trend towards serial connectivity向串行连接发展高速电路设计趋势Parallel I/O − Common Clock并行IO –共同时钟系统Pre-layout simulation for design exploration and post-layout simulation for verification可以通过SI前后仿真进行设计•Signal timing 信号时序•Signal noise 信号噪声•Undershoot and overshoot 过冲Parallel I/O − Common Clock (继续) 并行IO –共同时钟Increase data pin counts How to increase data rate? 如何提高数据速率Increase data pin counts 增加管脚Increase bus clock frequency 增加时钟频率But…… 但是……•Increase data pin counts − it’s more hard for PCB design(need more space for trace breakout, routing…..) 增加管脚造成PCB 设计困难•Increase clock frequency − it will reduce timing margin,destroy signal integrity (due to multi-drop top.), restrict data trace length, increase EMI…增加时钟频率使得时序紧张, 信号完整性问题突出, 走线线长约束严格, 电磁辐射增加…Parallel I/O − Source Synchronous并行I/O –源同步系统Provide guidelines for physical layout by sweeping the solution space 可以通过参数扫描分析确定电气约束Measurements for voltage and time specifications and worst case Measurements for voltage and time specifications and worst case report 得到最坏情况下的信号质量和时序要求Bus timing analysis 总线时序分析•Slew rate prorating/derating for Setup/Hold Time compensations (DDR2) 考虑边沿速率造成的的建立保持时间的补偿(DDR2)Increase bus clock frequency Parallel I/O − Source Synchronous (继续)并行I/O –源同步系统How to increase data rate? 如何提高数据速率Increase bus clock frequency 增加时钟频率From single strobe to dual strobe 采用读写数据采样时钟From single end strobe to differential strobe signaling 采用差分时钟•Increase bus clock frequency − there is no theoretical limit on bus clock frequency, but higher clock frequency will cause signal integrity depredation(due to multi ‐drop top.) But…… 但是……p (p p )增加时钟频率使得信号完整性问题突出…•From single strobe to differential strobe − for less timing margin while design migrates to high speed, differential strobe will increase valid timing window采用差分时钟提高速率但是因为速率提高, 时序参数更为紧张Parallel I/O -Integrating SI with Timing 并行接口分析–综合考虑SI 和时序Multiple TopologiesWaveformandSolution SpaceTiming Equation Signal Integrity and Timing Analysis integrated to one solution 信号完整性和时序分析组成一个完整的解决方案Vin_AC_HighVin_DC_HighVrefVin_DC_LowVin_AC_Low “Sim Start time” normalizedSerial I/O 串行I/OInterconnect loss of the channel (entire signal path) 考虑互连损耗Jitter controlled is required due to CDR 控制抖动Modeling complex drivers and receivers 需要更复杂的器件模型 Stress test the design with LARGE bit streams 要分析大量数据位传输S-parameter simulation (Time domain & Frequency Domain) S-参数分析, 时域和频域分析Agenda 课程安排High Speed Trends 高速设计趋势y gSynchronous Design 同步系统设计Source Synchronous Design 源同步系统设计-DDR2-DDR3Serial Link Design 高速串行设计-Interconnect consideration 互连考虑I t t id ti-Technologies 设计技术-8b/10b Encoding 8b/10b编码Synchronous Design 同步设计系统Sometimes called “Common Clock” 又叫共同时钟系统Clocks are distributed from a central point to all of the loads. 时钟信号由同一时钟源发送Max operating frequency is a function of Tco, Tpd, Setup, Hold, and M ti f i f ti f T T d S t H ld d Clock Skew最大工作频率由缓冲延时,传输延时,建立,保持时间和时钟偏移决定Synchronous Data Transfer 数据传输方式Clock 14HoldDriverT coFlight Time Setup23D0 D1 D2D0 D1 D2Driving ReceivingSynchronous Timing Terminology时序参数Cycle Time (Tcycle)时钟周期Clock Skew时钟偏移Cycle 1Cycle 2 Clock to Output (Tco)时钟输出延时Clock JitterSynchronous Timing Terminology (继续)时序参数Interconnect Delay (Tpd)互连传输延时Positive Interconnect Delay (Tpd)Negative Interconnect Delay (Tpd)Defining Tco Tco 定义Tco = time from clock rise to Vmeas into test load从时钟边沿进入器件到数据从器件输出有效的时间(数据输出接测试负载)DinClockOutput BufferInternal LogicClock rises t = 0V measT R L = 50 ΩTcoLoad for Tco measurement (from databook)Components of Tco Tco的组成ClockI t lClockDinOutputBufferInternalLogicR L= 50 Ωrisest = 0V measTcoInternal delay = from clock rise to the point where the output begins to switch内部逻辑时延External (buffer) delay = how long the buffer takes to drive the reference load to V meas缓冲器时延Clock Jitter 时钟抖动Clock Clock Jitter occurs when the clock period varies from one period to the nextDriverCycle 1Cycle 2one period to the next 考虑周期差抖动•Usually caused by PLLinstability in the clockdriver 通常由锁相环引起 Jitter increases / decreases the clock periodthe clock period,decreasing the effective clock cycle 抖动减小有效时钟周期Clock Skew 时钟偏斜Clock Driver t = 0Occurs when differentdevices see the clocktransition at differenttimesD0D0t = 1t = 2时钟到达不同器件的时延Increases / decreasesthe apparent clockcycle. Depending onwhich devices aredriving / receivingD1D2D1D2g g根据驱动接收不同变化Reduces the effectiveclock cycle 减小有效时钟周期内部偏斜和外部偏斜•时钟驱动器造成内部偏斜•而PCB布线和设计以及外部环境引起的偏斜被称为外C部偏斜tSKEW_INTRINSIC = 器件引起的偏斜tSKEW_EXTRINSIC = PCB + 布线+工作环境引起的偏斜tSKEW = tSKEW_INTRINSIC + tSKEW_EXTRINSIC内部偏斜-输出偏斜(tSK)•单一器件的指定输出之间的偏斜(JEDEC)•输出偏斜也称为引脚到引脚的偏斜。

IBIS模型的仿真研究与应用分析

IBIS模型的仿真研究与应用分析

石章如

【期刊名称】《武汉理工大学学报(信息与管理工程版)》

【年(卷),期】2005(027)005

【摘要】光收发一体模块作为光通信的核心器件一直是光通信领域的研究热点.通过阐述IBIS模型与PCB板信号完整性之间的关系,介绍了基于IBIS模型的信号完整性分析的概念及仿真步骤,最后给出了基于IBIS模型的仿真分析在千兆SFP光纤收发器中的成功应用实例.

【总页数】4页(P9-12)

【作者】石章如

【作者单位】武汉理工大学,信息工程学院,湖北,武汉,430070

【正文语种】中文

【中图分类】TN911

【相关文献】

1.基于IBIS模型的仿真分析在高速服务器主板GSMB-1中的应用 [J], 杨功立;刘春红;王晓东

2.仪控系统PCB设计中IBIS模型的研究与应用 [J], 钟秉飞;胡立生

3.基于IBIS模型的信号完整性仿真分析 [J], 方国华;刘光斌;余志勇

4.基于IBIS模型的仿真分析在高速DSP系统设计中的应用 [J], 童智勇;韩月秋

5.基于IBIS模型的多路脉冲信号源ADS仿真 [J], 周文渊;呼义翔;罗维熙;张信军;尹佳辉

因版权原因,仅展示原文概要,查看原文内容请购买。

基于时域有限差分法的IBIS模型修正

基于时域有限差分法的IBIS模型修正张志伟【摘要】针对高速电路设计中IBIS模型仿真精度较差问题,将时域有限差分算法与IBIS模型相结合.通过实验对高速PCB设计中常见的结构(完整接地面、狭缝和过孔)进行了信号完整性分析,结合时域有限差分法改进的波形、speed2000仿真波形与实际测量的波形三者之间的比较,结果表明该修正算法可以显著提高仿真模型的准确度,达到提高设计成功率,缩短研发周期,降低成本的功效.【期刊名称】《微型机与应用》【年(卷),期】2011(030)009【总页数】3页(P93-95)【关键词】时域有限差分法;speed2000;IBIS;信号完整性;仿真模型【作者】张志伟【作者单位】陕西理工学院.电信工程系,陕西汉中723000【正文语种】中文【中图分类】TP391.41高速PCB设计在数字系统设计中占据着越来越重要的地位,系统能够稳定工作,在很大程度上取决于PCB设计。

整个高速PCB设计过程就是发现由高速高密度引起的信号完整性问题然后解决的过程[1]。

目前,进行信号完整性分析主要借助于专业软件的帮助,然而,每个公司的产品均会对自己公司的设计或者研究领域有侧重,相对于一些有个性需求的公司或者设计,往往会存在兼容性不好。

针对IBIS模型仿真精确度低的现象,对模型进行适当的修正就是设计师必须考虑的问题[2]。

近年来在信号完整性的电磁场数值分析方法中,时域有限差分法(FDTD)受到广泛的重视。

时域有限差分法是求解麦克斯韦微分方程的直接时域方法,在计算中将空间某一点的电场(或磁场)与周围格点的磁场(或电场)直接相关连,且介质参数已赋值给空间中的每一个元胞,因此此方法可以处理复杂形状目标和非均匀介质物体的电磁散射、辐射等问题[3]。

1 时域有限差分算法分析IBIS模型1.1 IBIS模型简介Intel最初提出了IBIS模型的概念,IBIS(Input/Output Buffer Informational Specifation)是用来描述 IC器件的输入、输出和I/O Buffer行为特性的文件。

IBIS仿真模型的应用

的敏感信息, 从而保护了研发者及经销商的知识产 权。因此, 在高速 PCB 仿真设计中, IBIS 模型受到仿 真者的青睐。为了便捷高效的应用好 IBIS 进行高速 PCB 的仿真设计, 本文比较深入剖析了 IBIS 模型的 应 用 , 从 IBIS 模 型 中 , 可 以 得 出 以 下 几 个 方 面 重 要 结论:

IBIS( I/O Buffer Information Specification) 模型采 用 I/V 和 V/T 表的形式来描述 数 字 集 成 电 路 I/O 单 元的电气特性, 并把这些数据记录在标准的文件中。 IBIS 行为建模数据可以通过裸芯片直接测量得到, 也可以由模拟获得, 因此行为模型不仅较 SPICE 模 型简单, 而且可能具有更高精度, 同时该模型具有分 段线性特性, 因此采用器件行为模型的模拟一般比 采用相应的晶体管模型模拟执行起来速度更快, 从 而可提高系统的电路分析效率。另外, 一个行为级的 器件模型不泄露任何有关设计技术和底层布线过程

min

max

dV/dt_r

1.1766/0.1304n 1.0713/0.1987n

1.2583/0.1022n

dV/dt_f

1.1887/96.7911p 1.0618/0.1536n

1.2756/72.6418p

R_load = 50.0000

可以看出在典型驱动的情况下,

Tr=

dt_r+dt_f 2

4 倍和 6 倍的信号走线延时 Td 的情况。上面的四组 波形中, 前三个波形都出现了一定的信号完整性问 题, 第四组波形正好是集中参数系统, 没有出现信号 完整性问题。由此证实了通过 IBIS 模型来估算信号 的上升时间 Tr, 进而确定 PCB 走线的关键长度, 当这 个长度超过关键长度时应该考虑信号完整性问题。

IBIS模型及其应用讲解

IBIS模型及其应用CDMA事业部眭诗菊摘要:本文介绍了用于高速系统信号完整性分析的IBIS模型的历史背景、IBIS模型的结构、IBIS模型的建模过程、IBIS模型的参数、语法格式,以及在使用IBIS模型时常遇到的问题和解决方法。

关键词:IBIS模型、EDA、信号完整性、缓冲器、单调性、收敛高时钟频率下运行的并行处理系统或其它功能更加复杂的高性能系统,对电路板的设计提出了极其严格的要求。

按集总系统的方法来设计这些系统的线路板已不可想象。

许多EDA (电子设计自动化)供应商都提供能进行信号完整性分析和EMC分析的PCB设计工具。

这些工具需要描述线路板上元器件的电气模型。

IBIS(I/O Buffer Information Specification)模型是EDA供应商、半导体器件供应商和系统设计师广泛接受的器件仿真模型。

一、IBIS的背景及其发展在IBIS出现之前,人们用晶体管级的SPICE模型进行系统的仿真,这种方法有以下三个方面的问题:第一,结构化的SPICE模型只适用于器件和网络较少的小规模系统仿真,借助这种方法设定系统的设计规则或对一条实际的网络进行最坏情况分析。

第二,得到器件结构化的SPICE模型较困难,器件生产厂不愿意提供包含其电路设计、制造工艺等信息的SPICE模型。

第三,各个商业版的SPICE软件彼此不兼容,一个供应商提供的SPICE模型可能在其它的SPICE仿真器上不能运行。

因此,人们需要一种被业界普遍接受的、不涉及器件设计制造专有技术的、并能准确描述器件电气特性的行为化的、“黑盒”式的仿真模型。

1990年初,INTEL公司为了满足PCI总线驱动的严格要求,在内部草拟了一种列表式的模型,数据的准备和模型的可行性是主要问题,因此邀请了一些EDA供应商参与通用模型格式的确定。

这样,IBIS 1.0 在1993年6月诞生。

1993年8月更新为IBIS 1.1版本,并被广泛接受。

此时,旨在与技术发展要求同步和改善IBIS模型可行性的IBIS论坛成立,更多的EDA供应商、半导体商和用户加入IBIS论坛。

IBIS模型

IBIS:Input/Output Buffer Information Specification的简写,是进行数字电路的传输线路分析即信号完整性分析,描述高速器件输入输出特性的行为模型。

简单的说就是【高速PCB板仿真使用的模型】。

IBIS的规格是IBIS开放论坛制定的,但是其只规定了信息的格式,关于仿真处理和模型的使用方法并没有特别规定。

1IBIS模型的构成:IBIS模型里记录器件Pin脚的排列信息和输入输出的特性,基本的构成如下:1、驱动模型(输出模型)Though rate: 上升、下降的特性Pull down I-V curb: 在输出为逻辑低电平时,半导体的I/V特性曲线Pull up I-V curb: 在输出为逻辑高电平时,半导体的I/V特性曲线I/V curb: 【power clamp】clamp和【GND clamp】clamp二极管特性半导体芯片的电容C_comp封装的LCR特性2、接收器模型(1):I-V curb:【power clamp】clamp和【GND clamp】clamp 二极管特性(2):半导体芯片的电容C_comp(3):封装的LRC特性等效电路图IBIS模型的创建及优化随着半导体器件的高速化和高度集成,要求我们从电路设计阶段到PCB板设计阶段就需要进行传输线路的仿真分析,来合理布局布线。

作为分析中必要的器件模型,IBIS模型和SPICE模型得到了广泛的利用,但是IBIS模型凭借其易于获得,简易,仿真速度的优势,更加适用于PCB高速仿真。

含有高速半导体器件的PCB板设计中,为了减少改版的次数,运用EDA工具进行信号完整性分析是必不可少的。

但是,如果我们获取的高速器件的IBIS模型有问题,在仿真的时候就会产生错误,这样又需要研究错误原因,修改IBIS模型,从而导致仿真时间的增加。

另外,实用有问题的IBIS模型即使能顺利仿真,但样机的实际测量值于仿真结果不一致,就无法确认设计是否符合要求,这样的话,仿真起不到其作用。

ibis模型在高速电路设计中的应用

ibis模型在高速电路设计中的应用导言:高速电路设计是现代电子产品设计中的重要部分,涉及到信号传输速率、电流与电压波形的稳定性、信号完整性等多个关键参数。

为了准确评估高速电路的性能,工程师需要使用模型来进行仿真和分析。

其中,Ibis模型是一种常用的工具,被广泛应用于高速电路设计中。

本文将介绍Ibis模型的基本原理以及其在高速电路设计中的应用。

一、Ibis模型的基本原理1. Ibis模型的概念Ibis(Input/Output Buffer Information Specification)模型是一种用来描述输入输出缓冲器行为的数学模型。

它包含了关于信号传输和响应延时的信息,能够准确地预测芯片之间的信号完整性和电路性能。

2. Ibis模型的组成Ibis模型由四个主要部分组成:输入特性、输出特性、仿真模型和电路模型。

输入特性定义了输入电信号的波形、电压和电流。

输出特性则描述了输出电信号的波形、电压和电流。

仿真模型和电路模型用于将输入和输出特性转化为电路仿真所需的数学模型。

二、Ibis模型在高速电路设计中的应用1. 信号完整性评估Ibis模型能够准确地描述信号传输的特性,从而帮助工程师评估信号完整性。

通过分析Ibis模型中的波形和传输特性,工程师可以确定信号的稳定性、上升/下降时间等关键参数,以便优化电路设计,提高信号质量。

2. 电压和电流仿真在高速电路设计中,为了保证电路的工作稳定性,需要对电压和电流进行仿真。

Ibis模型提供了输入和输出的电压、电流信息,并且能够通过仿真模型和电路模型准确地进行电压和电流仿真,从而帮助工程师评估电路性能和优化设计。

3. 时序分析Ibis模型还能够用于时序分析,即分析信号的传输延迟和时序关系。

通过分析Ibis模型中的传输延迟和时序特性,工程师可以确定信号传输的先后顺序,并且确保信号到达目标设备的正确时刻,从而提高系统的稳定性和可靠性。

4. 模型验证与产品测试在高速电路设计的过程中,工程师需要验证Ibis模型的准确性,并对设计的产品进行测试。

高速数字电路设计信号完整性仿真IBIS模型编写原理

由上可知,IBIS 模型的优点可以概括为: 在 I/O 非线性方面能够提供准确的模型,同时考虑了封装的寄生参数与 ESD 结构; 提供比结构化的方法更快的仿真速度; 可用于系统板级或多板信号完整性分析仿真。可用 IBIS 模型分析的信号完整性问题包括: 串扰、反射、振荡、上冲、下冲、不匹配阻抗、传输线分析、拓扑结构分析。IBIS 尤其能够 对高速振荡和串扰进行准确精细的仿真,它可用于检测最坏情况的上升时间条件下的信号行 为及一些用物理测试无法解决的情况; 模型可以免费从半导体厂商处获取,用户无需对模型付额外开销; 兼容工业界广泛的仿真平台。 当然,IBIS 不是完美的,它也存在以下缺点: 许多芯片厂商缺乏对 IBIS 模型的支持。而缺乏 IBIS 模型,IBIS 工具就无法工作。虽然 IBIS 文件可以手工创建或通过 Spice 模型自动转换,但是如果无法从厂家得到最小上升时间 参数,任何转换工具都无能为力。 IBIS 不能理想地处理上升时间受控的驱动器类型的电路,特别是那些包含复杂反馈的电 路; IBIS 缺乏对地弹噪声的建模能力。IBIS 模型 2.1 版包含了描述不同管脚组合的互感,从

IBIS 模型是以元件为中心的,也就是说,一个 IBIS 文件允许你模拟整个的一个元件, 而不仅仅是一个特定的输入、输出或 I/O 缓冲器。因而,除了器件缓冲器的电学特性参数以 外,IBIS 文件还包括了器件的管脚信息以及器件封装的电学参数。从 Version 1.1 开始,就 定义了一个 IBIS 模型文件的最基本的组成元素为 I/V 数据表、开关信息和封装信息(图 1)。

高速电路中的信号完整性问题

高速电路中的信号完整性问题摘要:介绍高速电路的特点,引入高速电路中的信号完整性问题,讨论了影响高速电路信号完整性的因素,介绍分析信号完整性的模型和仿真工具。

关键词PCB 信号完整性分析1.概述所谓高速数字电路,是指由于信号的高速变化而使得电路中的模拟特性,如导线的电感,电容等发生作用的电路。

高速数字电路一般来说频率较高,电容电阻的特性变化较快。

信号变化速度较快时,容抗感抗的值将无法忽略。

同时两个互不相连的导线之间也会产生无法忽略的感应电流和感应电压。

正是因为这些新特点,从而使得高速电路设计时,产生了许多需要考虑的新问题:信号的反射,地弹,振铃,以及信号间的串扰。

基于以上这些原因,我们要对PCB 进行信号完整性的分析。

2.信号完整性2.1 信号完整性(SI)定义信号完整性是指信号在信号线上的质量。

信号具有良好的信号完整性是指信号在需要的时候,具有所必需达到相应的电压电平和时间指标。

信号完整性具有以下两个基本条件:(1)空间完整性,又称信号幅值完整性,为满足电路的最小输入高电平和最大输入低电平要求;(2)时间完整性,为满足电路的最小建立和维持时间。

2.2 信号完整性解决的主要问题(1)电源分布电源分布网络是高速电路板设计中最重要的考虑因素。

电源分布网络必须为低噪声的电路板上各部分电路提供一个低噪声的电源,包括VCC 和接地。

电源分布网络同时还得为电路板上所有产生或接受的信号提供一个信号回路。

(2)串扰(Crosstalk)串扰是指线迹之间不必要的信号耦合,它可以是电容性的或者是电感的。

电容性串扰是指信号线路之间的信号电容耦合,当线路以一定的距离彼此靠近时,会出现这种情况。

电感的串扰可以看作是不需要的变压器的原线圈和次级线圈之间的信号耦合。

变压器的线圈就是电路板或者系统上的电流环路,它可能是由无效的布局造成的人造环路,也可能是信号路径和信号返回路径综合形成的自然环路。

(3)反射、过冲、振铃、多次跨越逻辑电平错误传输过程中的任何不均匀(如阻抗变化、直角线或过孔)都会引起信号的反射,反射的结果对模拟信号(正弦波)将形成驻波,对数字信号则表现为上升沿、下降的振铃和过冲。

高速数字系统PCB电路中的信号完整性设计方案

现在的高速数字系统的频率可能高达数百兆Hz,其快斜率瞬变和极高的工作频率,以及很大的密集度,必将使得系统表现出与低速设计截然不同的行为,出现了信号完整性问题。

破坏了信号完整性将直接导致信号失真、定时错误,以及产生不正确数据、地址和控制信号,从而造成系统误工作甚至导致系统崩溃。

因此,信号完整性问题已经越来越引起高速设计人员的关注。

1 信号完整性问题及其产生机理信号完整性SI(Signal Ingrity)涉及传输线上的信号质量及信号定时的准确性。

在数字系统中对于逻辑1和0,总有其对应的参考电压,正如图1(a)中所示:高于ViH的电平是逻辑1,而低于ViL的电平视为逻辑0,图中阴影区域则可视为不确定状态。

而由图1(b)可知,实际信号总是存在上冲、下冲和振铃,其振荡电平将很有可能落入阴影部分的不确定区。

信号的传输延迟会直接导致不准确的定时,如果定时不够恰当,则很有可能得到不准确的逻辑。

例如信号传输延迟太大,则很有可能在时钟的上升沿或下降沿处采不到准确的逻辑。

一般的数字芯片都要求数据必须在时钟触发沿的tsetup前即要稳定,才能保证逻辑的定时准确(见图1(c))。

对于一个实际的高速数字系统,信号由于受到电磁干扰等因素的影响,波形可能会比我们想象中的更加糟糕,因而对于tsetup 的要求也更加苛刻,这时,信号完整性是硬件系统设计中的一个至关重要的环节,必须加以认真对待。

一个数字系统能否正确工作其关键在于信号定时是否准确,信号定时与信号在传输线上的传输延迟和信号波形的损坏程度有关。

信号传输延迟和波形的原因复杂多样,但主要是以下三种原因破坏了信号完整性:(1)反射噪声其产生的原因是由于信号的传输线、过孔以及其它互连所造成的阻抗不连续。

(2)信号间的串扰随着印刷板上电路的密集度不断增加,间的几何距离越来越小,这使得信号间的电磁已经不能忽略,这将急剧增加信号间的串扰。

(3)电源、地线噪声由于芯片封装与电源平面间的寄生和的存在,当大量芯片内的电路和输出级同时动作时,会产生较大的瞬态,导致电源线上和地线上的电压波动和变化,这也就是我们通常所说的地跳。

利用IBIS模型完善信号完整性计算和PCB设计

利用IBIS模型完善信号完整性计算和PCB设计利用IBIS模型完善信号完整性计算和PCB设计本文是关于在印刷电路板(PCB)开发阶段使用数字输入/输出缓冲信息规范(IBIS)模拟模型的文章。

本文将介绍如何使用一个IBIS 模型来提取一些重要的变量,用于信号完整性计算和确定 PCB 设计解决方案。

请注意,该提取值是 IBIS 模型不可或缺的组成部分。

图1 错配端接阻抗 PCB 装置。

信号完整性问题当观察传输线两端的数字信号时,设计人员会吃惊于将信号驱动至某条 PCB 线迹时出现的结果。

通过相对较长的距离,相比瞬时变化信号,电信号更像行波。

描述电路板上电波行为的较好模拟是池中波(wave in a pool)。

纹波穿过池顺利传播,因为体积相同的两组水具有相同的“阻抗”。

然而,池壁的阻抗差异明显,并以相反方向反射波。

注入PCB 线迹的电信号也出现相同的现象,其在阻抗错配时以类似方式反射。

图 1 显示了错配端接阻抗的一个 PCB 装置。

微控制器即TI MSP430 向 TI ADS8326 ADC 发送一个时钟信号,其将转换数据发送回 MSP430。

图 2 显示了该装置中阻抗错配所形成的反射。

这些反射在传输线迹上引起信号完整性问题。

让一端或者两端的 PCB 线迹电阻抗相匹配可极大地减少反射。

图2:图1中错配端接阻抗促发反射。

要解决系统电阻抗匹配问题,设计人员需要理解集成电路(IC)的阻抗特性,以及起到传输线迹作用的PCB 线迹的阻抗特性。

知道这些特性,让设计人员能够将各连接单元建模为分布式传输线迹。

传输线迹为各种电路服务,从单端和差分端器件到开漏输出器件。

本文主要介绍单端传输线迹,其驱动器有一个推拉输出电路设计。

图3 显示了用于设计该举例传输线迹的各组成部分。

图3 实例单端传输线电路。

另外,还需要如下 IC 引脚规范:发送器输出电阻 Z T (Ω)发送器上升时间t Rise和下降时间t Fall (秒)接收机输入电阻Z R (Ω)接收机引脚电容值C R_Pin (F)这些规范一般没有在 IC 制造厂商的产品说明书中。

IBIS模型及其应用讲解

CDMA事业部眭诗菊摘要:本文介绍了用于高速系统信号完整性分析的IBIS模型的历史背景、IBIS模型的结构、IBIS模型的建模过程、IBIS模型的参数、语法格式,以及在使用IBIS模型时常遇到的问题和解决方法。

关键词:IBIS模型、EDA、信号完整性、缓冲器、单调性、收敛高时钟频率下运行的并行处理系统或其它功能更加复杂的高性能系统,对电路板的设计提出了极其严格的要求。

按集总系统的方法来设计这些系统的线路板已不可想象。

许多EDA (电子设计自动化)供应商都提供能进行信号完整性分析和EMC分析的PCB设计工具。

这些工具需要描述线路板上元器件的电气模型。

IBIS(I/O Buffer Information Specification)模型是EDA供应商、半导体器件供应商和系统设计师广泛接受的器件仿真模型。

一、 IBIS的背景及其发展在IBIS出现之前,人们用晶体管级的SPICE模型进行系统的仿真,这种方法有以下三个方面的问题:第一,结构化的SPICE模型只适用于器件和网络较少的小规模系统仿真,借助这种方法设定系统的设计规则或对一条实际的网络进行最坏情况分析。

第二,得到器件结构化的SPICE模型较困难,器件生产厂不愿意提供包含其电路设计、制造工艺等信息的SPICE模型。

第三,各个商业版的SPICE软件彼此不兼容,一个供应商提供的SPICE模型可能在其它的SPICE仿真器上不能运行。

因此,人们需要一种被业界普遍接受的、不涉及器件设计制造专有技术的、并能准确描述器件电气特性的行为化的、“黑盒”式的仿真模型。

1990年初,INTEL公司为了满足PCI总线驱动的严格要求,在内部草拟了一种列表式的模型,数据的准备和模型的可行性是主要问题,因此邀请了一些EDA供应商参与通用模型格式的确定。

这样,IBIS 在1993年6月诞生。

1993年8月更新为IBIS 版本,并被广泛接受。

此时,旨在与技术发展要求同步和改善IBIS模型可行性的IBIS论坛成立,更多的EDA供应商、半导体商和用户加入IBIS论坛。

IBIS模型详解中文版

目录§1 绪论 (1)1.1 IBIS模型的介绍 (1)1.2 IBIS的创建 (3)§2 IBIS模型的创建 (3)2.1 准备工作 (3)2.1.1 基本的概念 (3)2.1.2 数据列表的信息 (4)2.2 数据的提取 (4)2.2.1 利用Spice模型 (4)2.2.2 确定I/V数据 (4)2.2.3 边缘速率或者是V/T波形的数据的测量 (7)2.2.4 试验测量获取I/V和转换信息的数据 (7)2.3 数据的写入 (8)2.3.1 IBS文件的头I信息 (8)2.3.2 器件和管脚的信息 (8)2.3.3 关键词Model的使用 (9)§3 用IBIS模型数据验证模型 (10)3.1 常见的错误 (10)3.2 IBIS模型的数据验证 (12)3.2.1 Pullup、Pulldown特性 (12)3.2.2 上升和下降的速度(Ramp rate) (12)3.2.3 上下拉特性和Ramp rate的关系 (12)3.3 用IBIS模型数据验证模型参数的实例 (12)§1 绪论1.1 IBIS模型的介绍IBIS(Input/Output Buffer Informational Specifation)是用来描述IC器件的输入、输出和I/OBuffer行为特性的文件,并且用来模拟Buffer和板上电路系统的相互作用。

在IBIS模型里核心的内容就是Buffer的模型,因为这些Buffer产生一些模拟的波形,从而仿真器利用这些波形,仿真传输线的影响和一些高速现象(如串扰,EMI等。

)。

具体而言IBIS描述了一个Buffer的输入和输出阻抗(通过I/V曲线的形式)、上升和下降时间以及对于不同情况下的上拉和下拉,那么工程人员可以利用这个模型对PCB板上的电路系统进行SI、串扰、EMC以及时序的分析。

IBIS模型中包含的是一些可读的ASCII格式的列表数据。

IBIS模型简介

IBIS 模型简介

IBIS(Input/Output Buffer Information Specification)模型是一种基于 V/I 曲线的 对 I/O BUFFER 快速准确建模的方法,是反映芯片驱动和接收电气特性的一种国际标准,它提 供一种标准的文件格式来记录如驱动源输出阻抗、上升/下降时间及输入负载等参数,非常适 合做振荡和串扰等高频效应的计算与仿真。

IBI驱动器 和接收器的不同参数,但并不说明这些被记录的参数如何使用,这些参数需要由使用 IBIS 模 型的仿真工具来读取。欲使用 IBIS 进行实际的仿真,需要先完成以下四件工作:

(1)获取有关芯片驱动器和接收器的原始信息源; (2)获取一种将原始数据转换为 IBIS 格式的方法; (3)提供用于仿真的可被计算机识别的布局布线信息; (4)提供一种能够读取 IBIS 和布局布线格式并能够进行分析计算的软件工具。

IBIS 模型的分析精度主要取决于 I/V 和 V/T 表的数据点数和数据的精确度。由于基于 IBIS 模型的 PCB 板级仿真采用查表计算,因而计算量较小,通常只有相应的 SPICE 模型的 1/10 到 1/100。

采用 SPICE,产品推向市场的时间取决于获得模型,得到仿真结果的时间;在 IBIS 中, 主要是从 SPICE 仿真界果中建立模型。换句话说, IBIS 模型能够很容易的验证产品测试结 果(并且,如果有必要产生新的模型)。如果同样进行测量和模型验证的话,IBIS 模型能够 同 SPICE 具有同样的精度。IBIS 模型提供的信息需要 I/O 传输特性、而不是内部电路的信息。 IBIS 是为了满足信号完整性(SI)仿真的需要,其结果是 IBIS 模型具有信号完整性(signal integrity)分析所需要的信息,如在不同的负载下信号上升/下降时间。由于提取的水平如 此之高,所以模型不能够很容易的调整大小,但是对于信号完整性(SI)的应用不成问题。

PCB仿真

【摘要】随着微电子技术和计算机技术的不断发展,信号完整性分析的应用已经成为解决高速系统设计的唯一有效途径。

借助功能强大的Cadence公司SpecctraQue st仿真软件,利用IBIS模型,对高速信号线进行布局布线前信号完整性仿真分析是一种简单可行行的分析方法,可以发现信号完整性问题,根据仿真结果在信号完整性相关问题上做出优化的设计,从而缩短设计周期。

本文概要地介绍了信号完整性(SI)的相关问题,基于信号完整性分析的PCB设计方法,传输线基本理论,详尽的阐述了影响信号完整性的两大重要因素—反射和串扰的相关理论并提出了减小反射和串扰得有效办法。

讨论了基于SpecctraQucst的仿真模型的建立并对仿真结果进行了分析。

研究结果表明在高速电路设计中采用基于信号完整性的仿真设计是可行的, 也是必要的。

【关键字】高速PCB、信号完整性、传输线、反射、串扰、仿真AbstractWith the developmentofmicro-electronicstechnology and comp uter technology,application of signalintegrity analysis is th eonlyway to solve high-speed systemdesign.By dint ofSpecctraQuest which is a powerful simulation software,it’s a simpleand doable analytical method tomake use of IBIS modelto analyze signal integrity on high-speed signal lines before componentplacement and routing.Thismethod can findout signalintegrity problemand make optimizationdesignon interrelated problem ofsignal integrity.Thenthe design period i sshortened.In this paper,interrelated problemof signalintegrity,PCB design based on signal integrity,transmission lines basal principle are introduced summarily.The interrelated problem ofreflection an dcrosstalk whichare thetwoimportantfactorsthat influence signalintegrity is expounded.It gives effective methodsto reduce reflection and crosstalk.Theestablishment of emulationalmodel based onSpecctraQucstisdiscussed and theresultofsimulationisanalysed.The researchful fruit indicates it’s doable and necessaryto adoptemulationaldesignbased on signal integrity in high-speed electrocircuitdesign.Key WordsHigh-speed PCB、Signalintegrity、Transmission lines、reflect、crosstalk、simulation目录第一章绪论 (5)第二章Candence Allegro PCB简介……………………………………………..62.1 高速PCB的设计方法……………………………………………………..62.2SpecctraQuest InterconnectDesigner在高速信号印刷板设计中的应用.72.3 PCB板的SI仿真分析 (8)第三章信号完整性分析概论……………………………………………………123.1 信号完整性(SignalIntegrity)概念 (12)3.2 信号完整性的引发因素 (1)3.3信号完整性的解决方案………………………………………………….14第四章传输线原理 (15)4. 1 传输线模型 (15)4.2 传输线的特性阻抗 (1)第五章反射的理论分析和仿真………………………………………………..195.1反射形成机理…………………………………………………………….195.2反射引起的振铃效应…………………………………………………….205.3端接电阻匹配方式 (2)5.4多负载的端接…………………………………………………………….285.5反射的影响因素 (2)第六章串扰的理论分析和仿真 (34)6.1 容性耦合电流…………………………………………………………….346.2 感性耦合电流 (3)6.3 近端串扰………………………………………………………………….366.4 远端串扰………………………………………………………………….386.5 串扰的影响因素 (4)第七章结束语 (46)参考文献……………………………………………………………………………47致谢…………………………………………………………………………………47附录:A/D、D/A 采样测试板原理图和PCB板图……………………………...61第一章绪论随着信息宽带化和高速化的发展,以前的低速PCB已完全不能满足日益增长信息化发展的需要,人们对通信需求的不断提高,要求信号的传输和处理的速度越来越快,相应的高速PCB的应用也越来越广,设计也越来越复杂。

高速pcb设计和apsim仿真工具

高速PCB设计与APSIM仿真的协同工作流程

数据共享

迭代优化

通过将仿真结果反馈给设计工程师,实现高速PCB 设计与仿真的迭代优化,提高设计效率和质量。

APSIM仿真工具能够与高速PCB设计软件进 行数据共享,实现设计数据与仿真数据的无 缝对接。

协同工作

APSIM仿真工具与高速PCB设计软件之间的 协同工作流程能够缩短产品上市时间,提高 设计成功率。

信号完整性分析

在高速PCB设计中,信号完整 性是关键因素,需要进行仿真 分析以确保信号传输的稳定性

和可靠性。

电磁兼容性分析

随着信号速率的提高,电磁干 扰问题愈发突出,需要进行电 磁兼容性仿真以优化PCB布局

和布线。

热分析

高密度集成元器件在高速PCB 中产生大量热量,需要进行热

仿真以优化散热设计。

APSim仿真工具在高速PCB设计中的应用

高速PCB设计与APSIM仿真工具

目录

• 高速PCB设计基础 • APSim仿真工具介绍 • 高速PCB设计与APSIM仿真的结合 • 案例分析 • 结论与展望

01

高速PCB设计基础

PCB设计的基本概念

PCB

印刷电路板,是电子系统中的基础部件,用于实 现电子元器件之间的连接。

PCB设计

根据电路原理图和相关要求,利用设计软件进行 电路板的布局和布线的过程。

地弹

当信号线上的电流发生变化时, 地平面会产生电压波动,称为地 弹。减小地弹的方法包括增加接 地面、使用多层板等。

02

APSim仿真工具介绍

APSim仿真工具概述

APSim(Advanced Printed Circuit Board Simulator)是一款用于高速 PCB(印刷电路板)设计的仿真工具, 它能够模拟电路板中信号的传输、电 磁场和热传导等物理现象。

仪控系统PCB设计中IBIS模型的研究与应用

an d I BI S mo d e l s , a n d v e r i f i e s t h e e fe c t i v e n e s s o f t h e me t h o d. Th e r e s u l t s s h o w t h a t p r op er t e r mi n a t i o n , g r o u n d i s o l a t i o n

崩已经

串 扰 影 响 ,对 指 导 P CB 设计 具 有 积极 的现 实意 义 。 关 键 词 :I B I S ;反 射 ;串 扰 ; 仿 真 ;P C B 中 图分 类 号 :T P 2 1 2 / 2 1 7 文 献 标 志 码 :A

Re s e a r c h a nd a p p l i c a t i o n o f I BI S mo d e l i n PCB d e s i g n f o r I &C S y s t e m

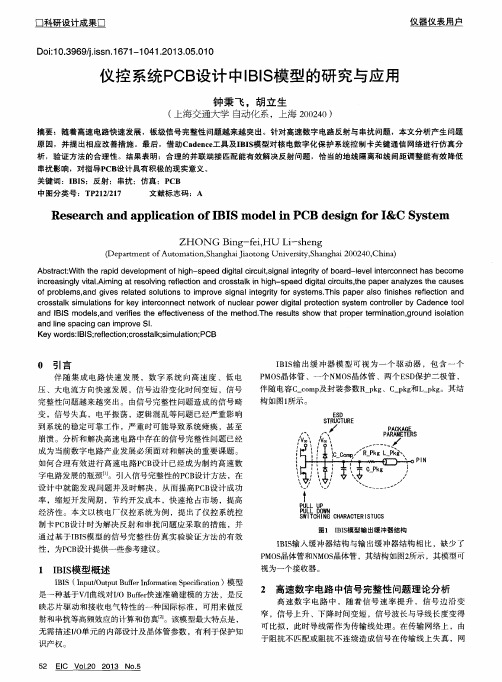

伴 随 电容C — c o m p 及封 装参数R — p k g 、C _ p k g 和L — p k g 。其结 构如图1 所示 。

完整性 问题越来 越突出 。由信号完整性 问题造成 的信号畸 变 ,信 号失真 ,电平振荡 ,逻辑混乱 等问题 已经严 重影响

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

. 作者简介: ,跃胜,, 年7 硕士, 授, 男6 3 月生, 副教 研究方向 为高速信号 传输理论与 板极E A技术、 D 计算机

图形学与可视化技术. 通讯地址: 407 湖南长沙国防科技大学计算机学院64 103 0 教研室 A de : h f pt Si al vO D f sTc. hnsaH nn 03P . i dr s c. C m u r . t U i f e e h C agh ,ua 407. C n s S o o e c, ' n . e n e , N 1 . ha R

模型V .版正在研究开发中。 4 0

22 I S IE模型的异同 . I S与 PC B

现在,电子器件主要用 S IE II PC 和 BS

S IE模型是以 ue 为中心的,该 bfr PC 模型常表示 b fr多输入或输出端中的一 ue f

明 工I模型的版本号、注释 、文件名、文 BS 件修定级、日期、来源 、 版权等信息。 ・ 器件管腿数据部分:也即器件描述部 分,它定义器件管腿与电模型的对应关系。

中国计算机学会

一一一一一一一一一一一 Xli # I t fX f

_

II 模型与高速PB C 设计分析 BS

IIM d ad h pe C A a s Hg- e P B li BS e n i S d n y s o l

曹跃胜. C o -hn a Y e eg uS ( 国防科技大学计算机学院 )

大多数 S 分析工具都可将 PB I C 板作ቤተ መጻሕፍቲ ባይዱ板材 料和布线几何形状的函数进行分析计算, 但 是得到一个能够反映板上元件、 连接器、电 缆等器件的好的分析模型却相对较难, BS II 模型可以帮助设计者在存在 S 约束的设计 i 中获取准确的信息以进行分析和计算。目 前,II 模型己 BS 得到 E A公司、半导体厂 D 商和系统开发者的一致认同, 并作为电子器 件的接 口数据格式得到广泛应用。

个;而II模型是以器件 (o pnn) BS cm oet 为

中 的, 模型描述物理器 ( mo n 心 其 件( p e ) c nt o 的所有管脚 (i) p 。作为性能方法构造的 n

II模型.它不用 I BS C制造商提供具有专利 属性的信息 ( 如:bfr u e 本身结构的详细描 述) ,而是把器件作为一个黑盒子 ( lk Ba c Bx o )来处理,只要给出在特定激励下的器 件响应就能生成 II 模型, BS 这一点对 I C制 造商来说尤其具有吸引力。 另外, P E 象SI C 模型一样,II BS模型也是可读的 A CI S I格 式,同时,II BS模型比 S IE模型更容易 P C 创建, 并且其模型中的数据还可以 通过模拟 结果或实验测量派生出。目 器件的II 前, BS 模型比SIE模型更易得到。 P C 通常逻辑设计师希望在设计过程中完 成信号完整性分析即容易又有效; 信号完 而 整性工程师则需要一个最正确 ( 最接近实 际) 的结论, 这样就要在容易 使用和快速获 得( 结论)这两方面作出折中。 D 软件 EA 开发商总结以上两方面的应用需求, 开发出 易 用、 快速,并且设计正确、 模拟与设计环 境集成一体的软件工具: 同时, 半导体供应 商为满足其客户的应用需求提供客户级的 应用模型, 但又不使其设计专利冒 着落入竞 争对手手中的风险:基于 II BS模型的信号 完整性分析就可以满足以上要求, II 并且 BS 模型最常见的应用也就在于进行信号完整 性分析。有比较显示,基于 II BS的模拟方 法, 其仿真的速度要比等效的SIE PC 模拟快

( NSI A-5- I 6 041 ,而 I I I I 6 6A. C 2 1- ) A E E BS

类功能, 振铃(nbc)过冲( eho 如: rga 、 i k o r ot vs ) 和 p --n时间。目 itp no i 前,市场上流行的几

种 S IE模型标准各具特色, PC 这就存在 P B C 上的器件可能来 自 不同供应商, 那么, 它们 S IE模型不相兼容的特点使得不可能在 P C 同一电路 (C )上一起模拟。 PB 另一种器件建摸方法是描述其性能

术与促进的开放论坛 ( I II Oe E B p A S n

Fr )也随之诞生。 om u 最开始使用的 II BS模型 V A版主要 I 用于 C S T L类型的 I B fr MO 和 T / u e 和仅 O 包含 II BS参数的内核集;随后,获得广泛 认可的 V .版,其 U 2 1 O类型得到了进一步 扩充 ( 增加了如:E L P C 和差分等) C . L E , 波形表 ( / 曲线)和管脚 (I )影像特 VT PN 征也得到了更多其他方面的扩张。II BS模 型 V .版也被批准作为 E /N I 5 21 I A S66标 A - 准。即信号完整性模型标准. ’ 目前,II BS模型已广泛被电路器件 ( ) 制造商提供, I C 同时, 越来越多的E A D 软件也支持 II BS模型的建摸与分析仿真。 19 年国际设计 自 97 动化大会( A ) II D C 上 BS 模型 V . 3 0被大会批准认可,并在现有 II BS 模型基础上对驱动器选择、二极管存储充 ( 放)电、封装模型扩展、电子板级描述 (B 、多台阶驱动器和串联元素等内容 ) ED 进行7扩充与增强。BS模型 V .版 19 II 3 2 97 年被批准由 建议标准 (I S 45) EA 57 升至为 P 美国国家标准 ( I- 6 ) EA6 - :次年 (00 5A 20 年) E 接受作为国际标准( C 11. 被I C I 604 ) E 2 当 前 使 用 的 国 际 标 准 是 V. 版 3 2

(col o pt Si c N tnl e i oD f sTcnl y ShooC m u r ne aoaU i rt f e e ho g) f e c , e i n s v y e n e o

摘 要: 本文简述了II棋型的发展历程, BS 分析了II模型与SIE BS PC 模型的异同, 具体介绍了II模 BS 型及其建立方法;并结合 E A技术和器件模型的发展, D 叙述了对于现代高速设计进行板级分析的必要性

两种方式构建模型。S IE模型源于美国 P C

UCBr l , . e ey 它描述电 . e k 路器件内 部的实际

连接与属性,主要用于模拟环境下的 I C设 计与验证。 半导体制造商通常可提供相应器 件的、 具有专利属性的 S IE模型 ( PC 这种模 型有时因涉及 I C制造商的设计专利而不便 提供) 。通过应用 S IE模型可以得到与实 PC 际物理结论差别不大的模拟结果, 但是, 如 果要进行完全的模拟, 即使是一个不太复杂 的电路,也要花相当长的运行时间。 SIE模型用于板级分析的限制就在 PC 于最初它并不是设计为用于传输线的模型, 因而也就不适合荃于 P B( C 印制板) 或其它 更大结构情况下的应用。 尽管, 现在许多公 司提供的基于 S IE模型的模拟器已经扩 P C 展了可处理更多先进结构的功能, 然而, 从 适配 S IE模型到具体应用常常导致非常 PC 长的模拟时间和难以 操作的结果。在 P B C 上, 应用 SIE模型验证一小组网线(e ) P C nt s 都难以实现, 更不用说进行整板或多板系统 的模拟。 此外, 大多数基于 SIE的 PC 模拟器 没有非常有用的用于分析或验证中的测量

(BS模型) II 。与描述器件实际电属性 ( IE不同, BS模型描述在特定负载条 S C) P II 件下 I C封装的驱动端和接受端的性能参数

与指标。BS模型标准并不说明 II II BS数据 怎样应用,也不包含应用该性能参数的算 法。任何 II BS兼容的模拟器都可以 用此数 据模型模拟器件, 而模型中的性能参数也是 在各种负载条件下的表现。 用性能方法构造 的II模型( BS 与实际电 气组成构造的S IE P C 模型相比) 可以 使模拟的速度更快, 这样通 过应用 II BS模型就可以分析一个更大的设 计或一个设计的更大部分. 这对于密度越来 越高的 P B及其需分析的关键网线的比 C 例 越来越多的高速设计领域来说,这是最基 本,也是最重要的优点。

很多 E A公司提供这类设计与分析工具。 D E A 分析工具要完成某个设计的信号完整 D 性 (I 分析, S) 必须提供相应 P B的结构 C 与材料、 信号的傲励和器件的模型等。 其中 器件模型描述器件的电气属性, 其参数的准 确性直接决定着分析结果的可信度。II BS

(O fr rc Sei ao) I B eIea pcitn 模型作 / u n fe f i t c 为国际标准用来分析验证板级信号完整性 (I S)问题,是高速 PB C 设计成功的关键。

E a : co utd. m i v a问ndeu n l s . c

2 I 模型的发展与应用 I S B

21 旧I . S模型回顾

早在 19 90年,当 Ie 公司尝试转换 nl t 需求迫切的 P I C 总线驱动器的时候, 就开始 建立基于Lt 表格方式的模型,并提供一 os u 种共同 格式作为部门间的外部联络。由 此, 在 Ie 公司强有力的动员下,业界致力创 nl t 建信号完整性模型的标准并最终将 II BS确 定为信号完整性的新标准。 此后, 部件厂商 都广泛采用 II BS格式,使得这一标准开始 流行, 并成为不断提速的高速设计能否进行 仿真与分析的关键。II 1 BS . 0版本于 19 93 年 6月推出,随后又于 19 年 8 93 月推出改 进的 II 1 版本,同时,致力于 II B S 1 . BS技

K y od : IM dl i - e DsnB a Lvl liSIE dl D Tcnl y ew rs I S e Hg S e eg, r eeA a s, M e E A ho g B o , p d i o d n y s PC o , e o h