CMOS石英晶振最优起振条件分析与电路设计(增益和nyquist)

石英晶体振荡电路设计

石英晶体振荡电路设计摘要:不同的制造商提供各种形状与大小的石英晶体,其性能指标也各不一样。

这些指标包括谐振频率、谐振模式、负载电容、串联阻抗、管壳电容以及驱动电平。

本应用笔记帮助读者理解这些指标参数,并允许用户根据应用选择合适的晶体以及在MAX1470超外差接收机电路应用中获得最佳效果。

不同的制造商提供各种形状与大小的石英晶体,其性能指标也各不一样。

这些指标包括谐振频率、谐振模式、负载电容、串联阻抗、管壳电容以及驱动电平。

本篇应用笔记帮助读者理解这些指标参数,并允许用户根据应用选择合适的晶体以及在MAX1470超外差接收机电路应用中获得最佳效果。

晶体的等效电路见图1。

图中包括了动态元件:电阻Rs、电感Lm、电容Cm和并联电容Co。

这些动态元件决定了晶体的串联谐振频率和谐振器的Q值。

并联电容Co是晶体电极、管壳和引腿作用的结果。

图1. 晶体模型以下详细给出主要的性能指标。

谐振频率晶体频率可以根据接收频率指定。

由于MAX1470使用低端注入的中频,晶体频率可由下式给出(单位为MHz):对于315MHz应用,晶体的频率可为,而在应用时需要晶体。

仅基频模式的晶体需要指定(无需泛音)。

谐振模式晶体具有两种谐振模式:串联(两个频率中的低频率)和并联(反谐振,两个频率中的高频率)。

所有在振荡电路中呈现纯阻性时的晶体都表现出两种谐振模式。

在串联谐振模式中,动态电容的容抗Cm、感抗Lm相等且极性相反,阻抗最小。

在反谐振点。

阻抗却是最大的,电流是最小的。

在振荡器应用中不使用反谐振点。

通过添加外部元件(通常是电容),石英晶体可振荡在串联与反谐振频率之间的任何频率上。

在晶体工业中,这就是并联频率或者并联模式。

这个频率高于串联谐振频率低于晶体真正的并联谐振频率(反谐振点)。

图2给出了典型的晶体阻抗与频率关系的特性图。

图2. 晶体阻抗相对频率负载电容和可牵引性在使用并联谐振模式时负载电容是晶体一个重要的指标。

在该模式当中,晶体的总电抗呈现感性,与振荡器的负载电容并联,形成了LC谐振回路,决定了振荡器的频率。

基于CMOS工艺的晶体振荡器设计及频率校准的研究的开题报告

基于CMOS工艺的晶体振荡器设计及频率校准的研究的开题报告一、研究背景和意义晶体振荡器是一种用于产生稳定的电信号或时钟信号的电子设备,广泛应用于数字电路、无线通信、计算机系统等领域。

当前,晶体振荡器具有体积小、功耗低、频率稳定等优点,成为了电子产品中必不可少的核心部件之一。

基于CMOS工艺的晶体振荡器是当前的研究热点之一,其具有低功耗、波形纯净和可集成等优点,能够满足微型化、集成化和便携化的发展需求。

在此基础上,如何进行频率校准也成为了当前研究中的重要问题。

因此,本研究旨在基于CMOS工艺的晶体振荡器设计并探究其频率校准的方法,为电子产品的应用和制造提供更加可靠和稳定的时钟信号,具有重要的研究价值和应用前景。

二、研究内容和目标本研究的主要内容和目标包括:1. 分析现有的晶体振荡器的结构和特点,研究基于CMOS工艺的晶体振荡器的设计原理和方法;2. 设计并实现基于CMOS工艺的晶体振荡器电路,分析其性能和特点;3. 探究基于CMOS工艺的晶体振荡器的频率校准方法,分析频率误差产生的原因,提出解决方案;4. 实验验证晶体振荡器的频率校准方法的有效性和可行性,以实验数据为依据对研究成果进行评估。

通过以上研究,旨在设计出具有更优性能和更高稳定性的CMOS晶体振荡器,并探究其频率校准方法,为晶体振荡器的性能提升和制造提供技术支持。

三、研究方法和步骤本研究的方法和步骤主要包括:1. 研究文献资料的综述和分析,了解晶体振荡器的基本原理和当前研究状况;2. 设计并实现基于CMOS工艺的晶体振荡器电路,进行仿真和测试,分析其性能和特点;3. 分析和实验验证晶体振荡器的频率误差产生的原因,提出并验证频率校准方案的有效性和可行性;4. 根据实验结果和分析,对研究成果进行总结和评估,提出进一步的改进和优化方法。

四、预期成果本研究的预期成果包括:1. 设计出具有更高稳定性和更优性能的基于CMOS工艺的晶体振荡器电路;2. 探究基于CMOS工艺的晶体振荡器的频率校准方法,提出有效和可行的解决方案;3. 实验验证频率校准方案的有效性和可行性,为晶体振荡器的制造提供技术支持和指导;4. 发表相关研究论文,为晶体振荡器的研究和应用提供新思路和新技术。

CMOS石英晶振最优起振条件分析与电路设计(精)

CMOS 石英晶振最优启振条件分析与电路设计摘要 :本文基于自动控制原理,对 Pierce CMOS晶振电路的启振条件作了详细的分析, 对电路中影响石英晶振起振的各种寄生参数作了深入研究,结合 Matlab 对理论分析作了验证,并以 15Mhz 晶振为例,设计了一个保证晶振可靠起振的最优反相器,最后通过 HSPICE 模拟进一步验证了理论分析的正确性。

关键词:CMOS ;石英晶振;启振条件The optimum start-up conditions analysis and Circuit design of CMOS Crystal Oscillator Jiang Renjie(School of Computer Science, National University of Defense TechnologyAbstract :This paper investigates the start-up conditions in Pierce CMOS crystal oscillator base upon the auto-control principle . The effect of oscillator start-up conditions caused by crystal circuit parasitics has been analyzed theoretically in detail. The result of theoretical analysis is verified using Matlab, and the optimum inverter which can guarantee circuit oscillate reliably has been designed for the 15Mhz crystal oscillator as an example. Finally, using Hspice simulation, the correctness of the theoretical analysis is verified further.Key words:CMOS, Crystal oscillator, Start-up conditionI . 引言在现代电子系统中, Pierce CMOS 晶振电路,作为时钟发生器,得到越来越广泛的应用 [1][2][8][10]。

石英晶体振荡电路.pptx

+VOH

vI

VT-

O VT+

-VOL

第15页/共32页

通过上述几种电压比较器的分析,可得出如下结论:

(1)用于电压比较器的运放,通常工作在开环或正反馈状态和非线性区,其输出电 压只有高电平VOH和低电VOL两种情况。

(2)一般用电压传输特性来描述输出电压与输入电压的函数关系。

(3)电压传输特性的关键要素 输出电压的高电平VOH和低电平VOL 门限电压 输出电压的跳变方向

振荡周期

O

T4R4CU om4R1R4C

t

UZ

R2

Vom

第26页/共32页

9.8.3 锯齿波产生电路

第27页/共32页

一、电路组成

充放电时间常数 不同

第28页/共32页

二、工作原理

vO1

VZ

T2

T1

O t

VZ vO

Vom

O t

Vom

T

第29页/共32页

三、输出幅度和振荡周期

Uom

R1 R2

voVZvo 3 vo0时vo3V Z 29V vo0时vo3V Z 29V VT 9V33V VT -9V33V

第17页/共32页

• 集成电压比较器

• 集成电压比较器比集成运算放大器的开环增益低、 失调电压大、共模抑制比小,因而它的灵敏度往往 不如用集成运算放大器构成的比较器高,但由于集 成电压比较器通常工作在两种状态之一,因此不需 要频率补偿电容,也就不存在像集成运算放大器那 样因加入补偿电容引起转换速率受限。

UZ

uO1

UZ

T2

T1

T1

2R1RW C R2

O

UZ

晶振电路的设计原理

晶振电路的设计原理今天来聊聊晶振电路的设计原理。

咱先从生活中的一个现象说起吧。

不知道你有没有留意过摆钟,摆钟下面那个钟摆一下一下很有规律地摆动,滴答滴答地计时。

晶振电路就有点像这个摆钟的机芯,起着提供精准节拍,让整个系统有条不紊运行的作用呢。

晶振,就是晶体振荡器的简称。

通俗来讲,它能以非常精准且稳定的频率产生振动,这个频率就像是音乐里的节拍一样,在电子设备里十分关键。

我一开始接触晶振电路的时候,心里就直犯嘀咕,这么个小小的元件,是怎么做到这么精确的呢?打个比方,晶振就像是一个训练有素的鼓手,它能一直稳定、精确地敲出同一个节奏。

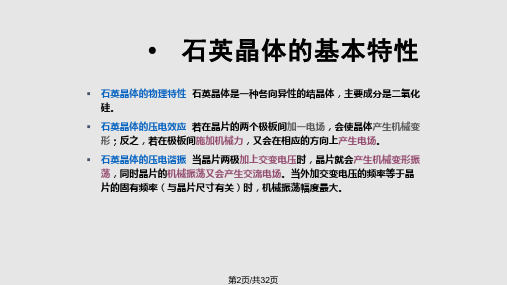

在晶振电路里有一个石英晶体,这是最重要的部分。

石英晶体具有一种很神奇的特性,叫做压电效应。

就好比是你轻轻按一下那种有弹性的东西,它会发生微小的形变,反过来,当对它施加电压的时候,它也会产生振动。

这个振动的频率非常稳定,比咱们人工能控制的要准确得多。

这就要说到晶振电路的设计了。

在设计的时候,得考虑好多因素,就像盖房子得考虑地基稳不稳、结构牢固不牢固一样。

首先,要根据电路需要的频率来选择合适的晶振。

比如说我们常见的一些电子产品,像手机里的晶振频率可能是几十兆赫兹,不同功能模块可能需要不同的频率晶振协同工作。

另外,电路里的电容、电阻等元件的取值也很讲究。

它们就像鼓手旁边的调音师,调试这个节奏的稳定性。

电容的值不合理,就可能导致这个“鼓手”敲出来的节拍不准。

在实际应用中,晶振电路无处不在。

就拿电脑主板来说吧,上面的晶振电路为CPU、各种芯片以及接口等提供时钟信号。

如果晶振电路出了问题,电脑可能就出现死机、程序无法运行等各种乱七八糟的问题。

老实说,我还在继续学习晶振电路的设计原理。

有时候也会遇到一些很困惑的现象,比如温度对晶振频率的影响。

温度可能会让石英晶体的参数发生一些细微变化,就像天气太热或太冷的时候,鼓手的状态可能也会有一点点不同。

这个时候可能就需要一些更特殊的设计或者矫正措施来保证晶振电路的准确性,不过这部分我还不是特别精通呢。

石英晶体振荡电路1正弦波振荡电路

正弦波振荡电路能产生正弦波信号,它是在 放大电路的基础上加上正反馈网络构成的。为了 获得单一频率的正弦波,正弦波振荡电路还必须 包含选频网络。为了得到稳定的等幅振荡信号, 正弦波振荡电路还要有一个稳幅环节,它可以由 晶体管的非线性作用来实现。

因此,正弦波振荡电路由放大电路、正反馈 网络、选频网络、稳幅环节组成。

3

1

j(

0 )

0

5.1 正弦波振荡电路

5.1.2 RC正弦波振荡器

1.RC串并联网络的选频特性

0

,

F

1

32 ( 0 )2

f arctg 0 3

0

当 f 0时,

F

Vf Vo

1 3

f 0

5.1 正弦波振荡电路

满足振荡的相位平衡条件。

串联型石英晶体振荡器

5.2 非正弦波产生电路

5.2.1 矩形波产生电路

1.滞回比较器

U 0 U Z

5.2 非正弦波产生电路

5.2.1 矩形波产生电路

1.滞回比较器

UT

R2 R2 R3

UZ

U i>UT 时,U 0 U Z

UT

R2 R2 R3

UZ

5.1 正弦波振荡电路

5.1.3 LC正弦波振荡器

5.三点式振荡器构成法则

由AF 1得: X 1 、X 2 为同类电抗, X 3 与 X 1 、X 2

为相反种类的电抗。

5.1 正弦波振荡电路

5.1.3 LC正弦波振荡器

〖例7-3〗试用相位平衡条件法判断如图所示电路能否振荡. 解:断开反馈到放大器的输入端点, 假设在输入端加入一正的瞬时信号, 用瞬时极性法判定反馈信号的极性, 若反馈信号与输入信号同相,则满 足相位条件,电路能振荡;否则电 路不能振荡。 通过分析,如图所示电路能振荡。

石英晶体振荡器设计报告

石英晶体振荡器设计报告张炳炎09微电03 目录1 设计要求2 设计方案论证a.电路形式的选取b.参数的设计、估算c. 设计内容的实现3 电路的工作原理4 晶体振荡器的特点5 电路设计制作过程中遇到的主要问题及解决方法、心得和建议6 参考文献7 附录1设计要求(1)晶体振荡器的工作频率在100MHZ以下(2)振荡器工作可调,反馈元件可更换(3)具有三组不同的负载阻抗(4)电源电压为12V(5)在10K负载上输出目测不失真电压波形Vopp>=4V,振荡器频率读出5为有效数字2设计方案论证a.电路形式的选取: 串联型石英晶体振荡器串联型石英晶体振荡器交流等效电路石英晶体的物理和化学性能都十分稳定,等效谐振回路具有很高的标准性,Q值很高,对频率变化具有极灵敏的补偿能力具有.利用石英晶体作为串联谐振元件,在谐振时阻抗接近于零,此时正反馈最强,满足振荡条件.因此,电路的振荡频率和频率稳定度都取决于石英晶体的串联谐振频率.b.参数的设计、估算选用石英晶体(6M)作为串联谐振元件,提高振荡器的标准性,三极管为高频中常用的小功率管9018,作为放大电路的主要器件,选用阻值较大的可调电阻Rp(50k)来调节电路的静态工作点,使输出幅值达到最大而不失真,在LC 组成的谐振回路加可变电容(100p)调节谐振频率。

三组负载分别为1k、10k、110k,用来比较对振荡器频率及幅值的影响。

c. 设计内容的实现○1输入电源电压12V,测试电路的静态工作点, 三极管Vbe>0.7v,Vc>Vb>Ve,三极管工作在放大区。

○2输出端接上示波器,观察到正弦波,通过改电位器、可变电容使输出的幅值达到最大。

○3改变负载值,测量不同负载下电路输出的频率及幅值大小。

可知,负载几乎对频率没有影响,因为输出的频率主要由石英晶体决定,而幅值随着负载的减小而略微下降,当空载时幅值最大。

3 电路的工作原理石英晶体振荡器总原理图如上图,C6,C7和L2组成π型滤波器,对外部直流电源进行滤波而只通过直流量,防止其对电路产生干扰。

一种低功耗CMOS晶振电路设计

一种低功耗CMOS晶振电路设计彭伟娣;张文杰;谢亮;金湘亮【摘要】A CMOS inverter of two-transistors has two transistor gates coupled together by a coupling capacitor.DC gate bias is supplied to each transistor through high value resistors.The P-channel transistor is biased to a threshold below the power and the N-channel transistor is biased to a threshold above ground.The biasing voltage are developed through the use of a current mirror so that the biasing is independent of processing variables and temperature.A crystal oscillator created using such an inverter and biasing will operate at voltage substantially below sum of P and N thresholds and at a current level about one-fifth of that of a conventional CMOS oscillator.This low power CMOS crystal oscillator circuit was designed based on MXIC's 0.5 μm CMOS process,the current consumption of the whole circuit is under 750 nA.%在组成反相器的两个晶体管的栅端添加一个串联电容,直流通过连接在反相器内部的大电阻偏置这两个晶体管,P管被低于电源电压一个阈值的电压偏置,N管被高于低电压一个阈值的电压偏置,偏置电压通过电流镜镜像,因此受温度和工艺的影响较低.一种低功耗CMOS晶体振荡电路利用上述反相器,它的开启电压低于P管和N管的阈值之和,整体电路消耗的电流大概为传统电路的1/5.此晶振电路基于MXIC 0.5μm仿真模型验证实现,整体电路消耗的功耗电流小于750 nA.【期刊名称】《电子器件》【年(卷),期】2013(036)003【总页数】4页(P336-339)【作者】彭伟娣;张文杰;谢亮;金湘亮【作者单位】湘潭大学材料与光电物理学院,湖南湘潭411105;湘潭大学材料与光电物理学院,湖南湘潭411105;湘潭大学材料与光电物理学院,湖南湘潭411105;湘潭大学材料与光电物理学院,湖南湘潭411105【正文语种】中文【中图分类】TN431随着信息科学技术的迅猛发展,低功耗设计成为集成电路发展的趋势。

一种低功耗CMOS晶体振荡器的设计

一种低功耗CMOS晶体振荡器的设计

孙磊

【期刊名称】《中国集成电路》

【年(卷),期】2016(0)5

【摘要】本文提出一种新的低功耗晶体振荡器(Low Power Crystal Oscillator,简称LPCO)设计.本设计中的低功耗晶体振荡器的增益可选,在石英晶体应用时,使用大增益模式启动晶体,晶体触发后,经过稳定时间切换到小增益模式,在有源晶体应用时,使用小增益模式.经流片验证,低功耗晶体振荡器的功能和性能满足要求,功耗只有2 mA.它的ESD防护能力超过4 kV,Latch-up防护能力超过+/-100 mA.

【总页数】8页(P15-22)

【作者】孙磊

【作者单位】北京中电华大电子设计有限责任公司,北京100102

【正文语种】中文

【相关文献】

1.一种低功耗CMOS过温保护电路的设计 [J], 李树镇;冯全源

2.一种低功耗射频CMOS电荷泵锁相环的设计 [J], 刘忠来

3.一种用于CMOS图像传感器的高速高精度低功耗LVDS驱动器设计 [J], 李闯泽; 韩本光; 何杰; 吴龙胜

4.一种超低功耗的全CMOS基准电压源设计 [J], 王梓淇;王永顺;陈昊

5.一种工作于亚阈值区的低功耗CMOS晶体振荡器 [J], 孟新;马成炎;叶甜春;殷明因版权原因,仅展示原文概要,查看原文内容请购买。

低压低功耗CMOS振荡器的研究与设计

摘要21世纪被称为信息时代,信息和通信技术革命从上世纪开始方兴未艾,以电子技术为基础的无线电通信技术和信息技术已经逐步走向成熟,电子工业的进步给人类生活方式带来了天翻地覆的变化。

新一代的通信技术需要更大带宽的基带芯片,大数据时代处理更多的数据需要更强运算能力的处理芯片,这对集成电路的发展提出了新的要求。

作为电子设备中时钟源信号产生的重要模块,低压低功耗的高精度振荡器一直是国内外学者研究的重点之一。

本论文对工艺、电源电压和温度波动如何影响振荡器输出频率展开研究并提出提高时钟精度的方法,提出了两种不同结构的低功耗的张弛振荡器,在-40-80℃的温度范围内产生32.768kHz目标频率,两种振荡器输出时钟具有较小的温漂和较高的电源线性。

振荡器的性能如下:(1)基于反相器方案的张弛振荡器提出了一种全MOS(Metal Oxide Semiconductor)管PTAT(Proportional to Absolute Temperature)电流源,利用多级反相器和RC延迟单元构成反馈回路作为振荡器核心电路,通过局部电压调整电路为振荡器核心电路供电,实现电源与振荡器核心电路隔离,降低了电源电压波动对振荡器输出频率的影响,此外偏置电路中使用MOS管阈值电压的温度特性对反相器延迟时间的温度波动进行补偿,降低了温度对振荡器温漂特性的影响。

室温下,振荡器输出频率33.769kHz,相对频率变化在-0.049%-0.353%之间,在-40-40℃温度范围内,相对频率变化不超过±0.62‰;(2)基于比较器方案的张弛振荡器使用14nA低功耗PTAT电流源提供偏置,为提高时钟信号精度,对核心电路中电阻进行微调,并进行正负温度系数电阻匹配以降低电阻温漂,同时采用温度系数较小的MOM电容。

为了改善振荡器输出波形,比较器输出级后加入数字逻辑单元,对振荡器波形进行整形和分频,产生我们需要的目标频率。

室温下,PTAT偏置电流源输出14nA,振荡器在1V电源电压下功耗约130nW,产生32.768kHz稳定的时钟信号输出,在-40-80℃范围内温漂为0.14%/℃;电源电压在0.9-1.5V电压范围内稳定输出。

石英晶体振荡电路

石英晶体振荡电路石英晶体谐振器, 简称石英晶体, 具有非常稳定的固有频率。

对于振荡频率的稳定性要求高的电路, 应选用石英晶体作选频网络。

一、石英晶体的特点将二氧化硅(SiO2)结晶体按一定的方向切割成很薄的晶片, 再将晶片两个对应的表面抛光和涂敷银层, 并作为两个极引出管脚, 加以封装, 就构成石英晶体谐振器。

其结构示意图和符号如右图所示。

1.压电效应和压电振荡在石英晶体两个管脚加交变电场时, 它将会产有利于一定频率的机械变形, 而这种机械振动又会产生交变电场, 上述物理现象称为压电效应。

一般情况下, 无论是机械振动的振幅, 还是交变电场的振幅都非常小。

但是, 当交变电场的频率为某一特定值时, 振幅骤然增大, 产生共振, 称之为压电振荡。

这一特定频率就是石英晶体的固有频率, 也称谐振频率。

2.石英晶体的等效电路和振荡频率石英晶体的等效电路如下图(a)所示。

当石英晶体不振动时, 可等效为一个平板电容C0, 称为静态电容;其值决定于晶片的几何尺寸和电极面积, 一般约为几到几十皮法。

当晶片产生振动时, 机械振动的惯性等效为电感L, 其值为几毫亨。

晶片的弹性等效为电容C, 其值仅为0.01到0.1pF, 因此, C<<C0。

晶片的磨擦损耗等效为电阻R, 其值约为100Ω, 理想情况下R=0。

当等效电路中的L、C、R支路产生串联谐振时, 该支路呈纯阻性, 等效电阻为R, 谐振频率谐振频率下整个网络的电抗等于R并联C0的容抗, 因R<<ω0C0, 故可近似认为石英晶体也呈纯阻性, 等效电阻为R。

当f<fs时, C0和C电抗较大, 起主导作用, 石英晶体呈容性。

当f>fs 时, L、C、R支路呈感性, 将与C0产生并联谐振, 石英晶体又呈纯阻性, 谐振频率石英晶体基础知识1、石英晶体的应用:a、石英钟 b、温度计 c、压力指示器(频率与应力)d、加速度计2、晶体的自然面及解理面平行于原子面3、石英的机械、电气、化学和温度等综合性能,都满足需要电气通讯领域。

石英晶体正弦波振荡器设计

目录第一章振荡器的基本常识 (1)第一节振荡器的分类 (1)第二节振荡产生的原理 (1)一自激振荡的产生 (1)二产生振荡的条件 (2)第三节起振和稳幅 (3)一起振过程 (3)二振幅的稳定 (3)第四节正弦波振荡器 (4)第五节频率稳定度 (5)第二章石英晶体 (6)第一节石英晶体的基本特性 (6)一石英晶体的基本结构 (6)二压电效应 (6)第二节石英晶体等效电路和振荡电路 (7)第三章12MHz石英晶体正弦波振荡器 (10)第一节电路的选择 (10)第二节石英晶体振荡器设计 (10)一主要技术指标 (10)二设计说明........................................... (10)(一)选择电路............................................ .10 (二)选择晶体管和石英晶体. (11)(三)确定直流工作点并计算偏置电路元件参数 (11)(四)求C1\C2\Ct的电容值 (12)心得体会 (13)参考文献 (13)第一章振荡器的基本常识第一节振荡器的分类震荡器(Oscillator)是一种能量转换装置。

它的能量来源一般是直流形式(振荡器电路的直流供电电源)。

经过振荡器转换后,此直流能量转换为一定频率、一定幅度和一定波形的交流能量输出。

这种电能的“转换”过程被称作“振荡”(Oscillation)。

振荡器的作用是产生特定的输出信号,因此也常常被称为信号发生器(signal creator)。

振荡器的类型繁多,按照振荡过程是否依赖于外部激励信号的参与,可以分为他激振荡器和自激振荡器;按照波形分类有正弦波振荡器和非正弦波振荡器;按照振荡器振荡频率的高低,可以分为低频振荡器、高频振荡器、超高频振荡器等;按照振荡器的选频元件分类,则有RC振荡器、LC振荡器、石英晶体振荡器等。

第二节振荡产生的原理一自激振荡的产生无需外加激励就能产生特定波形的交流输出信号,这种振荡电路称为自激振荡器。

石英晶体振荡电路

第6章 波形发生器

图6-18 串联型晶体振荡电路

晶体接在VT1、VT2组成的正反馈电路中。当振荡频率 等于晶体的串联谐振频率fs时,石英谐振器的阻抗最小,且 为纯阻性,因此反馈最强,且相移为0,电路满足自激振荡

条件,振荡频率为fs。

6

6.4 石英晶体振荡电路

第6章 波形发生器

1

6.4 石英晶体振荡电路

第6章 波形发生器

6 .4.2 石英晶体的基本特性与等效电路

1.石英晶体的压电效应

石英晶体所以能做振荡电路是基于它的压电效应,从 物理学中知道,若在晶片的两个极板间加一电场,会使晶 体产生机械变形;反之,若在极板间施加机械力,又会在 相应的方向上产生电场,这种现象称为压电效应。如在极 板间所加的是交变电压,就会产生机械变形振动,同时机 械变形振动又会产生交变电场。一般来说,这种机械振动 的振幅是比较小的,其振动频率则是很稳定的。但当外加 交变电压的频率与晶片的固有频率(决定于晶片的尺寸)相等 时,机械振动的幅度将急剧增加,这种现象称为压电谐振, 因此石英晶体又称石英晶体谐振器。

7

6.4 石英晶体振荡电路

6 .4.1 正弦波振荡电路的频率稳定问题

第6章 波形发生器

振荡频率稳定度,是指振荡器在一定时间间隔(例如1 天、1周、1个月等等)和温度下,振荡频率的相对变化量。 此频率相对变化量可用下式表示

Sf

f

f0fLeabharlann f0 f0式中,Sf为振荡频率稳定度,f0为振荡器标称频率, f是经过一定时间间隔后振荡器的实际振荡频率。Sf值 越小,振荡器的振荡频率稳定度就越高。

2

6.4 石英晶体振荡电路

2.石英晶体的符号和 等效电路

石英晶体振荡器设计参考

石英晶体振荡器设计参考石英晶体振荡器设计参考振荡器是一种将直流电能转换为具有一定频率的交流电能的装置,而将石英晶体谐振器(以下简称晶体)作为频率控制元件的振荡器就叫做石英晶体振荡器(以下简称晶振)。

由于晶体的机械品质因数(Q值)可达到105~106数量级,其相移随频率的变化△Φ/△ω很大,故晶振有很高的频率稳定度,约在10-4~10-12的范围。

目前晶振被广泛应用到军、民用通信电台、微波通信设备、程控电话交换机、无线电综合测试仪、移动电话发射台、高档频率计数器、GPS、卫星通信、遥控移动设备等。

目前晶振有以下八类:普通晶体振荡器(XO)、压控晶体振荡器(VCXO)、温度补偿晶体振荡器(TCXO)、恒温晶体振荡器(OCXO)、温补压控晶体振荡器(TCVCXO)、恒温压控晶体振荡器(OCVCXO)、微机补偿晶体振荡器(MCXO)和铷-晶体振荡器。

其中,温度补偿晶体振荡器包括模拟温补、数字温补、模拟-数字混合温补和单片机温补的晶体振荡器。

以下根据晶振的分类和应用,对晶振设计时需考虑的问题做一下简单介绍。

1.晶体的选用(1)切型的选取晶体的切型有AT、BT、CT、DT、ET、FT、ST、x+5、AC、BC、FC、LC、SC等,每种切型都有各自的特性,而目前在晶振中应用最多的切型是AT切和SC切。

由于AT切石英片的尺寸合适,便于加工,体积可以做的很小,在较宽的温度范围内具有良好的频率温度特性(在-55℃~85℃范围内可达到±25×10-6),并有较高的压电活性等优点,从而得到最广泛的应用。

它是石英谐振器中最重要的一种切型,频率范围约为800kH z~350MHz,采用离子刻蚀技术,其基音频率可达到1GHz左右。

目前的温度补偿晶体振荡器基本都是采用的AT切型晶体。

SC切晶体是一种双旋转切型晶体。

由于它具有应力补偿和热瞬变补偿特性,故其频率与热应力及电极应力在表面内所产生的应力无关。

因此,这种切型具有老化小、相位噪声低、短期频率稳定性好、热滞效应小及开机特性好等优点,特别适用于高稳定晶体振荡器。

一种低功耗快速起振晶体振荡器

一种低功耗快速起振晶体振荡器

武振宇;马成炎;叶甜春

【期刊名称】《微电子学》

【年(卷),期】2010()1

【摘要】基于CSMC0.5μm40VBCD工艺,设计了一种32.768kHz的晶体振荡器电路。

通过Matlab分析振荡条件,以指导电路设计;通过自动增益控制环路,使振荡器的起振时间低至206ms;由微电流的跨导放大器实现了集成电路中的大电阻,用在反馈电阻和滤波器中;环路稳定后,振荡器核心电路的电流仅为195nA,同时,该电路还提供占空比为46%的方波输出。

【总页数】5页(P45-49)

【关键词】晶体振荡器;自动增益控制;起振时间

【作者】武振宇;马成炎;叶甜春

【作者单位】中国科学院微电子研究所;杭州中科微电子有限公司

【正文语种】中文

【中图分类】TN43

【相关文献】

1.一种用于射频调谐器的低相位噪声低功耗晶体振荡器 [J], 唐路;王志功;曾贤文;徐建

2.一种低功耗CMOS晶体振荡器的设计 [J], 孙磊

3.低功耗快速起振晶体振荡器的应用探讨 [J], 谢志国

4.一种低功耗快速起振晶体振荡器分析 [J], 刘轶琼

5.一种自动振幅控制的快速起振晶体振荡器设计 [J], 秦缤;李天望

因版权原因,仅展示原文概要,查看原文内容请购买。

石英晶体振荡器

C0

C

L

R

X

0

X>0为感性区域

X<0为容性区域

s

p

C0— 两金属片间电容 C — 振动弹性,等效于电容 L — 晶体等效质量惯性,等 效于电感 R — 振动的磨擦损耗,等效 于电阻R

串联支路的谐振频率

并联回路的谐振频率

在上式中令X

1、石英晶体简介

继续

(1)石英晶体的压电效应

石英晶体的符号

本页完

若在晶片的两极板间加一电场,会使晶体产生机械变形;反之若在极板间施加机械力,又会在相应的方向上产生电场,这种现象称为压电效应。

若在极板间所加的是交变电场,就会产生机械变形振动,同时机械变形振动又会产生交变电场。

返回

学习要点

01

本 节 学 习 要 点 和 要 求

02

晶振器等效电路的工作原理

03

晶体振荡电路的工作过程

04

晶体谐振器应用在电路中的串、并联正反馈

05

返回

06

晶体振荡器

01

03

05

02

04

石英晶体的等效电路及特性

06

返回

晶体振荡电路主页

/CONTENTS

晶体振荡器

1、石英晶体简介 (1)石英晶体的压电效应

由晶体的频率特性知,电路中 f < fs 和 f > fp的频率,晶体呈现电容性质的阻抗,此时等效于一只电容器。

显然由C1、C2 、C3和C组成的电路不是选频回路,不可能有谐振频率。所以这些频率受到衰减。

并联晶体振荡器

X>0为感性区域

X<0为容性区域

X

晶振选则和设计概要

晶体振荡器(晶振)的工作原理石英晶体振荡器是高精度和高稳定度的振荡器,被广泛应用于彩电、计算机、遥控器等各类振荡电路中,以及通信系统中用于频率发生器、为数据处理设备产生时钟信号和为特定系统提供基准信号。

一、石英晶体振荡器的基本原理1、石英晶体振荡器的结构石英晶体振荡器是利用石英晶体(二氧化硅的结晶体)的压电效应制成的一种谐振器件,它的基本构成大致是:从一块石英晶体上按一定方位角切下薄片(简称为晶片,它可以是正方形、矩形或圆形等),在它的两个对应面上涂敷银层作为电极,在每个电极上各焊一根引线接到管脚上,再加上封装外壳就构成了石英晶体谐振器,简称为石英晶体或晶体、晶振。

其产品一般用金属外壳封装,也有用玻璃壳、陶瓷或塑料封装的。

2、压电效应若在石英晶体的两个电极上加一电场,晶片就会产生机械变形。

反之,若在晶片的两侧施加机械压力,则在晶片相应的方向上将产生电场,这种物理现象称为压电效应。

如果在晶片的两极上加交变电压,晶片就会产生机械振动,同时晶片的机械振动又会产生交变电场。

在一般情况下,晶片机械振动的振幅和交变电场的振幅非常微小,但当外加交变电压的频率为某一特定值时,振幅明显加大,比其他频率下的振幅大得多,这种现象称为压电谐振,它与LC回路的谐振现象十分相似。

它的谐振频率与晶片的切割方式、几何形状、尺寸等有关。

3、符号和等效电路当晶体不振动时,可把它看成一个平板电容器称为静电电容C,它的大小与晶片的几何尺寸、电极面积有关,一般约几个PF到几十PF。

当晶体振荡时,机械振动的惯性可用电感L来等效。

一般L的值为几十mH 到几百mH。

晶片的弹性可用电容C来等效,C的值很小,一般只有0.0002~0.1pF。

晶片振动时因摩擦而造成的损耗用R来等效,它的数值约为100Ω。

由于晶片的等效电感很大,而C很小,R也小,因此回路的品质因数Q很大,可达1000~10000。

加上晶片本身的谐振频率基本上只与晶片的切割方式、几何形状、尺寸有关,而且可以做得精确,因此利用石英谐振器组成的振荡电路可获得很高的频率稳定度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CMOS石英晶振最优启振条件分析与电路设计摘要:本文基于自动控制原理,对Pierce CMOS晶振电路的启振条件作了详细的分析,对电路中影响石英晶振起振的各种寄生参数作了深入研究,结合Matlab对理论分析作了验证,并以15Mhz晶振为例,设计了一个保证晶振可靠起振的最优反相器,最后通过HSPICE模拟进一步验证了理论分析的正确性。

关键词:CMOS;石英晶振;启振条件The optimum start-up conditions analysis and Circuit design of CMOS Crystal OscillatorJiang Renjie(School of Computer Science, National University of Defense Technology)Abstract:This paper investigates the start-up conditions in Pierce CMOS crystal oscillator base upon the auto-control principle . The effect of oscillator start-up conditions caused by crystal circuit parasitics has been analyzed theoretically in detail. The result of theoretical analysis is verified using Matlab, and the optimum inverter which can guarantee circuit oscillate reliably has been designed for the 15Mhz crystal oscillator as an example. Finally, using Hspice simulation, the correctness of the theoretical analysis is verified further.Key words:CMOS, Crystal oscillator, Start-up conditionI . 引言在现代电子系统中,Pierce CMOS晶振电路,作为时钟发生器,得到越来越广泛的应用[1][2][8][10]。

基于CMOS反相器的石英晶体振荡器是一种常用的结构,然而,以前的分析直接从电路结构入手,没有把晶振电路作为一个控制系统来分析,也没有很好的关注晶振中寄生参数对振荡器起振的影响[8][10],只是说明了反相器在某一尺寸可以起振,并没有说明怎样设计一个反相器,使其尺寸在一个范围内都能使晶振电路可靠起振,以及怎么使其快速起振。

晶振电路在固定偏置下,即使环路增益满足“巴克豪森准则”,振荡器似乎能够振荡,而实际上如果环路增益太大,电路也不能起振。

本文针对这些问题,把晶振电路从控制系统的角度,结合自动控制原理进行理论分析,详细说明了各种参数对电路性能的影响,得到使晶振电路起振的环路增益的范围,并结合Matlab 得到一个最优值,最后以15MHz晶振电路设计为例,在SMIC 130nm CMOS工艺下,通过Spice 模拟验证理论分析的正确性。

II . 原理石英谐振器简称晶体,是晶体振荡的核心原件,它由石英晶体片、电极、支架及其他辅助装置组成,是利用石英晶体的压电效应原理制成的电、机械振荡系统。

如图1是石英晶振的等效电路。

图1. 石英晶振等效电路Fig. 1. crystal equivalent circuit石英晶振由等效电阻R 0、等效电感L 0和等效电容C 0组成的串联振荡回路与静态电容C 3并联组成。

在等效电路中,L 0、C 0组成串联谐振电路,谐振频率为[5]:0f =(1)而L 0、C 0又与C 3组成并联谐振回路,谐振频率为:f ∞=(2)当工作频率0f f <时,晶体呈容性;当工作频率0f f f ∞<<时,晶体呈感性;而当工作频率f f ∞>时,晶体呈容性。

晶体在晶体振荡器主振级的振荡电路中呈现感性,即工作频率满足0f f f ∞<<。

如图2是常用的Pierce振荡器拓扑图。

图2. Pierce 石英振荡电路Fig. 2. Pirece crystal oscillator circuitPierce 振荡器电路用并联反馈电阻R f引进直流偏置。

在电路起振时,R f 使得反向器的V in ≈V out ≈V dd /2。

为了减小晶振上的负载电阻,这些偏置电阻在工艺和有源器件的特性允许的情况下要尽可能的大,当振荡频率为1MHz~~20MHz 时,R f 典型值为1MΩ~~10MΩ范围。

反相器提供了必要的增益并产生180°相移,电容C 1和C 2设置电路的反馈因子,结合晶振的感抗产生振荡所需的另外180°相移,在加上反相器提供的180°相移,只要电路环路增益满足“巴克豪森准则”[3]:00|()|1()180H j H j ωωO≥⎧⎪⎨∠=⎪⎩(3) 那么电路就会在0ω处起振。

这两个条件是必须的但还不充分,在存在温度和工艺变化的情况下为了确保振荡,典型地我们将选择环路增益至少两倍或三倍于所要求的值。

图2所示的振荡器的小信号模型如图3所示,这可以用来确定振荡器的起振条件。

跨导g m 取决反相器以及电路的偏置条件,电阻R 1和R 2分别表示总的输入输出阻抗。

电容C 1和C 2包括有源器件电容和电路产生寄生电容。

R 0、C 0和L 0构成晶振的等效电路。

电容C 3包括了有源器件的电容,但是主要取决于晶振的固有电容,R f 是偏置引入的电阻。

-图3. 石英振荡器小信号模型Fig. 3. Small-signal crystal oscillator←如图3,我们可以研究电路的稳定性条件,从受控电流源的输出端断开环路,引进一个测试电流i 流过反馈环路以计算环路增益。

首先,分析晶振等效电路以及R 3、C 3的等效阻抗,如下:003011()||||()f Z s R R L s C s C s=++ (4) 200002203000000003(1)(1)(1)f f R L C s R C s C R C s L C s R C s L C s R C s C ++=++++++ (5)现在我们可以通过计算环路传输函数来分析电路的稳定性,如图3,断开反馈环路,引入测试电流i ,则有:221121211||1||11||()||in R C sV R C sR Z s R C s C s=∙++ (6) out m in i g V = (7)()out m in i g VT s i i=-=- (8) 121122122211()()(1)(1)(1)(1)m g R R T s Z s R C s R C s R R C s R R C S =-++++++ (9)从传输函数可以看出,T(s)包含高Q 值复数零、极点对,加上两个负实数极点和一个负实数零点。

现在,可以用一些典型的晶振参数值代入函数,产生相应的波特图、根轨迹图、Nyquist (奈奎斯特)图,以分析振荡电路的是否能够起振。

III 、Matlab 分析式(8)是电路的传输函数T(s),可以看出T(s)是g m 的线性函数,则可以得到归一化的传输函数()//m in T s g V i -=,g m 作为根轨迹图中变量,其变化范围为0~~+∞。

首先不考虑寄生参数R f 和C 3,且将反向器的输入电阻看成∞,用谐振频率为15MHz 典型的参数:L 0=11.25mH 、C 0=10fF 、R 0=25Ω、R 2=1K Ω、C 1=12pF 、C 2=15pF ,用Matlab 得到的根轨迹图如图4所示。

根轨迹法是分析和设计线性系统的定常控制系统的图解方法,它是开环系统某一参数从零变化到无穷时,闭环系统特征方程的根在s 平面上变化的轨迹,如果闭环极点全部位于S 左半平面,则系统一定是稳定的,否则系统就不稳定,即稳定性只与闭环极点位置有关,而与闭环零点位置无关[4]。

从图4可见,在g m 变化的整个范围内,根轨迹在右半平面都存在,系统不稳定,所以电路不存在起振的问题。

图4.根轨迹图Fig.4. Root-locus diagram但是,忽略C 3只是理想情况。

为了电路能偏置在一个合理的工作点,R f 是必须的,下面来考虑实际情况,C 3=12pF 、R f =5M Ω、R 1=1020Ω,我们可以得到Matlab 分析结果如图5所示,其中图5(a)为根轨迹图。

从图5(a)可见,随着g m 增加,根轨迹会进入右半平面,电路会起振,但是随着g m 继续增大,根轨迹又会重新进入左半平面,系统会达到稳定,电路不能起振。

所以g m 只有在一个合适的范围之内电路才会起振。

从图5(c)Nyquist 也可以得到相应的结论,它包含负实轴上的点(-1/g m ,0),从而也可以得到使得电路起振g m 的范围。

如图5(d)可以看到在频率为晶体谐振频率15MHz 时,相移达到了180°这个关键点,且增益的绝对值大于一,满足了巴克豪森准则,所以只要确定一个合理的g m ,电路就会起振。

当然,为了电路能够可靠的起振,我们希望g m 的范围越大越好,而实际上g m 的范围是由电路参数确定的,而现在15MHz 晶振的参数是确定的,经Matlab 分析可知,当R f 到达几兆欧姆时,对g m 范围的影响可以忽略,增大C 1、C 2都可以增大g m 的范围,但是电容太大,会影响振荡频率的精确度;而反相器输入输出电阻也是影响电路起振的重要因素。

所以下一节就是要通过Hspice 找到一个合理的反向器,使它的输入输出电阻及g m 能够使得电路能可靠起振。

(a)(b)(c)(d)图5. (a) 根轨迹图; (b) 根轨迹局部放大图;(c) Nyquist 图;(d) 波特图Fig.5. (a) Root-locus diagram (b) enlarged diagram of Root-locus (c)Nyquist diagram (d) Bode plotIV 、Spice 模拟用15MHz 晶振典型参数得到如图5(a)根轨迹图,随着g m 增大,根轨迹会进入右半平面,当g m 继续增大,根轨迹又会回到左半平面,因为根轨迹图中,左半平面系统是稳定的,右半平面系统是不稳定,而振荡电路是一个不稳定系统,所以需要根轨迹进入右半平面,此时临界点的g mmin = 1.36mA/V 和g mmax =36.5mA/V ,及当反相器的g m 在此之间时,系统就会发生振荡,但是为了使反相器能够快速起振,反相器的跨导应满足[2]:moptg=(10)确定了反相器g mopt的值,接下来就可以确定反相器的尺寸了。