zedboard启动流程

Zedboard开发例程--点亮Led流水灯(基于PS+PL+SmallRTOS)

图 8、 Vivado 主界面 主界面主要包括: Flow Navigator: Sources: 在此可以找到整个设计过程中涉及到的所有流程 工程包含的设计源文件,源码、约束等

微型嵌入式实时操作系统 SmallRTOS 官方网站:

微型嵌入式实时操作系统 SmallRTOS 官方网站:

图 5、 新建工程向导 step3

图 6、 选择器件/开发板 最后一步:所建立工程的概要信息。

Zedboard 开发例程‐‐点亮 Led 流水灯

——基于 PS+PL+SmallRTOS

1、目标规划

硬件平台:Zedboard; 软件平台:Vivado、SDK; 实时操作系统:SmallRTOS; 实现功能:采用 PL 添加 IP 核,PS 控制 GPIO 的方式,控制 LED 流水灯,同时熟 悉微型嵌入式实时操作系统 SmallRTOS 的多任务功能; 实现流程: 建立工程 添加 ARM 内核、 GPIO IP 综合、 实现、 烧写 板级测试;

微型嵌入式实时操作系统 SmallRTOS 官方网站:

图 3、 新建工程向导 step1

图 4、 新建工程向导 step2 指定工程名和存储路径 勾选图 5 复选框内的选项,表明不在此时指定源文件。

Properties: Project Summary: Design Runs: 令 3.2. 流程控制子窗口

所选中对象的属性信息 在此可以查看工程信息 在此可以查看提示信息、警告、错误、也可以输入 tcl 命

图 9、 流程子窗口

微型嵌入式实时操作系统 SmallRTOS 官方网站:

图 12 3.4、添加 cpu 在 Diagram 子窗体中找到 Add IP 按钮,位置如图 13 所示的提示框左上方。

Zynq学习笔记(基本设计流程)

4.设置boot模式。

输入0,1-9测试

5.将LED_Dimmer.BIN文件名字改为BOOT.BIN(后缀不用修改),再拷贝到SD卡中,并插入Zedboard。

6.设置boot模式。

5.配置PS时钟:CLKIN=33.3333(常用的)。CPU=666.6666;DDR_CLK=533.333.

CPU Clock Ratio=6:2:1,均为默认值。

设置外设时钟。

QSPI的模块内部有一个2分配的电路,应此想设置他的工作频率为100M,就需要将输入时钟设为200MHz。

SDIO(即SD卡的时钟),设为50MHz。

勾选USB0,28-39

勾选Ethernet0,改EMIO为MIO:16-27,打开“+”,勾选MDIO:52-53

添加SD 0 40-45, CD:47, WP:46

点开GPIO,勾选GPIO MIO,设置MIO的Direction:50-51为输入,MIO7只能是输出,其余为输入输出。若看不到,就向右拉移动条。

3.下面是main.c的具体设计步骤,附件为完整的程序,可以拷贝以节省时间。

4.点击system.mss,可以找到外设的驱动和例程,axi_gpio_1,Examples(点击);打开xgpio_example.c。

5.在main.c中从xgpio_example.c中拷贝并添加两个头文件。#include "xparameters.h";#include "xgpio.h"

11.往GPIO写0,灭灯。XGpio_DiscreteWrite(&Gpio, LED_CHANNEL, 0);

zedboard的大体架构介绍(PS、PL、硬件互联)

zedboard 可以将逻辑资源和软件分别映射到 PS 和 PL 中,这样可以实 现独一无二和差异换的系统功能,主要分为两大部分,处理系统和可编程逻 辑。以及二者之间的互联特性。这篇笔记主要记录 zedboard 的大体架构。 1. 处理系统(PS) 应用处理单元(APU) 存储器接口 I/O外设,包括静态存储器和Flash存储器接口,可以通过共 享一个 54 引脚的多路复用 io(MIO) 互联,也可以扩展访问 PL 中的 IO 2. 可编程逻辑(PL)

GPIO, 3 模式的以太网控制器, USB 控制器,可以作为主设备或者 OTG SD/SDIO 控制器,两个,可以作为基本的启动设备,支持 sd 2.0 规 范, SPI 控制器:四线总线,MOSI,MISO,SCLK,SS,支持全双工操 作, CAN 控制器(两个) UART 控制器两个 i2c 控制器(两个)

1. 基于 AXI 高性能数据通路开关的 PS 互联 OCM 互联,提供来自中央互联和 PL 的,用于对 256KB 存储器的访 问, CPU 和 ACP 的接口, 中央互联, 中央互联是 64 位的,将 IOP 和。将以太网、usb、和 sd/sdio 控制器内的本地 DMA 单元连接到中央互联,将 PS 内的主设备连接到 IOP。 2. PS-PL 接口,包含所有 PL 设计者的可用信号,可以基于 PL 的功 能和 PS 集结在 一起。 功能接口,包含 AXI 互联,用于大多数的 IO 外设、中断,DMA 控 制流、时钟和调试接口的扩展 MIO 接口,

可编程逻辑 PL 特性 可配置逻辑块(CLB) 36KB 的 Bram,双端口,最多 72 位宽度,可编程 fifo 逻辑, 数字信号处理-DSP48E1 芯片 时钟管理 可配置的 io 模数转换特性(XADC) 互联特性

《一步一步学ZedBoard

(这是本系列的第一篇,每个步骤均给出截图)硬件平台:Diligent ZedBoard开发环境:Windows XP 32 bit软件:PlanAhead 14.1 + XPS 14.1 + SDK 14.1Zed板上的Zynq是一个PS(processing system, 双核A9 + 存储管理+ 外设)+ PL(programable Logic) 结构,如果不使用PL,zynq的开发和普通的ARM 芯片开发一样。

不同的是PS单元是可配置,因而硬件信息是不固定的。

这也是zynq灵活性的一个表现。

一、配置硬件信息启动PlanAhead,进入新建工程向导选择工程名和路径工程类型,这里选择RTL 工程由于只需要PS部分信息,而这部分在后面由XPS完成,因而不需要添加任何文件一直点下一步,直道出现芯片和板载信息。

直接选择Boards,选择系列是Zynq-7000。

14.1目前只支持XC7Z020器件。

完成新建工程向导PlanAhead进入工作视图,在Project Manger中选择建立的工程,右键,Add Sources选择Add or Create Embeded Sources单击Create Subdesign输入需要建立嵌入系统名称,这里填duocore确定后,提示所建立的工程是一个Zynq工程,提示是否添加PS到系统。

点确认。

XPS会被启动,可以看到Zynq的配置界面。

Diligent公司做好了一套配置方案,从其网站上能下载到配置文件:import这个配置文件,点“+”找到文件位置后,点OK可以看到配置后的结果,同时MHS和UCF文件也被修改。

其中有颜色标记为使用,没有颜色标记表示没有使用。

可以对其修改,这是对应ZedBoard的硬件接口,保持默认就可。

至此,硬件配置结束。

关闭XPS,切换到PlanAHead。

可以看到duocore.xmp已经加入到工程中。

在硬件配置文件duocore.xmp上右键,选择Create Top HDL,生成顶层HDL文件可以看到生成的duocor_stub.v文件最后一步,将硬件信息导入到SDK。

ZedBoard Linux开发 ---- OLED驱动详解

ZedBoard Linux开发---- OLED驱动详解但凡单片机的初学者基本都有这样一个试验,也就是点亮第一个LED,类似于程序员的“helloworld”,我当年也是如此。

本来我也是希望从LED开始学习,不过对于ZedBoard来说,可能还找不到现成的LED驱动程序可以学习(事后发现在Digilent Linux内核中,点亮一个LED所要理解的机制其实更加复杂),反而倒是提供了OLED的内核驱动,因此我们就从点亮OLED开始吧。

对于OLED在用户空间的操作,之前介绍了两种方式,即shell以及编写C应用程序,博客链接如下:/thinki_cao/blog/static/8394487520143193932495/OLED的驱动在Linux内核源码中的位置是linux-digilent/drivers/pmods/pmodoled-gpio.c,而在内核配置中的位置是:-> Device Drivers-> Pmod Support (PMODS [=y])(注意make ARCH=arm menuconfig的时候务必要把ARCH加上)并且默认是编译进内核的,而在Digilent OOB Design中是以模块驱动的形式放在ramdisk文件系统中的,因此如果重新编译内核的话,原先的load_oled,unload_oled都是无法使用的,原理很简单,上面两个命令都是脚本,并且是单纯的insmod以及rmmod驱动。

下面就开始看分析pmodoled-gpio.c文件:首先跳到文件最后几行,找到函数module_platform_driver(gpio_pmodoled_driver); 该函数定义在include/linux/platform_device.h文件中:#define module_platform_driver(__platform_driver) \module_driver(__platform_driver, platform_driver_register, \platform_driver_unregister)而module_driver()函数则定义在include/linux/device.h文件中:#define module_driver(__driver, __register, __unregister, ...) \static int __init __driver##_init(void) \{ \return __register(&(__driver) , ##__VA_ARGS__); \} \module_init(__driver##_init); \static void __exit __driver##_exit(void) \{ \__unregister(&(__driver) , ##__VA_ARGS__); \} \module_exit(__driver##_exit);通俗一点来理解的话,module_platform_driver(gpio_pmodoled_driver);最终展开后就是如下形式:static int __init gpio_pmodoled_driver_init(void){return platform_driver_register(&gpio_pmodoled_driver);}module_init(gpio_pmodoled_driver_init);static void __exit gpio_pmodoled_driver_init(void){return platform_driver_unregister(&gpio_pmodoled_driver);}module_exit(gpio_pmodoled_driver_exit);看到module_init()和module_exit()估计就熟悉很多了,其实一开始我也不习惯这些宏,不过后来习惯了以后发现还是有不少好处的,所以我们编写驱动的时候可以参考内核中的代码风格和习惯,非常具有学习意义。

ZedBoard学习笔记(一)—永远的led

ZedBoard学习笔记之(一)—永远的led灯Author:HJS-6511Date:2013-11-5教程简介:如果你未接触过ZedBoard板卡或PlanAhead软件,那么就对了,我们来做一个实验:用板卡上的SW0-7开关来控制LD0-7的led灯。

实验代码如下(Verilog):module demo(input [7:0]sw, //信号输入,将连接到ZedBorad板卡上的SW0-7。

output [7:0]led //信号输出,将连接到ZedBoard板卡上的LD0-7。

);assign led = sw; //SW0-7与LD0-7一一对应。

Endmodule这下知道有多简单了吧,那我们就开始动手吧。

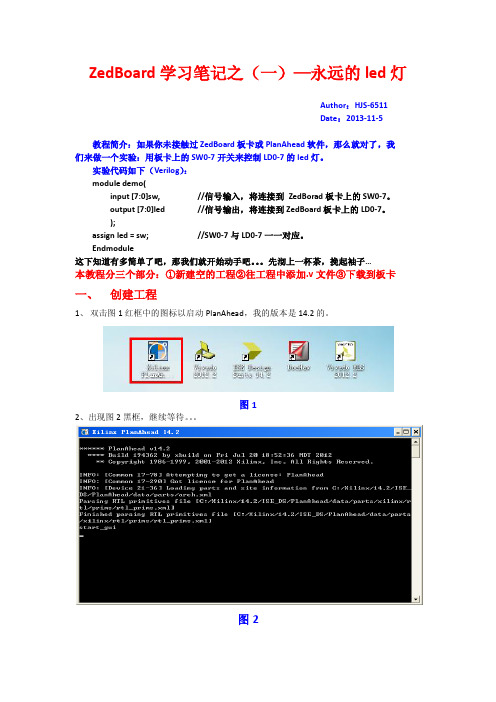

先沏上一杯茶,挽起袖子…本教程分三个部分:①新建空的工程②往工程中添加.v文件③下载到板卡一、创建工程1、双击图1红框中的图标以启动PlanAhead,我的版本是14.2的。

图12、出现图2黑框,继续等待。

图23、好吧,终于是启动了,如图3,;但是可能会出现图4中的对话框,这是要你更新到新版本,不用管,点击EXIT退出更新提示。

图3图44、下面我们就来创建一个新的工程,点击Create New Project,如图5图55、添加工程路径和工程名,做好后点击Next,如图6图66、点击Next,如图7图7 继续,如图8图87、接下来会出现如图9、10、11对话框,一路点击Next,别狂点啊,出现图12就收手吧。

图9图10图11 8、选择板卡如下,好了之后点击Next,如图12图129、这就是我们的工作环境,大概分为以下几个部分,如图13图13以上步骤,我们便完成了创建一个全新奉的空的工程,是不是想问:咦?在哪里写代码呢?别急接下来我们要往工程里面添加一个东西,那就是.v文件,写在.v里面不就行了吗。

二、添加文件1、点击Add Sources添加文件。

如图14图142、选择Add or Create Design Sources,即添加或创建设计文件,然后Next,如图15图153、创建一个源文件,点击Create File,如图16图164、选择语言,这里我们选择Verilog,输入.v文件的文件名,这里给大家演示一下就取demo.v 吧,输入demo后,点击OK,如图17图175、已经添加上了,好吧,直接点击Finish创建完成,如图18图186、其实还没有完成,呵呵。

Zedboard USB串口驱动安装

Zedboard USB串口驱动安装

Zedboard上板载有一个USB转UART串口,采用了Cypress公司的USB-UART控制器CY7C642 25。

CY7C64225提供了一个非常简洁的USB串口方案,片内集成了USB2.0全速控制器、UART 收发器、晶振以及EEPROM等各种功能,而只采用了28脚的SSOP封装。

Zedboard的USB驱动安装很简单,首先下载USB驱动程序,解压缩后会有3个子目录分别对应Windows XP、Windows Vista和Windows 7系统,根据自己的计算机系统选择。

Zedboard上的J14 USB口(有UART标识)作为USB-UART接口,连接Micro USB到计算机。

接通电源,系统会识别USB设备,这里我们需要安装两次驱动。

首先识别设备Cypress-USB2U ART-0123456,

安装驱动之后会产生一个USB设备Cypress Virtual Comm Port00,这里继续选择刚才的驱动程序位置

安装完成之后打开设备管理器可以看到USB串口端号。

小结

在Windows XP下安装Zedboard USB串口驱动。

参考资料

Zedboard Cypress USB-UART配置说明

(爱板网经验频道)。

Vivado+Zedboard之流水灯

Vivado+Zedboard之流水灯环境:Vivado 2014.2开发板:Zedboard version xc7z020clg484-1实验:使用Vivado与SDK进行Zedboard开发,制作一个简单的流水灯程序以说明软硬件协同设计的方法、开发流程等。

本文将分为三个部分:1. 使用Vivado创建一个工程,并构建一个Zynq嵌入式处理系统2. 在上述基础上,将完成后的硬件导入到SDK中进行软件设计。

3. 最后下载到ZedBoard上进行调试。

1. 使用Vivado创建工程1.1新建工程1.鼠标左键双击Vivado 2014.2图标,打开Vivado 2014.2,出现如下界面:2.单击Create New Project创建一个新的工程:3.单击Next执行下一步;4.选择工程所在的位置,并输入工程名test_led,单击Next;5.在Vivado中新建一个RTL工程,暂不添加文件,单击Next;6. 单击Next执行下一步;7. 单击Next执行下一步;8. 单击Next执行下一步;9.这一步要注意,在左上角Specify处选择Boards,选择ZedBoard Zynq Evaluation and Development Kit version D器件,单击Next;10.单击Finish11.等待软件根据设定新建一个RTL工程。

这样新建工程的步骤就完成了,下面进行硬件设计步骤;1.2硬件设计新建工程的界面如下:1.单击Create Block Design,创建并添加IP核;2.输入工程名led,单击OK;3.等待软件Create Block Design,创建完成后的界面如下:4. Add IP,通常会提示This design is empty.To get started, Add IP from the catalog,单击Add IP会出现IP的目录,假如此处没有提示,能够单击Diagram左边框的Add IP添加;5. 在目录Search中输入ZYNQ7 Processing System;6.双击ZYNQ7 Processing System完成IP核的添加;7.等待软件Add IP,添加完成后的界面如下:8.单击Run Block Automation;9.单击processing_system7_0;10.单击OK;11.等待软件运行,运行后的界面为:12.假如想熟悉内部的全面结构与进行接口配置,能够双击ZYNQ7 Processing System核,(此实验不需要设置,假如想直接进行下一步实验能够直接跳到步骤16)13.等待软件运行,运行后的界面为:14.单击左侧对应内容能够进行接口配置:15.单击OK完成配置;16.继续添加IP ,单击左侧的Add IP图标:17.在目录Search中输入AXI GPIO;18.双击AXI GPIO添加;19.继续添加IP,单击左侧的Add IP图标,在目录Search中输入AXI BRAM Controller:20.双击AXI BRAM Controller,完成添加;21.继续添加IP,单击左侧的Add IP图标,在目录Search中输入Block Memory Generator:22. 双击Block Memory Generator,完成添加;23.右键单击Block Memory Generator,选择Customize Block:24. Mode处选择BRAM Controller,Memory Type处选择True Dual Port RAM:25.单击OK完成设置;26.连接the Block Memory Generator to the AXI4 BRAM Controller 27.Run Connection Automation 选择/axi_gpio_0/S_AXI:28.单击OK,完成此部分的连接;29. Run Connection Automation again, 选择/axi_gpio_0/GPIO;30.选择leds_8bits,单击OK;31.Run Connection Automation again, 选择/axi_bram_ctrl_0/S_AXI;32.单击OK;33. 修改the range of the AXI BRAM Controller to 64K:34. 单击File选择Save Block Design储存设计(也能够直接Ctrl+S)1.3硬件处理1. Tools >Validate Design2.等待软件运行,运行后的界面如下:3.单击OK;4.right-click the top-level subsystem design->Generate Output Products5.单击Generate,等待软件运行,运行完成后right-click the top-level subsystem design->Create HDL Wrapper6.单击OK;7. 单击Generate Bitstream,单击Yes,首先进行分析综合与实现;(这里也能够直接先点击Run Synthesis,然后点击Run Implementation,然后再点击Generate Bitstream) 需要等待运行的时间比较长,本机大概需要15分钟;8.运行完成后,会自动弹出对话框,选择Open Implemented Design,单击OK:9.运行完成后的界面如下:10. 在关联到SDK时,需要将Package与Device都打开,假如运行后只是自动打开了device,需要Open Synthesized Design来打开Package11.单击NO,将Package与Device同时显示出来;打开后的界面如下:12. 单击Open Block Design to invoke the IP integrator design13. 连接micro-usb cable between the PC and the JTAG port of the board, another micro-usb cable between the PC and the UART port of the board,.打开Zedboard板的电源,如下图所示,打开电源之后POWER灯会亮;14.单击Hardware Manager中的Open Target,这里由于曾经在本机上使用过Zedboard,因此会直接显示出Localhost,假如是第一次连接Zedboard,要单击Open New Target (假如直接显示出Localhost,能够直接点击Localhost进行步骤18)15.单击Next;(假如hardware manager中找不到硬件板,这是由于在任务管理器的进程中,hw_server.exe进程一直在执行,需要将其关掉,假如关了之后还检测不到硬件板,则需要关机之后再开机便可;)16.选择Local server,单击Next;17.软件会自动检测出Localhost,选择后单击Next;18.单击Finish,自动Open Target;19. 单击Hardware Manager中的Program Device,单击xc7z020_1:20.单击Program将比特流烧写到ZedBoard板上;完成后板上的DONE蓝灯会亮,提示成功:21.单击File中的Export,单击Export Hardware22.单击OK23. 单击File中的launch SDK:24.单击OK;这样在Vivado中的操作就完成了,软件会自动打开SDK:SDK中的软件设计打开后的SDK界面如下:1. 单击File > New > Application Project2.输入工程名zj,单击Next:3. 选择一个空的模板:empty application,单击Finish,等待工作环境的建立:4. 单击led > 右键单击src > new > Source File5.输入工程名zj.c,单击Finish;6. 编写如下程序,Ctrl+S,储存的同时,软件会自动开始编译,在左下角problem处能够看到相应的warning与error;程序如下:#include"xparameters.h"/* Peripheral parameters */#include"xgpio.h"/* GPIO data struct and APIs */#include"xil_printf.h"#include"xil_cache.h"#define GPIO_BITWIDTH 8 /* This is the width of the GPIO */ #define GPIO_DEVICE_ID 0//device id#define LED_DELAY 10000000/* times delay*/#define LED_MAX_BLINK 0x1 /* Number of times the LED Blinks */#define LED_CHANNEL 1 /* GPIO channel*/#define printf xil_printf /* A smaller footprint printf */ XGpio Gpio; /* The Instance of the GPIO Driver */XGpio GpioOutput; /* The driver instance for GPIO Device configured as O/P */int GpioMarquee (u16 DeviceId, u32 GpioWidth){volatile int Delay;u32 LedBit;u32 LedLoop;int Status;/** Initialize the GPIO driver so that it's ready to use,* specify the device ID that is generated in xparameters.h */Status = XGpio_Initialize(&GpioOutput, DeviceId);if (Status != XST_SUCCESS){return XST_FAILURE;}//Set the direction for all signals to be outputsXGpio_SetDataDirection(&GpioOutput, LED_CHANNEL, 0x0);// Set the GPIO outputs to lowXGpio_DiscreteWrite(&GpioOutput, LED_CHANNEL, 0x0);for (LedBit = 0x0; LedBit < GpioWidth; LedBit++){for (LedLoop = 0; LedLoop < LED_MAX_BLINK; LedLoop++) {//Set the GPIO Output to HighXGpio_DiscreteWrite(&GpioOutput, LED_CHANNEL,1 << LedBit);//Wait a small amount of time so the LED is visiblefor (Delay = 0; Delay < LED_DELAY;Delay++);//Clear the GPIO OutputXGpio_DiscreteClear(&GpioOutput, LED_CHANNEL,1 << LedBit);// Wait a small amount of time so the LED is visiblefor (Delay = 0; Delay < LED_DELAY; Delay++);}}return XST_SUCCESS;}int main(void){//Application start/* loop forever*/int cnt=0;while(1){u32 status;status = GpioMarquee (GPIO_DEVICE_ID,GPIO_BITWIDTH);if (status == 0){printf("%d:SUCESS!.\r\n",cnt++);if(cnt>=1000)cnt=0;}elseprintf("FAILED.\r\n");}return XST_SUCCESS;}7. 单击Xilinx Tools > program FPGA将比特流烧写到板上(在Vivado中就先将比特流烧写到板上有两个原因:1.假如SDK调试时出现问题,这样能够检测首先是不是Vivado的问题,假如成功烧写,说明板的连接没有问题,同时Vivado软件本身没有问题;2.在之前的调试过程中出现过直接Xilinx Tools > program FPGA无法烧写的情况;因此,保险起见,选择在Vivado中就先将比特流烧写到板上)8.单击Program(与在Vivado中烧写的现象一样,完成后DONE蓝色指示灯会亮)注:假如软件本身与板的连接没有问题,那么这个步骤会在三秒左右完成,假如一直卡在一半的进度,说明SDK与Vivado没有很好的建立关联;9.在Terminal处,单击带有加号的图标,对串口进行配置:10.在用到串口打印时,需要设置的COM口,为设备管理器中的USB serial port (本机为COM5),因此要选择COM5,注意波特率为115200:11.右键工程目录中的zj目录,选择Run As > Run Configurations;12.在STDIO Connection中设置COM 5与波特率115200:13.单击Run即可运行程序,看到流水灯的效果,每次跑完一圈会打印:数字:SUCESS!.的消息,数字为流水灯循环的次数。

基于XVC协议的Zedboard平台远程更新与调试

基于X V C协议的Z e d b o a r d平台远程更新与调试朱琛1,沈小波1,周志刚2(1.中国电子科技集团公司第五十八研究所,无锡214000;2.中国船舶重工集团公司第702研究所)摘要:船舶雷达数据处理设备是许多科研院所面对庞大的雷达数据而研发的处理设备㊂此类处理设备属于船用设备,且设备中处理板卡众多㊂为了在不打开设备的情况下,脱离专用的U S B J T A G下载电缆对处理板中的F P G A进行远端升级,本文提出一种虚拟线缆协议,通过以太网,利用Z e d b o a r d平台的P S端控制P L端生成的J T A G接口对其进行远程更新与调试的方法㊂该方案成本较低,易于拓展,同时也提高了更新可靠性㊂关键词:X V C协议;Z e d b o a r d;J T A G接口;T C P/I P;远程更新与调试中图分类号:T N919文献标识码:AR e m o t e U p d a t i n g a n d D e b u g g i n g o f Z e d b o a r d P l a t f o r m B a s e d o n X V C P r o t o c o lZ h u C h e n1,S h e n X i a o b o1,Z h o u Z h i g a n g2(1.T h e58R e s e a r c h I n s t i t u t e o f C h i n a E l e c t r o n i c s T e c h n o l o g y G r o u p C o r p o r a t i o n,W u x i214000,C h i n a;2.T h e702R e s e a r c h I n s t i t u t e o f C h i n a S h i p b u i l d i n g I n d u s t r y C o r p o r a t i o n)A b s t r a c t:T h e s h i p r a d a r d a t a p r o c e s s i n g e q u i p m e n t i s d e v e l o p e d b y m a n y s c i e n t i f i c r e s e a r c h i n s t i t u t e s i n t h e f a c e o f h u g e r a d a r d a t a.T h i s k i n d o f p r o c e s s i n g e q u i p m e n t b e l o n g s t o m a r i n e e q u i o m e n t,a n d t h e r e a r e m a n y p r o c e s s i n g b o a r d s i n t h e e q u i p m e n t.T h i s s t u d y a i m s t o d e s i g n a n d i m p l e m e n t r e m o t e u p d a t i n g a n d d e b u g g i n g m u l t i-f i e l d p r o g r a mm a b l e g a t e a r r a y f o r t h e d e t e c t o r w i t h o u t o p e n i n g t h e e q u i p-m e n t,s e p a r a t e f r o m t h e s p e c i l a U S B-J T A G d o w n l o a d c a b l e.I n t h e p a p e r,a n e t w o r k b a s e d Z e d b o a r d̓s p r o c e s s i n g s y s t e m i s u s e d t o a c c e p t c o n f i g u r a t i o n f i l e s v i a n e t w o r k a n d g e n e r a t e J T A G b y Z e d b o a r d̓s p r o g r a mm a b l e l o g i c s e q u e n c e t o F P G A b y m e a n s o f X i l i n x v i s u a l c a b l e p r o t o c o l.T h e r e m o t e u p d a t i n g a n d d e b u g g i n g o f m u l t i-F P G A a r e r e a l i z e d.T h i s m e t h o d i m p r o v e s t h e r e l i a b i l i t y o f r e m o t e u p d a t i n g a n d d e b u g g i n g o f F P G A s a n d i s e a s y t o e x t e n d w i t h l o w c o s t.K e y w o r d s:X V C p r o t o c o l;Z e d b o a r d;J T A G i n t e r f a c e;T C P/I P;r e m o t e u p d a t i n g a n d d e b u g g i n g0引言早期的船舶雷达设备和其他电子设备一样经历过电子管和晶体管的元件阶段㊂随着大规模集成电路的出现,现在的船舶导航雷达处理单元,大多采用高性能的F P G A 进行数据采集及加速㊂当大量模块单元需要升级时,需要拆卸机箱,耗时耗力[1]㊂考虑到对设备进行程序更新及版本升级,拆卸设备工作量较大且更新时易出错,本文设计了一种基于X V C (X i l i n x V i r t u a l C a b l e)的协议,通过以太网,配合A R M+ F P G A混合架构的Z Y N Q7000系列板卡,利用G P I O口模拟J T A G接口进行远程更新调试的方案㊂该方案操作简单,无需额外开发T C P/I P软件,基于网络的通信能够保证足够远距离的灵活可靠的数据传输,还能对F P G A进行远程H a r d w a r e M a n a g e r调试㊂同时,通过简单的J T A G链路连接可以完成远端多片F P G A在线升级及调试㊂1系统架构本设计采用Z e d b o a r d平台嵌入式开发板,其基于X i l-i n x Z Y N Q7000系列芯片㊂Z Y N Q7000采用A R M+ F P G A架构,具有高度集成性,整个系统具有丰富的处理器和扩展资源,用户可以根据需求将不同的模块连接起来,实现自定义逻辑功能[2],因而非常利于多片F P G A远程更新与调试㊂Z e d b o a r d开发板实物图如图1所示㊂通过A R M处理器中网络口控制A X I(A d v a n c e d e X-t e n s i b l e I n t e r f a c e)总线,将更新程序发送到F P G A端,F P-G A端例化一个J T A G接口对光纤接口板进行更新与调试[3]㊂设计实现远程更新船舶雷达设备中光纤接口板(核心芯片为x c7k325t),整体架构图如图2所示㊂2基于Z e d b o a r d平台的P L端开发在Z e d b o a r d平台上进行P L(P r o g r a mm a b l e L o g i c)端开发,核心是通过G P I O口实现J T A G模块功能㊂J T A G图1 Z e d b o a r d开发板实物图图2 设计整体架构图模块功能主要是通过器件内部的T A P (T e s t A c c e s s P o r t,图3 F P G A 端设计架构测试访问端口)对芯片内部的寄存器进行访问㊂T A P 控制器包含一个具有16个状态的自动状态机,对数据寄存器D R (D a t a R e g i s t e r )和指令寄存器I R (I n s t r u c t i o n R e g-s i t e r)进行相关操作㊂本设计中需要4个I P 核:p r o c e s s i n g _s ys t e m 7_0㊁a x i _i n t e r c o n n e c t _0㊁p r o c _s y s _r e s e t _0和a x i _j t a g _0㊂p r o c e s s -i n g _s y s t e m 7_0为Z Y N Q 7000的系统I P 核㊂a x i _i n t e r -c o n n e c t _0为A X I 总线中转I P 核㊂p r o c _s ys _r e s e t _0为系统连接其他A X I 的复位I P 核㊂a x i _j t a g_0为G P I O 配置J T A G 时序I P 核㊂F P G A 端的设计架构图如图3所示㊂P S (P r o c e s s i n g S y s t e m )端通过A X I 总线对a x i _j t a g_0进行数据传输,主要是内核中寄存器的读写,本文中a x i_j t a g _0内核设计了5个寄存器,即[31ʒ0]s l v _r e g0㊁[31ʒ0]s l v _r e g 1㊁[31ʒ0]s l v _r e g 2㊁[31ʒ0]s l v _r e g3㊁[31ʒ0]s l v _r e g 4,分别对应数据传输长度L E N G T H ㊁J T A G 总线的TM S 信号数据㊁J T A G 总线的T D I 信号据㊁J T A G 总线的T D O 信号数据及P S 端传输有效E N A B L E信号㊂通过开发软件设置a x i _j t a g _0的IP 核寄存器起始地址为0x 43C 0_0000,长度为64K B ㊂最后R T L 分析综合㊁实现并生成二进制文件,给P S 端提供软件设计的硬件平台㊂3 基于Z e d b o a r d 的嵌入式L i n u x 平台开发本设计基于Z e d b o a r d 开发板,在P S 端移植嵌入式L i n u x 系统,并需要在开发应用程序中实现X V C 虚拟网络功能㊂3.1 引导程序的移植嵌入式操作系统都会采用引导程序来引导内核,本设计使用u b o o t 作为启动引导[5]㊂由于使用Z Y N Q 系列芯片,在引导操作系统与之前单纯的只含有A R M 架构的芯片有所不同,需要在u b o o t 之前增加F S B L .e l f 及s ys -t e m.b i t 文件,其L i n u x 系统启动过程如图4所示㊂并对u b o o t 进行相应配置,主要包含内核镜像㊁设备树㊁文件系统㊁网络地址㊁加载方式等信息,配置启动方式为Q S P I 启动,Q S P I 的存储文件及地址分配如图5所示㊂图4 Z Y N Q 7000系统启动过程图5 Q S P I 内部存储文件及地址分配3.2 移植L i n u x 内核及生成设备树及文件系统L i n u x 内核是嵌入式系统的关键部分[4]㊂由于嵌入式系统比较精简,通常需要对L i n u x 内核进行裁剪㊂官网下载L i n u x 内核进行相应的配置,编译生成z I m a ge 文件㊂Z Y N Q 7系列芯片的A R M 内核是通过设备树形式的数据结构来配置系统启动的设备参数[5]㊂本设计需要在官方提供的设备树d e v i c e t r e e .d t b 中增加J T A G 接口I P 核的信息,代码如下:&a m b ar a n g e s ; a x i _j t a g _0:a x i j t a g@43C 00000{ c o m p a t i a b l e ="ge n e r i c u i o "; r e g =<0x 43C 000000x 10000>; };};文件系统为嵌入式系统及设备提供文件输入输出等文件管理功能,本设计不展开叙述,编译生成文件系统r a m d i s k 8M.i m a g e .gz 压缩包[6]㊂在启动过程中,u b o o t 会将此文件加载到内存中,并将内存地址传递给内核,待内核启动时,即可同时运行文件系统[7]㊂3.3 X V C 应用程序设计X V C 协议是一种基于T C P /I P 的虚拟线缆协议[8],允许用户通过网络访问X i l i n x F P G A 的J T A G 接口并对其进行高效率的远程更新与调试㊂X V C 协议内容简单,使用方便,其基本内容可总结为如下三条指令[9],如表1所列㊂表1 函数指令功能函数名功 能ge f i n f o ()获取X V C 服务的版本信息㊁t m s 及t d i 字节向量一次能够移位的最大长度s h i f t (n u m b i t s ,t m s v e c t o r ,t d i v e c t o r )以字节向量T M S v e c t o r 和T D I v e c t o r 的形式发送n u m _b i t s 个二进制数给X V C服务器s e t t c k()设置通信协议周期成纳秒,返回值为实际周期值本设计实现的X V C 服务器功能主要通过T C P /I P 协议以及内存映射来进行数据交互㊂首先打开U I O 设备即在系统中生成a x i _j t a g _0的设备,并进行内存映射;然后进行T C P /I P 通信需要的一些初始化的工作,建立通信,通过h a n d l e _d a t a ()函数来交互数据㊂X V C 服务器程序设计如图6所示㊂图6 X V C 服务器程序设计流程图h a n d l e _d a t a ()函数内利用m e m c m p ()及m e m c p y()实现命令识别及应用层与设备的数据交互㊂h a n d l e _d a t a()函数内部设计如图7所示㊂图7 h a n d l e _d a t a()函数流程图X V C 协议具体实现内容如下:由于V i v a d o 软件每次发送s h i f t 指令的最大长度为2048字节,故设置接收缓存区b u f f e r 大小为2048,而发送缓存区r e s u l t 大小为1024㊂网络设置包括创建s o c k e t ()进行网络通信,并设置其通信协议为T C P ,非阻塞模式,端口号为2542,并为其分配I P 地址和MA C 地址㊂打开s o c k e t ()并监听网络连接请求㊂从s o c k e t()接收6个字节数据到缓存区,如果与字符串s h i f t 相同,则继续读取4字节的内容作为n u m _b i t s,并转换为n r _b yt e s ㊂接着按该字节数分别读取T M S v e c t o r 和T D I v e c t o r 到接收缓存区b u f f e r ,之后通过m e m c p y()将数据映射到a x i _j t a g _0设备的寄存器中,a x i _j t a g_0模块将读到的寄存器数据赋值给TM S 和T D I 引脚,同时产生周期性的T C K 信号㊂a x i _j t a g _0模块检测到TD O 引脚上的信号写入寄存器s l v _r e g 3,应用层通过m e m c p y ()读到寄存器,发送给P C ㊂P C 验证收到的T D O 数据无误,继续通过s h i f t 指令发送下一个数据包㊂由此便实现了一个完整的J T A G 数据链路,从而实现远程P C 由网络将配置数据通过模拟的J T A G 接口配置给F P G A 的过程㊂4 测试验证及总结利用V i v a d o 软件中的H a r d w a r e M a n a ge r 进行远程更新,首先通过S D K 软件将系统启动所需要的文件烧写进Z e d b o a r d 平台,启动L i n u x 系统㊂在Z e d b o a r d 运行X V C 服务程序,等待P C 通过网络配置F P G A ㊂在V i v a d o 的T C L c o n s o l e 输入以下命令:>>c o n n e c t _h w _s e r v e r>>o p e n _h w _t a r ge t -x v c _u r l 192.168.1.10:2542从图8中可以看出,已经成功连接到光纤接口板,网络I P 地址为192.168.1.10,端口号为2542㊂图8 实验结果该设计具有可扩展性,可以拓展为多F P G A 远程更新与调试,只需要在逻辑设计时加入多个J T A G 模块,并在X V C 应用层程序中更改相应的设备,即可实现多个F P G A 远程更新与调试㊂随着船用雷达的不断更新换代以及多功能化的实现,设备的更新在所难免,本设计给后续升级提供了可靠便捷的保障,已在某型号舰载设备上使用,对今后工业化设备在线升级算法㊁远程更新程序,具有重要引导意义㊂参考文献[1]陶吉怀.基于S O P C 的船用雷达处理单元研究与设计[D ].成都:电子科技大学,2013.[2]文华武.基于以太网的F P G A 远程程序升级系统的设计与研究[D ].重庆:重庆大学,2012.[3]王利军,张超.基于C P U 实现F P G A 远程更新[J ].信息通信,2013,20(6):4445.[4]薛乾,曾云,张杰.基于X V C 网络协议的多F P G A 远程更新与调试[J ].核技术,2015,38(12).[5]3G P P T S 36.322.R a d i o L i n k C o n t r o l (R T C )pr o t o c o l [S ],2015.[6]余婷婷.嵌入式文件系统的研究与设计[D ].武汉:武汉理工大学,2007.[7]华抒军.基于Z e d b o r a d 的软件无线电软件平台的设计与实现[J ].软件,2015,36(10):5760.[8]X i l i n x .X i l i n x v i r t u a l c a b l e o v e r v i e w ,2015.[9]X i l i n x .X i l i n x v i r t u a l c a b l e r u n n i n g o n Z y n q 7000u s i n g th e pe t a l L i n u x t o o l s ,2015.朱琛(工程师),主要研究方向为F P G A 逻辑设计及嵌入式硬件设计;沈小波(工程师),主要研究方向为雷达信号处理系统;周志刚(工程师),主要研究方向为嵌入式L i n u x 系统及应用㊂(责任编辑:薛士然 收稿日期:2020-06-18)。

arduino操作基础与开流程

arduino操作基础与开流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor.I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!Arduino操作基础与开发流程详解随着物联网技术的发展,Arduino作为一款开源电子原型平台,因其易用性和灵活性,受到了广大爱好者和初学者的热烈欢迎。

zedboard启动流程新

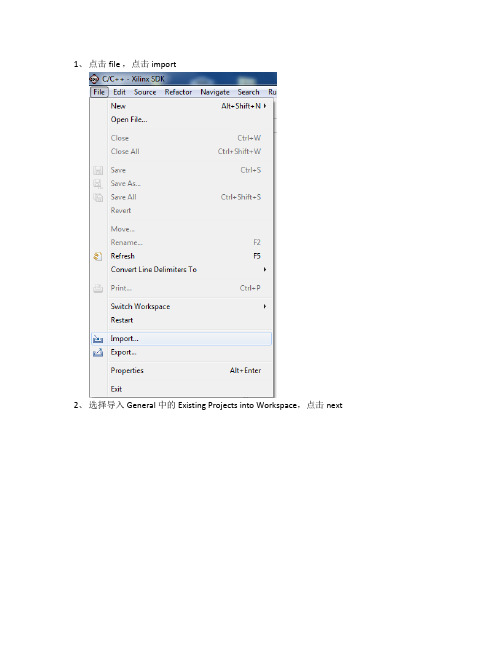

1、点击file ,点击import2、选择导入General 中的Existing Projects into Workspace,点击next3、点击Browse4、选中解压出的NJ-cpu1-src,点击OK5、弹出界面如下图,点击Finish6、在Project Explorer可看到如下界面:7:点击展开app_cpu1,继续点击展开src,双击app_cpu1.c8、此时界面如下:9、点击Xilinx Tools ,点击Creat Zynq Boot Image10、点击browse,选择BIF文件保存位置,取名为zrobot.bif11、一次添加amp_fsbl.elf、system.bit、u-boot.elf、app_cpu1.elf。

前3个文件直接使用提供的,第4个替换成自己编译的文件。

点击add后弹窗如下:12、点击Browse,选中NJ-cpu1-targets中的amp_fsbl.elf,点击Open13、点击OK14、继续点击add,点击Browse,选中NJ-cpu1-targets中的system.bit,点击Open15、点击OK16、继续点击add,点击Browse,选中NJ-cpu1-targets中的u-boot.elf,点击Open17、点击OK18、继续点击add,点击Browse,选中NJ-cpu1-targets中的app_cpu1.elf,点击Open19、点击OK20、create image界面最终如下,可以看到添加的四个文件。

必须按照此顺序修改输出文件名,讲output.bin修改成BOOT.bin21、点击Create Image,Console窗口输出结果如下:下图是SD卡中必要的文件,其中init2.sh是由init.sh文件重命名的。

如果你需要由SD自启动需将此文件修改成init.sh文件名,如果你需要Linux单步调试,则需要将其修改成init2.sh,或者其他名称。

Avnet ZedBoard 7020 开发板说明书

ZedBoard ™KIT INCLUDES-Avnet ZedBoard 7020 baseboard -12 V power supply -4 GB SD Card -Micro-USB cable-USB Adapter: Male Micro-B to Female Standard-A -Getting Started Guide-Xilinx Vivado ® Design Edition license voucher (device locked to 7Z020)ZedBoard ™ is a low-cost development board for the Xilinx Zynq ®-7000 All Programmable SoC. This board containseverything necessary to create a Linux, Android, Windows ® or other OS/RTOS-based design. Additionally, several expansion connectors expose the processing system and programmable logic I/Os for easy user access. T ake advantage of the Zynq-7000 AP SoC’s tightly coupled ARM ® processing system and 7 series programmable logic to create unique and powerful designs with ZedBoard. ZedBoard is supported by the community website where users can collaborate with other engineers also working on Zynq designs.FEATURES-Zynq ®-7000 All Programmable SoC XC7Z020-CLG484-1 -Memory-512 MB DDR3-256 Mb Quad-SPI Flash -4 GB SD card-Onboard USB-JTAG Programming -10/100/1000 Ethernet -USB OTG 2.0 and USB-UART -PS & PL I/O expansion-(FMC, Pmod™ Compatible, XADC)-Multiple displays (1080p HDMI, 8-bit VGA, 128 x 32 OLED) -I2S Audio CODECTARGET APPLICATIONS-Video processing -Motor control -Software acceleration-Linux/Android/RTOS development -Embedded ARM ® processing-General Zynq ®-7000 All Programmable SoC prototyping To purchase this kit, visit BLOCK DIAGRAMAsia151 Lorong Chuan#06-03 New Tech Park Singapore 556741********************+65-6580-6000North America 2211 S 47th StreetPhoenix, Arizona 85034 United States of America *******************1-800-585-1602CONTACT INFORMATIONJapanYebisu Garden Place Tower, 23F 4-20-3 Ebisu, Shibuya-ku Tokyo 150-6023 Japan **********************+81-(0)3-5792-8210EuropeGruber Str. 60c 85586 Poing Germany********************+49-8121-77702FEATURED MANUFACTURERSCopyright © 2017 Avnet, Inc. AVNET, "Reach Further," and the AV logo are registered trademarks of Avnet, Inc. All other brands are the property of their respective owners.LIT# 5066-PB-AES-Z7EV-7Z020-G-V1Countries Available for Purchase: Americas, EMEA, Asia, JapanSPONSORS。

ZedBoard移植嵌入式Linux教程

ZedBoard移植嵌入式Linux教程

1.准备硬件

首先,我们需要准备好ZedBoard开发板以及适配器和连接线,确保电源正常连接。

另外,我们需要一台配有SD卡读卡器的计算机。

3.设置与建立支持文件系统

在SDK中,我们需要创建一个新的应用程序工程,并选择Zynq FSBL 模板作为起点。

然后我们需要按照SDK的指导建立新的设备树文件和根文件系统。

4.配置并构建内核

5.设置并测试启动

完成内核构建后,我们将使用Xilinx SDK生成的文件将ZedBoard启动到U-Boot中。

首先,我们将使用Vivado生成的bit文件和FSBL文件来设置FPGA和启动载入代码。

然后,我们将使用U-Boot设置启动参数并通过TFTP加载内核映像和设备树文件。

最后,我们可以通过串行终端连接到ZedBoard并查看启动输出,确保系统正常启动。

需要注意的是,这仅仅是嵌入式Linux移植的基本步骤。

根据具体情况,可能需要进行更多的定制和调整。

此外,由于涉及到硬件和软件的复杂性,可能需要更深入的了解和经验才能成功完成移植过程。

用zedboard的PS测试简单的嵌入式开发程序

下载完成后程序执行在串口监视窗口会输出“Hello world〞,“1234!〞,“你 好!〞。

最后的“你好பைடு நூலகம்没能输出到终端,具体原因还没有找到。

至此一个简单的ARM Cortex-A9内核的系统已经建立,可以进展软件开发了。

3〕在XPS中设定硬件的配置,与之前版本不一样的地方是右边系统窗口里增加了 Zynq标签页,图形化的表示PS内部框图。图中绿色的局部是可以修改参数也就是 说可以重新配置的。

确定后导入了定义好的Zedboard文件,配置后的框图如下,这是点击绿色图块会发 现逻辑已经设定好。

5〕关闭XPS,又回到PlanAhead窗口。这时在Design Souces下增加了刚刚建立 的.xmp工程。邮件点击.xmp选择Create Top HDL。

上图可以看到system.xml文件包含了硬件平台的配置信息。ps7_init.c和ps7_init.h 中包含了处理器平台硬件的初始化s设置。

7〕接通Zedboard的电源,目前处于等待JTAG变成状态,只有电源指示LED〔LD13〕 变亮。翻开一个串口监视,这里用超级终端来监视,波特率115200、数据位8位、 停顿位1位、奇偶校验无。

8〕选择File->New->Xilinx C Project,弹出窗口建立一个hello_world的例程

其他设置选择默认一直点next,直到完成〔finish〕。

9〕完成之后现在建立了一个Hello_world的小程序,并且自动编译。编译完成后 右键点击hello_world_0,选择Run as->Launch on Hardware将程序下载到Zedboard。

报告内容

利用PS局部建立嵌入式系统

操作步骤

Zedboard学习(七)PS下第一个裸奔程序

Zedboard学习(七)PS下第一个裸奔程序一、打开PlanAhead创建工程1、选择Create New Project新建工程Project name:hello一路默认,只有Board项需要选择ZedBoard Zynq EvaluaTIon and Development KitFinish创建工程之后的界面二、添加资源 1.Click Add Sources in the Project Manager.The Add Sources wizard opens.2.Select the Add or Create Embedded Sources opTIon and click Next.3.In the Add or Create Embedded Source window, click Create Sub-Design.4.Type a name for the module and click OK. For this example, use the name system.The module you created displays in the sources list.5.Click Finish.这个时候XPS会自动打开,硬件相关的配置可以在XPS中进行。

三、在XPS中配置硬件1、The dialog box opens, and asks if you want to create a Base System using the BSB Wizard. Select Yes.The first window of the BSB asks you to elect whether to create an AXI-based or PLB-based system.2.Select AXI System and click OK.3.In the Base System Builder wizard, create a project using the setTIngs described in the table. Where a setTIng or command has not been specified, accept the default values.3 、Remove all peripherals from the list by selecting each one and clicking Remove.4、Click Finish5.Close the XPS window. The active PlanAhead tool session updates itself with the project settings.关闭XPS之后,PlanAhead中会自动更新。

ZedBoard开发板硬件用户手册

ZedBoard(Z ynq™E valuation and D evelopment)Hardware User’s GuideVersion 1.9January 29th, 2013Table of Contents1INTRODUCTION (2)1.1Z YNQ B ANK P IN A SSIGNMENTS (4)2FUNCTIONAL DESCRIPTION (5)2.1A LL P ROGRAMMABLE S O C (5)2.2M EMORY (5)2.2.1DDR3 (5)2.2.2SPI Flash (8)2.2.3SD Card Interface (10)2.3USB (11)2.3.1USB OTG (11)2.3.2USB-to-UART Bridge (11)2.3.3USB-JTAG (12)2.3.4USB circuit protection (13)2.4D ISPLAY AND A UDIO (13)2.4.1HDMI Output (13)2.4.2VGA Connector (16)2.4.3I2S Audio Codec (17)2.4.4OLED (18)2.5C LOCK SOURCES (18)2.6R ESET S OURCES (18)2.6.1Power-on Reset (PS_POR_B) (18)2.6.2Program Push Button Switch (19)2.6.3Processor Subsystem Reset (19)2.7U SER I/O (19)2.7.1User Push Buttons (19)2.7.2User DIP Switches (19)2.7.3User LEDs (20)2.810/100/1000E THERNET PHY (20)2.9E XPANSION H EADERS (21)2.9.1LPC FMC Connector (21)2.9.2Digilent Pmod™ Compatible Headers (2x6) (22)2.9.3Agile Mixed Signaling (AMS) Connector, J2 (23)2.10C ONFIGURATION M ODES (26)2.10.1JTAG (27)2.11P OWER (28)2.11.1Primary Power Input (28)2.11.2On/Off Switch (28)2.11.3Regulators (28)2.11.4Sequencing (29)2.11.5Power Good LED (30)2.11.6Power Estimation (30)2.11.7Testing (31)2.11.8Probes (31)3ZYNQ-7000 AP SOC BANKS (32)3.1Z YNQ-7000AP S O C B ANK V OLTAGES (33)4JUMPER SETTINGS (34)5MECHANICAL (36)1 IntroductionThe ZedBoard is an evaluation and development board based on the Xilinx Zynq TM-7000 All Programmable SoC (AP SoC). Combining a dual Corex-A9 Processing System (PS) with 85,000 Series-7 Programmable Logic (PL) cells, the Zynq-7000 AP SoC can be targeted for broad use in many applications. The ZedBoard’s robust mix of on-board peripherals and expansion capabilities make it an ideal platform for both novice and experienced designers. The features provided by the ZedBoard consist of:·Xilinx® XC7Z020-1CLG484CES Zynq-7000 AP SoCo Primary configuration = QSPI Flasho Auxiliary configuration options§Cascaded JTAG§SD Card·Memoryo512 MB DDR3 (128M x 32)o256 Mb QSPI Flash·Interfaceso USB-JTAG Programming using Digilent SMT1-equivalent circuit§Accesses PL JTAG§PS JTAG pins connected through PS Pmodo10/100/1G Etherneto USB OTG 2.0o SD Cardo USB 2.0 FS USB-UART bridgeo Five Digilent Pmod™ compatible headers (2x6) (1 PS, 4 PL)o One LPC FMCo One AMS Headero Two Reset Buttons (1 PS, 1 PL)o Seven Push Buttons (2 PS, 5 PL)o Eight dip/slide switches (PL)o Nine User LEDs (1 PS, 8 PL)o DONE LED (PL)·On-board Oscillatorso33.333 MHz (PS)o100 MHz (PL)·Display/Audioo HDMI Outputo VGA (12-bit Color)o128x32 OLED Displayo Audio Line-in, Line-out, headphone, microphone·Powero On/Off Switcho12V @ 5A AC/DC regulator·Softwareo ISE® WebPACK Design Softwareo License voucher for ChipScope™ Pro locked to XC7Z020Figure 1 – ZedBoard Block Diagram1.1 Zynq Bank Pin AssignmentsThe following figure shows the Zynq bank pin assignments on the ZedBoard followed by a table that shows the detailed I/O connections.Figure 2 - Zynq Z7020 CLG484 Bank Assignments2 Functional Description2.1 All Programmable SoCThe ZedBoard features a Xilinx Zynq XC7Z020-1CLG484 All Programmable SoC (AP SoC). Initial ZedBoards ship with Engineering Sample "CES" grade silicon. Later shipments will eventually switch to production "C" grade silicon once they become available. The Zynq-7000 AP SoC part markings indicate the silicon grade.2.2 MemoryZynq contains a hardened PS memory interface unit. The memory interface unit includes a dynamic memory controller and static memory interface modules.2.2.1 DDR3The ZedBoard includes two Micron MT41J128M16HA-15E:D DDR3 memory components creating a 32-bit interface. As of August 2012, this device has been marked by Micron for end-of-life. There are several options that Micron offers for a replacement. ZedBoard will likely migrate to the MT41K128M16JT-125 device, although this is pending validation. The DDR3 is connected to the hard memory controller in the Processor Subsystem (PS) as outlined in the Zynq datasheet.The multi-protocol DDR memory controller is configured for 32-bit wide accesses to a 512 MB address space. The PS incorporates both the DDR controller and the associated PHY, including its own set of dedicated I/Os. DDR3 memory interface speeds up to 533MHz (1066Mbs) are supported.The DDR3 uses 1.5V SSTL-compatible inputs. DDR3 Termination is utilized on the ZedBoard. The Zynq-7000 AP SoC and DDR3 have been placed close together keeping traces short and matched.DDR3 on the PS was routed with 40 ohm trace impedance for single-ended signals, and DCI resistors (VRP/VRN) as well as differential clocks set to 80 ohms. Each DDR3 chip needs its own 240-ohm pull-down on ZQ.DDR-VDDQ is set to 1.5V to support the DDR3 devices selected. DDR-VTT is the termination voltage which is ½ DDR-VDDQ. DDR-VREF is a separate buffered output that is equal to ½ nominal DDR-VDDQ. The DDR-VREF is isolated to provide a cleaner reference for the DDR level transitions.The PCB design guidelines outlined in Zynq datasheet must be followed for trace matching, etc.Table 1 - DDR3 ConnectionsSignal Name Description Zynq pin DDR3 pin DDR_CK_P Differential clockoutput N4 J7DDR_CK_N Differential clockoutput N5 K7DDR_CKE Clock enable V3 K9DDR_CS_B Chip select P6 L2DDR_RAS_B RAS row addressselect R5 J3DDR_CAS_B RAS column addressselect P3 K3DDR_WE_B Write enable R4 L3DDR_BA[2:0] Bank address PS_DDR_BA[2:0] BA[2:0] DDR_A[14:0] Address PS_DDR_A[14:0] A[14:0]DDR_ODT Output dynamictermination P5 K1DDR_RESET_B Reset F3 T2DDR_DQ[31:0] I/O Data PS_DDR_[31:0] DDR3_DQ pins DDR_DM[3:0] Data mask PS_DDR_DM[3:0] LDM/UDM x2DDR_DQS_P[3:0] I/O Differential datastrobe PS_DDR_DQS_P[3:0] UDQS/LDQSDDR_DQS_N[3:0] I/O Differential datastrobe PS_DDR_DQS_N[3:0] UDQS#/LDQS#DDR_VRP I/O Used to calibrateinput termination N7 N/ADDR_VRN I/O Used to calibrateinput termination M7 N/ADDR_VREF[1:0] I/O Referencevoltage H7, P7 H1For best DDR3 performance, DRAM training is enabled for write leveling, read gate, and read data eye options in the PS Configuration Tool in Xilinx Platform Studio (XPS). The PS Configuration tools’ Memory Configuration Wizard contains two entries to allow for DQS to Clock Delay and Board Delay information to be specified for each of the four byte lanes. These parameters are specific to every PCB design. Xilinx Answer Record 46778 provides a tool for calculating these parameters by a printed circuit board design engineers. The Excel worksheet file ar46778_board_delay_calc.xlsx included in the answer record provides instructions in the worksheet for calculating these board training details based upon specific trace lengths for certain DDR3 signals. Using the information from the trace length reports pertaining to the DDR3 interface for ZedBoard these delay values can be recreated by following the directions found in the Excel worksheet.The PCB lengths are contained in the ZedBoard PCB trace length reports. The DQS to CLK Delay and Board Delay values are calculated specific to the ZedBoard memory interface PCB design. The AR46778 worksheet allows for up to 4 memory devices to be configured for DDR34x8 flyby topology. Note that ZedBoard is configured for DDR3 2x16 flyby routing topology. The first two clock trace midpoint values (CLK0 and CLK1) are used to represent the Micron device electrically nearest to 7Z020 (IC26) and the second two clock trace midpoint values (CLK2 andCLK3) are used to represent the Micron device electrically furthest from 7Z020 (IC25). The worksheet calculation results are shown in the following table.Table 2 - DDR3 Worksheet CalculationsPin Group Length(mm) Length(mils)PackageLength(mils)TotalLength(mils)PropagationDelay(ps/inch)TotalDelay(ns)DQS toCLKDelay(ns)BoardDelay(ns)CLK0 55.77 2195.9 470 2665.9 160 0.427CLK1 55.77 2195.9 470 2665.9 160 0.427CLK2 41.43 1631.1 470 2101.1 160 0.336CLK3 41.43 1631.1 470 2101.1 160 0.336DQS0 51.00 2008.0 504 2512.0 160 0.402 0.025DQS1 50.77 1998.8 495 2493.8 160 0.399 0.028DQS2 41.59 1637.6 520 2157.6 160 0.345 -0.009DQS3 41.90 1649.4 835 2484.4 160 0.398 -0.061DQ[7:0] 50.63 1993.3 465 2458.3 160 0.393 0.410 DQ[15:8] 50.71 1996.4 480 2476.4 160 0.396 0.411 DQ[23:16] 40.89 1609.9 550 2159.9 160 0.346 0.341 DQ[31:24] 40.58 1597.8 780 2377.8 160 0.380 0.358The DQS to CLK Delay fields in the PS7 DDR Configuration window should be populated usingthe corresponding values from the previous table.The configuration fields of the tool may not allow you to input a negative delay value, this is a known problem with the 14.1 tools and scheduled for correction in the 14.2 tools release. In the case of DQS2 and DQS3 fields for DQS to CLK Delay, simply enter a value of zero rather thanthe negative delay values. This is an acceptable workaround since the calculated values are relatively close to zero and the values provided in these fields are used as initial values for theread/write training for DDR3. Keep in mind for LPDDR2 there is no write leveling, and for DDR2 there is no training whatsoever. In these memory use cases, the accuracy of the trace length infois more important. This is covered in further detail in section 10.6.8 of the Xilinx Zynq TRM,UG585.Figure 3 - DQS to Clock Delay SettingsThe Board Delay fields in the PS7 DDR Configuration window should be populated using the corresponding values from the table above.Figure 4 - DDR3 Board Delay Settings2.2.2 SPI FlashThe ZedBoard features a 4-bit SPI (quad-SPI) serial NOR flash. The Spansion S25FL256S is used on this board. The Multi-I/O SPI Flash memory is used to provide non-volatile code, and data storage. It can be used to initialize the PS subsystem as well as configure the PL subsystem (bitstream). Spansion provides Spansion Flash File System (FFS) for use after booting the Zynq-7000 AP SoC.The relevant device attributes are:·256Mbit·x1, x2, and x4 support·Speeds up to 104 MHz, supporting Zynq configuration rates @ 100 MHzo In Quad-SPI mode, this translates to 400Mbs·Powered from 3.3VThe SPI Flash connects to the Zynq-7000 AP SoC supporting up to Quad-I/O SPI interface. This requires connection to specific pins in MIO Bank 0/500, specifically MIO[1:6,8] as outlined in the Zynq datasheet. Quad-SPI feedback mode is used, thus qspi_sclk_fb_out/MIO[8] is connected to a 20K pull-up resistor to 3.3V. This allows a QSPI clock frequency greater than FQSPICLK2.Note: Zynq only supports 24-bit addressing, however the full capacity of the 256Mb Flash can be accessed via internal bank switching. As of now the S25FL256S is not supported in iMPACT. Note: 14.x is required for in-direct QSPI Flash Programming.Table 3 – QSPI Flash Pin Assignment and DefinitionsSignal Name DescriptionZynq Pin MIO QSPI PinDQ0 Data0 A2 (Bank MIO0/500)1:6 5DQ1 Data1 F6 (MIO Bank 0/500) 2 DQ2 Data2 E4 (MIO Bank 0/500) 3 DQ3 Data3 A3 (MIO Bank 0/500) 7 SCK Serial Data Clock A4 (MIO Bank 0/500) 6 CS Chip Select A1 (MIO Bank 0/500) 1 FB Clock QSPI Feedback E5 (MIO Bank 0/500) 8 N/C Note: The QSPI data and clock pins are shared with the Boot Mode jumpers.Two packages can be used on the ZedBoard; SO-16 and WSON. For the WSON package, there is a heat sink slug under the package that is not connected to any signal on the PCB.Figure 5 - Overlying Packages for SPI Flash2.2.3 SD Card InterfaceThe Zynq PS SD/SDIO peripheral controls communication with the ZedBoard SD Card (A 4GB Class 4 card is included in the ZedBoard kit.) The SD card can be used for non-volatile external memory storage as well as booting the Zynq-7000 AP SoC. PS peripheral sd0 is connected through Bank 1/501 MIO[40-47], including, Card Detect and Write Protect.The SD Card is a 3.3V interface but is connected through MIO Bank 1/501 (1.8V). Therefore, a TI TXS02612 level shifter performs this translation. The TXS02612 is a 2-port SDIO port expander with level translation. ZedBoard only makes use of one of these parts. TI offered an alternative TXS0206 device, but the 0.4mm pitch of that device’s packaging was too fine for our manufacturer.Based on the Zynq TRM, host mode is the only mode supported.The ZedBoard SD Card is connected through a 9-pin standard SD card connector, J12, TE 2041021-1. A Class 4 card or better is recommended.Note: To use the SD Card, JP6 must be shorted.Figure 6 - SD Card InterfaceTable 4 – SD Card Pin Assignment and DefinitionsSignal Name Description Zynq PinMIO Level ShiftPinSD CardPinCLK Clock E14 (MIO Bank1/501)40 Pass-Thru 5CMD Command C8 ((MIO Bank 1/501) 41 Pass-Thru 2Data[3:0] Data MIO Bank 1/501D0: D8D1: B11D2: E13D3: B942:45 Pass-ThruData Pins7891CD Card Detect B10 (MIO Bank1/501)47 Pass-Thru CDWP Write Protect D12 ((MIO Bank1/501)46 Pass-Thru WP2.3 USB2.3.1 USB OTGWarning: After the design of the ZedBoard was complete, a timing incompatibility between the TUSB1210 PHY and Zynq was discovered. The TUSB1210 is not recommended for new designs with Xilinx Zynq. Please refer to the ZedBoard Errata for more details.ZedBoard implements one of the two available PS USB OTG interfaces. An external PHY with an 8-bit ULPI interface is required. A TI TUSB1210 Standalone USB Transceiver Chip is used as the PHY. The PHY features a complete HS-USB Physical Front-End supporting speeds of up to 480Mbs. This part is available in a 32-pin QFN package. VCCio for this device is 1.8V and cannot be connected through level shifters. The PHY is connected to MIO Bank 1/501, which is powered at 1.8V. Additionally the USB chip must clock the ULPI interface which requires an oscillator. A Fox XPRESSO oscillator (767-26-31) is used on ZedBoard.The external USB interface connects through a TE 1981584-1.The usb0 peripheral is used on the PS, connected through MIO[28-39] in MIO Bank 1/501.This USB port will not power the board. However, ZedBoard provides 5V when in Host or OTG modes. REFCLK pin of TUSB1210 is tied to ground as the Zynq-7000 AP SoC will drive the CLOCK input of this part.Table 5 - USB OTG Pin Assignment and DefinitionsSignal Name Description Zynq PinMIO TUSB1210PinUSBConn PinOTG_Data[8:0] USB Data lines MIO Bank 1/50128:39 Data[7:0] N/COTG_CLOCK USB Clock MIO Bank 1/501 26 N/C OTG_DIR ULPI DIR output signal MIO Bank 1/501 31 N/C OTG_STP ULPI STP input signal MIO Bank 1/501 29 N/C OTG_NXT ULPI NXT output signal MIO Bank 1/501 2 N/C OTG_CS USB Chip Select 11 N/C DP DP pin of USB Connector N/C 18 2 DM DM pin of USB Connector N/C 19 3ID Identification pin of theUSB connectorN/C 23 4OTG_RESET_B Reset MIO Bank 1/501 27 N/C OTG_VBUS_OC VBus Output Control Bank 34 L16 TPS2051See the Jumper Settings section for configuring the USB interface for Host, Device and OTG mode. The jumpers control the Vbus supply as well.2.3.2 USB-to-UART BridgeThe ZedBoard implements a USB-to-UART bridge connected to a PS UART peripheral. ACypress CY7C64225 USB-to-UART Bridge device allows connection to a host computer. TheUSB/UART device connects to the USB Micro B connector, J14, (TE 1981584-1) on the board. Only basic TXD/RXD connection is implemented. If flow control is required this can be added through Extended MIO on a PL-Pmod™.Cypress provides royalty-free Virtual COM Port (VCP) drivers which permit the CY7C64225 USB-to-UART bridge to appear as a COM port to host computer communications application software(for example, HyperTerm or Tera Term). Please refer to the CY7C64225 Setup Guide posted on for detailed instructions for installing the driver.The UART 1 Zynq PS peripheral is accessed through MIO[48:49] in MIO Bank 1/501 (1.8V). Since the CY7C64225 device requires either 3.3V or 5V signaling, a TI TXS0102 level shifter is used to level shift between 3.3V and 1.8V.This USB port will not power the board. Therefore, Vbus needs to be connected to 3.3V though a 1KΩ series resistor. The Wake pin, pin 22, connects to GND. A 24Ω series resistor was placed on each of the data lines, D+ and D-.Table 6 – CY7C6 ConnectionsUARTFunction inZynq Zynq Pin MIOSchematic NetNameCY7C6 PinUART Functionin CY7C64225TX, data out D11 (MIO Bank1/501)48:49USB_1_RXD 23 RXD, data inRX, data in C14 (MIO Bank1/501)USB_1_TXD 4 TXD, data outFigure 7 – USB-UART Bridge Interface2.3.3 USB-JTAGThe ZedBoard provides JTAG functionality based on the Digilent USB High Speed JTAG Module, SMT1 device. This USB-JTAG circuitry is fully supported and integrated into Xilinx ISE tools, including iMPACT, ChipScope, and SDK Debugger. Designers who want to re-use this circuit on their board can do so by acquiring these modules from Avnet./en-us/design/drc/Pages/Digilent-JTAG-SMT1-Surface-Mount-Programming-Module.aspxThe JTAG is available through a Micro B USB connector, J17, TE 1981568-1. TCK has a series termination resistor, 20-30Ω, to prevent signal integrity issues.For the JTAG Chain setup, please refer to the Configuration section.2.3.4USB circuit protectionAll USB data lines, D+/-, are protected with a TE SESD0402Q2UG-0020-090. Figure 8 – ESD Protection2.4 Display and Audio2.4.1HDMI OutputAn Analog Devices ADV7511 HDMI Transmitter provides a digital video interface to theZedBoard. This 225MHz transmitter is HDMI 1.4- and DVI 1.0-compatible supporting 1080p60 with 16-bit, YCbCr, 4:2:2 mode color.The ADV7511 supports both S/PDIF and 8-channel I2S audio. The S/PDIF can carry compressed audio including Dolby® Digital, DTS®, and THX®. There is an independent DPDIF input and output. The I2S interface is not connected on ZedBoard. Analog Devices offers Linux drivers and reference designs illustrating how to interface to this device.The HMDI Transmitter has 25 connections to Bank 35 (3.3V) of the Zynq-7000 AP SoC:USB Con nLevel ShifterD+ D-Table 7 - HDMI Interface ConnectionsSignal Name Description Zynq pin ADV7511 pin HDP Hot Plug Detect signal input N/C 30HD-INT Interrupt signal output W16 45HD-SCL I2C Interface. Supports CMOSlogic levels from 1.8V to 3.3V AA18 55HD-SDA Y16 56 HD-CLK Video Clock Input. Supportstypical CMOS logic levels from1.8V up to 3.3VW18 79HD-VSYNC Vertical Sync Input (Not requiredif using embedded syncs)W17 2HD-HSYNC Horizontal Sync Input (Notrequired if using embeddedsyncs)V17 98HD-DE Data Enable signal input forDigital Video (Not required ifusing embedded syncs)U16 97 HD_D[15:0] Video Data Input Bank 35D0: Y13 D1: AA12 D2: AA14 D3: Y14 D4: AB15 D5: AB16 D6: AA16 D7: AB17 D8: AA17 D9: Y15 D10: W13 D11: W15 D12: V15 D13: U17 D14: V14 D15: V13 88 87 86 85 84 83 82 81 80 78 74 73 72 71 70 69HD-SPDIF Sony/Philips Digital InterfaceAudio InputU15 10HD-SPDIFO Sony/Philips Digital InterfaceAudio OutputY18 46Figure 9 - HDMI Video Interface TimingThe HDMI transmitter connects externally via a HDMI Type A connector, J9, TE 1903015-1. Circuit protection for the HDMI interface is provided by a Tyco Electronics SESD0802Q4UG.The ZedBoard also allows 12-bit color video output through a through-hole VGA connector, TE 4-1734682-2. Each color is created from resistor-ladder from four PL pins.Figure 10 - DB15An Analog Devices ADAU1761 Audio Codec provides integrated digital audio processing to the Zynq-7000 AP SoC. It allows for stereo 48KHz record and playback. Sample rates from 8KHz to 96KHz are supported. Additionally, the ADAU1761 provides digital volume control. The Codec can be configured using Analog Devices SigmaStudio™ for optimizing audio for specific acoustics, numerous filters, algorithms and enhancements. Analog Devices provides Linux drivers for this device./en/content/cu_over_sigmastudio_graphical_dev_tool_overview/fca.html The Codec interface to the Zynq-7000 AP SoC consists of the following connections:Table 9 - CODEC ConnectionsSignal Name Description Zynq pin ADAU1761 pinAC-ADR0I2C Address Bit 0/SPI LatchSignalAB1 3AC-ADR1I2C Address Bit 1/SPI DataInputY5 30AC-MCLK Master Clock Input AB2 2AC-GPIO2Digital Audio Bit ClockInput/OutputAA6 28AC-GPIO3Digital Audio Left-Right ClockInput/OutputY6 29AC-GPIO0Digital Audio Serial-Data DACInputY8 27AC-GPIO1Digital Audio Serial Data ADCOutputAA7 26AC-SDA I2C Serial Data interface AB5 31 AC-SCK I2C Serial Data interface AB4 32 The Codec connects to the following connectors:Table 10 - External Codec Connections3.5mm Audio (Mic In) Pink TE 1734152-53.5mm Audio (Line In) Light Blue TE 1734152-63.5mm Audio (Line Out) Lime TE 1734152-43.5mm Audio (Headphone) Black TE 1734152-72.4.4 OLEDAn Inteltronic/Wisechip UG-2832HSWEG04 OLED Display is used on the ZedBoard. This provides a 128x32 pixel, passive-matrix, monochrome display. The display size is 30mm x11.5mm x 1.45mm.Table 11 - OLED ConnectionsPin Number Symbol Zynq Pin FunctionPower Supply7 VDD U12 Power Supply for Logic6 VSS N/C Ground of OEL System15 VCC N/C Power Supply for OEL PanelDriver13 IREF N/C Current Reference for Brightness Adjustment14 VCOMH N/C Voltage Output High Level for COM Signal DC/DC Converter5 VBAT U11 Power Supply for DC/DC Converter Circuit3 /4 1 / 2 C1P / C1NC2P / C2NN/CPositive Terminal of the Flying Inverting CapacitorNegative Terminal of the Flying Boost CapacitorInterface9 RES# U9 Power Reset for Controller and Driver8 CS# N/C Chip Select – Pulled Down on Board10 D/C# U10 Data/Command Control11 SCLK AB12 Serial Clock Input Signal12 SDIN AA12 Serial Data Input Signal2.5 Clock sourcesThe Zynq-7000 AP SoC’s PS subsystem uses a dedicated 33.3333 MHz clock source, IC18, Fox 767-33.333333-12, with series termination. The PS infrastructure can generate up to four PLL-based clocks for the PL system. An on-board 100 MHz oscillator, IC17, Fox 767-100-136,supplies the PL subsystem clock input on bank 13, pin Y9.2.6 Reset Sources2.6.1 Power-on Reset (PS_POR_B)The Zynq PS supports external power-on reset signals. The power-on reset is the master reset of the entire chip. This signal resets every register in the device capable of being reset. ZedBoard drives this signal from a comparator that holds the system in reset until all power supplies are valid. Several other IC’s on ZedBoard are reset by this signal as well.2.6.2 Program Push Button SwitchA PROG push switch, BTN6, toggles Zynq PROG_B. This initiates reconfiguring the PL-subsection by the processor.2.6.3 Processor Subsystem ResetPower-on reset, labeled PS_RST/BTN7, erases all debug configurations. The external system reset allows the user to reset all of the functional logic within the device without disturbing the debug environment. For example, the previous break points set by the user remain valid after system reset. Due to security concerns, system reset erases all memory content within the PS, including the OCM. The PL is also reset in system reset. System reset does not re-sample the boot mode strapping pins.2.7 User I/O2.7.1 User Push ButtonsThe ZedBoard provides 7 user GPIO push buttons to the Zynq-7000 AP SoC; five on the PL-side and two on the PS-side.Pull-downs provide a known default state, pushing each button connects to Vcco.Table 12 - Push Button ConnectionsSignal Name Subsection Zynq pinBTNU PL T18BTNR PL R18BTND PL R16BTNC PL P16BTNL PL N15PB1 PS D13 (MIO 50)PB2 PS C10 (MIO 51)2.7.2 User DIP SwitchesThe ZedBoard has eight user dip switches, SW0-SW7, providing user input. SPDT switches connect the I/O through a 10kΩ resistor to the VADJ voltage supply or GND.Table 13 - DIP Switch ConnectionsSignal Name Zynq pinSW0 F22SW1G22SW2H22SW3F21SW4H19SW5H18SW6H17SW7M152.7.3 User LEDsThe ZedBoard has eight user LEDs, LD0 – LD7. A logic high from the Zynq-7000 AP SoC I/O causes the LED to turn on. LED’s are sourced from 3.3V banks through 390Ω resistors.Table 14 - LED ConnectionsSignal Name Subsection Zynq pinLD0 PL T22 LD1 PL T21 LD2 PL U22 LD3 PL U21 LD4 PL V22 LD5 PL W22 LD6 PL U19 LD7 PL U14 LD9 PSD5 (MIO7)2.8 10/100/1000 Ethernet PHYThe ZedBoard implements a 10/100/1000 Ethernet port for network connection using a Marvell 88E1518 PHY. This part operates at 1.8V. The PHY connects to MIO Bank 1/501 (1.8V) and interfaces to the Zynq-7000 AP SoC via RGMII. The RJ-45 connector is a TE Connectivity1840750-7 featuring integrated magnetics. The RJ-45 has two status indicator LEDs that indicate traffic and valid link state.A high-level block diagram of one 10/100/1000 Ethernet interface is shown in the following figure.Figure 11 - 10/100/1000 Ethernet InterfaceZynq requires a voltage reference for RGMII interfaces. Thus PS_MIO_VREF, F8, is tied to 0.9V, half the bank voltage of MIO Bank 1/501.Table 15 – Ethernet PHY Pin Assignment and DefinitionsSignal Name Description Zynq pin MIO 88E1510 pinRX_CLK Receive Clock A1416:27 40RX_CTRL Receive Control D7 37RXD[3:0] Receive Data RXD0: E11RXD1: B7RXD2: F12RXD3: A1338394142TX_CLK Transmit Clock D6 47 TX_CTRL Transmit Control F11 2TXD[3:0] Transmit Data TXD0: E9TXD1: A7TXD2: E10TXD3: A84445481MDIO Management Data C1252:53 5MDC Management Clock D10 4The datasheet for the Marvell 88E1518 is not available publicly. An NDA is required for this information. Please contact your local Avnet or Marvell representative for assistance.2.9 Expansion Headers2.9.1 LPC FMC ConnectorA single low-pin count (LPC) FMC slot is provided on the ZedBoard to support a large ecosystem of plug-in modules. The LPC FMC exposes 68 single-ended I/O, which can be configured as 34 differential pairs. The FMC interface spans over two PL I/O banks, banks 34 and 35. To meet the FMC spec, these banks are powered from an adjustable voltage set by jumper, J18. Selectable voltages include 1.8V, default, and 2.5V. It is also possible to set Vadj to 3.3V. Since 3.3V could potentially be the most damaging voltage setting for Vadj, this is not available with the default board hardware. To set Vadj to 3.3V, solder a short across the 3V3 pads at J18 or solder in an additional 1x2 header. The FMC pin out can be copied from the Master UCF, see .WARNING: Before attaching a FMC Card, ensure the correct voltage is selected on jumper, J18. Failure to do so may result in damage to the FMC card and/or the ZedBoard.Note, the following LPC FMC connections guidelines were followed:§CLK_#_M2C–50 ohm single-ended impedance–Less than 10mil skew in P/N pair–Connected to GC (Global Clock) preferential or MRCC (Multi-Region) if not available–No length matching to any other feature§LA bus–50 ohm single-ended impedance–Less than 10mil skew in P/N pair–Less than 100mil length skew across all bits in a bus•No restriction between LA, HA or HB–LA Bus 0:16 to be located in one bank–LA Bus 17:33 to be located in one bank–CC Pairs 0, 17 to be placed on MRCC pins–CC Pairs 1, 18 to be placed on SRCC pins•HB_06_CC optional placed on clock pin if available§To conserve Zynq pins, GA[1:0] were removed and connected to GND.。

大数据之hadoop分布式集群初次启动

大数据之hadoop分布式集群初次启动上篇文章中我们通过克隆已有虚拟机并修改相应的参数配置将hadoop分布式集群搭建完成,接下来我们启动Hadoop分布式集群。

1、ssh免密登录首先打开虚拟机软件VMware然后开启master、slave1、slave2三个虚拟机。

一般搭建hadoop分布式集群时需要配置集群中各个节点间的ssh免密登录,然后才可以启动hadoop分布式集群。

我们在master虚拟机终端中输入命令ssh slave1 ,此时出现如下提示,然后输入yes注意输入exit命令退出slave2的登录。

接下来我们就可以远程登录到slave2了。

在登录的过程中我们也无需输入密码。

小伙伴们会不会有疑问,我们什么时候配置过ssh免密登录?其实我们还真的配置了,由于现在集群中的三个虚拟机最终的源头都是由伪分布集群的虚拟机复制过来的,在这过程中也把.ssh 目录下的authorized_keys这个文件复制过来了。

这个文件的作用之前提前过,简单来说就是认证登录ssh服务器的客户机,只要客户机的公钥在这里面就可以不用密码登录ssh服务器了。

下图为slave1节点hduser用户主目录下的.ssh 目录大家可以看到authorized_keys目录已经存在了。

2、格式化HDFS由于我们集群中的虚拟机都是由伪分布集群虚拟机克隆出来的所以会有HDFS相关的目录,而且目录中还有数据,为了不影响格式化操作我们需要将这些目录中的数据都删除,然后再执行格式化。

2.1删除master虚拟机HDFS目录数据输入命令rm -rf tmp/dfs/ 删除dfs目录2.2删除slave1虚拟机HDFS目录数据首先通过ssh slave1登录slave1然后执行rm -rf tmp/dfs/删除slave1 中的dfs目录。

记得exit退出slave1的登录。

2.3删除slave2虚拟机HDFS目录数据删除方式与删除slave1虚拟机HDFS目录的方式一致,这里不再赘述,具体操作可参照下图。

ZedBoard的启动流程(以运行linux操作系统为例)

ZedBoard的启动流程(以运行linux操作系统为例)ZedBoard启动需要的文件:1、BOOT.bin (由fsbl.elf、system.bit、u-boot.elf 组成)2、devicetree.dtb3、uImage4、uramdisk.image.gzZedBoard的启动流程通常可以分为三个步骤:阶段0:在器件上电运行后,处理器会自动执行片内BootROM中的代码,BootROM中的代码是固化的,不可修改。

BootROM中的代码将对zynq的NAND、NOR、SD等基本外设控制器进行初始化,使ARM核可以访问使用这些外设。

而DDR等其他外设将在阶段1之后进行初始化。

同时BootROM的代码还负责将阶段1的启动镜像(fsbl镜像)加载到OCM(zynq片上一个256K的RAM,但在fsbl运行前只能使用其中的192K,所以fsbl要小于192K),然后运行fsbl。

至于从哪个外部存储器中加载fsbl镜像,要看ZedBoard上MIO[5:3]引脚选择哪种启动方式。

一般是选择从SD卡启动(这就是为什么BootROM要先对SD卡等基本外设控制器进行初始化的原因)。

阶段1:该阶段运行的是fsbl代码。

完成的主要工作是根据XPS中的配置,完成PS端的初始化(这一部分应该包括对DDR外设控制器的初始化)使用比特流文件(Bitstream)对PL进行配置(如果不使用PL,就不需要这一步)加载阶段2的代码(ssbl)到内存空间(DDR上),并运行ssbl代码注:fsbl的代码可以直接使用xilinx的SDK软件自动生成(也可根据需要进行修改),步骤很简单。

阶段2:该阶段运行的是ssbl(u-boot.elf),ssbl会完成Linux内核启动之前所必需的硬件初始化,例如串口、USB设备等。

并设置好启动参数,然后将Linux内核、设备树镜像从SD卡加载到内存中。

之后将控制权交给内核。

当Linux内核拥有系统的控制权后,就会先进行初始化,建立内核的运行环境,如进行虚拟地址到物理地址的映射。

ZedBoard_Linux开发_---_GPIO驱动详解ZedBoard 安装 Ubuntu11.04

ZedBoard Linux开发--- GPIO驱动详解下载LOFTER客户端本来这是要作为ZedBoard Linux的第一个学习实例,不过由于一开始实在找不到内核中针对ZedBoard GPIO具体操作的代码在哪里,所以只能先从OLED开始看起,在学习完OLED驱动之后有了不少发现,比如OLED驱动中就有使用GPIO的操作,后来发现这些操作都被Linux内核中的GPIOLIB库管理着,相关的文档在Documentation/gpio.txt中有介绍,通读一遍之后就会有不少发现的,相关的GPIOLIB库文件位于drivers/gpio/gpio-lib.c文件中,不过这部分文件只是提供了库函数,而真正在ZedBoard启动时进行GPIO注册管理的文件是drivers/gpio/gpio-xilinxps.c,可以在这个文件中找到这样一个宏定义:这里一共注册了118个GPIO口,看看Datasheet就知道这里的意思应该是MIO[0:53]+EMIO[54:117],也就是54个MIO加上64个EMIO,看到这里我还是有一些疑问,因为并不是所有的IO口都作为GPIO 来使用的,有很大一部分是进行IO复用的,下面是我在XPS中的MIO配置截图:可以看到MIO中真正作为GPIO口使用的也就只有MIO[0,7,9:15,50:51],我当时就有疑问:如果我在Linux中申请了这一部分被复用的GPIO,这会不会与正在复用的那些功能起冲突?(至少在MCU中有很多复用功能是在配置了GPIO方向之后才能正常复用的)后来看来一下zynq的UG585手册,找到了下面这张图才解决了问题:可以看到所有GPIO与其他复用的功能最后都是经过MIO网络路由到外部的GPIO端口的,也就是说即使在相应的GPIO寄存器中配置了GPIO的功能,那么这部分功能也不会生效!而配置这些复用功能的寄存器是在slcr(System Level Control Registers)寄存器中操作的,可以在UG585上找到这些寄存器具体的参数:而在Digilent Linux内核中,slcr相关的文件可以在linux-digilent/arch/arm/mach-zynq/slcr.c中找到。

Vivado+Zedboard之入门实例精选

Vivado+Zedboard之入门实例精选继续介绍vivado+zedboard入门实例。

均为参照教程实际操作验证成功的实例,在此拿出来与大家分享。

由于教程中步骤已经非常清晰,本文只是简单介绍实例以及试验时的修正记录,具体的教程及个人实现在我的资源中可以找到。

本次介绍的实例为xilinx官网XUP下关于zedboard的实例。

链接为还是先介绍实验环境:环境:win7 64 vivado 2013.2 (从lab23开始切换为vivado2014.1版本)开发板:zedboard version d xc7z020clg484-1串口软件:SecureCRT1. lab2.2 Adding IP cores in PL监测开关值和键值的实例,读取并实时发送当前开关值和键值;增加了两个GPIO IP用于读取开关值和键值。

本例是一个完整的vivado+zedboard软硬件协同设计,可以了解vivado+zedboard开发流程,对zedboard开发板中的开关、按键的控制和使用以及串口通讯有所了解。

2. lab4.1 Building a Complete Embedded System这个例子很好,一个完整的嵌入式系统的例子。

测试Switch0-7和BTNR,可通过GPIO IP通过PL部分对开关和相应LED操作,也可以通过EMIO直接让PS与BTNR通信。

可以阅读下程序,对开关和按键的初始化、控制和使用原理有所了解,对GPIO和EMIO的读写有所了解。

本例最好选用VHDL语言以为本章其他实例准备。

部分步骤需要调整,已经在lab1.pdf中标注了。

需要解决源码中的xdc的问题:换为BNTR,重新create wrapper。

3. lab5.6 Creating a Processor System Lab非常好的实例,建议对zedboard感兴趣者一定试验下。

一个完整的vivado (block design)、SDK(C、download)、HLS(IP)设计实例,使用了Xilinx的IP、第三方IP、用户HLS设计的IP等,进行软硬件协同设计,软、硬件运行时间效果对比(这一点可以体现硬件甚至FPGA的速度优势)等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1、点击file ,点击import2、选择导入General 中的Existing Projects into Workspace,点击next3、点击Browse4、选中解压出的NJ-cpu1-src,点击OK5、弹出界面如下图,点击Finish6、在Project Explorer可看到如下界面:7:点击展开app_cpu1,继续点击展开src,双击app_cpu1.c8、此时界面如下:9、点击Xilinx Tools ,点击Creat Zynq Boot Image10、点击browse,选择BIF文件保存位置,取名为zrobot.bif11、一次添加amp_fsbl.elf、system.bit、u-boot.elf、app_cpu1.elf。

前3个文件直接使用提供的,第4个替换成自己编译的文件。

点击add后弹窗如下:12、点击Browse,选中NJ-cpu1-targets中的amp_fsbl.elf,点击Open13、点击OK14、继续点击add,点击Browse,选中NJ-cpu1-targets中的system.bit,点击Open15、点击OK16、继续点击add,点击Browse,选中NJ-cpu1-targets中的u-boot.elf,点击Open17、点击OK18、继续点击add,点击Browse,选中NJ-cpu1-targets中的app_cpu1.elf,点击Open19、点击OK20、create image界面最终如下,可以看到添加的四个文件。

必须按照此顺序修改输出文件名,讲output.bin修改成BOOT.bin21、点击Create Image,Console窗口输出结果如下:下图是SD卡中必要的文件,其中init2.sh是由init.sh文件重命名的。

如果你需要由SD自启动需将此文件修改成init.sh文件名,如果你需要Linux单步调试,则需要将其修改成init2.sh,或者其他名称。

Linux单步调试时,启动流程如下:运行到某处时,输入红字部分的命令U-Boot 2013.01 (Mar 23 2014 - 16:21:00)DRAM: 384 MiBWARNING: Caches not enabledMMC: zynq_sdhci: 0SF: Detected S25FL256S with page size 64 KiB, total 32 MiB*** Warning - bad CRC, using default environmentIn: serialOut: serialErr: serialNet:000Hit any key to stop autoboot: 0Copying Linux from SD to RAM...Device: zynq_sdhciManufacturer ID: 27OEM: 5048Name: SD04GTran Speed: 50000000Rd Block Len: 512SD version 2.0High Capacity: YesCapacity: 3.7 GiBBus Width: 4-bitreading uImage3362872 bytes read in 456 ms (7 MiB/s)reading devicetree.dtb7321 bytes read in 15 ms (476.6 KiB/s)reading uramdisk.image.gz5315592 bytes read in 711 ms (7.1 MiB/s)## Booting kernel from Legacy Image at 03000000 ...Image Name: Linux-3.8.0-xilinxImage Type: ARM Linux Kernel Image (uncompressed) Data Size: 3362808 Bytes = 3.2 MiBLoad Address: 00008000Entry Point: 00008000Verifying Checksum ... OK## Loading init Ramdisk from Legacy Image at 02000000 ...Image Name:Image Type: ARM Linux RAMDisk Image (gzip compressed)Data Size: 5315528 Bytes = 5.1 MiBLoad Address: 00000000Entry Point: 00000000Verifying Checksum ... OK## Flattened Device Tree blob at 02a00000Booting using the fdt blob at 0x02a00000Loading Kernel Image ... OKOKLoading Ramdisk to 17644000, end 17b55bc8 ... OKLoading Device Tree to 1763f000, end 17643c98 ... OKStarting kernel ...Booting Linux on physical CPU 0x0Linux version 3.8.0-xilinx (sigma@sigma-ThinkPad-R61) (gcc version 4.7.2 (Sourcery CodeBench Lite 2012.09-104) ) #1 SMP PREEMPT Wed Apr 2 01:4CPU: ARMv7 Processor [413fc090] revision 0 (ARMv7), cr=18c5387dCPU: PIPT / VIPT nonaliasing data cache, VIPT aliasing instruction cacheMachine: Xilinx Zynq Platform, model: Xilinx Zynqbootconsole [earlycon0] enabledcma: CMA: reserved 16 MiB at 16400000Memory policy: ECC disabled, Data cache writeallocPERCPU: Embedded 7 pages/cpu @c09aa000 s7616 r8192 d12864 u32768Built 1 zonelists in Zone order, mobility grouping on. Total pages: 97536Kernel command line: console=ttyPS0,115200 root=/dev/ram rw earlyprintk maxcpus=1 coherent_pool=2MPID hash table entries: 2048 (order: 1, 8192 bytes)Dentry cache hash table entries: 65536 (order: 6, 262144 bytes)Inode-cache hash table entries: 32768 (order: 5, 131072 bytes)__ex_table already sorted, skipping sortMemory: 384MB = 384MB totalMemory: 361208k/361208k available, 32008k reserved, 0K highmemVirtual kernel memory layout:vector : 0xffff0000 - 0xffff1000 ( 4 kB)fixmap : 0xfff00000 - 0xfffe0000 ( 896 kB)vmalloc : 0xd8800000 - 0xff000000 ( 616 MB)lowmem : 0xc0000000 - 0xd8000000 ( 384 MB)pkmap : 0xbfe00000 - 0xc0000000 ( 2 MB)modules : 0xbf000000 - 0xbfe00000 ( 14 MB).text : 0xc0008000 - 0xc06094c0 (6150 kB).init : 0xc060a000 - 0xc0633dc0 ( 168 kB).data : 0xc0634000 - 0xc0677ec8 ( 272 kB).bss : 0xc0677ec8 - 0xc06a2bf0 ( 172 kB)Preemptible hierarchical RCU implementation.Dump stacks of tasks blocking RCU-preempt GP.RCU restricting CPUs from NR_CPUS=4 to nr_cpu_ids=2.NR_IRQS:16 nr_irqs:16 16xslcr mapped to d8802000Zynq clock initps7-ttc #0 at d8804000, irq=43sched_clock: 32 bits at 100 Hz, resolution 10000000ns, wraps every 4294967286ms Console: colour dummy device 80x30Calibrating delay loop... 1332.01 BogoMIPS (lpj=6660096)pid_max: default: 32768 minimum: 301Mount-cache hash table entries: 512CPU: Testing write buffer coherency: okCPU0: thread -1, cpu 0, socket 0, mpidr 80000000Setting up static identity map for 0x46db68 - 0x46db9cL310 cache controller enabledl2x0: 8 ways, CACHE_ID 0x000000c0, AUX_CTRL 0x72360000, Cache size: 524288 B Brought up 1 CPUsSMP: Total of 1 processors activated (1332.01 BogoMIPS).devtmpfs: initializedNET: Registered protocol family 16DMA: preallocated 2048 KiB pool for atomic coherent allocationsxgpiops e000a000.ps7-gpio: gpio at 0xe000a000 mapped to 0xd880c000hw-breakpoint: found 5 (+1 reserved) breakpoint and 1 watchpoint registers.hw-breakpoint: maximum watchpoint size is 4 bytes.bio: create slab <bio-0> at 0vgaarb: loadedSCSI subsystem initializedusbcore: registered new interface driver usbfsusbcore: registered new interface driver hubusbcore: registered new device driver usbLinux video capture interface: v2.00pps_core: LinuxPPS API ver. 1 registeredpps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti <giometti@linux.it> PTP clock support registeredcfg80211: Calling CRDA to update world regulatory domainSwitching to clocksource xttcps_clocksourceNET: Registered protocol family 2TCP established hash table entries: 4096 (order: 3, 32768 bytes)TCP bind hash table entries: 4096 (order: 3, 32768 bytes)TCP: Hash tables configured (established 4096 bind 4096)TCP: reno registeredUDP hash table entries: 256 (order: 1, 8192 bytes)UDP-Lite hash table entries: 256 (order: 1, 8192 bytes)NET: Registered protocol family 1RPC: Registered named UNIX socket transport module.RPC: Registered udp transport module.RPC: Registered tcp transport module.RPC: Registered tcp NFSv4.1 backchannel transport module.Trying to unpack rootfs image as initramfs...rootfs image is not initramfs (no cpio magic); looks like an initrdFreeing initrd memory: 5188Khw perfevents: enabled with ARMv7 Cortex-A9 PMU driver, 7 counters availablejffs2: version 2.2. (NAND) (SUMMARY) © 2001-2006 Red Hat, Inc.msgmni has been set to 747io scheduler noop registeredio scheduler deadline registeredio scheduler cfq registered (default)dma-pl330 f8003000.ps7-dma: Loaded driver for PL330 DMAC-267056dma-pl330 f8003000.ps7-dma: DBUFF-128x8bytes Num_Chans-8 Num_Peri-4 Num_Events-16 e0001console [ttyPS0] enabled, bootconsole disabledconsole [ttyPS0] enabled, bootconsole disabledxdevcfg f8007000.ps7-dev-cfg: ioremap f8007000 to d8862000 with size 1000brd: module loadedloop: module loadedxqspips e000d000.ps7-qspi: master is unqueued, this is deprecatedm25p80 spi0.0: found s25fl256s1, expected n25q128m25p80 spi0.0: fallback to 3-byte address modem25p80 spi0.0: maximum accessible size is 16MBm25p80 spi0.0: s25fl256s1 (32768 Kbytes)5 ofpart partitions found on MTD device spi0.0Creating 5 MTD partitions on "spi0.0":0x000000000000-0x000000100000 : "qspi-fsbl-uboot"0x000000100000-0x000000600000 : "qspi-linux"0x000000600000-0x000000620000 : "qspi-device-tree"0x000000620000-0x000000c00000 : "qspi-rootfs"0x000000c00000-0x000001000000 : "qspi-bitstream"xqspips e000d000.ps7-qspi: at 0xE000D000 mapped to 0xD8864000, irq=51e1000e: Intel(R) PRO/1000 Network Driver - 2.1.4-ke1000e: Copyright(c) 1999 - 2012 Intel Corporation.libphy: XEMACPS mii bus: probedxemacps e000b000.ps7-ethernet: pdev->id -1, baseaddr 0xe000b000, irq 54usbcore: registered new interface driver rtl8187usbcore: registered new interface driver rtl8192cuehci_hcd: USB 2.0 'Enhanced' Host Controller (EHCI) Driverehci-pci: EHCI PCI platform driverULPI transceiver vendor/product ID 0x0451/0x1507Found TI TUSB1210 ULPI transceiver.ULPI integrity check: passed.xusbps-ehci xusbps-ehci.0: Xilinx PS USB EHCI Host Controllerxusbps-ehci xusbps-ehci.0: new USB bus registered, assigned bus number 1 xusbps-ehci xusbps-ehci.0: irq 53, io mem 0x00000000xusbps-ehci xusbps-ehci.0: USB 2.0 started, EHCI 1.00hub 1-0:1.0: USB hub foundhub 1-0:1.0: 1 port detectedInitializing USB Mass Storage driver...usbcore: registered new interface driver usb-storageUSB Mass Storage support registered.mousedev: PS/2 mouse device common for all micei2c /dev entries driverusbcore: registered new interface driver uvcvideoUSB Video Class driver (1.1.1)gspca_main: v2.14.0 registeredxadcps f8007100.ps7-xadc: Failed to request memory regionsdhci: Secure Digital Host Controller Interface driversdhci: Copyright(c) Pierre Ossmansdhci-pltfm: SDHCI platform and OF driver helpermmc0: SDHCI controller on e0100000.ps7-sdio [e0100000.ps7-sdio] using ADMAusbcore: registered new interface driver usbhidusbhid: USB HID core driverTCP: cubic registeredNET: Registered protocol family 17lib80211: common routines for IEEE802.11 driversVFP support v0.3: implementor 41 architecture 3 part 30 variant 9 rev 4Registering SWP/SWPB emulation handlerdmatest: Started 1 threads using dma0chan0dmatest: Started 1 threads using dma0chan1dmatest: Started 1 threads using dma0chan2dmatest: Started 1 threads using dma0chan3dmatest: Started 1 threads using dma0chan4dmatest: Started 1 threads using dma0chan5dmatest: Started 1 threads using dma0chan6dmatest: Started 1 threads using dma0chan7drivers/rtc/hctosys.c: unable to open rtc device (rtc0)RAMDISK: gzip image found at block 0mmc0: new high speed SDHC card at address 0007mmcblk0: mmc0:0007 SD04G 3.70 GiBmmcblk0: p1usb 1-1: new high-speed USB device number 2 using xusbps-ehciuvcvideo: Found UVC 1.00 device Webcam C170 (046d:082b)input: Webcam C170 as /devices/amba.0/e0002000.ps7-usb/xusbps-ehci.0/usb1/1-1/1-1:1.0/input/input0EXT3-fs (ram0): warning: feature flags set on rev 0 fs, running e2fsck is recommendedEXT2-fs (ram0): warning: feature flags set on rev 0 fs, running e2fsck is recommended VFS: Mounted root (ext2 filesystem) on device 1:0.devtmpfs: mountedFreeing init memory: 164KStarting rcS...++ Mounting filesystem++ Setting up mdev++ Starting telnet daemon++ Starting http daemon++ Starting ftp daemon++ Starting ssh daemonrcS Complete当运行到此处输入如下命令:zynq> mount -o loop /mnt/cv.image /tmp/EXT3-fs (loop0): error: couldn't mount because of unsupported optional features (240) EXT2-fs (loop0): error: couldn't mount because of unsupported optional features (244) EXT4-fs (loop0): warning: maximal mount count reached, running e2fsck is recommended EXT4-fs (loop0): recovery completeEXT4-fs (loop0): mounted filesystem with ordered data mode. Opts: (null)当运行到此处输入如下命令:zynq> chroot /tmp/\e[0;31mzynq>\e[m suroot@(none):/# cd /root/root@(none):~# rwmem 0xfffffff0 0x18000000root@(none):~# rwmem 0xffff80000x00000000ffff8000 = 0x00000007root@(none):~# rwmem 0xffff80000x00000000ffff8000 = 0x00000009root@(none):~# rwmem 0xffff80000x00000000ffff8000 = 0x0000000broot@(none):~# ./NumRecogusb 1-1: reset high-speed USB device number 2 using xusbps-ehci VIDIOC_QUERYMENU: Invalid argumentVIDIOC_QUERYMENU: Invalid argumentVIDIOC_QUERYMENU: Invalid argumentVIDIOC_QUERYMENU: Invalid argumentVIDIOC_QUERYMENU: Invalid argumentVIDIOC_QUERYMENU: Invalid argumentVIDIOC_QUERYMENU: Invalid argumentflag reset done!flag = 0。