STM32F030F4 时钟树

stm32时钟概念

STM32时钟概念1. 引言STM32是一款由意法半导体(STMicroelectronics)推出的32位单片机系列,广泛应用于各种嵌入式系统中。

在STM32的开发过程中,时钟是一个非常重要的概念,它影响着系统的性能、功耗和稳定性。

本文将详细介绍STM32时钟概念中的关键概念,包括时钟树、主时钟源、系统时钟等,并解释其定义、重要性和应用。

2. 时钟树2.1 定义时钟树是指将外部晶振或者其他主时钟源通过分频器、倍频器等电路分配给各个模块和外设的一系列信号链路。

在STM32中,时钟树起到了提供精确时间基准以及同步各个模块工作的作用。

2.2 重要性时钟树在STM32系统中扮演着至关重要的角色。

首先,它为整个系统提供了统一的时间基准,保证了各个模块之间工作的协调性和稳定性。

其次,通过合理设计时钟树可以提高系统的灵活性和可扩展性,使得不同模块可以根据需求选择不同的时钟源。

此外,时钟树还可以通过合理的分频和倍频设置来控制系统的功耗。

2.3 应用在STM32开发中,我们经常需要配置时钟树来满足不同系统需求。

下面是一些常见的应用场景:•配置系统时钟源:可以选择外部晶振、内部RC振荡器或者其他外设作为系统时钟源,根据实际需求进行配置。

•分频和倍频设置:可以通过分频器和倍频器来调整系统时钟频率,从而满足不同模块对时钟精度和速度的要求。

•使能外设时钟:每个外设都有自己的时钟使能位,需要根据实际使用情况使能或禁用相应的外设时钟。

3. 主时钟源3.1 定义主时钟源是指供给STM32系统整体工作的主要时钟信号源。

在STM32中,主要有以下几种主时钟源:•外部晶振(HSE):通过将外部晶振连接到MCU上提供稳定的高精度时钟信号。

•内部RC振荡器(HSI):MCU内部集成了一个低功耗高精度的RC振荡器。

•PLL锁相环:通过对主时钟源进行倍频和分频,可以得到更高频率的时钟信号。

3.2 重要性主时钟源是整个STM32系统的基础,它直接影响着系统的性能和稳定性。

STM32F4时钟树概述

STM32F4时钟树概述STM32F4 相对于 STM32F1 来说,时钟部分复杂了很多, STM32F4 的时钟配置,我们提供两个函数: Sys_Clock_Set 和Stm32_Clock_Init。

其中 Sys_Clock_Set 是核⼼的系统时钟配置函数,由 Stm32_Clock_Init 调⽤,实现对系统时钟的配置。

外部程序,⼀般调⽤ Stm32_Clock_Init函数来配置时钟。

sys⽂件夹中在 STM32F4 中,有 5 个最重要的时钟源,为 HSI、 HSE、 LSI、 LSE、 PLL。

其中 PLL 实际是分为两个时钟源,分别为主 PLL 和专⽤PLL。

从时钟频率来分可以分为⾼速时钟源和低速时钟源,在这 5 个中 HSI, HSE 以及 PLL 是⾼速时钟, LSI 和 LSE 是低速时钟。

从来源可分为外部时钟源和内部时钟源,外部时钟源就是从外部通过接晶振的⽅式获取时钟源,其中 HSE 和LSE 是外部时钟源,其他的是内部时钟源。

①、 LSI 是低速内部时钟, RC 振荡器,频率为 32kHz 左右。

供独⽴看门狗和⾃动唤醒单元使⽤。

②、 LSE 是低速外部时钟,接频率为 32.768kHz 的⽯英晶体。

这个主要是 RTC 的时钟源。

③、 HSE 是⾼速外部时钟,可接⽯英/陶瓷谐振器,或者接外部时钟源,频率范围为 4MHz~26MHz。

我们的开发板接的是 8M 的晶振。

HSE 也可以直接做为系统时钟或者 PLL 输⼊。

④、 HSI 是⾼速内部时钟, RC 振荡器,频率为 16MHz。

可以直接作为系统时钟或者⽤作 PLL输⼊。

⑤、 PLL 为锁相环倍频输出。

STM32F4 有两个 PLL:1)主 PLL(PLL)由 HSE 或者 HSI 提供时钟信号,并具有两个不同的输出时钟。

第⼀个输出 PLLP ⽤于⽣成⾼速的系统时钟(最⾼ 168MHz)第⼆个输出 PLLQ ⽤于⽣成 USB OTG FS 的时钟(48MHz),随机数发⽣器的时钟和 SDIO时钟。

stm32时钟树分析

void RCC_Configuration(void){/* RCC system reset(for debug purpose) */ RCC_DeInit();/* Enable HSE */RCC_HSEConfig(RCC_HSE_ON);/* Wait till HSE is ready */HSEStartUpStatus = RCC_WaitForHSEStartUp();if(HSEStartUpStatus == SUCCESS){/* Enable Prefetch Buffer */FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);/* Flash 2 wait state */FLASH_SetLatency(FLASH_Latency_2);/* HCLK = SYSCLK */RCC_HCLKConfig(RCC_SYSCLK_Div1);/* PCLK2 = HCLK */RCC_PCLK2Config(RCC_HCLK_Div1);/* PCLK1 = HCLK/2 */RCC_PCLK1Config(RCC_HCLK_Div2);/* PLLCLK = 8MHz * 9 = 72 MHz */RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9);/* Enable PLL */RCC_PLLCmd(ENABLE);/* Wait till PLL is ready */while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET){}/* Select PLL as system clock source */RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);/* Wait till PLL is used as system clock source */while(RCC_GetSYSCLKSource() != 0x08){}}}systemclock共有三个来源,上面代码最后RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);应该是选择PLLCLK为时钟源void RCC_Configuration(void){/* RCC system reset(for debug purpose) */RCC_DeInit();/* Enable HSE */RCC_HSEConfig(RCC_HSE_ON); ------------SHE外部晶振起震(8M)/* Wait till HSE is ready */HSEStartUpStatus = RCC_WaitForHSEStartUp();if(HSEStartUpStatus == SUCCESS) --------------起震成功配置,flash取指令设置{/* Enable Prefetch Buffer */FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);/* Flash 2 wait state */FLASH_SetLatency(FLASH_Latency_2);/* HCLK = SYSCLK */RCC_HCLKConfig(RCC_SYSCLK_Div1); --------------AHB总线不分频/* PCLK2 = HCLK */RCC_PCLK2Config(RCC_HCLK_Div1); --------------APB2总线不分频/* PCLK1 = HCLK/2 */RCC_PCLK1Config(RCC_HCLK_Div2); --------------APB1总线二分频/* PLLCLK = 8MHz * 9 = 72 MHz */RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9); -----PLLCLK =8MHz * 9 = 72 MHz/* Enable PLL */RCC_PLLCmd(ENABLE); --------------- PLL 使能/* Wait till PLL is ready */while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET){}/* Select PLL as system clock source */RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK); -------选择PLLCLK为系统时钟systemclk/* Wait till PLL is used as system clock source */while(RCC_GetSYSCLKSource() != 0x08){}}}从这里可以看到最后AHB时钟为72M(最大也是72M);APB2时钟72M(最大也是72M);APB1时钟36M(最大也是36M);所以可以得到APB2预分频系数为1;APB1预分频系数为2。

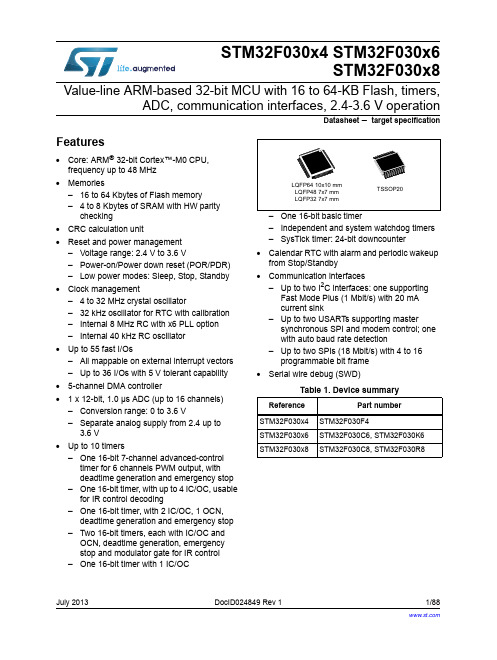

STM32F030F4数据手册

July 2013DocID024849 Rev 11/88STM32F030x4 STM32F030x6STM32F030x8Value-line ARM-based 32-bit MCU with 16 to 64-KB Flash, timers,ADC, communication interfaces, 2.4-3.6 V operationDatasheet target specificationFeaturesCore: ARM ® 32-bit Cortex™-M0 CPU, frequency up to 48 MHz Memories–16 to 64 Kbytes of Flash memory– 4 to 8Kbytes of SRAM with HW parity checking CRC calculation unitReset and power management –Voltage range: 2.4V to 3.6V–Power-on/Power down reset (POR/PDR)–Low power modes: Sleep, Stop, Standby Clock management– 4 to 32 MHz crystal oscillator–32kHz oscillator for RTC with calibration –Internal 8MHz RC with x6 PLL option –Internal 40kHz RC oscillator Up to 55 fast I/Os–All mappable on external interrupt vectors –Up to 36 I/Os with 5V tolerant capability 5-channel DMA controller1 x 12-bit, 1.0µs ADC (up to 16 channels)–Conversion range: 0 to 3.6V–Separate analog supply from 2.4 up to 3.6V Up to 10 timers–One 16-bit 7-channel advanced-control timer for 6 channels PWM output, with deadtime generation and emergency stop –One 16-bit timer, with up to 4 IC/OC, usable for IR control decoding–One 16-bit timer, with 2 IC/OC, 1 OCN, deadtime generation and emergency stop –Two 16-bit timers, each with IC/OC and OCN, deadtime generation, emergency stop and modulator gate for IR control –One 16-bit timer with 1 IC/OC–Independent and system watchdog timers –SysTick timer: 24-bit downcounterCalendar RTC with alarm and periodic wakeup from Stop/Standby Communication interfaces–Up to two I 2C interfaces: one supporting Fast Mode Plus (1Mbit/s) with 20mA current sink–Up to two USARTs supporting mastersynchronous SPI and modem control; one with auto baud rate detection–Up to two SPIs (18Mbit/s) with 4 to 16 programmable bit frame Serial wire debug (SWD)Table 1. Device summaryReferencePart numberSTM32F030x4STM32F030F4STM32F030x6STM32F030C6, STM32F030K6STM32F030x8STM32F030C8, STM32F030R8Contents1Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93Functional overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123.1ARM® CortexTM-M0 core with embedded Flash and SRAM . . . . . . . . . 123.2Memories . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123.3Boot modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123.4Cyclic redundancy check calculation unit (CRC) . . . . . . . . . . . . . . . . . . . 133.5Power management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133.5.1Power supply schemes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133.5.2Power supply supervisors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133.5.3Voltage regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133.5.4Low-power modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143.6Clocks and startup . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143.7General-purpose inputs/outputs (GPIOs) . . . . . . . . . . . . . . . . . . . . . . . . . 163.8Direct memory access controller (DMA) . . . . . . . . . . . . . . . . . . . . . . . . . . 163.9Interrupts and events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163.9.1Nested vectored interrupt controller (NVIC) . . . . . . . . . . . . . . . . . . . . . . 163.9.2Extended interrupt/event controller (EXTI) . . . . . . . . . . . . . . . . . . . . . . 163.10Analog to digital converter (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173.10.1Temperature sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173.10.2Internal voltage reference (V REFINT) . . . . . . . . . . . . . . . . . . . . . . . . . . . 173.11Timers and watchdogs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183.11.1Advanced-control timer (TIM1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183.11.2General-purpose timers (TIM3, TIM14..17) . . . . . . . . . . . . . . . . . . . . . . 193.11.3Basic timer TIM6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193.11.4Independent watchdog (IWDG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193.11.5System window watchdog (WWDG) . . . . . . . . . . . . . . . . . . . . . . . . . . . 203.11.6SysTick timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203.12Real-time clock (RTC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203.13Inter-integrated circuit interfaces (I2C) . . . . . . . . . . . . . . . . . . . . . . . . . . . 213.14Universal synchronous/asynchronous receiver transmitters (USART) . . 22 2/88DocID024849 Rev 13.15Serial peripheral interface (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223.16Serial wire debug port (SW-DP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224Pinouts and pin descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 5Memory mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 336Electrical characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366.1Parameter conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366.1.1Minimum and maximum values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366.1.2Typical values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366.1.3Typical curves . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366.1.4Loading capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366.1.5Pin input voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366.1.6Power supply scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 376.1.7Current consumption measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . 386.2Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 386.3Operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 406.3.1General operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 406.3.2Operating conditions at power-up / power-down . . . . . . . . . . . . . . . . . . 416.3.3Embedded reset and power control block characteristics . . . . . . . . . . . 416.3.4Embedded reference voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 416.3.5Supply current characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 426.3.6Wakeup time from low-power mode . . . . . . . . . . . . . . . . . . . . . . . . . . . 476.3.7External clock source characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 486.3.8Internal clock source characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 526.3.9PLL characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 536.3.10Memory characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 546.3.11EMC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 546.3.12Electrical sensitivity characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . 566.3.13I/O current injection characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . 576.3.14I/O port characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 576.3.15NRST pin characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 626.3.1612-bit ADC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 646.3.17Temperature sensor characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . 676.3.18Timer characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 676.3.19Communication interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69DocID024849 Rev 13/887Package characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 747.1Package mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 747.2Thermal characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 837.2.1Reference document . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 837.2.2Selecting the product temperature range . . . . . . . . . . . . . . . . . . . . . . . 83 8Part numbering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86 9Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 874/88DocID024849 Rev 1STM32F030x4 STM32F030x6 STM32F030x8List of tables List of tablesTable 1.Device summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Table 2.STM32F030x device features and peripheral counts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 Table 3.Temperature sensor calibration values. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Table 4.Internal voltage reference calibration values . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 Table 5.Timer feature comparison. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 Table parison of I2C analog and digital filters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Table 7.STM32F030x I2C implementation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Table 8.STM32F030x USART implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Table 9.STM32F030x SPI implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 Table 10.Legend/abbreviations used in the pinout table. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Table 11.Pin definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 Table 12.Alternate functions selected through GPIOA_AFR registers for port A . . . . . . . . . . . . . . . 31 Table 13.Alternate functions selected through GPIOB_AFR registers for port B . . . . . . . . . . . . . . . 32 Table 14.STM32F030x peripheral register boundary addresses. . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 Table 15.Voltage characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38 Table 16.Current characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39 Table 17.Thermal characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39 Table 18.General operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40 Table 19.Operating conditions at power-up / power-down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41 Table 20.Embedded reset and power control block characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . 41 Table 21.Embedded internal reference voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41 Table 22.Typical and maximum current consumption from V DD supply at VDD= 3.6 . . . . . . . . . . . 43 Table 23.Typical and maximum current consumption from the V DDA supply . . . . . . . . . . . . . . . . . . 43 Table 24.Typical and maximum V DD consumption in Stop and Standby modes. . . . . . . . . . . . . . . . 44 Table 25.Typical and maximum V DDA consumption in Stop and Standby modes. . . . . . . . . . . . . . . 44 Table 26.Typical current consumption in Run mode, code with data processingrunning from Flash . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45 Table 27.Switching output I/O current consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47 Table 28.Low-power mode wakeup timings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47 Table 29.High-speed external user clock characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48 Table 30.Low-speed external user clock characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49 Table 31.HSE oscillator characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 Table 32.LSE oscillator characteristics (f LSE = 32.768 kHz) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51 Table 33.HSI oscillator characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52 Table 34.HSI14 oscillator characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53 Table 35.LSI oscillator characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53 Table 36.PLL characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54 Table 37.Flash memory characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54 Table 38.Flash memory endurance and data retention. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54 Table 39.EMS characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55 Table 40.EMI characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56 Table 41.ESD absolute maximum ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56 Table 42.Electrical sensitivities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56 Table 43.I/O current injection susceptibility. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57 Table 44.I/O static characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57 Table 45.Output voltage characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60 Table 46.I/O AC characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61 Table 47.NRST pin characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62DocID024849 Rev 15/88List of tables STM32F030x4 STM32F030x6 STM32F030x8 Table 48.ADC characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64 Table 49.R AIN max for f ADC = 14 MHz. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65 Table 50.ADC accuracy. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65 Table 51.TS characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67 Table 52.TIMx characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67 Table 53.IWDG min/max timeout period at 40 kHz (LSI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68 Table 54.WWDG min-max timeout value @48 MHz (PCLK). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68 Table 55.I2C characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69 Table 56.I2C analog filter characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70 Table 57.SPI characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71 Table 58.LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package mechanical data. . . . . . . . . . 75 Table 59.LQFP48 – 7 x 7 mm, 48-pin low-profile quad flat package mechanical data . . . . . . . . . . . 77 Table 60.LQFP32 – 7 x 7mm 32-pin low-profile quad flat package mechanical data . . . . . . . . . . . . 79 Table 61.TSSOP20 – 20-pin thin shrink small outline package mechanical data . . . . . . . . . . . . . . . 81 Table 62.Package thermal characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83 Table 63.Ordering information scheme. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86 Table 64.Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87 6/88DocID024849 Rev 1STM32F030x4 STM32F030x6 STM32F030x8List of figures List of figuresFigure 1.Block diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 Figure 2.Clock tree . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15 Figure 3.LQFP64 64-pin package pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23 Figure 4.LQFP48 48-pin package pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 Figure 5.LQFP32 32-pin package pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 Figure 6.TSSOP20 package pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 Figure 7.STM32F030x memory map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 Figure 8.Pin loading conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 Figure 9.Pin input voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 Figure 10.Power supply scheme. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37 Figure 11.Current consumption measurement scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38 Figure 12.High-speed external clock source AC timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48 Figure 13.Low-speed external clock source AC timing diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49 Figure 14.Typical application with an 8 MHz crystal. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51 Figure 15.Typical application with a 32.768 kHz crystal. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52 Figure 16.TC and TTa I/O input characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59 Figure 17.Five volt tolerant (FT and FTf) I/O input characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . 59 Figure 18.I/O AC characteristics definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62 Figure 19.Recommended NRST pin protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63 Figure 20.ADC accuracy characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66 Figure 21.Typical connection diagram using the ADC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66 Figure 22.I2C bus AC waveforms and measurement circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70 Figure 23.SPI timing diagram - slave mode and CPHA = 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72 Figure 24.SPI timing diagram - slave mode and CPHA = 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72 Figure 25.SPI timing diagram - master mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73 Figure 26.LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package outline . . . . . . . . . . . . . . . . . 75 Figure 27.LQFP64 recommended footprint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76 Figure 28.LQFP48 – 7 x 7 mm, 48 pin low-profile quad flat package outline. . . . . . . . . . . . . . . . . . . 77 Figure 29.LQFP48 recommended footprint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78 Figure 30.LQFP32 – 7 x 7mm 32-pin low-profile quad flat package outline. . . . . . . . . . . . . . . . . . . . 79 Figure 31.LQFP32 recommended footprint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80 Figure 32.TSSOP20 - 20-pin thin shrink small outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81 Figure 33.TSSOP20 recommended footprint . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82 Figure 34.LQFP64 P D max vs. T A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85DocID024849 Rev 17/88Introduction STM32F030x4 STM32F030x6 STM32F030x8 1 IntroductionThis datasheet provides the ordering information and mechanical device characteristics ofthe STM32F030x microcontrollers.This STM32F030x4, STM32F030x6, and STM32F030x8 datasheet should be read inconjunction with the STM32F0xxxx reference manual (RM0091). The reference manual isavailable from the STMicroelectronics website .For information on the ARM Cortex™-M0 core, please refer to the Cortex™-M0 TechnicalReference Manual, available from the website at the following address:/help/index.jsp?topic=/com.arm.doc.ddi0432c/index.html.8/88DocID024849 Rev 1STM32F030x4 STM32F030x6 STM32F030x8Description 2 DescriptionThe STM32F030x microcontroller incorporates the high-performance ARM Cortex™-M0 32-bit RISC core operating at a 48 MHz frequency, high-speed embedded memories (up to64Kbytes of Flash memory and up to 8 Kbytes of SRAM), and an extensive range ofenhanced peripherals and I/Os. All devices offer standard communication interfaces (up totwo I2Cs, up to two SPIs, and up to two USARTs), one 12-bit ADC, up to 6 general-purpose16-bit timers and an advanced-control PWM timer.The STM32F030x microcontroller operates in the -40 to +85 °C temperature range, from a2.4 to3.6 V power supply. A comprehensive set of power-saving modes allows the design oflow-power applications.The STM32F030x microcontroller includes devices in four different packages ranging from20 pins to 64 pins. Depending on the device chosen, different sets of peripherals areincluded. The description below provides an overview of the complete range ofSTM32F030x peripherals proposed.These features make the STM32F030x microcontroller suitable for a wide range ofapplications such as application control and user interfaces, handheld equipment, A/Vreceivers and digital TV, PC peripherals, gaming platforms, e-bikes, consumer appliances,printers, scanners, alarm systems, video intercoms, and HVACs.DocID024849 Rev 19/88DescriptionSTM32F030x4 STM32F030x6 STM32F030x810/88DocID024849 Rev 1Table 2. STM32F030x device features and peripheral countsPeripheralSTM32F030F4STM32F030K6STM32F030C6/C8STM32F030R8Flash (Kbytes)1632326464SRAM (Kbytes)44488TimersAdvanced control1 (16-bit)General purpose 4 (16-bit)(1)4 (16-bit)(1)4 (16-bit)(1)5 (16-bit) 5 (16-bit)Basic --- 1 (16-bit)1 (16-bit)Comm. interfacesSPI1(2)1(2)1(2)22I 2C 1(3)1(3)1(3)22USART1(4)1(4)1(4)2212-bit synchronized ADC (number of channels)1(11 channels)1(12 channels)1(12 channels)1(18 channels)GPIOs15263955Max. CPU frequency 48 MHz Operating voltage 2.4 to 3.6VOperating temperature Ambient operating temperature: -40 °C to 85 °CPackagesTSSOP20LQFP32LQFP48LQFP641.TIM15 is not present.2.SPI2 is not present.3.I2C2 is not present.ART2 is not present.STM32F030x4 STM32F030x6 STM32F030x8Description1.TIMER6, TIMER15, SPI2, USART2 and I2C2 are available on STM32F030x8 devices only.DocID024849 Rev 111/88Functional overview STM32F030x4 STM32F030x6 STM32F030x8 3 Functional overview3.1 ARM® Cortex TM-M0 core with embedded Flash and SRAMThe ARM Cortex™-M0 processor is the latest generation of ARM processors for embeddedsystems. It has been developed to provide a low-cost platform that meets the needs of MCUimplementation, with a reduced pin count and low-power consumption, while deliveringoutstanding computational performance and an advanced system response to interrupts.The ARM Cortex™-M0 32-bit RISC processor features exceptional code-efficiency,delivering the high-performance expected from an ARM core in the memory size usuallyassociated with 8- and 16-bit devices.The STM32F0xx family has an embedded ARM core and is therefore compatible with allARM tools and software.Figure1 shows the general block diagram of the device family.3.2 MemoriesThe device has the following features:Up to 8 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states and featuring embedded parity checking with exception generation for fail-critical applications.The non-volatile memory is divided into two arrays:–16 to 64 Kbytes of embedded Flash memory for programs and data–Option bytesThe option bytes are used to write-protect the memory (with 4 KB granularity) and/orreadout-protect the whole memory with the following options:–Level 0: no readout protection–Level 1: memory readout protection, the Flash memory cannot be read from or written to if either debug features are connected or boot in RAM is selected –Level 2: chip readout protection, debug features (Cortex-M0 serial wire) and boot in RAM selection disabled3.3 Boot modesAt startup, the boot pin and boot selector option bit are used to select one of three bootoptions:Boot from User FlashBoot from System MemoryBoot from embedded SRAMThe boot loader is located in System Memory. It is used to reprogram the Flash memory byusing USART on pins PA14/PA15 or PA9/PA10.。

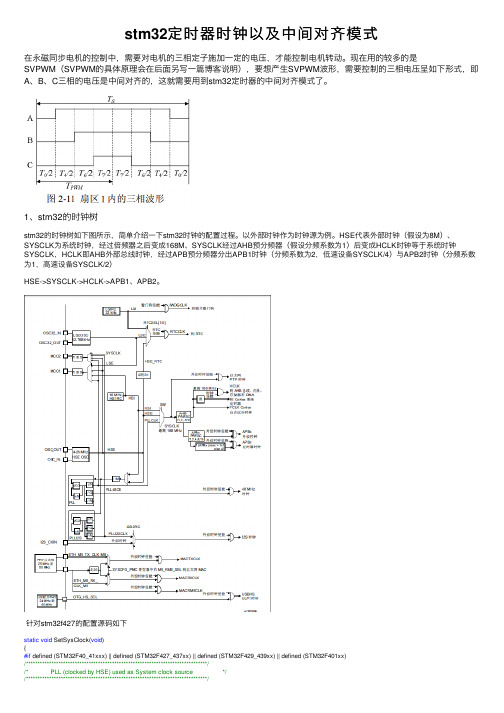

stm32定时器时钟以及中间对齐模式

stm32定时器时钟以及中间对齐模式在永磁同步电机的控制中,需要对电机的三相定⼦施加⼀定的电压,才能控制电机转动。

现在⽤的较多的是SVPWM(SVPWM的具体原理会在后⾯另写⼀篇博客说明),要想产⽣SVPWM波形,需要控制的三相电压呈如下形式,即A、B、C三相的电压是中间对齐的,这就需要⽤到stm32定时器的中间对齐模式了。

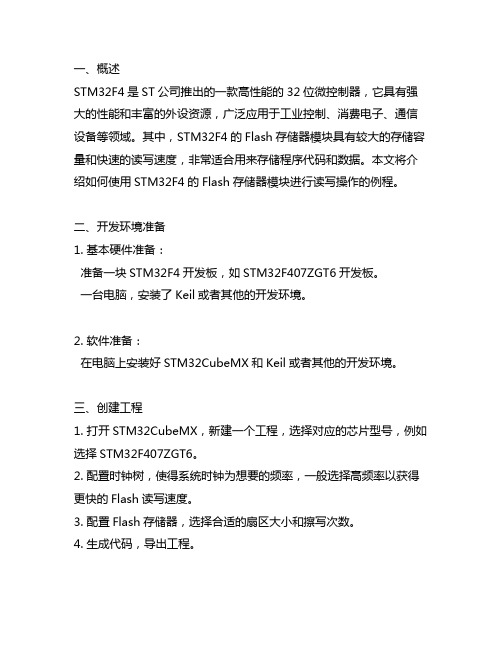

1、stm32的时钟树stm32的时钟树如下图所⽰,简单介绍⼀下stm32时钟的配置过程。

以外部时钟作为时钟源为例。

HSE代表外部时钟(假设为8M)、SYSCLK为系统时钟,经过倍频器之后变成168M、SYSCLK经过AHB预分频器(假设分频系数为1)后变成HCLK时钟等于系统时钟SYSCLK,HCLK即AHB外部总线时钟,经过APB预分频器分出APB1时钟(分频系数为2,低速设备SYSCLK/4)与APB2时钟(分频系数为1,⾼速设备SYSCLK/2)HSE->SYSCLK->HCLK->APB1、APB2。

针对stm32f427的配置源码如下static void SetSysClock(void){#if defined (STM32F40_41xxx) || defined (STM32F427_437xx) || defined (STM32F429_439xx) || defined (STM32F401xx)/******************************************************************************//* PLL (clocked by HSE) used as System clock source *//******************************************************************************/__IO uint32_t StartUpCounter = 0, HSEStatus = 0;/* Enable HSE */RCC->CR |= ((uint32_t)RCC_CR_HSEON);/* Wait till HSE is ready and if Time out is reached exit */do{HSEStatus = RCC->CR & RCC_CR_HSERDY;StartUpCounter++;} while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));if ((RCC->CR & RCC_CR_HSERDY) != RESET){HSEStatus = (uint32_t)0x01;}else{HSEStatus = (uint32_t)0x00;}if (HSEStatus == (uint32_t)0x01){/* Select regulator voltage output Scale 1 mode */RCC->APB1ENR |= RCC_APB1ENR_PWREN;PWR->CR |= PWR_CR_VOS;/* HCLK = SYSCLK / 1*/RCC->CFGR |= RCC_CFGR_HPRE_DIV1;//AHB时钟#if defined (STM32F40_41xxx) || defined (STM32F427_437xx) || defined (STM32F429_439xx)/* PCLK2 = HCLK / 2*/RCC->CFGR |= RCC_CFGR_PPRE2_DIV2;//APB2时钟/* PCLK1 = HCLK / 4*/RCC->CFGR |= RCC_CFGR_PPRE1_DIV4;//APB1时钟#endif /* STM32F40_41xxx || STM32F427_437x || STM32F429_439xx *//* Configure the main PLL */RCC->PLLCFGR = PLL_M | (PLL_N << 6) | (((PLL_P >> 1) -1) << 16) |(RCC_PLLCFGR_PLLSRC_HSE) | (PLL_Q << 24);/* Enable the main PLL */RCC->CR |= RCC_CR_PLLON;/* Wait till the main PLL is ready */while((RCC->CR & RCC_CR_PLLRDY) == 0){}#if defined (STM32F427_437xx) || defined (STM32F429_439xx)/* Enable the Over-drive to extend the clock frequency to 180 Mhz */PWR->CR |= PWR_CR_ODEN;while((PWR->CSR & PWR_CSR_ODRDY) == 0){}PWR->CR |= PWR_CR_ODSWEN;while((PWR->CSR & PWR_CSR_ODSWRDY) == 0){}/* Configure Flash prefetch, Instruction cache, Data cache and wait state */FLASH->ACR = FLASH_ACR_PRFTEN | FLASH_ACR_ICEN |FLASH_ACR_DCEN |FLASH_ACR_LATENCY_5WS; #endif /* STM32F427_437x || STM32F429_439xx *//* Select the main PLL as system clock source */RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));RCC->CFGR |= RCC_CFGR_SW_PLL;/* Wait till the main PLL is used as system clock source */while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS ) != RCC_CFGR_SWS_PLL);{}}else{ /* If HSE fails to start-up, the application will have wrong clockconfiguration. User can add here some code to deal with this error */}}2、stm32定时器的时钟stm32定时器分为⾼级定时器(TIM1与TIM8)、通⽤定时器(TIM2-TIM5、TIM9-TIM14)、基本定时器(TIM6、TIM7)。

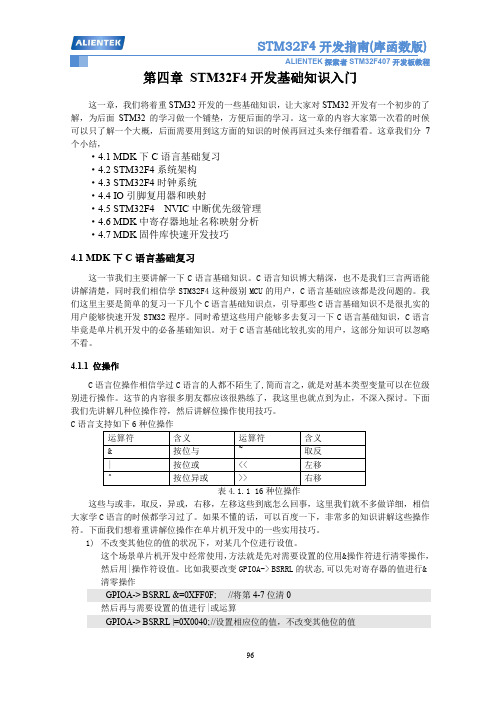

第四章 STM32F4开发基础知识入门-正点原子探索者STM32F4开发板-STM32F4开发指南-库函数

第四章STM32F4开发基础知识入门这一章,我们将着重STM32开发的一些基础知识,让大家对STM32开发有一个初步的了解,为后面STM32的学习做一个铺垫,方便后面的学习。

这一章的内容大家第一次看的时候可以只了解一个大概,后面需要用到这方面的知识的时候再回过头来仔细看看。

这章我们分7个小结,·4.1 MDK下C语言基础复习·4.2 STM32F4系统架构·4.3 STM32F4时钟系统·4.4 IO引脚复用器和映射·4.5 STM32F4 NVIC中断优先级管理·4.6 MDK中寄存器地址名称映射分析·4.7 MDK固件库快速开发技巧4.1 MDK下C语言基础复习这一节我们主要讲解一下C语言基础知识。

C语言知识博大精深,也不是我们三言两语能讲解清楚,同时我们相信学STM32F4这种级别MCU的用户,C语言基础应该都是没问题的。

我们这里主要是简单的复习一下几个C语言基础知识点,引导那些C语言基础知识不是很扎实的用户能够快速开发STM32程序。

同时希望这些用户能够多去复习一下C语言基础知识,C语言毕竟是单片机开发中的必备基础知识。

对于C语言基础比较扎实的用户,这部分知识可以忽略不看。

4.1.1 位操作C语言位操作相信学过C语言的人都不陌生了,简而言之,就是对基本类型变量可以在位级别进行操作。

这节的内容很多朋友都应该很熟练了,我这里也就点到为止,不深入探讨。

下面我们先讲解几种位操作符,然后讲解位操作使用技巧。

C表4.1.1 16种位操作这些与或非,取反,异或,右移,左移这些到底怎么回事,这里我们就不多做详细,相信大家学C语言的时候都学习过了。

如果不懂的话,可以百度一下,非常多的知识讲解这些操作符。

下面我们想着重讲解位操作在单片机开发中的一些实用技巧。

1)不改变其他位的值的状况下,对某几个位进行设值。

这个场景单片机开发中经常使用,方法就是先对需要设置的位用&操作符进行清零操作,然后用|操作符设值。

stm32f4 flash读写例程

一、概述STM32F4是ST公司推出的一款高性能的32位微控制器,它具有强大的性能和丰富的外设资源,广泛应用于工业控制、消费电子、通信设备等领域。

其中,STM32F4的Flash存储器模块具有较大的存储容量和快速的读写速度,非常适合用来存储程序代码和数据。

本文将介绍如何使用STM32F4的Flash存储器模块进行读写操作的例程。

二、开发环境准备1. 基本硬件准备:准备一块STM32F4开发板,如STM32F407ZGT6开发板。

一台电脑,安装了Keil或者其他的开发环境。

2. 软件准备:在电脑上安装好STM32CubeMX和Keil或者其他的开发环境。

三、创建工程1. 打开STM32CubeMX,新建一个工程,选择对应的芯片型号,例如选择STM32F407ZGT6。

2. 配置时钟树,使得系统时钟为想要的频率,一般选择高频率以获得更快的Flash读写速度。

3. 配置Flash存储器,选择合适的扇区大小和擦写次数。

4. 生成代码,导出工程。

四、编写代码1. 在Keil或者其他的开发环境中打开刚刚生成的工程。

2. 找到Flash读写相关的API,一般在芯片提供的库函数中可以找到。

3. 根据需要编写Flash读写的代码,例如可以编写一个函数来实现向Flash写入数据的功能。

五、编译下载1. 编译代码,生成bin文件。

2. 将bin文件下载到STM32F4开发板中,可以使用ST-Link或者其他下载工具来完成。

六、调试运行1. 确保下载成功,重启开发板。

2. 进行调试,观察Flash读写是否正常。

七、注意事项1. 在进行Flash写入操作时,一定要小心谨慎,避免对程序的正常运行造成影响。

2. 在进行Flash擦除操作时,务必注意擦除的范围,避免擦除了不该擦除的数据。

3. 在进行Flash读写操作时,需要留意Flash的特性和限制,以免造成不必要的麻烦。

八、总结本文介绍了如何在STM32F4开发板上使用Flash存储器进行读写操作的例程,从开发环境准备到代码编写再到调试运行都有详细的步骤说明,并给出了注意事项和总结。

STM32时钟树

STM32时钟树STM32的时钟系统相较于51单⽚机,stm32的时钟系统可以说是⾮常复杂了,我们现在看下⾯的⼀张图:上图说明了时钟的⾛向,是从左⾄右的从时钟源⼀步步的分配给外设时钟。

需要注意的是,上图左侧⼀共有四个时钟源,从上到下依次是:⾼速内部时钟(HSI):以内部RC振荡器产⽣,频率为8Mhz,但相较于外部时钟不稳定。

⾼速内部时钟(HSE):以外部晶振作为时钟源,晶振频率可取范围为4~16Mhz,⼀般采⽤8Mhz的晶振。

低速外部时钟(LSE): 以外部晶振作为时钟源,主要是提供给实时时钟模块,所以⼀般选⽤32.768khz,该频率下定时器⽅便取整。

低速内部时钟(LSI): 从内部RC振荡器产⽣,频率为40khz,也是主要提供给实时时钟模块。

根据上图,以我们最常⽤的⾼速外部时钟为例,沿着路线⼀步步的分析:1. 从最左端的OSC_OUT和OSC_IN开始,这两个引脚分别连接到外部晶振的两端。

2. 我们假设连接的晶振为8Mhz,它遇到了第⼀个分频器PLLXTPRE。

在这个分频器中,可以选择设置⼆分频,或者不分频。

这⾥我们选择不分频。

3. 然后箭头指向了开关PLLSRC,这个开关可以选择HSE或者HSI作为其时钟输出。

这⾥我们选择HSE,紧接着⼜遇到锁相环PLL,也叫倍频器。

我们可以设定2到16的倍频因⼦(PLLMUL),经过PLL的时钟称为PLLCLK。

在这⾥设置倍频因⼦为9,也就是说乘以9,PLLCLK为72Mhz。

4. 然后⼜遇到⼀个开关SW,经过这个开关之后就是STM32的系统时钟(SYSCLK)了。

通过这个开关,可以切换SYSCLK的时钟源,有HSI,PLLCLK,HSE三个选择。

我们选择PLLCLK时钟,所以SYSCLK就为72Mhz了。

5. PLLCLK在输⼊到SW前,还流向了USB预分频器,所以这个PLLCLK也作为USB的时钟。

6. 再继续看SYSCLK,SYSCLK经过AHB预分频器,分频后再输⼊到其他外设。

stm32时钟概念

stm32时钟概念STMicroelectronics的STM32系列是一系列基于ARM Cortex-M 内核的微控制器(MCU)。

时钟系统在STM32芯片中是一个关键的概念,因为它驱动了芯片内部的各种功能模块,包括CPU、外设、总线等。

以下是与STM32时钟相关的一些基本概念:1. 系统时钟(SYSCLK): SYSCLK是STM32中的主时钟,它驱动CPU和内存等核心模块。

其频率由时钟源和分频器的组合决定。

2. 时钟源: STM32芯片通常支持多个时钟源,包括内部RC振荡器、外部晶体振荡器、PLL(相位锁定环)等。

选择适当的时钟源取决于应用的要求,例如需要更高的稳定性或更低的功耗。

3. PLL(Phase-Locked Loop):PLL是一种用于产生高稳定性时钟信号的电路。

通过将一个参考时钟信号与一个可调节的倍频器相锁定,PLL可以生成一个高频率的时钟信号。

4. AHB、APB总线:在STM32中,系统总线被分为高性能总线(AHB)和低速外设总线(APB)。

这两个总线有各自的时钟域,因此可以独立配置时钟。

这种分级的结构有助于提高系统的性能和灵活性。

5. 时钟树:时钟树描述了时钟系统的层次结构,显示了时钟源如何通过PLL和分频器传递到各个模块。

了解时钟树结构对于调整系统时钟和解决时钟相关问题非常有用。

6. 时钟配置寄存器: STM32芯片具有一系列寄存器,允许程序员配置时钟系统。

这些寄存器包括RCC寄存器(RCC,Reset and Clock Control)等,通过编程这些寄存器,可以设置各种时钟参数。

7. 低功耗模式时钟: STM32芯片支持不同的低功耗模式,如停机模式、待机模式等。

在这些模式下,可以降低系统的功耗,因此时钟系统在这些模式下的配置也需要考虑。

时钟配置通常是在启动代码或初始化过程中完成的,程序员可以通过修改相应的寄存器来调整时钟设置以满足应用的需求。

对于具体的时钟配置和使用,建议查阅STMicroelectronics提供的芯片手册和相关文档。

图文详解stm32时钟树

对于广大初次接触STM32的读者朋友(甚至是初次接触ARM器件的读者朋友)来说,在熟悉了开发环境的使用之后,往往“栽倒”在同一个问题上。

这问题有个关键字叫:时钟树。

众所周知,微控制器(处理器)的运行必须要依赖周期性的时钟脉冲来驱动——往往由一个外部晶体振荡器提供时钟输入为始,最终转换为多个外部设备的周期性运作为末,这种时钟“能量”扩散流动的路径,犹如大树的养分通过主干流向各个分支,因此常称之为“时钟树”。

在一些传统的低端8位单片机诸如51,AVR,PIC等单片机,其也具备自身的一个时钟树系统,但其中的绝大部分是不受用户控制的,亦即在单片机上电后,时钟树就固定在某种不可更改的状态(假设单片机处于正常工作的状态)。

比如51单片机使用典型的12MHz晶振作为时钟源,则外设如IO口、定时器、串口等设备的驱动时钟速率便已经是固定的,用户无法将此时钟速率更改,除非更换晶振。

而STM32微控制器的时钟树则是可配置的,其时钟输入源与最终达到外设处的时钟速率不再有固定的关系,本文将来详细解析STM32微控制器的时钟树。

图1是STM32微控制器的时钟树,表1是图中各个标号所表示的部件。

标号图1标号释义1内部低速振荡器(LSI,40Khz)2外部低速振荡器(LSE,32.768Khz)3外部高速振荡器(HSE,3-25MHz)4内部高速振荡器(HIS,8MHz)5PLL输入选择位6RTC时钟选择位7PLL1分频数寄存器8PLL1倍频寄存器9系统时钟选择位10USB分频寄存器11AHB分频寄存器12APB1分频寄存器13AHB总线14APB1外设总线15APB2分频寄存器16APB2外设总线17ADC预分频寄存器18ADC外设19PLL2分频数寄存器20PLL2倍频寄存器21PLL时钟源选择寄存器22独立看门狗设备23RTC设备图1STM32的时钟树在认识这颗时钟树之前,首先要明确“主干”和最终的“分支”。

假设使用外部8MHz 晶振作为STM32的时钟输入源(这也是最常见的一种做法),则这个8MHz便是“主干”,而“分支”很显然是最终的外部设备比如通用输入输出设备(GPIO)。

STM32F4时钟树外设挂靠总线学习小结

STM32F4时钟树学习小结时钟是单片机的心脏,重要性不言而喻,STM32F4的时钟树是比较复杂的。

时钟树图一时钟树图二1:STMF4xx系统共计有三个主要时钟源(HSI、HSE和PLL)和两个次要时钟源(LSE、LSI)。

2:SYSCLK可以来自HSI、HSE和PLL,多数采用PLL频率最高能达到168MHz。

3:RTC时钟可以来自LSE、LSI和HSE,但只有用LSE时,才能保证系统电源掉电时RTC仍能正常工作。

4:可通过多个预分频器配置AHB 频率、高速APB (APB2) 和低速APB (APB1)。

AHB 域的最大频率为168 MHz。

高速APB2 域的最大允许频率为84 MHz。

低速APB1 域的最大允许频率为42 MHz。

5:STM32F405xx/07xx 和STM32F415xx/17xx 的定时器时钟频率由硬件自动设置。

如果APB 预分频器为1,定时器时钟频率等于APB 域的频率。

否则,等于APB 域的频率的两倍(×2)。

6:除以下时钟外,所有外设时钟均由系统时钟(SYSCLK) 提供:●来自于特定PLL 输出(PLL48CLK) 的USB OTG FS 时钟(48 MHz)、基于模拟技术的随机数发生器(RNG) 时钟(<=48 MHz) 和SDIO 时钟(<= 48 MHz)。

●I2S 时钟●由外部PHY 提供的USB OTG HS (60 MHz) 时钟●由外部PHY 提供的以太网MAC 时钟(TX、RX 和RMII)。

下面介绍挂在不同总线上的设备情况1、挂在AHB1总线的外设有:最高时钟频率:168MHZ1)GPIOA~K2)RCC_AHB1Periph_CRC3)FLITF4)SRAM15)SRAM26)BKPSRAM7)SRAM38)CCMDATARAMEN9)DMA110)DMA211)DMA2D12)ETH_MAC、ETH_MAC_Tx、ETH_MAC_Rx、ETH_MAC_PTP13)OTG_HS、OTG_HS_ULPI2、挂在AHB2总线的外设有:最高时钟频率:168MHZ1)DCMI2)CRYP3)HASH4)RNG5)OTG_FS3、挂在APB1_Peripherals 有:最高时钟频率:42MHZ1)TIM2~142)WWDG3)SPI2~34)USART2~35)UART4~5,7~86)I2C1~37)CAN1~28)PWR9)DAC4、挂在APB2_Peripherals 有:最高时钟频率:84MHZ1)TIM1,8~112)USART1,63)ADC4)ADC1~35)SDIO,1,4,5,66)SYSCFG7)SAI18)LTDC。

STM32时钟总结剖析

STM32时钟总结一、时钟基本概念 (2)二、时钟树 (7)三、STM32上电后时钟的过程. (7)3.1 执行SystemInit ()函数 (7)3.2 执行SetSysClock()函数. (8)3.3 执行SetSysClockTo72()函数 (8)3.3.2 判断外部高速时钟源是否稳定 (8)3.3.4 FLASH 配置. (9)3.3.5 系统时钟配置是HCLK,PCLK2为HCLK,PCLK1为HCLK的一半93.3.6 配置PLL 在这里修改倍频值。

RCC_CFGR_PLLMUL9L 93.3.7 失能PLL;判断PLL是否Readay;选择PLL 为系统时钟,一直等到时钟稳定 (9)四、时钟源的选择 (10)4.1 系统默认配置时钟8*9=72M (10)4.2 配置HSI(高速内部时钟)为系统主时钟(永远不变8M)104.3 配置HSE为系统主时钟。

8M(和外部晶振有关)114.4 配置PLLCLK为系统主时钟. (11)4.5 程序 (11)五、配置HCLK,PCLK,1 PCLK2. (11)、时钟基本概念钟。

当时钟源被直接或通过PLL间接作为系统时钟时,它将不能被停止。

稳定阶段的延迟或PLL 稳定),从一个时钟源到另一个时钟源的切换才会发生。

在被选择时钟源没有就绪时,系统时钟的切换不会发生。

直至目标时钟源就绪,才发生切换。

时钟安全系统(CSS)时钟安全系统可以通过软件被激活。

一旦其被激活,时钟监测器将在HSE振荡器启动延迟后被使能,并在HSE时钟关闭后关闭。

如果HSE时钟发生故障,HSE 振荡器被自动关闭,时钟失效事件将被送到高级定时器TIM1的刹车输入端,并产生时钟安全中断CSSI,允许软件完成营救操作。

此CSSI中断连接到Cortex ?M3的NMI中断。

一旦CSS被激活,并且HSE时钟出现故障,CSS中断就产生,并且NMI 也自动产生。

NMI 将被不断执行,直到CSS中断挂起位被清除。

stm32几种时钟控制介绍,含原理图

stm32几种时钟控制介绍,含原理图本文提到的有以下内容:• 时钟系统与总线矩阵• SysTick系统定时器• RTC实时时钟• 看门狗定时器• 通用定时器一、时钟系统与总线矩阵stm32F4的时钟树如下图所示:在STM32中,有五个时钟源,为HSI、HSE、LSI、LSE、PLL。

HSI是高速内部时钟,RC振荡器,频率为8MHz。

HSE是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。

LSI是低速内部时钟,RC振荡器,频率为40kHz。

LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。

倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

我们在学习51单片机的时候,其内部是没有晶振的,而stm32是有的。

stm32可以通过RCC(时钟控制寄存器)对时钟进行参数配置以及使能。

我们还可以通过修改system_stm32f4xx.c文件,来配置上述时钟树上的一些分频、倍频参数,得到理想的频率。

在单片机系统中,CPU和总线以及外设的时钟设置是非常重要的,因为没有时钟就没有时序,组合电路需要好好理解清楚。

我们先来看一下总线矩阵。

片上总线标准种类繁多,而由ARM公司推出的AMBA片上总线受到了广大IP开发商和SoC系统集成者的青睐,已成为一种流行的工业标准片上结构。

AMBA规范主要包括了AHB(Advanced High performance Bus)系统总线和APB(Advanced Peripheral Bus)外围总线。

二者分别适用于高速与相对低速设备的连接。

一般性的时钟设置需要先考虑系统时钟的来源,是内部RC还是外部晶振还是外部的振荡器,是否需要PLL。

然后考虑内部总线和外部总线,最后考虑外设的时钟信号。

遵从先倍频作为CPU时钟,然后在由内向外分频,下级迁就上级的原则。

STM32-时钟配置与使用

STM32-时钟配置与使⽤0、前⾔RCC-复位和时钟控制器可以实现配置系统时钟SYSCLK,配置AHB(HCLK)总线时钟,配置外设APB1(PCLK1)和APB2(PCLK2)时钟库函数的标准配置为PCLK2=HCLK=SYSCLK=PLLCLK=72M,PCLK1=HCLK/2=36M系统初始化时会调⽤函数实现时钟配置。

#ifdef SYSCLK_FREQ_HSEuint32_t SystemCoreClock = SYSCLK_FREQ_HSE; /*!< System Clock Frequency (Core Clock) */#elif defined SYSCLK_FREQ_24MHzuint32_t SystemCoreClock = SYSCLK_FREQ_24MHz; /*!< System Clock Frequency (Core Clock) */#elif defined SYSCLK_FREQ_36MHzuint32_t SystemCoreClock = SYSCLK_FREQ_36MHz; /*!< System Clock Frequency (Core Clock) */#elif defined SYSCLK_FREQ_48MHzuint32_t SystemCoreClock = SYSCLK_FREQ_48MHz; /*!< System Clock Frequency (Core Clock) */#elif defined SYSCLK_FREQ_56MHzuint32_t SystemCoreClock = SYSCLK_FREQ_56MHz; /*!< System Clock Frequency (Core Clock) */#elif defined SYSCLK_FREQ_72MHzuint32_t SystemCoreClock = SYSCLK_FREQ_72MHz; /*!< System Clock Frequency (Core Clock) */static void SetSysClock(void){#ifdef SYSCLK_FREQ_HSESetSysClockToHSE();#elif defined SYSCLK_FREQ_24MHzSetSysClockTo24();#elif defined SYSCLK_FREQ_36MHzSetSysClockTo36();#elif defined SYSCLK_FREQ_48MHzSetSysClockTo48();#elif defined SYSCLK_FREQ_56MHzSetSysClockTo56();#elif defined SYSCLK_FREQ_72MHzSetSysClockTo72();#endif在system_stm32f10x.c⽂件中可更改宏定义改变系统时钟频率#if defined (STM32F10X_LD_VL) || (defined STM32F10X_MD_VL) || (defined STM32F10X_HD_VL)/* #define SYSCLK_FREQ_HSE HSE_VALUE */#define SYSCLK_FREQ_24MHz 24000000#else/* #define SYSCLK_FREQ_HSE HSE_VALUE *//* #define SYSCLK_FREQ_24MHz 24000000 *//* #define SYSCLK_FREQ_36MHz 36000000 *//* #define SYSCLK_FREQ_48MHz 48000000 *//* #define SYSCLK_FREQ_56MHz 56000000 */#define SYSCLK_FREQ_72MHz 72000000#endif1、时钟树主要时钟HSE:⾼速外部时钟,可由有源晶振或⽆源晶振提供,4-16MHzPLL以HSE为来源时可设置不分频或2分频PLL:锁相环时钟源,可配置来⾃HSE或HSI/2PLLCLK:锁相环时钟,可设置倍频[2,3,4,5,6,7,8,9,10,11,12,13,14,15,16]SYSCLK:系统时钟PCLK2:APB2总线时钟,由HCLK通过⾼速APB2预分频得到,分频因⼦[1,2,4,8,16]其他时钟USB时钟:由PLLCLK通过USB预分频器得到,分频因⼦[1,1.5]Cortex系统时钟:由HCLK8分频得到,⽤来驱动内核的系统定时器SysTickADC时钟:由PCLK2经ADC预分频得到,分频因⼦[2,4,6,8]RTC时钟:由HSE/128或LSE或LSI得到MCO时钟:输出时钟,可由PLLCLK/2,HSI,HSE,SYSCLK配置2、时钟配置相关库函数配置函数/*将RCC外设初始化为复位状态*/void RCC_DeInit(void);/*使能HSE,可选参数RCC_HSE_OFF,RCC_HSE_ON,RCC_HSE_Bypass*/void RCC_HSEConfig(uint32_t RCC_HSE);/*等待时钟源启动稳定,返回SUCCESS,ERROR*/ErrorStatus RCC_WaitForHSEStartUp(void);/*配置PLL时钟源和PLL倍频因⼦RCC_RLLSource:RCC_PLLSource_HSE_Div1,RCC_PLLSource_HSE_Div2,RCC_PLLSource_HSI_Div2RCC_PLLMul:RCC_PLLMul_2 [2,3,4,5,6,7,8,9,10,11,12,13,14,15,16]*/void RCC_PLLConfig(uint32_t RCC_PLLSource, uint32_t RCC_PLLMul);/*配置系统时钟,可选参数RCC_SYSCLKSource_HSI,RCC_SYSCLKSource_HSE,RCC_SYSCLKSource_PLLCLK */void RCC_SYSCLKConfig(uint32_t RCC_SYSCLKSource);/*配置HCLK,可选参数RCC_SYSCLK_Div1 [1,2,4,8,16,64,128,256,512]*/void RCC_HCLKConfig(uint32_t RCC_SYSCLK);/*配置PCLK1,可选参数RCC_HCLK_Div1 [1,2,4,8,16]*/void RCC_PCLK1Config(uint32_t RCC_HCLK);/*配置PCLK2,可选参数RCC_HCLK_Div1 [1,2,4,8,16]*/void RCC_PCLK2Config(uint32_t RCC_HCLK);操作函数/*控制PLL开关,可选参数DISABLE,ENABLE*/void RCC_PLLCmd(FunctionalState NewState);/*获取状态,可选参数#define RCC_FLAG_HSIRDY ((uint8_t)0x21)#define RCC_FLAG_HSERDY ((uint8_t)0x31)#define RCC_FLAG_PLLRDY ((uint8_t)0x39)#define RCC_FLAG_LSERDY ((uint8_t)0x41)#define RCC_FLAG_LSIRDY ((uint8_t)0x61)#define RCC_FLAG_PINRST ((uint8_t)0x7A)#define RCC_FLAG_PORRST ((uint8_t)0x7B)#define RCC_FLAG_SFTRST ((uint8_t)0x7C)#define RCC_FLAG_IWDGRST ((uint8_t)0x7D)#define RCC_FLAG_WWDGRST ((uint8_t)0x7E)#define RCC_FLAG_LPWRRST ((uint8_t)0x7F)返回SET,RESET*/* - 0x08: PLL used as system clock*/uint8_t RCC_GetSYSCLKSource(void);使⽤HSE配置系统时钟1、开启HSE ,并等待 HSE 稳定2、设置 AHB、APB2、APB1的预分频因⼦3、设置PLL的时钟来源,和PLL的倍频因⼦,设置各种频率主要就是在这⾥设置4、开启PLL,并等待PLL稳定5、把PLLCK切换为系统时钟SYSCLK6、读取时钟切换状态位,确保PLLCLK被选为系统时钟/* 设置系统时钟:SYSCLK, AHB总线时钟:HCLK, APB2总线时钟:PCLK2, APB1总线时钟:PCLK1* PCLK2 = HCLK = SYSCLK* PCLK1 = HCLK/2,最⾼只能是36M* 参数说明:pllmul是PLL的倍频因⼦,在调⽤的时候可以是:RCC_PLLMul_x , x:[2,3,...16]* 举例:HSE_SetSysClock(RCC_PLLMul_9); 则设置系统时钟为:8MHZ * 9 = 72MHZ* HSE_SetSysClock(RCC_PLLMul_16); 则设置系统时钟为:8MHZ * 16 = 128MHZ,超频慎⽤** HSE作为时钟来源,经过PLL倍频作为系统时钟,这是通常的做法*/void HSE_SetSysClock(uint32_t pllmul){__IO uint32_t StartUpCounter = 0, HSEStartUpStatus = 0;// 把RCC外设初始化成复位状态,这句是必须的RCC_DeInit();//使能HSE,开启外部晶振,野⽕开发板⽤的是8MRCC_HSEConfig(RCC_HSE_ON);// 等待 HSE 启动稳定HSEStartUpStatus = RCC_WaitForHSEStartUp();// 只有 HSE 稳定之后则继续往下执⾏if (HSEStartUpStatus == SUCCESS){//----------------------------------------------------------------------//// 使能FLASH 预存取缓冲区FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);// SYSCLK周期与闪存访问时间的⽐例设置,这⾥统⼀设置成2// 设置成2的时候,SYSCLK低于48M也可以⼯作,如果设置成0或者1的时候,// 如果配置的SYSCLK超出了范围的话,则会进⼊硬件错误,程序就死了// 0:0 < SYSCLK <= 24M// 1:24< SYSCLK <= 48M// 2:48< SYSCLK <= 72MFLASH_SetLatency(FLASH_Latency_2);//----------------------------------------------------------------------//// AHB预分频因⼦设置为1分频,HCLK = SYSCLKRCC_HCLKConfig(RCC_SYSCLK_Div1);// APB2预分频因⼦设置为1分频,PCLK2 = HCLKRCC_PCLK2Config(RCC_HCLK_Div1);// APB1预分频因⼦设置为1分频,PCLK1 = HCLK/2RCC_PCLK1Config(RCC_HCLK_Div2);//-----------------设置各种频率主要就是在这⾥设置-------------------//// 设置PLL时钟来源为HSE,设置PLL倍频因⼦// PLLCLK = 8MHz * pllmulRCC_PLLConfig(RCC_PLLSource_HSE_Div1, pllmul);//------------------------------------------------------------------//// 开启PLLRCC_PLLCmd(ENABLE);// 等待 PLL稳定while (RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET){}// 当PLL稳定之后,把PLL时钟切换为系统时钟SYSCLKRCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);// 读取时钟切换状态位,确保PLLCLK被选为系统时钟while (RCC_GetSYSCLKSource() != 0x08){}}else{// 如果HSE开启失败,那么程序就会来到这⾥,⽤户可在这⾥添加出错的代码处理// 当HSE开启失败或者故障的时候,单⽚机会⾃动把HSI设置为系统时钟,// HSI是内部的⾼速时钟,8MHZwhile (1){使⽤HSI配置系统时钟1、开启HSI ,并等待 HSI 稳定2、设置 AHB、APB2、APB1的预分频因⼦3、设置PLL的时钟来源,和PLL的倍频因⼦,设置各种频率主要就是在这⾥设置4、开启PLL,并等待PLL稳定5、把PLLCK切换为系统时钟SYSCLK6、读取时钟切换状态位,确保PLLCLK被选为系统时钟/* 设置系统时钟:SYSCLK, AHB总线时钟:HCLK, APB2总线时钟:PCLK2, APB1总线时钟:PCLK1* PCLK2 = HCLK = SYSCLK* PCLK1 = HCLK/2,最⾼只能是36M* 参数说明:pllmul是PLL的倍频因⼦,在调⽤的时候可以是:RCC_PLLMul_x , x:[2,3,...16]* 举例:HSI_SetSysClock(RCC_PLLMul_9); 则设置系统时钟为:4MHZ * 9 = 72MHZ* HSI_SetSysClock(RCC_PLLMul_16); 则设置系统时钟为:4MHZ * 16 = 64MHZ** HSI作为时钟来源,经过PLL倍频作为系统时钟,这是在HSE故障的时候才使⽤的⽅法* HSI会因为温度等原因会有漂移,不稳定,⼀般不会⽤HSI作为时钟来源,除⾮是迫不得已的情况* 如果HSI要作为PLL时钟的来源的话,必须⼆分频之后才可以,即HSI/2,⽽PLL倍频因⼦最⼤只能是16 * 所以当使⽤HSI的时候,SYSCLK最⼤只能是4M*16=64M*/void HSI_SetSysClock(uint32_t pllmul){__IO uint32_t HSIStartUpStatus = 0;// 把RCC外设初始化成复位状态,这句是必须的RCC_DeInit();//使能HSIRCC_HSICmd(ENABLE);// 等待 HSI 就绪HSIStartUpStatus = RCC->CR & RCC_CR_HSIRDY;// 只有 HSI就绪之后则继续往下执⾏if (HSIStartUpStatus == RCC_CR_HSIRDY){//----------------------------------------------------------------------//// 使能FLASH 预存取缓冲区FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);// SYSCLK周期与闪存访问时间的⽐例设置,这⾥统⼀设置成2// 设置成2的时候,SYSCLK低于48M也可以⼯作,如果设置成0或者1的时候,// 如果配置的SYSCLK超出了范围的话,则会进⼊硬件错误,程序就死了// 0:0 < SYSCLK <= 24M// 1:24< SYSCLK <= 48M// 2:48< SYSCLK <= 72MFLASH_SetLatency(FLASH_Latency_2);//----------------------------------------------------------------------//// AHB预分频因⼦设置为1分频,HCLK = SYSCLKRCC_HCLKConfig(RCC_SYSCLK_Div1);// APB2预分频因⼦设置为1分频,PCLK2 = HCLKRCC_PCLK2Config(RCC_HCLK_Div1);// APB1预分频因⼦设置为1分频,PCLK1 = HCLK/2RCC_PCLK1Config(RCC_HCLK_Div2);//-----------------设置各种频率主要就是在这⾥设置-------------------//// 设置PLL时钟来源为HSE,设置PLL倍频因⼦// PLLCLK = 4MHz * pllmulRCC_PLLConfig(RCC_PLLSource_HSI_Div2, pllmul);//------------------------------------------------------------------//// 开启PLLRCC_PLLCmd(ENABLE);// 等待 PLL稳定while (RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET){}// 当PLL稳定之后,把PLL时钟切换为系统时钟SYSCLKRCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);// 读取时钟切换状态位,确保PLLCLK被选为系统时钟while (RCC_GetSYSCLKSource() != 0x08){}}else{// 如果HSI开启失败,那么程序就会来到这⾥,⽤户可在这⾥添加出错的代码处理// 当HSE开启失败或者故障的时候,单⽚机会⾃动把HSI设置为系统时钟,// HSI是内部的⾼速时钟,8MHZwhile (1){MCO输出MCO GPIO初始化/** 初始化MCO引脚PA8* 在F1系列中MCO引脚只有⼀个,即PA8,在F4系列中,MCO引脚会有两个*/void MCO_GPIO_Config(void){GPIO_InitTypeDef GPIO_InitStructure;// 开启GPIOA的时钟RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA, ENABLE);// 选择GPIO8引脚GPIO_InitStructure.GPIO_Pin = GPIO_Pin_8;//设置为复⽤功能推挽输出GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;//设置IO的翻转速率为50MGPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;// 初始化GPIOA8GPIO_Init(GPIOA, &GPIO_InitStructure);}输出// MCO 引脚初始化MCO_GPIO_Config();// 设置MCO引脚输出时钟,⽤⽰波器即可在PA8测量到输出的时钟信号,// 我们可以把PLLCLK/2作为MCO引脚的时钟来检测系统时钟是否配置准确// MCO引脚输出可以是HSE,HSI,PLLCLK/2,SYSCLK//RCC_MCOConfig(RCC_MCO_HSE);//RCC_MCOConfig(RCC_MCO_HSI);//RCC_MCOConfig(RCC_MCO_PLLCLK_Div2);RCC_MCOConfig(RCC_MCO_SYSCLK);Systick系统定时器简介SysTick——系统定时器是属于 CM3 内核中的⼀个外设,内嵌在 NVIC 中。

专题三stm32时钟树及相关库函数

#ifndef STM32F10X_CL

RCC->CFGR &= (uint32_t)0xF8FF0000;

#else

RCC->CFGR &= (uint32_t)0xF0FF0000;

#endif /* STM32F10X_CL */

APB2ENR|=1<<2;//或运算,1有效。

第二种方法就是调用库函数。

四、介绍两种库函数

4.1外设时钟使能函数

与rcc有关寄存器设置的库函数都在stm32f10x_rcc.c以及stm32f10x_rcc.h文档中。上面说要使能GPIO时钟,因为GPIO是APB2的外设,因此就是使能APB2相应外设时钟。库函数是:

三

从前面的图1可以看到,要设置STM32芯片的时钟,有以下几个方面要考虑:

1.芯片的时钟源选择HSE,HIS还是其他?

2.SYSCLK系统时钟应该选择哪个?

3.各总线的分频系数?

4.PLL锁相环的倍频系数?

5.各个外设对应的时钟是开启呢,还是禁止?

上面5个问题,STM32统一用RCC来解决。我们首先来看下与RCC相关的寄存器有哪些。

输入参数2:NewState,外设时钟的新状态,可以是DISABLE,ENABLE两种。

返回值:无

调用示范:RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOB,ENABLE);//使能GPIOB时钟

函数的具体定义引用如下:

void RCC_APB2PeriphClockCmd(uint32_t RCC_APB2Periph, FunctionalState NewState)

STM32时钟源的介绍及使用方法——STM32时钟树

STM32时钟源的介绍及使⽤⽅法——STM32时钟树【温馨提⽰:以下内容均来⾃⽹友的⽆私奉献或书本的摘抄,在此表⽰感谢!】上图是STM32的时钟树,从树上我们可以看到,STM32的时钟有两个来源——内部时钟和外部时钟。

按时钟频率来分,⼜可分为⾼速时钟和低速时钟。

因此STM32的时钟有四个来源:⾼速外部时钟信号(HSE)、低速外部时钟信号(LSE)、⾼速内部时钟信号(HSI)和低速内部时钟信号(LSI)(图中分别⽤蓝⾊的①~④标注)。

①HSE⾼速外部时钟:由外部4~16MHz的晶体或有源晶振提供,通常采⽤8MHz。

②LSI低速外部时钟:外部晶体提供,主要是给实时时钟(RTC),⼀般为32.768kHz。

③HSI⾼速内部时钟:由内部RC振荡器产⽣的8MHz时钟,但不够稳定。

④LSI低速内部时钟:内部RC振荡器产⽣的供给RTC的时钟,频率在30kHz~60kHz之间,通常约40kHz。

时钟在STM32内部最终是供给四⼤块(图中⽤红⾊椭圆圈出):USB的48MHz时钟、系统时钟SYSCLK、实时时钟模块RTC、独⽴看门狗的时钟IWDGCLK。

其中最主要的,也是最⼤头是系统时钟SYSCLK,它可以是内部或外部⾼速时钟直接接过来,也可以内、外部⾼速时钟是PLL倍频后提供的,系统时钟再分别供给Cortex内核、SDIO、AHB总线、DMA、APB1、APB2等。

我们通常是采⽤外部8MHz⾼速时钟(HSE),所以着重说HSE。

我们以前⾯的GPIO上的时钟为例,由ST的Datasheet可知,GPIO是在APB2⾼速外设总线上的,图中绿⾊的线就是时钟的流程,我们⼀步步地来看。

8MHz外部晶体(或晶振)输⼊后,先经过⼀个开关PLLXTPRE(HSE divider for PLL entry),此开关决定对HSE进⾏2分频再输⼊到PLL或直接到PLL。

我们选择不分频。

这样时钟⼜到了第⼆个开关PLLSRC(PLL entry clock source),此开关决定PLL的时钟来源,是内部⾼速时钟⼆分频的时钟还是PLLXTPRE的输出。

STM32时钟配置方法详解

STM32时钟配置方法详解时钟树是STM32微控制器中一系列时钟源和时钟分频器的组成部分。

时钟树包括系统时钟、外设时钟和内核时钟。

系统时钟用于驱动整个微控制器系统的核心,外设时钟用于驱动各种外设,内核时钟用于驱动CPU的运算。

在进行时钟配置之前,首先需要了解系统所需的时钟频率。

在STM32中,系统时钟可以通过多种方式进行配置,例如使用外部晶体、外部时钟、内部RC振荡器或者PLL(锁相环)等方式。

外部晶体是一种常用的时钟源,可以提供高精度的时钟频率。

在使用外部晶体时,首先需要设置PLL的时钟源为外部晶体,并设置PLL输入除频器的分频系数。

然后,再根据系统所需的时钟频率,设置PLL的倍频系数,以得到最终的系统时钟频率。

外部时钟是从外部提供的时钟信号,一般用于测试和调试。

使用外部时钟时,需要设置PLL的时钟源为外部时钟,并设置PLL的倍频系数,以得到所需的系统时钟频率。

内部RC振荡器是一种低成本的时钟源,但是其频率不如外部晶体稳定和精确。

在使用内部RC振荡器时,需要设置PLL的时钟源为内部RC振荡器,并设置PLL的倍频系数,以得到所需的系统时钟频率。

PLL是一种用于产生稳定高频时钟的电路,可以从一个低频时钟源产生一个高频时钟源。

使用PLL时,需要设置其输入时钟源和倍频系数。

系统时钟的分频系数可以通过RCC_CFGR寄存器进行设置。

RCC_CFGR寄存器的各个位域用于配置系统时钟的分频系数,包括分频因子、APB1的分频系数、APB2的分频系数等。

外设时钟是用于驱动外设的时钟,可以由系统时钟分频得到。

外设时钟的分频系数可以通过RCC_CFGR寄存器及各个外设的控制寄存器进行设置。

内核时钟是用于驱动CPU的运算的时钟。

在STM32微控制器中,CPU 时钟可以由系统时钟分频得到,分频系数可以通过RCC_CFGR寄存器和FLASH_ACR寄存器进行设置。

除了上述方法之外,STM32还可以使用时钟配置工具进行时钟配置。

你应该知道的STM32F04x单片机时钟切换教程

你应该知道的STM32F04x单片机时钟切换教程本次编写的教程主要是针对STM32F04x系列的单片机,对于STM32单片机的时钟,想必使用过STM32的人都比较清楚,STM32它是基于 Cortex®-Mx系列内核的微处理器,芯片内部集成了丰富的外设。

同时也集成了内部的时钟源。

也就是说芯片不需要外接晶振就可以运行。

但是大多数的使用情况都是使用了芯片外部的晶振,包括官方的标准固件库也都是默认使用外部晶振,但是有些特殊情况下,不需要使用外部晶振,这样可以节省一个晶振和两个谐振电容,最主要的是可以节省PCB板子的面积。

但如果使用内部晶振,就得要编写程序,更改相关寄存器的值,切换至内部晶振才可以。

对于芯片时钟源切换这样的事情,对高手来说是很简单,对于新手来说就有些搞不清了,因此本教程叙述一下STM32F04x系列单片机时钟源切换的流程。

既然是切换单片机的时钟源,就不能不了解下芯片内部的时钟结构,几乎所有的STM32芯片,官方在手册中都会描述一下芯片内部的时钟结构。

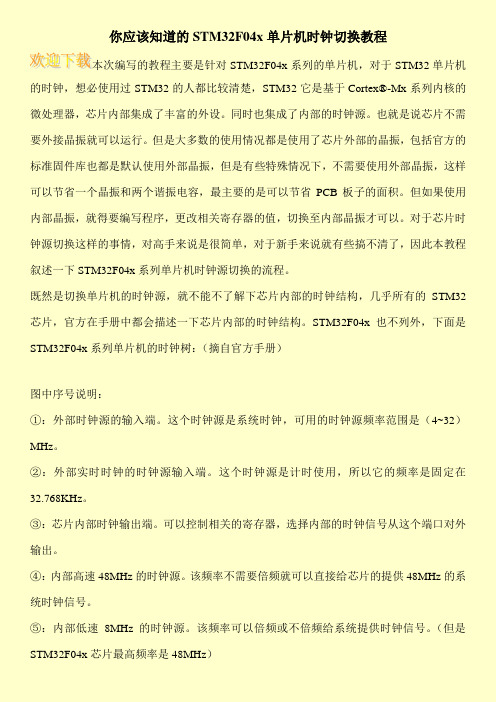

STM32F04x也不列外,下面是STM32F04x系列单片机的时钟树:(摘自官方手册)图中序号说明:①:外部时钟源的输入端。

这个时钟源是系统时钟,可用的时钟源频率范围是(4~32)MHz。

②:外部实时时钟的时钟源输入端。

这个时钟源是计时使用,所以它的频率是固定在32.768KHz。

③:芯片内部时钟输出端。

可以控制相关的寄存器,选择内部的时钟信号从这个端口对外输出。

④:内部高速48MHz的时钟源。

该频率不需要倍频就可以直接给芯片的提供48MHz的系统时钟信号。

⑤:内部低速8MHz的时钟源。

该频率可以倍频或不倍频给系统提供时钟信号。

(但是STM32F04x芯片最高频率是48MHz)。