时钟树综合

时钟树综合.

在CTO后仍有时序违规

时钟树已经进行很好的平衡,但仍存在建立 时间违规?

“Useful Skew”优化

“Useful Skew CTO”使用流水借时间工 艺来减少或消除建立时间违规,同时在 其它地方保持平衡偏移

“Useful Skew”优化

修复建立时间违规通过利用在流水中的正偏 移进行改变时钟buffer尺寸

Post-CTS优化:根据需要反复执行

对于一个大的设计,每 次优化目标只有一个,如 修复hold时间等

Post-CTS布局优化结果

通过逻辑优化和单元重新放 置来修复时序(建立时间和保 持时间)、最大电容和最大过 渡时间违规可能会影响时钟 网络----FFS可能会被移动. 这将可能影响时钟偏移和插 入延时. 因此要分析时钟偏移和插入 延时! 如果想不影响时钟偏移和插 入延时,则需保持FFS位置固 定,执行clock->Utilities>Mark Clock Tree…

同步Pins和忽略Pins

同步Pins: CTS优化达到 buffer约束(最大传 输时间/电容)和时 钟树目标(偏移,插 入延时等)) 忽略Pins: CTS加入一个小的 buffer去隔离所有 的Pins 忽略buffer约束 (最大传输时间/电 容和时钟树目标)

默认的Skew Optimization

符合buffer约束(不符合该约束会报违规) 最大传输时间延迟 最大负载电容 最大扇出 最大buffer级数 符合时钟树目标(不会报违规) 最大偏移 根据Min/Max delay插入延迟

CTS流程

布局完成 设置时钟公共选项 综合时钟树 重新连接扫描链 使能传播时钟 Post-CTS布局优化 优化时钟偏移(CTO) 优化时序(Useful Skew CTO) 布线

数字后端设计实现之时钟树综合实践篇

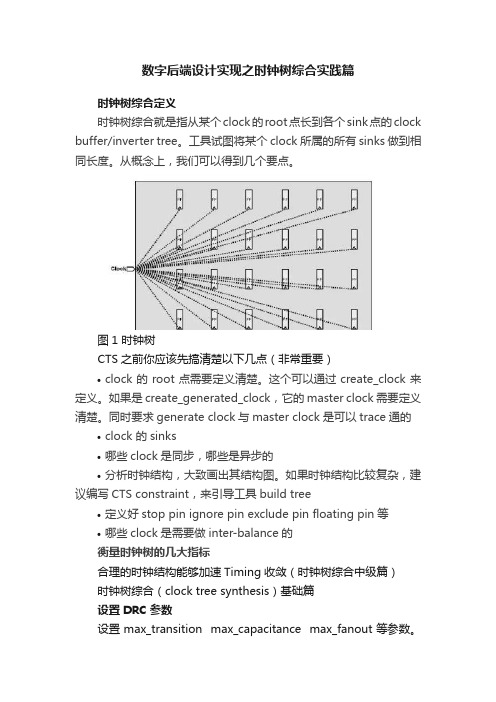

数字后端设计实现之时钟树综合实践篇时钟树综合定义时钟树综合就是指从某个clock的root点长到各个sink点的clock buffer/inverter tree。

工具试图将某个clock所属的所有sinks做到相同长度。

从概念上,我们可以得到几个要点。

图1 时钟树CTS之前你应该先搞清楚以下几点(非常重要)•clock的root点需要定义清楚。

这个可以通过create_clock来定义。

如果是create_generated_clock,它的master clock需要定义清楚。

同时要求generate clock与master clock是可以trace通的•clock 的sinks•哪些clock是同步,哪些是异步的•分析时钟结构,大致画出其结构图。

如果时钟结构比较复杂,建议编写CTS constraint,来引导工具build tree•定义好stop pin ignore pin exclude pin floating pin等•哪些clock是需要做inter-balance的衡量时钟树的几大指标合理的时钟结构能够加速Timing收敛(时钟树综合中级篇)时钟树综合(clock tree synthesis)基础篇设置DRC参数设置max_transition max_capacitance max_fanout等参数。

对于clock的max transition的设置,应该根据clock的频率来设置。

高频率的clock,需要额外设置严格点。

指定clock inverter listset_clock_tree_references -references $cts_clock_inv_listset_clock_tree_references -references $cts_clock_inv_list -sizing_onlyset_clock_tree_references -references $cts_clock_inv_list -delay_insertion_onlyclock inverter cell list的选择往往比较有讲究。

时钟树综合解读

同步Pins和忽略Pins

同步Pins: CTS优化达到 buffer约束(最大传 输时间/电容)和时 钟树目标(偏移,插 入延时等)) 忽略Pins: CTS加入一个小的 buffer去隔离所有 的Pins 忽略buffer约束 (最大传输时间/电 容和时钟树目标)

默认的Skew Optimization

带有SDC不确定的传播时钟

如果SDC不确定值包括抖动和时间裕量,Astro仍 能计算实际的时钟网络延时,同时模仿这些效应 调整SDC中set_clock_uncertainty 的值 通过估计偏移值减少这个值 执行相同的命令 sdc “set_propagated_clock [all_clocks]” 调节下面的时序设置项 Unset “Ignore Clock Uncertainty ” Unset “Ignore Propagated Clock ”

符合buffer约束(不符合该约束会报违规) 最大传输时间延迟 最大负载电容 最大扇出 最大buffer级数 符合时钟树目标(不会报违规) 最大偏移 根据Min/Max delay插入延迟

CTS流程

布局完成 设置时钟公共选项 综合时钟树 重新连接扫描链 使能传播时钟 Post-CTS布局优化 优化时钟偏移(CTO) 优化时序(Useful Skew CTO) 布线

时钟树综合结果

时钟buffer增加 阻塞可能会增加 非时钟树单元可能 会被移动到不理想 的位置 可能会引起新的时 序和最大tran/cap 违规

Post-CTS布局优化

Post-CTS布局优化能 优化时序和减少阻塞 执行逻辑和布局优化 去修复可能的时序 (建立时间和保持时 间)、最大电容和最 大过渡时间违规 保持时间推荐在这 里进行首次修复 Congestion Removal 能通过移动不必要的 非时钟树buffer减少 阻塞

时钟树综合(1)

时钟树综合(1)时钟树综合学习背景时钟信号是数据传输的基准,他对于同步数字系统的功能、性能、稳定性起决定性作⽤。

时钟信号通常是整个芯⽚中有最⼤扇出、通过最长距离、以最⾼速度运⾏的信号。

时钟信号必须要保证在最差的条件下,关键的时序要求能够满⾜,否则对时钟信号的任何不当的控制都可能导致紊乱情况,将错误的数据信号索存到寄存器,从⽽导致系统功能的错误。

时钟信号怎么产⽣的时钟信号源⼀般是从晶体(⽯英晶体、陶瓷晶体)产⽣的。

IC设计时通常会使⽤晶体振荡器来提供时钟源信号。

⼀般会使⽤PLL加上晶体振荡器来给芯⽚内部电路提供倍频或相位的时钟信号。

时钟信号特征时钟的周期(频率)、时钟延迟、时钟信号的不确定性是时钟的三个主要特征要素。

时钟信号延迟时钟信号延迟(latency)⼜称为插⼊延迟(insertion delay), 包括时钟源插⼊延迟和时钟⽹络插⼊延迟。

时钟源插⼊延迟是来⾃系统到当前芯⽚(当前模块)时钟根节点(clock root pin)之间的延迟,时钟⽹络插⼊延迟是时钟树的延迟。

时钟信号不确定性时钟信号的不确定性主要是有时钟信号抖动引起的,时钟抖动是先天存在的,所以在时钟树综合的时候只能考虑起影响,⽆法消除。

时钟抖动是信号实际时间与理想时间的偏差,抖动中含有确定抖动成分和随机抖动的成分【】。

时钟信号偏差时钟信号偏差是指同⼀时钟达到该时钟域内的不同寄存器之间的时间偏差,也即是skew=max(|t i−t j|)产⽣时钟偏差的原因有多种:时钟源到各个时钟端点的路径长度不同、各个端点负载不同、在时钟⽹中插⼊的缓冲器不同等。

在什么时候做时钟树综合:如下图所⽰,通常在物理设计布局完成之后布线之前进⾏时钟树综合。

在此之前所有的寄存器时钟信号是由同⼀个时钟pin驱动的,具有相同的延时的理想时钟。

已经⽣成了gatelevel 的netlist已经有⼀个初步的版图规划,每个逻辑门包括时序器件都有⼀个具体的位置。

已经基于理想时钟完成了时序优化设计。

芯片中时钟树综合质量评价指标

芯片中时钟树综合质量评价指标介绍时钟树是芯片设计中非常重要的一部分,它负责为芯片内的各个功能模块提供稳定的时钟信号。

时钟树的设计质量直接影响芯片的性能和功耗。

因此,对时钟树的综合质量进行评价是芯片设计过程中的重要任务。

时钟树的综合质量评价指标时钟树的综合质量评价指标主要包括以下几个方面:1. 时钟树延迟时钟树的延迟是指时钟信号从源端到达目的端所需的时间。

时钟树延迟的大小直接影响芯片的工作频率和时序要求。

因此,评价时钟树的综合质量时,需要考虑时钟树延迟是否满足设计要求。

2. 时钟树功耗时钟树的功耗是指时钟信号在时钟树中传输过程中所消耗的能量。

时钟树功耗的大小与时钟树的拓扑结构、电压和频率等因素有关。

评价时钟树的综合质量时,需要考虑时钟树功耗是否在可接受范围内。

3. 时钟树抖动时钟树的抖动是指时钟信号的相位或频率在传输过程中发生的变化。

时钟树抖动会导致芯片的时序偏差和时钟信号的不稳定性。

因此,评价时钟树的综合质量时,需要考虑时钟树抖动是否满足设计要求。

4. 时钟树噪声时钟树的噪声是指时钟信号中的不良成分,包括时钟信号的谐波、杂散等。

时钟树噪声会对芯片的功能模块产生干扰,影响芯片的性能和可靠性。

因此,评价时钟树的综合质量时,需要考虑时钟树噪声是否在可接受范围内。

评价指标的权重不同的芯片设计对时钟树的要求不同,因此,在评价时钟树的综合质量时,需要为不同的评价指标分配不同的权重。

一般来说,时钟树延迟和功耗是两个比较重要的指标,因为它们直接关系到芯片的性能和功耗。

而时钟树抖动和噪声相对来说可以适当放宽要求。

评价方法和工具评价时钟树的综合质量可以采用静态分析和动态仿真的方法。

静态分析是指通过对时钟树的结构和参数进行分析,预测时钟树的性能指标。

动态仿真是指通过模拟时钟信号在时钟树中的传输过程,评估时钟树的实际性能。

评价时钟树的综合质量还可以借助一些专门的工具,如PrimeTime、HSPICE等。

这些工具可以对时钟树进行详细的分析和仿真,提供时钟树的延迟、功耗、抖动和噪声等性能指标。

高性能芯片设计中的时钟树优化技术

高性能芯片设计中的时钟树优化技术时钟树是芯片设计中至关重要的一个组成部分,它负责传输时钟信号以保证芯片的正常工作。

在高性能芯片设计中,时钟树的优化技术尤为重要,可以提高芯片的稳定性、降低功耗,并保证芯片的高性能工作。

本文将介绍高性能芯片设计中的时钟树优化技术,并探讨其在芯片设计中的应用。

一、时钟树设计的重要性时钟信号是芯片工作的基准,它控制着各个功能模块的操作时序,因此时钟树设计的合理性直接影响着芯片的性能和功耗。

在高性能芯片设计中,要实现较高的工作频率和低功耗,时钟树的设计至关重要。

一个优秀的时钟树设计应具备以下几个方面的特点:1. 低时钟抖动:时钟抖动会导致芯片工作不稳定,降低性能。

通过合理的时钟树设计,可以减少时钟抖动,提高芯片的工作稳定性和可靠性。

2. 低功耗:时钟信号在芯片中的传输需要消耗功耗,较长的时钟路径和不优化的时钟树设计将导致大量的功耗浪费。

通过优化时钟树设计,可以降低功耗,提高芯片的能效。

3. 均衡和分布平衡:时钟信号在传输过程中,应该保持均衡和分布平衡,避免信号传输的不平衡导致时钟抖动和延迟问题。

二、时钟树优化的目标在高性能芯片设计中,时钟树优化的目标是实现如下几个方面的优化:1. 降低时钟路径的长度:时钟路径越短,芯片的工作频率越高,性能越好。

2. 降低时钟路径的延时:通过合理的时钟树设计,可以降低时钟路径的延时,提高芯片的工作速度。

3. 降低时钟树的功耗:优化时钟树设计,可以减少时钟信号传输过程中的功耗损耗,提高芯片的能效。

三、时钟树优化技术1. 时钟树综合:时钟树综合是时钟树优化的一项重要技术,通过对时钟信号的分析和综合,优化时钟树的结构,减少时钟路径的长度和延时。

时钟树综合工具可以根据设计需求自动完成时钟树的综合工作,生成一个最优的时钟树结构,提高芯片的性能和功耗。

2. 缓冲器插入:在时钟路径过长或者时钟分布不均衡时,可以通过插入合适的缓冲器来优化时钟树设计。

缓冲器可以提升时钟信号的驱动能力,减少时钟路径的延时和功耗。

Clock Tree

关于时钟树的调研在集成电路设计中,时钟信号是数据传输的基准,它对于同步数字系统的功能、性能和稳定性起着决定性的作用,所以时钟信号的特性及其分配网络尤其被人们关注。

时钟信号通常是整个芯片中有最大扇出、通过最长距离、以最高速度运行的信号。

时钟信号必须保证在最坏的条件下,关键的时序要求能得到满足。

因此有必要引入时钟树的概念。

首先,我们要明确时钟树的定义。

时钟树,即clock tree,是个由许多缓冲单元(buffer cell)平衡搭建的网状结构,它有一个源点,一般是时钟输入端(clock input port),也有可能是design内部某一个单元输出脚(cell output pin),然后就是由一级一级的缓冲单元搭建而成,具体的多少级,根据你的设置以及所使用的单元而定,目的就是使所用终点的clock skew(时钟脉冲相位差)、insertion delay(插入延迟)以及transtion最小了,满足设计要求。

一、为什么要使用时钟树和时间管理器?FPGA内部所有的同步部件(如可编程逻辑块内被配置为触发器的寄存器)都需要时钟信号来驱动。

这样的时钟信号一般是来自外部世界的,通过专用时钟输入引脚进入FPGA,接着传送到整个器件并连接到适当的寄存器。

之所以称为时钟树,是因为主时钟信号在芯片内一次又一次地进行分支(触发器可以视为在分支末端的“叶子”)。

使用这种结构是为了保证所有触发器的时钟信号尽可能一致。

如果时钟使用一条长的走线来一个接一个地驱动触发器,那么最接近时钟引脚的触发器接受的信号看上去将比位于链条的最末端所接收到的快很多,这被称为偏移,并且会带来很多问题(甚至使用时钟树时,在分支上的寄存器之间和分支本身之间也存在一定量的偏移)。

时钟树使用专门的走线,与通用可编程互连相分离。

在实际情况中,可以有多个始终引脚(不能使用的时钟引脚可以作为通用I/O 引脚),而在器件内部可以有多个时钟树。

如果在配置时不把时钟引脚直接连入内部的时钟树,也可以先用该引脚驱动一个称为时钟管理器的专用硬件功能块,由时钟管理器产生一定数量的时钟树。

合理的时钟结构能够加速Timing收敛(时钟树综合中级篇)

合理的时钟结构能够加速Timing收敛(时钟树综合中级篇)时钟树综合(Clock Tree Synthesis)一直是数字后端实现中最为重要的步骤之一。

随着芯片时钟越来越多,设计阶段都采用了时钟切换电路,时钟结构越来越复杂(除了func mode外,还有test mode 和mbist等模式)。

针对复杂的时钟结构,想单纯依靠EAD TOOL的CTS engine来实现一个比较好的clock tree质量,几乎不太可能。

而且一个比较理想的clock tree,都是要通过若干次的迭代而产生的,绝对不是你随便跑一次flow就可以的。

在这里顺便强调一个观念,数字后端实现绝对不仅仅是run flow,你的价值不应该停留于此。

如果你还仅仅停留在run flow这个level,劝施主早日改邪归正,呵呵。

那么,下面进入今天的主题。

首先谈谈衡量时钟树质量的几大指标。

时钟树综合(clock tree synthesis)基础篇1.clock tree latency最短clock inverter更少,clock tree上的power更小,占用更少的routing resource以及更容易timing signoff。

2. skew 最小skew对setup和hold都有影响。

特别是hold,如果两个需要进行hold check的register存在较大的skew,那么hold violation就会比较大。

Hold 比较大,就意味着要插比较多的buffer,有可能导致route的问题。

3. Duty Cycle对于时钟树需要保持一个很好的duty cycle。

很多IO接口像DDR,在时钟上升沿和下降沿都会采样数据,所以在clock tree上也需要一个rise delay和fall delay一致的clock inverter。

4. Uncommon path 最短由于clock tree上的common path,会有一部分CRPR补偿(考虑OCV效应)。

集成电路中的时钟树综合分析

集成电路中的时钟树综合分析2012301510055 杨焦电科当前,集成电路工艺发展非常迅速,已从亚微米(015~1μm) 进入到深亚微米(小于015μm) ,进而到超深亚微米(小于0125μm) 。

目前,集成电路批量生产的最小线宽已达到0109μm。

随着工艺的发展,对集成电路设计的要求也日益提高,尤其是同步数字集成电路的时序问题更备受关注。

在同步数字集成电路中,时钟信号为系统中的数据传送提供时间基准,通常是整个芯片中扇出最大、通过距离最长、以最高速度运行的信号,它对于同步系统的运行至关重要,所以,在同步数字系统中时钟信号的特性及其分配网络更被人们所关注。

时钟树必须保证在最差条件下关键的时序要求能得到满足,对时钟信号任何不当的控制都可能导致情况紊乱,将错误的数据信号锁存到寄存器中。

大部分的同步数字系统由级联的时序寄存器组和每组寄存器之间的组合电路组成。

每个数据信号都锁存在一个双稳态寄存器中,该寄存器的使能时钟信号一到达,数据信号就离开双稳态寄存器,穿过组合电路网络进入下一个寄存器,并完全锁存在该寄存器直到下一个时钟信号到达。

一个常用数字同步系统的延时单元由以下三个子系统组成:1) 记忆存储元件; 2) 组合逻辑元件; 3) 时钟产生电路和其分配网络(clocktree) 。

这三个子系统的相互关系对电路能否获得最好的性能和可靠性起着关键作用。

对任意的有序寄存器对R1 、R2 ,其关系可能为以下两种情况之一 :1) R1 输出不能仅通过一系列组合逻辑元件传输到R2 的输入端;2) 存在一组组合逻辑元件直接连接R1 的输出端和R2 的输入端。

在第一种情况下, R1 输出端的信号变化不影响同一周期内R2 的输入。

第二种情况下(用R1 →R2 表示) , R1 输出端的信号转变将传到R2 的输入端,该情况下R1 、R2 被称为时序相邻的寄存器对,它们组成了一条本地数据路径。

如图1[1 ]所示, Ri 和Rf 为一对时序相邻寄存器对,它们分别为本地数据路径的起始和目标寄存器, Ci 、Cf 分别为驱动Ri 和Rf 的时钟信号,这两个时钟信号都由同一个时钟信号源通过时钟树产生。

ASIC后端设计中的时钟偏移以及时钟树综合0

ASIC 后端设计中的时钟偏移以及时钟树综合千路,林平分(北京工业大学北京市嵌入式系统重点实验室,北京100022)摘要:目前的ASIC 设计中,时钟偏移成为限制系统时钟频率的主要因素,时钟树综合技术通过在时钟网络中插入缓冲器来减小时钟偏移。

但是,有时这样做并不能达到系统要求的时钟偏移。

以一款SMIC 0118L m 工艺的DVB T 数字电视解调芯片为例,分析了时钟偏移的产生原因。

介绍了使用Synopsys 公司Astro 工具进行时钟树综合的方法,重点分析了在时钟树综合之前如何设置约束手动优化电路从而改善设计的时序,最后的流片结果证明该方法是有效的。

关键词:时钟偏移;时钟树综合;Astro;手动优化中图分类号:TN402 文献标识码:A 文章编号:1003-353X (2008)06-0527-03C lock Skew and Clock Tree Synthesis in AS IC Backend DesignQian Lu,Lin Pingfen(Bei j ing Embedded Syste m Key Lab ,Beijin g Un iversity o f Technology ,Bei j ing 100022,China)Abstract:Clock skew becomes the primary fac tor of restricting clock frequency in current ASIC design.clock tree synthesis can reduce ske w by inserting buffers,but sometimes it can .t create a satisfactory clock network.The generation principle of clock skew was analyzed taking a SMIC 0118L m digital TV demodulation chip as an e xample.The perform of CTS (clock tree synthesis)using Synopsys Astro was analyzed,how to manually optimize the circuit in order to improve timing was focused,the validity of the method is proved by the tapeout result.Key words:clock skew;clock tree synthesis (CTS);Astro;manually optimize EEAC C:1265A0 引言在大规模集成电路中,时钟信号通常是整个芯片中扇出最大、通过距离最长、以最高速度运行的信号。

Clock tree

Clock tree一、简介时钟树,是个由许多缓冲单元(buffer cell)平衡搭建的网状结构,它有一个源点,一般是时钟输入端(clock input port),也有可能是design内部某一个单元输出脚(cell output pin),然后就是由一级一级的缓冲单元搭建而成,具体的多少级,根据你的设置以及所使用的单元而定,目的就是使所用终点的clock skew(一般最关心这个)、insertion delay以及transtion 了,满足设计要求。

1在传统的集成电路设计中,只须考虑门本身的延迟,互连引起的延迟可忽略。

深亚微米芯片的设计不能沿用传统的设计流程,因为随着器件尺寸的不断减小和电路规模的扩大,门的延时越来越小,限制电路性能提高的主要因素是互连延迟。

因此,精确地计算互连延迟在芯片设计中具有十分重要的意义。

表1是线延时在不同工艺下占总延时的比例关系。

可以清楚的看到:随着工艺的发展,线延时逐渐占据了主导地位。

对集成电路设计的要求也日益提高,尤其是同步数字集成电路的时序问题更备受关注.在同步数字集成电路中,时钟信号为系统中的数据传送提供时间基准,通常是整个芯片中扇出最大、通过距离最长、以最高速度运行的信号,它对于同步系统的运行至关重要。

时钟树必须保证在最差条件下关键的时序要求能得到满足,对时钟信号任何不当的控制都可能导致情况紊乱,将错误的数据信号锁存到寄存器中。

2二、同步数字集成电路系统大部分的同步数字系统由级联的时序寄存器组和每组寄存器之间的组合电路组成.每个数据信号都锁存在一个双稳态寄存器中,该寄存器的使能时钟信号一到达,数据信号就离开双稳态寄存器,穿过组合电路网络进入下一个寄存器,并完全锁存在该寄存器直到下一个时钟信号到达.一个常用数字同步系统的延时单元由以下三个子系统组成[1]:1)记忆存储元件;2)组合逻辑元件; 3)时钟产生电路和其分配网络(clocktree).这三个子系统的相互关系对电路能否获得最好的性能和可靠性起着关键作用.对任意的有序寄存器对R1、R2,其关系可能为以下两种情况之一[1]:1) R1输出不能仅通过一系列组合逻辑元件传输到R2的输入端;2)存在一组组合逻辑元件直接连接R1的输出端和R2的输入端.在第一种情况下, R1输出端的信号变化不影响同一周期内R2的输入.第二种情况下(用R1yR2表示), R1输出端的信号转变将传到R2的输入端,该情况下R1、R2被称为时序相邻的寄存器对,它们组成了一条本地数据路径.如图1[1]所示, Ri和Rf为一对时序相邻寄存器对,它们分别为本地数据路径的起始和目标寄存器, Ci、Cf分别为驱动Ri和Rf的时钟信号,这两个时钟信号都由同一个时钟信号源通过时钟树产生.该时钟树用以产生同步于每个寄存器的特定时钟信号.从理论上来说,同步事件在同一时刻发生于所有寄存器上.在这个整体时钟策略的基础上,时钟信号到每个寄存器的时间都基于一个全局时间基准来定义.图1 本地数据路径选择时钟周期使得由起始寄存器产生的最迟信号在激活起始寄存器的时钟沿的下一个时钟沿到来时被锁存到目标寄存器中,故时序数据路径中的任意时序相邻寄存器对所允许的最小时钟周期TCP(min)和最大时钟频率fmax可由以下公式算出:1fmax= TCP(min)= tPD(max)+ tskewif+ tsetup.其中tskewif=tCi-tCf,tCi、tCf分别为从时钟源到Ri和Rf的时钟延迟,故tskewif可以为正或者为负(即Ci超前或滞后Cf);tPD(max)为数据路径的总路径延时,可由以下公式计算出:tPD(max)=tC-Q+tL+tInt,其中tC-Q为Ci到达后数据离开起始寄存器所需要的最大时间,tL+tInt为穿过组合逻辑块L和连线所需要的时间;tsetup为寄存器的建立时间.为了保证数据成功锁存进目标寄存器,必须满足两个条件:1)在使能时钟沿到达之前的一段时间内数据必须为有效和稳定的,这段时间称为建立时间,即tsetup.2)在使能时钟沿到达之后的一段时间内数据必须保持稳定,这段时间称为保持时间,即thold.三、时钟偏移1、时钟偏移的定义在整个同步数字系统中,时钟偏移是指时钟信号到达所有寄存器的最大时钟延迟和最小时钟延时之差[1~3],可以由如下公式表示:tskew=tmax-tmin,tmax和tmin分别为时钟源到接收端的最大和最小延时.如果所有时钟同时到达相应寄存器,则时钟偏移为零.2、时钟偏移对时序限制的影响时钟偏移的大小和极性会对系统的性能和可靠性产生好的或差的影响.tskewif相对任意两个时序相邻寄存器对而言,可正可负,而且由于时钟颤动的影响,会出现一定的不确定性,所以在时序分析中均采用最差情况.分析建立时间时采用tskewif为正的情况,分析保持时间时采用tskewif为负的情况.下面将就时钟偏移对同步数字电路的时序限制的影响进行详细分析.1)最大延时数据路径和时钟偏移的关系如果Ci超前Cf,即tskewif=tCi-tCf>0,则称时钟偏移为正时钟偏移.这种情况下主要考虑的是最大延时数据路径的建立时间问题,定义ts为要求信号最迟到达寄存器的时间treq max 和实际到达寄存器的时间tarr的差,TCP为时钟周期.要满足建立时间问题,必须使:ts=treq max-tarr=(TCP-tsetup-tskewif)-tPD(max)=(TCP-tsetup-tskewif)-(tC-Q+tL+tInt)>0 (1)由式(1)可知,正的时钟偏移使得ts减小,系统可达到的最大工作频率减小.2)最小延时数据路径和时钟偏移的关系如果Ci滞后Cf,即tskewif=tCi-tCf<0,则称时钟偏移为负时钟偏移.负时钟偏移可用于提高同步数字系统的最大工作频率,但是可能会导致最小延时路径的保持时间问题.定义th为要求信号实际到达寄存器的时间tarr与最早到达寄存器的时间treq min的差.要满足保持时间问题,必须使: th=tarr-treq min=(tC-Q+tL+tInt)-(thold+tskewif)>0 (2)由式(2)可知,tskewif为负时,th减小,当th<0时,可能导致紊乱情况,将错误的数据信号锁存到寄存器中.四、时钟树的经验结构及设计流程一种有效的方法是缓冲器插入。

ASIC后端设计中低功耗时钟树综合方法

111568 3925923

16233

112311 3942146

表2 两种时钟树面积和标准门单元数量对比 由表2(其中面积单位为平方微米)可以看出:

(1)反向器的数量(743)比缓冲器的数量(598)增加

了23%,也就是说,新的时钟网络的外部充放电节点增多,

平均负载电容降低,Switch Power的变化难以直观判断。

的方法,依靠严格的流程,以大量数据做对比,证明其方法 的可行性。

二、CMOS电路门级功耗的分类和计算方法

CMOS电路中,功耗有4种来源,其总功耗为:

Ptotal=Pdynamic+Pleakage+Pshort-circuit+PDC

(1)

Pdynamic是节点电压越前时对寄生电容充放电所引起的动态

开关功耗;

Pleakage由两部分组成:一部分是MOSFET开关的非理想段态 特性所引起的亚阈值泄露功耗,另一部分是载流子隧道效

应通过薄氧化层所导致的栅极泄露功耗;

Pshort-circuit是CMOS晶体管栅极的上拉和下拉网络同时打开 时输入信号跃迁所产生的瞬态功耗;

PDC 是CMOS电路在低电压摆幅输入信号驱动时所消耗的 静态直流功率[3]。

(2)反向器构成的是时钟网络面积(16223平方微米)

是缓冲器构成时钟网络面积(32614平方毫米)的50%整个

ASIC后端设计中的时钟树综合

ASIC后端设计中的时钟树综合周广;何明华【摘要】Clock tree synthesis is an important part in integrated circuit design nowadays. Therefore, the method of timing-driven placement and limitation of placement density are adopted to achieve good layout effect during the layout design of FFT processor chip. The optimal method of clock tree automatic synthesis and manually modification are employed to reduce clock skew. The strategy of specifying clock tree constraint file, chosing the buffer and modifying clock tree is put forward.The clock tree synthesis of FFT processor chip is completed and the design meets the requirements of design.%时钟树综合是当今集成电路设计中的重要环节,因此在FFT处理器芯片的版图设计过程中,为了达到良好的布局效果,采用时序驱动布局,同时限制了布局密度;为了使时钟偏移尽可能少,采用了时钟树自动综合和手动修改相结合的优化方法,并提出了关于时钟树约束文件的设置、buffer的选型及手动修改时钟树的策略,最终完成了FFT处理器芯片的时钟树综合并满足了设计要求.【期刊名称】《现代电子技术》【年(卷),期】2011(034)008【总页数】3页(P137-139)【关键词】FFT处理器芯片;布局布线;时钟树综合;时钟偏移【作者】周广;何明华【作者单位】福州大学物理与信息工程学院,福建,福州,350002;福州大学物理与信息工程学院,福建,福州,350002【正文语种】中文【中图分类】TN492-340 引言在大规模高性能的ASIC设计中,对时钟偏移(Clock Skew)的要求越来越严格,时钟偏移是限制系统时钟频率的主要因素。

时钟树综合算法

时钟树综合算法时钟树综合算法是在集成电路设计中非常重要的一项技术。

它的作用是将时钟信号传输到整个电路中的各个部分,确保电路的稳定运行。

在现代集成电路中,时钟信号被用来同步各个模块之间的操作。

因为电路中的不同模块需要按照一定的顺序进行操作,所以时钟信号的传输是非常关键的。

时钟信号不仅要准确地传输到每个模块,还需要满足一些设计约束,比如时延、功耗等方面的要求。

时钟树综合算法的目标是在满足设计约束的前提下,最小化时钟信号路径的时延和功耗。

为了实现这个目标,时钟树综合算法通常包括以下几个步骤:1. 时钟树构建:首先,根据设计规格和约束,确定时钟树的拓扑结构和时钟信号的传输路径。

这个步骤中需要考虑信号的时延、功耗以及电磁干扰等因素。

2. 时钟树优化:在确定了时钟树的拓扑结构后,需要对时钟信号路径进行优化。

优化的目标是使得时钟信号的时延最小化,从而提高电路的工作频率和性能。

常用的优化技术包括缩短时钟信号路径、减少时钟缓冲器的数量等。

3. 时钟树布线:优化后的时钟树需要进行布线,将时钟信号传输到各个模块。

布线的目标是使得时钟信号的功耗尽可能小,并且满足电磁兼容性和电磁互容性的要求。

为了达到这个目标,布线时需要考虑时钟线的走向、间距、层间距、抗干扰措施等因素。

4. 时钟树验证:最后,根据设计规格和约束进行时钟树的验证。

验证的目标是确保时钟信号能够准确地传输到每个模块,并满足时延和功耗等设计要求。

验证过程需要使用专门的工具进行模拟和分析,以确保时钟树的正确性。

时钟树综合算法在集成电路设计中起着重要的作用。

它可以帮助设计工程师在设计过程中更好地管理和优化时钟信号,从而提高电路的性能和稳定性。

通过合理的时钟树设计和优化可以降低时延和功耗,提高电路的工作频率和可靠性。

同时,时钟树综合算法也需要与其他的电路设计工具和算法进行配合,共同完成电路的设计和验证。

总之,时钟树综合算法是一项非常重要的电路设计技术,它对电路的性能和稳定性具有重要影响。

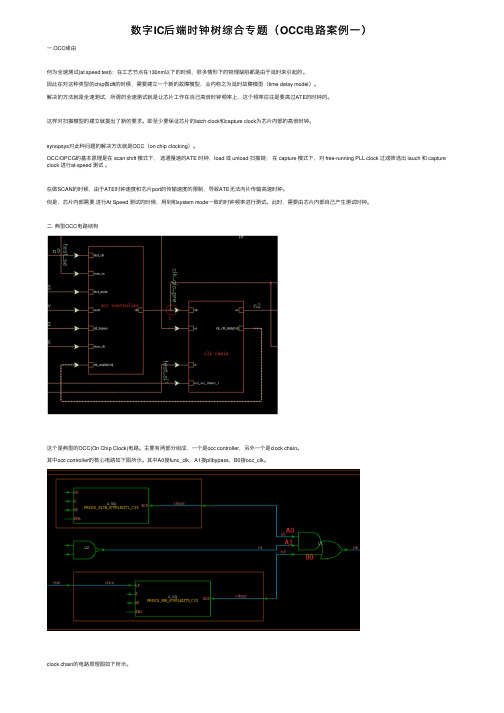

数字IC后端时钟树综合专题(OCC电路案例一)

数字IC后端时钟树综合专题(OCC电路案例⼀)⼀.OCC缘由何为全速测试(at speed test):在⼯艺节点在130nm以下的时候,很多情形下的物理缺陷都是由于延时来引起的。

因此在对这种类型的chip做dft的时候,需要建⽴⼀个新的故障模型,业内称之为延时故障模型(time delay model)。

解决的⽅法就是全速测试,所谓的全速测试就是让芯⽚⼯作在⾃⼰⾼倍时钟频率上,这个频率往往是要⾼过ATE的时钟的。

这样对扫描模型的建⽴就提出了新的要求。

即⾄少要保证芯⽚的latch clock和capture clock为芯⽚内部的⾼倍时钟。

synopsys对此种问题的解决⽅法就是OCC(on chip clocking)。

OCC/OPCG的基本原理是在 scan shift 模式下,选通慢速的ATE 时钟,load 或 unload 扫描链;在 capture 模式下,对 free-running PLL clock 过滤筛选出 lauch 和 capture clock 进⾏at-speed 测试。

在做SCAN的时候,由于ATE时钟速度和芯⽚port的传输速度的限制,导致ATE⽆法向⽚传输⾼速时钟。

但是,芯⽚内部需要进⾏At Speed 测试的时候,⽤到和system mode⼀致的时钟频率进⾏测试。

此时,需要由芯⽚内部⾃⼰产⽣测试时钟。

⼆. 典型OCC电路结构这个是典型的OCC(On Chip Clock)电路。

主要有两部分组成,⼀个是occ controller,另外⼀个是clock chain。

其中occ controller的核⼼电路如下图所⽰。

其中A0接func_clk,A1接pllbypass,B0接occ_clk。

clock chain的电路原理图如下所⽰。

OCC电路插⼊⽅式主要有两种⽅式,⽬前⼤部分应该还是采⽤第⼀种⽅式,如在综合dft阶段⼯具⾃动插⼊的⽅式。

1. DFT Compiler⾃动插⼊。

芯片中时钟树综合质量评价指标

芯片中时钟树综合质量评价指标芯片中的时钟树综合质量评价指标时钟树综合质量在芯片设计中起着至关重要的作用,它直接影响着整个芯片的性能和稳定性。

时钟树综合质量评价指标是评判时钟树设计是否合理、性能是否优越的重要标准。

在芯片设计过程中,工程师需要充分了解时钟树综合质量评价指标的相关知识,才能设计出高质量的时钟树,确保芯片性能的稳定和可靠。

一、时钟树综合质量评价指标的重要性时钟树综合质量评价指标是评判时钟树设计优劣的重要标准,它直接影响着芯片的工作稳定性、功耗和时序性能。

一个良好的时钟树设计能够减小时钟树网络的延迟、功耗和时钟偏移,提高时钟树的稳定性和可靠性,从而提升整个芯片的性能和功耗表现。

二、时钟树综合质量评价指标的内容时钟树综合质量评价指标主要包括时钟树的布线长度、时钟树的网络拓扑结构、时钟树的功耗和时钟偏移等指标。

其中,时钟树的布线长度直接影响着时钟信号传输的延迟和功耗,时钟树的网络拓扑结构则直接决定了时钟信号的传输效率和时序一致性,时钟树的功耗和时钟偏移则是评价时钟树稳定性和可靠性的重要指标。

三、时钟树综合质量评价指标的影响因素时钟树综合质量评价指标受到多种因素的影响,包括芯片的工作频率、布局结构、设计规则和工艺制程等。

不同的工艺制程和设计规则会对时钟树的布线长度和功耗产生影响,布局结构的不同也会影响时钟树网络的拓扑结构和时钟偏移。

工作频率对时钟树的设计要求也是不容忽视的因素,高频率下的时钟树设计需要更高的稳定性和可靠性。

四、时钟树综合质量评价指标的优化方法针对时钟树综合质量评价指标的影响因素,工程师可以采取一系列优化方法来改善时钟树的设计质量。

在布局设计阶段,可以采用合理的布局规则和工艺制程,来减小时钟树的布线长度和功耗;在时钟树综合阶段,可以优化时钟树的拓扑结构和时钟网络,来提高时钟信号传输效率和时序一致性;在时钟树布线阶段,可以采用时钟树缓冲技术和时钟树匹配技术,来降低时钟树的功耗和时钟偏移。

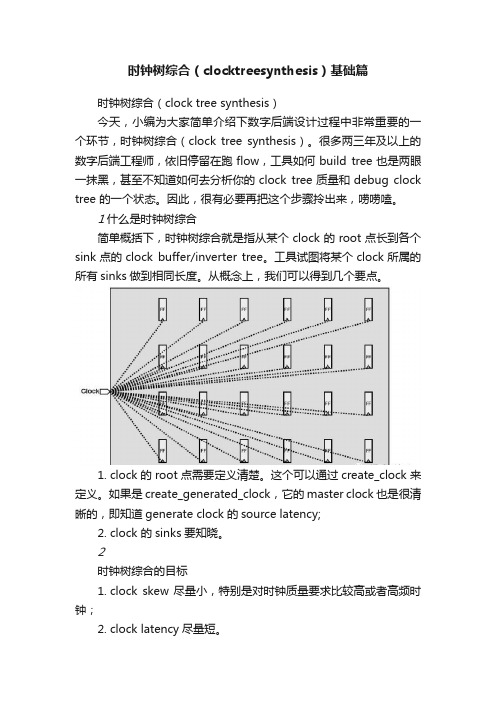

时钟树综合(clocktreesynthesis)基础篇

时钟树综合(clocktreesynthesis)基础篇时钟树综合(clock tree synthesis)今天,小编为大家简单介绍下数字后端设计过程中非常重要的一个环节,时钟树综合(clock tree synthesis)。

很多两三年及以上的数字后端工程师,依旧停留在跑flow,工具如何build tree也是两眼一抹黑,甚至不知道如何去分析你的clock tree质量和debug clock tree 的一个状态。

因此,很有必要再把这个步骤拎出来,唠唠嗑。

1什么是时钟树综合简单概括下,时钟树综合就是指从某个clock的root点长到各个sink点的clock buffer/inverter tree。

工具试图将某个clock所属的所有sinks做到相同长度。

从概念上,我们可以得到几个要点。

1.clock的root点需要定义清楚。

这个可以通过create_clock来定义。

如果是create_generated_clock,它的master clock也是很清晰的,即知道generate clock的source latency;2.clock 的sinks要知晓。

2时钟树综合的目标1.clock skew尽量小,特别是对时钟质量要求比较高或者高频时钟;2.clock latency尽量短。

那么,为了达到以上两大目标,数字后端工程师任到重远。

首先,我们拿到一个design,需要先花点时间,理清楚clock 结构,各种mode如何切换。

同时,需要不断向前端设计人员请教design相关(后端需要知道的信息),比如哪些clock是需要同步,哪些是异步。

3时钟树质量分析可能很多工程师估计都没用过下面这个功能吧。

ICC/ICC2中这个功能还是很不错的,可以帮助工程师快速理清clock的结构和debug clock tree 质量。

特地向大家推荐下。

借助上面推荐的方法GUI操作辅助我们分析。

选中某个clock,然后查看clock的时钟树综合结果,比如clock buffer的级数,clock latency,clock的最短路径和最长路径。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

时钟树偏移分析

拥塞图分析

为了得到更准确的拥塞图,执行GlobalRoute命令进 为了得到更准确的拥塞图,执行GlobalRoute命令进 GlobalRoute 行全局布线,再执行axgDisplayPLCongestionMap axgDisplayPLCongestionMap命令对拥 行全局布线,再执行axgDisplayPLCongestionMap命令对拥 塞图显示方式进行设置,然后按快捷键F6 F6在版图上显示布 塞图显示方式进行设置,然后按快捷键F6在版图上显示布 线拥塞的情况如图所示,从中可知仅存在4处蓝色( 线拥塞的情况如图所示,从中可知仅存在4处蓝色(溢出数 1)区域 因此可判断拥塞在允许范围内。 区域, 为1)区域,因此可判断拥塞在允许范围内。

CTS开始时的设计状态 开始时的设计状态

布局-----完成 布局-----完成 ----电源和地网络---------预布线 电源和地网络-----预布线 估计阻塞-----------可接受 估计阻塞------可接受 估计时序------可接受( ------可接受 估计时序------可接受(~0ns) 估计最大电容/传输时间---------没有违规 估计最大电容/传输时间-----没有违规 高扇出网络: 高扇出网络: Reset,Scan Enable已经综合 Enable已经综合 时钟还没有综合

时钟树偏移分析

执行命令

执行命令astSkewAnalysis得出时钟 执行命令astSkewAnalysis得出时钟 astSkewAnalysis 偏移报告,如图所示,从图中可知最 偏移报告,如图所示, 长时钟路径延时为1.487ns 1.487ns, 长时钟路径延时为1.487ns,最短时 钟路径延时为1.409ns 1.409ns, 钟路径延时为1.409ns,全局时钟偏 移为0.078ns 0.078ns。 移为0.078ns

带有SDC不确定的传播时钟 不确定的传播时钟 带有

如果SDC不确定值包括抖动和时间裕量,Astro仍 如果SDC不确定值包括抖动和时间裕量,Astro仍 SDC不确定值包括抖动和时间裕量,Astro 能计算实际的时钟网络延时,同时模仿这些效应 能计算实际的时钟网络延时, 调整SDC set_clock_uncertainty的值 SDC中 调整SDC中set_clock_uncertainty的值 通过估计偏移值减少这个值 执行相同的命令 sdc “set_propagated_clock [all_clocks] set_propagated_clock [all_clocks]” 调节下面的时序设置项 Uncertainty” Unset “Ignore Clock Uncertainty Ignore Clock” Unset “Ignore Propagated Clock Ignore

Starting Point Before CTS

CTS目标 目标

符合buffer约束(不符合该约束会报违规) 符合buffer约束(不符合该约束会报违规) buffer约束 最大传输时间延迟 最大负载电容 最大扇出 最大buffer buffer级数 最大buffer级数 符合时钟树目标(不会报违规) 符合时钟树目标(不会报违规) 最大偏移 根据Min/Max delay插入延迟 根据Min/Max delay插入延迟

同步Pins和忽略 和忽略Pins 同步 和忽略

同步Pins: 同步Pins: CTS优化达到 CTS优化达到 buffer约束 约束( buffer约束(最大传 输时间/电容) 输时间/电容)和时 钟树目标(偏移, 钟树目标(偏移,插 入延时等) 入延时等)) 忽略Pins: 忽略Pins: CTS加入一个小的 CTS加入一个小的 buffer去隔离所有 buffer去隔离所有 的Pins 忽略buffer buffer约束 忽略buffer约束 最大传输时间/ (最大传输时间/电 容和时钟树目标) 容和时钟树目标)

时钟树时序分析

使用astReportTiming命令进行时序分析得 使用astReportTiming命令进行时序分析得 astReportTiming 如图所示,从中可知建立时间、保持时间、 如图所示,从中可知建立时间、保持时间、最 大电容和最大过渡时间满足要求。 大电容和最大过渡时间满足要求。

指定非默认的偏移(例 指定非默认的偏移 例3)

不是一个时钟, 不是一个时钟,现在假设所有的时钟有不同 的不确定值,用更好的方法: 的不确定值,用更好的方法: 输入axSetIntparam acts ingore acts” 输入axSetIntparam “acts “ingore set_clock_uncertainty” 命令让Astro set_clock_uncertainty 0命令让Astro SDC文件中的值而不是GUI中的偏移目标 文件中的值而不是GUI 用SDC文件中的值而不是GUI中的偏移目标 值

时钟buffer约束 约束 时钟

最大tran/cap/fanout: 最大tran/cap/fanout: 如果在多个地方指定 ,SDC文件或Astro默 文件或Astro (库,SDC文件或Astro默 Astro使用最小值 认), Astro使用最小值 最大buffer buffer级数 最大ห้องสมุดไป่ตู้uffer级数 用默认的初始值(20) 用默认的初始值(20) 只有在仔细分析或基于 以住经验的基础上才需 要调整 如果设置太紧, 如果设置太紧,违规可能 不能修复

插入延时和忽略约束

插入延时目标: 插入延时目标: 用这些设置去控制 最小/ 最小/最大插入延时 默认在SDC SDC的插入 默认在SDC的插入 延时具有优先, 延时具有优先,除非 执行axSetIntparam 执行axSetIntparam “acts “ingore acts” ingore acts set_clock_latency” set_clock_latency 命令才忽略SDC SDC设 1命令才忽略SDC设 置 你可以选择完全忽 SDC或库的约束进 略SDC或库的约束进 行CTS

Post-CTS设置 传播时钟 设置:传播时钟 设置

CTS后,Astro能计算实际的时钟网络延时而 CTS后,Astro能计算实际的时钟网络延时而 不是使用SDC SDC中估计的理想值 不是使用SDC中估计的理想值 执行下面命令: 执行下面命令: sdc “set_propagated_clock [all_clocks]” 调整下面的时序设置项 set “Ignore Clock Uncertainty” Unset “Ignore Propagated Clock”

CTS流程 流程

时钟树综合

建立buffer树去平衡负载达到最小时钟偏移 建立buffer树去平衡负载达到最小时钟偏移 buffer

时钟树综合

延迟线加入去符合插入延迟目标

时钟树的起点和终点

时钟树起点是在.SDC文件 时钟树起点是在.SDC文件 .SDC 定义的时钟源: 定义的时钟源: create_clock –p 2 CLOCK p 时钟树终点在Astro Astro定义 时钟树终点在Astro定义 Pins” 的”stop Pins 两种类型的” Pins” 两种类型的”stop Pins 同步Pins: Pins:时序单元和宏 同步Pins:时序单元和宏 单元的Clock 单元的Clock Pins 忽略Pins: Pins:其它 忽略Pins:其它

默认的Skew Optimization 默认的

时钟延时在每一个时钟域内全部进行平衡, 时钟延时在每一个时钟域内全部进行平衡,经过所 有的主时钟和产生时钟的clock pin, clock有的主时钟和产生时钟的clock-pin,去减少时钟 偏移到0 偏移到0,或尽可能小

时钟公共选项设置

默认的设置如图 时钟公共选项设置 在CTS和优化之前进 CTS和优化之前进 行设置

指定非默认的偏移(例 指定非默认的偏移 例1)

若所有时钟在 SDC文件中有 SDC文件中有 set_clock_unc ertainty值为 ertainty值为 0.2ns,你想在 0.2ns,你想在 CTS时用这个值 CTS时用这个值 而不是默认值0 而不是默认值0, 则在Target 则在Target Skew中设置 中设置0.2 Skew中设置0.2 所有时钟用相 同的偏移值进 行综合

CTS) 时钟树综合 (CTS CTS

列出在CTS前的设计状态 列出在CTS前的设计状态 CTS 为设计单元进行CTS 为设计单元进行CTS 识别隐含的时钟树起点和终点, 识别隐含的时钟树起点和终点,明确什 么时候需要更改 通过约束和目标来控制CTS 通过约束和目标来控制CTS 识别三种不同的时钟偏移优化方法 执行推荐的CTS CTS和优化流程 执行推荐的CTS和优化流程 分析时序和CTS CTS后的时钟具体情况 分析时序和CTS后的时钟具体情况

Post-CTS优化 根据需要反复执行 优化:根据需要反复执行 优化

对于一个大的设计, 对于一个大的设计,每 次优化目标只有一个, 次优化目标只有一个,如 修复hold hold时间等 修复hold时间等

Post-CTS布局优化结果 布局优化结果

通过逻辑优化和单元重新放 置来修复时序( 置来修复时序(建立时间和保 持时间)、最大电容和最大过 持时间) 渡时间违规可能会影响时钟 网络----FFS可能会被移动. 网络----FFS可能会被移动. ----FFS可能会被移动 这将可能影响时钟偏移和插 入延时. 入延时. 因此要分析时钟偏移和插入 延时! 延时! 如果想不影响时钟偏移和插 入延时,则需保持FFS FFS位置固 入延时,则需保持FFS位置固 执行clock >Utilitiesclock定,执行clock->UtilitiesTree… >Mark Clock Tree

时钟树综合结果

时钟buffer增加 时钟buffer增加 buffer 阻塞可能会增加 非时钟树单元可能 会被移动到不理想 的位置 可能会引起新的时 序和最大tran/cap 序和最大tran/cap 违规