第六章 习题解答

第六章习题解答

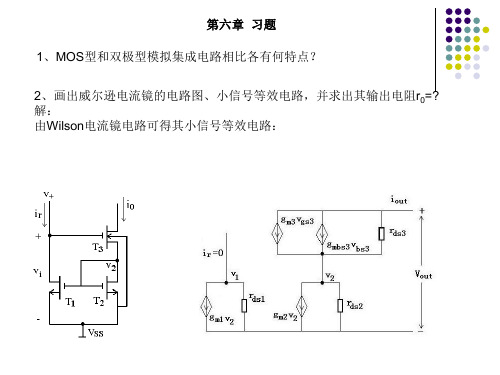

g m1 g m3 gm2

rds1

rds3

g m rds1 rds3 设g m1 g m2 g m3 g m

3 、 已 知 如 下 图 所 示 运 放 , 其 中 MOS 管 器 件 参 数 : Kn=25A/V2,Kp=10A/V2, n=p==0.04V-1, 则:

(1)、根据图中所示电路结构判断宜选N阱还是P阱工艺实现集成?简述理由。 (2)、若VDD=5V,VSS=-5V,求运放的静态功耗Pdiss和小信号电压增益AV(忽略 输出级产生的负载)。

gds5 p Ids5 0.04 40 1.6S

g ds8 n I ds8 0.04 40 1.6S

将以上各值代入增益表达式中,可求出该电路小 信号增益:

Av

109.5 74.8 2.4 2 1.6 2

533.2

解:

(1) 应采用P阱CMOS工艺。理由: 由电路拓扑可知,该电路为无缓冲二级放大器,差分放大器作输入级,为消除

输入NMOS管的衬底偏置效应导致的阈值电压漂移,应使其VBS=0。如将NMOS管 做在p型衬底上,则衬底必须接最低电位Vss,而NMOS差分对的共同源端电位至少 比Vss高一个饱和压降Vdsat7,必有VBS<0,显然有衬偏效应。因此应考虑将NMOS 差分对做在P阱中,利用阱的电位浮动技术,将其B、S短接,确保VBS=0。

Av

gm2 gds2 gds4

gm5 gds8 gds5

gm2

2 W L

2

kn

I ds2

ห้องสมุดไป่ตู้

2 4 25 60 109.5S

gm5

2

W L

5

k

p

I ds5

2 7 10 40 74.8S

C语言第6章习题解答

第6章函数和模块设计【习题6-1】更正下面函数中的错误。

(1)返回求x和y平方和的函数。

(2)返回求x和y为直角边的斜边的函数。

sum_of_sq(x,y) hypot(double x,double y){ {double x,y; h=sqrt(x*x+y*y);return(x*x+y*y); return(h);} }程序如下:/*c6_1(1).c*/ /*c6_1(2).c*/(1) (2)double sum_of_sq(double x,double y) double hypot(double x,double y) { {return(x*x+y*y); double h;} h=sqrt(x*x+y*y);return(h);}【习题6-2】说明下面函数的功能。

(1)itoa(int n,char s[ ])(2)int htod(char hex [ ]){ { int i,dec=0;static int i=0,j=0; for(i=0;hex[i]!='\0';i++)int c; { if(hex[i]>='0'&&hex[i]<='9') if(n!=0) dec=dec*16+hex[i]-'0';{ if(hex[i]>='A'&&hex[i]<='F') j++; dec=dec*16+hex[i]-'A'+10;c=n%10+'0'; if(hex[i]>='a'&&hex[i]<='f') itoa(n/10,s); dec=dec*16+hex[i]-'a'+10;s[i++]=c; }} return(dec);else }{ (3)void stod(int n)if(j==0) s[j++]='0'; { int i;s[j]='\0'; if(n<0){ putchar('-');n=-n;} i=j=0; if((i=n/10)!=0) stod(i);} putchar(n%10+'0');} }功能:(1)(略)(2)(略)【习题6-3】编写已知三角形三边求面积的函数,对于给定的3个量(正值),按两边之和大于第三边的规定,判别其能否构成三角形,若能构成三角形,输出对应的三角形面积。

微积分第六章习题解答

2

3、利用定积分的几何意义,说明下列等式: 利用定积分的几何意义,说明下列等式: 1 1 π 2

(1)

∫ 0 2 x dx = 1 ;

y

y = 2x

(2)∫

0

1 − x dx =

y

4

;

2

x2 + y2 = 1

o

1 x

o

(3) ∫

π

−π

sin x dx = 0 ;

( 4)

∫

π

1

x

2 π − 2

cos x dx = 2∫ 2 cos x dx .

1 1 e−x 0 1 dx + ∫ dx = − ln(1 + e − x ) + ln(1 + x ) =∫ 01+ x −1 1 + e − x 0 −1

e ⋅ y ′ + cos x = 0 ,

y′ = −

cos x e

y

.

11

4、求下列极限: 求下列极限: (2) lim

∫ 0 arctan t dt

x2

x

0 " "型 0

arctan x 1 = lim = . x →0 2x 2

x →0

sin 2 t dt ∫π

x

(3) lim π

x→ 2

2

F ′( x ) = f ( x ) + x f ′( x ) ,

∃c ∈ (ξ ,1) ⊂ (0,1) , 使 F ′( c ) = 0 ,即 f (c) + c f ′(c) = 0 ,

f (c ) 而 c > 0 , 即有 f ′(c ) = − . c

第六章金属电子论习题

电导率

q2 m*

n (EF0 )

弛豫时间

( E F0

)

m*

nq 2

平均自由程

v (EF0 )

m*v

nq 2

kF

nq2

0 K到室温之间的费密半径变化很小

9

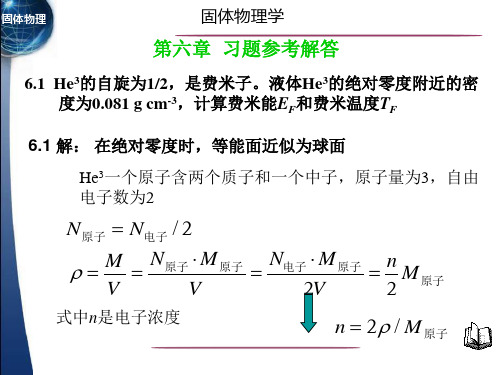

固体物理

固体物理学

或近自由电子近似情况下

EF

EF0

1

2

12

kBT EF0

2

kF m

1.055

10 34 1.20 9.1110 31

0

10

1.39 106 m / s

固体物理

固体物理学

(4) 费密球面的横截面积

S (kF sin )2 4.52 sin 2m2

是 与 轴之间的夹角

kF

(3n

2

)

1 3

8

固体物理

固体物理学

(5) 在室温以及低温时电子的平均自由程

3

固体物理

固体物理学

N

N(

( E F0

E

)

)

4V

(

2m h2

3N / 2EF0

)3/2 E1/2

N(E)

(

EF EF0

)1/

2

N

(

EF0

)

TF

EF0 kB

3N 2kB N (EF0 )

3 6.0221023 21.3811023 3.321042

19624K

N

固体物理

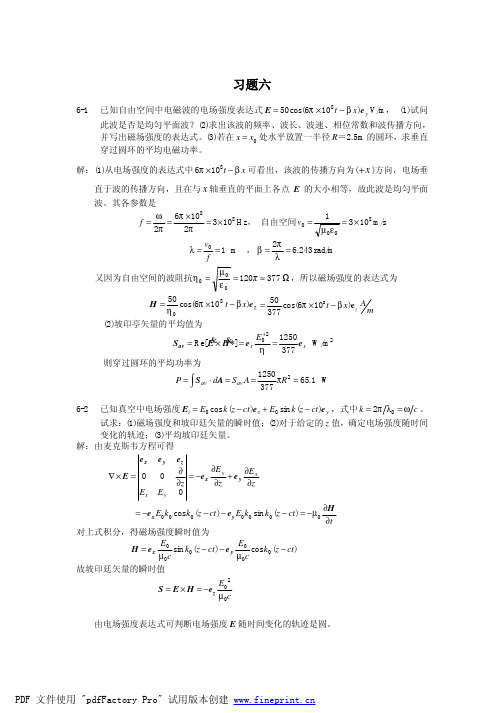

第6章习题解答

根据题意,可知:平面波的角频率ω = 18π ×106 rad s ;波数 k = 1π rad m 3

由此得出

频率: f = ω = 9×106 Hz ; 2π

相速: vp = f λ = 54 ×106 m s

波长: λ = 2π = 6m k

能流密度矢量为

S

=

E

×

H

=

ex

1 η

sin2 (18π

e

z

A/m

(3)当t = 10−8 s 时,为使电场强度为最大正值,应有

PDF 文件使用 "pdfFactory Pro" 试用版本创建

2π ×108 t − 4π x + π = 2π ×108×10−8 − 4π x + π = ±2nπ

36

36

解之得的电场强度最大正值的位置在

(V/m)

f = c = 3×108 = 45 ×108 = 1.43×109 (Hz) λ π /15 π

于是可知

H = −e y 3π cos(9 ×109 t + 30z) (A/m)

E = e x 360π 2 cos(9 ×109 t + 30z) (V/m)

6-4 在自由空间中,某电磁波的波长为 0.2m。当该波进入到理想电介质后,波长变为 0.09m。

x = 13 m 3 n = 13 m nλ 82 8

(n = 0,1,2L)

6-9 某电台发射 600KHz 的电磁波,在离电台足够远处可以认为是平面波。设在某一点 a, 某瞬间的电场强度为10−4 V/m,求该点瞬间的磁场强度。若沿电磁波的传播方向前行 100 m,到达另一点 b,问该点要迟多少时间,才具有10−4 V/m 电场。

《线性代数》第6章习题解答

1.2. 已知向量空间的一个基为α1=(1 1 0)T ,α2=(1 0 1)T,α3=(0 1 1 )T ,试求α=(2 0 0)T在上述基下的坐标。

解. 设α=()321ααα⎪⎪⎪⎭⎫ ⎝⎛321x x x , ()321ααα=⎪⎪⎪⎭⎫ ⎝⎛110101011()321ααα-1=⎪⎪⎪⎭⎫ ⎝⎛---11111111121所以 ⎪⎪⎪⎭⎫ ⎝⎛321x x x =()321ααα-1α=⎪⎪⎪⎭⎫⎝⎛---1111111111⎪⎪⎪⎭⎫ ⎝⎛002=⎪⎪⎪⎭⎫ ⎝⎛-111 2.验证α1=(1 -1 0)T,α2=(2 1 3)T,α3=(3 1 2 )T为R 3的一个基,并把α=(5 0 7)T ,β=(-9 -8 -13)T用这个基线性表示。

解.设()321ααα=⎪⎪⎪⎭⎫ ⎝⎛-230111321,321ααα= 230111321-= -6 ≠0所以α1,α2,α3为R 3的一个基。

设α=()321ααα⎪⎪⎪⎭⎫ ⎝⎛321x x x ,β=()321ααα⎪⎪⎪⎭⎫ ⎝⎛321y y y由()αααα21=A =⎪⎪⎪⎭⎫ ⎝⎛-723001115321→⎪⎪⎪⎭⎫⎝⎛-220054305321得α=()321ααα⎪⎪⎪⎭⎫ ⎝⎛321x x x =()321ααα⎪⎪⎪⎭⎫⎝⎛-132=2α1+3α2-α3 ,又有()βααα21=A=⎪⎪⎪⎭⎫ ⎝⎛----1323081119321→⎪⎪⎪⎭⎫ ⎝⎛---4200174309321 得β=()321ααα⎪⎪⎪⎭⎫ ⎝⎛321y y y =()321ααα⎪⎪⎪⎭⎫⎝⎛--233=3α1-3α2-2α3 。

3.下列n 阶方阵的集合,关于矩阵的加法和数乘矩阵两种运算是否构成线性空间?(1)n 阶对称矩阵全体所成之集合S ; (2)n 阶可逆矩阵全体所成之集合R ;(3)主对角线上各元素之和等于零的n 阶矩阵全体所成之集合T 。

高等代数第6章习题解

第六章习题解答习题6.11、设2V R =,判断下面V 到V 的映射哪些是V 的线性变换,哪些不是? (1),()x x y V f y y αα+⎛⎫⎛⎫=∈=⎪ ⎪⎝⎭⎝⎭;(2),()x x y V f y y αα-⎛⎫⎛⎫=∈= ⎪ ⎪⎝⎭⎝⎭;(3)2,()x y V f y x y αα+⎛⎫⎛⎫=∈=⎪ ⎪+⎝⎭⎝⎭; (4)0,()x V f y αααα⎛⎫=∈=+⎪⎝⎭,0V α∈是一个固定的非零向量。

(5)0,()x V f y ααα⎛⎫=∈= ⎪⎝⎭,0V α∈是一个固定的非零向量。

解:(1)是。

因为1122(,),(,),x y x y k F αβ''∀==∀∈,有1212121122121212()()()x x x x y y x y x y f f f f y y y y y y αβαβ++++++⎛⎫⎛⎫⎛⎫⎛⎫+===+=+ ⎪ ⎪ ⎪ ⎪++⎝⎭⎝⎭⎝⎭⎝⎭11111111()()kx kx ky x y f k f k kf ky ky y αα++⎛⎫⎛⎫⎛⎫==== ⎪ ⎪ ⎪⎝⎭⎝⎭⎝⎭(2)是。

因为1122(,),(,),x y x y k F αβ''∀==∀∈,有1212121122121212()()()()x x x x y y x y x y f f f f y y y y y y αβαβ++-+--⎛⎫⎛⎫⎛⎫⎛⎫+===+=+ ⎪ ⎪ ⎪ ⎪++⎝⎭⎝⎭⎝⎭⎝⎭11111111()()kx kx ky x y f k f k kf ky ky y αα--⎛⎫⎛⎫⎛⎫==== ⎪ ⎪ ⎪⎝⎭⎝⎭⎝⎭(3)不是。

因为12121212122()x x y y f f y y x x y y αβ+++⎛⎫⎛⎫+== ⎪ ⎪++++⎝⎭⎝⎭而 121211*********()()y y y y f f x y x y x x y y αβ++++⎛⎫⎛⎫⎛⎫+=+= ⎪ ⎪ ⎪+++++⎝⎭⎝⎭⎝⎭所以()()()f f f αβαβ+≠+(4)不是。

习题解答(第六章)

C 语言程序设计习题解答(第六章)6.1 题目略[解答] (1) A (2) A (3) C (4) D6.2 略6.3 从键盘输入3个整数, 要求设3个指针变量p1, p2, p3, 使p1指向3个数中的最大者, p2指向次大者, p3指向最小者, 最后按由大到小的顺序输出这3个数.[解答]#include <stdio.h>void main(){int x1, x2, x3, *p1=&x1, *p2=&x2, *p3=&x3, *p;printf("请输入3 个整数: ");scanf("%d%d%d", &x1, &x2, &x3);if(*p1<*p2){p=p1; p1=p2; p2=p;}if(*p1<*p3){p=p1; p1=p3; p3=p;}if(*p2<*p3){p=p2; p2=p3; p3=p;}printf("从大到小: %d, %d, %d\n", *p1, *p2, *p3);}6.4 想使指针变量pt1指向a和b中的较大者, pt2指向a和b中的较小者, 请问以下程序能否达到此目的?#include <stdio.h>void swap(int *p1, int *p2){int *p;p=p1; p1=p2; p2=p;}int main(void){int a, b;int *pt1, *pt2;scanf("%d, %d", &a, &b);pt1=&a; pt2=&b;if(a<b) swap(pt1, pt2);printf("%d, %d\n", *pt1, *pt2);return 0;}请分析此程序的执行情况, 指出pt1和pt2的指向并修改程序, 使之能够实现题目要求. [解答]main函数调用swap函数时, 将指针pt1和pt2的值分别赋给形式参数p1和p2, pt1与p1虽然都指向变量a, 但它们是不同的指针变量, 同样, pt2与p2也是不同的指针变量, swap函数中虽然改变了p1和p2的指向, 但不影响main函数中pt1和pt2的指向. 为了实现题目的要求, 可以修改程序, 将pt1与pt2的地址传给函数swap, 同时将swap的形式参数改为二级指针. 正确的程序如下:#include <stdio.h>void swap(int **p1, int **p2){int *p;p=*p1; *p1=*p2; *p2=p;}int main(void){int a, b;int *pt1, *pt2;scanf("%d, %d", &a, &b);pt1=&a; pt2=&b;if(a<b) swap(&pt1, &pt2);printf("%d, %d\n", *pt1, *pt2);return 0;}6.5 略6.6(1) 想输出数组a的10个元素, 用以下程序行不行? 为什么?#include <stdio.h>void main(){int a[10]={1, 2, 3, 4, 5, 6, 7, 8, 9, 10}, i;for(i=0; i<10; i++, a++)printf(“%d”, *a);}请修改程序使之能实现题目要求.(2) 想输出数组a的10个元素, 用以下程序行不行? 请与上题对比并进行分析, 得到必要的结论.#include <stdio.h>void print_arr(int a[], int n){int i;for(i=0; i<n; i++, a++)printf("%d", *a);}void main(){int arr[10]={1, 2, 3, 4, 5, 6, 7, 8, 9, 10};print_arr(arr, 10);}请修改程序使之能实现题目要求.[解答](1) 不行, 因为数组名a表示该数组的首地址, 是一个指针常量, 其值是不能改变的, 因此不能进行++ 运算. 正确的程序如下:void main(){int a[10]={1, 2, 3, 4, 5, 6, 7, 8, 9, 10}, i;for(i=0; i<10; i++)printf("%d ", *(a+i));}(2) 可以, 因为形参数组本质上是一个指针变量, 其值可以改变, 可以进行++ 运算.6.7 有一个数列, 含有20个整数, 现要求编一个函数, 能够对从指定位置开始的几个数按相反顺序排列, 并在main函数中输出新的数列. 例如, 原数列为:1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20若要求对从第5个数开始的10个数进行逆序处理, 则得到的新数列为1, 2, 3, 4, 14, 13, 12, 11, 10, 9, 8, 7, 6, 5, 15, 16, 17, 18, 19, 20[解答]#include <stdio.h>#define N 20void reverse(int a[], int m, int k) /* 将数组a 从第m 个数开始的k 个数按相反顺序排列*/ {int temp, *p, *q;for(p=a+m-1, q=p+k-1; p<q; p++, q--) /* p, q 初始时分别指向要反序的起始与终止位置*/{temp=*p; *p=*q; *q=temp;}}void main(){int i, m, k, a[]={1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20};printf("请输入要反序的数列的起始位置和长度: ");scanf("%d%d", &m, &k);reverse(a, m, k);printf("反序后的数列为: ");for(i=0; i<N; i++)printf("%d ", a[i]);printf("\n");}6.8 有n个人围成一圈, 顺序排号, 从第1号开始报数, 从1报到m, 凡报到m的人退出圈子.问最后留下的是原来第几序号的人? 要求如下:(1) 用函数实现报数并退出;(2) n和m的值由main函数输入并通过实参传递给该函数, 最后结果由main函数输出;(3) 要求使用指针.[解答]#include <stdio.h>#define N 100int baoshu(int a[], int n, int m) /* n 个人围成一圈, 从1 到m 报数的函数*/{int i, cnt, num, *p, last;for(i=0; i<n; i++) /*给每一个人赋予一个初始位置号*/*(a+i)=i+1;cnt=0; /* cnt 用于从1 到m 记数, 模拟报数*/num=0; /* num 用于记录出圈人数*/while(num<n)for(p=a; p<a+n; p++) /* 报数*/if(*p) /* 若*p 在圈中*/{cnt++; /* 报数记数器加1 */if(cnt==m) /* 若报数记数器到达m */{/* 处理出圈事宜*/last=*p; /* 用last 记录当前出圈者的位置号*/*p=0; /* 位置号清零, 表示从圈中删除此人*/cnt=0; /* 报数记数器清零, 下一个人重新开始报数*/num++; /* 出圈人数加1 */}}return last;}void main(){int n, m;int a[N]; /* 用数组 a 记录每一个人在圈中的位置 */printf("输入人数 n (<%d) 和所报的最大数 m: ", N);scanf("%d%d", &n, &m);printf("最后留下的是原来第 %d 号的人.\n", baoshu(a, n, m));}6.9 有一个二维数组a, 大小为53⨯, 其元素为⎥⎥⎥⎦⎤⎢⎢⎢⎣⎡=2927252321191715131197531a (1) 请说明以下各表达式的含义:a, a+2, &a[0], a[0]+3, *(a+1), *(a+2)+1, *(a[1]+2), &a[0][2], *(a[0][2]), *(*(a+2)+1), a[1][3].(2) 如果输出a+1和&a[1][0], 它们的值是否相等? 为什么? 它们各代表什么含义?[解答](1)a : 数组首地址, 等价于 &a[0]a+2 : 第 2 行的地址, 等价于 &a[2]&a[0] : a[0]的地址, 即第0行的地址, 也是整个数组的首地址, 等价于a a[0]+3 : 第 0 行第 3 列元素的地址, 即 &a[0][3]*(a+1) : 第 1 行第 0 列元素的地址, 等价于 a[1] 和 &a[1][0]*(a+2)+1 : 第 2 行第 1 列元素的地址, 即与 &a[2][1] 等价*(a[1]+2) : 第 1 行第 2 列元素的值, 即 a[1][2] = 15&a[0][2] : 第 0 行第 2 列元素的地址*(a[0][2]) : 无意义*(*(a+2)+1) : 第 2 行第 1 列元素的值, 即 a[2][1] = 23a[1][3] : 第 1 行第 3 列元素的值, 等于 17.(2) 如果输出a+1和&a[1][0], 它们的值相等, 但它们有着不同的含义, a+1 等价于 &a[1], 表示第1行的首地址, 是一个二级指针; &a[1][0] 表示第1行第0列的地址, 是一个一级指针. 由于a[1][0] 是第1行的首元素, 因此它的地址刚好就是第1行的首地址, 从而两者输出的值相等.6.10 有一个整型二维数组, 大小是n m ⨯, 要求找出最大值所在的行和列以及该最大值, 请编写一个程序max, 要求如下:(1) 以数组名和数组大小为该函数的形参;(2) 数组元素的值在main 函数中输入, 结果在max 函数中输出.[解答]#include <stdio.h>#define M 3#define N 4void max(int a[], int m, int n){int i, j, row=0, col=0, max=*a;for(i=0; i<m; i++)for(j=0; j<n; j++, a++)if(*a>max){max=*a;row=i;col=j;}printf("最大值是%d, 在第%d, 第%d 列.\n", max, row, col);}void main(){int i, j, a[M][N];printf("请输入%d * %d 个整数:\n", M, N);for(i=0; i<M; i++)for(j=0; j<N; j++)scanf("%d", &a[i][j]);max(*a, M, N);}6.11 有n个学生, 每个学生参加m门课程的考试, 要求编写一函数, 能检查n个学生有无不及格的课程, 如果某个学生有一门或一门以上课程不及格, 就输出该学生的学号(学号从0算起, 即0, 1, 2, …) 及其全部课程成绩.[解答]#include <stdio.h>#define M 5 /*学生数*/#define N 3 /*课程数*/void proc(float s[][N]){int i, j, k;for(i=0; i<M; i++){for(j=0; j<N; j++)if(s[i][j]<60.0) break;if(j<N){printf("第%d 个学生有不及格的课程, 其各门课的成绩为:\n", i);for(k=0; k<N; k++)printf("%7.2f", s[i][k]);printf("\n");}}}void main(){float score[M][N];int i, j;for(i=0;i<M;i++){printf("请输入第%d 个学生的成绩: ", i);for(j=0;j<N;j++)scanf("%f", &score[i][j]);}proc(score);}6.12 输入3行字符(每行60个字符以内), 要求统计出其中共有多少个大写字母, 小写字母, 空格及标点符号.[解答]#include <stdio.h>#include <string.h>#define M 3#define N 60void main(){int i, j, upper=0, lower=0, blank=0, punc=0; /* upper, lower, blank, punc 分别记录大写字母, 小写字母, 空格及标点符号的个数*/char str[M][N];printf("请输入%d 行字符, 每行不超过%d 个字符:\n", M, N);for(i=0; i<M; i++)gets(str[i]);for(i=0; i<M; i++)for(j=0; j<N && str[i][j]!='\0'; j++)if(str[i][j]>='A' && str[i][j]<='Z')upper++;else if(str[i][j]>='a' && str[i][j]<='z')lower++;else if(str[i][j]==' ')blank++;else if(str[i][j]>' ' && str[i][j]<'0' || str[i][j]>'9' && str[i][j]<127)punc++;printf("大写字母, 小写字母, 空格及标点符号的个数分别是%d, %d, %d, %d.\n", upper, lower, blank, punc);}6.13 指出下列程序的错误, 并分析出错的原因.#include <stdio.h>void Print(char *[], int len);int main(void){char *pArray[]={"Fred", "Barrey", "Wilma", "Betty"};int num=sizeof(pArray)/sizeof(char);printf("Total string numbers = %d\n", num);Print(pArray, num);return 0;}void Print(char *arr[], int len){int i;for(i=0; i<len; i++)printf("%s\n", arr[i]);}[解答]程序第6行试图计算指针数组pArray所含元素的个数, 但这是错误的, 一个数组所含元素个数应该等于数组大小除以数组元素类型的大小, 这个数组的元素是字符指针类型, 而不是字符类型, 正确的语句是:int num=sizeof(pArray)/sizeof(char *);6.14 建立一个动态二维数组, 用来存储1~10的1~4次幂.[解答]#include <stdio.h>#include <stdlib.h>#define M 10#define N 4void main(){int i, j, (*p)[N], pow;p=(int (*)[N])malloc(M*N);if(!p){printf("内存分配出错.\n");exit(1);}for(i=0; i<M; i++){pow=1;for(j=0; j<N; j++)p[i][j]=pow*=(i+1);}for(i=0; i<M; i++){for(j=0; j<N; j++)printf("%6d", p[i][j]);printf("\n");}// free(p);}6.15 略.6.16 题目略.[解答] (1) A (2) C.。

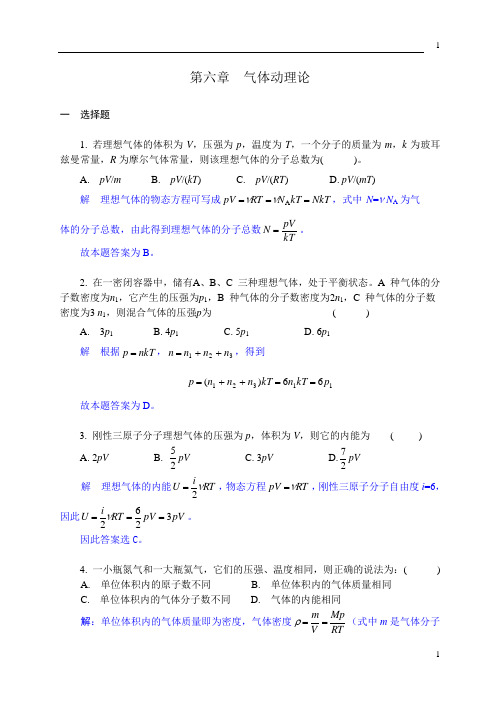

06气体动理论习题解答

第六章 气体动理论一 选择题1. 若理想气体的体积为V ,压强为p ,温度为T ,一个分子的质量为m ,k 为玻耳兹曼常量,R 为摩尔气体常量,则该理想气体的分子总数为( )。

A. pV /mB. pV /(kT )C. pV /(RT )D. pV /(mT )解 理想气体的物态方程可写成NkT kT N RT pV ===A νν,式中N =ν N A 为气体的分子总数,由此得到理想气体的分子总数kTpVN =。

故本题答案为B 。

2. 在一密闭容器中,储有A 、B 、C 三种理想气体,处于平衡状态。

A 种气体的分子数密度为n 1,它产生的压强为p 1,B 种气体的分子数密度为2n 1,C 种气体的分子数密度为3 n 1,则混合气体的压强p 为 ( )A. 3p 1B. 4p 1C. 5p 1D. 6p 1 解 根据nkT p =,321n n n n ++=,得到1132166)(p kT n kT n n n p ==++=故本题答案为D 。

3. 刚性三原子分子理想气体的压强为p ,体积为V ,则它的内能为 ( ) A. 2pV B.25pV C. 3pV D.27pV解 理想气体的内能RT iU ν2=,物态方程RT pV ν=,刚性三原子分子自由度i =6,因此pV pV RT i U 3262===ν。

因此答案选C 。

4. 一小瓶氮气和一大瓶氦气,它们的压强、温度相同,则正确的说法为:( ) A. 单位体积内的原子数不同 B. 单位体积内的气体质量相同 C. 单位体积内的气体分子数不同 D. 气体的内能相同解:单位体积内的气体质量即为密度,气体密度RTMpV m ==ρ(式中m 是气体分子质量,M 是气体的摩尔质量),故两种气体的密度不等。

单位体积内的气体分子数即为分子数密度kTpn =,故两种气体的分子数密度相等。

氮气是双原子分子,氦气是单原子分子,故两种气体的单位体积内的原子数不同。

6章 习题解答

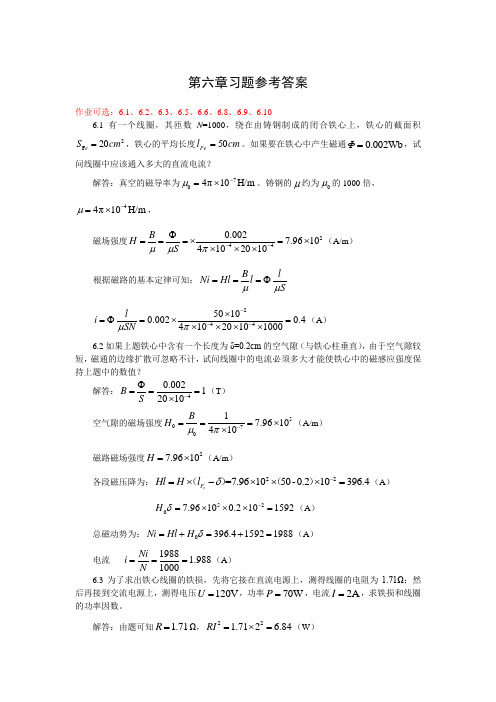

第六章习题参考答案作业可选:6.1、6.2、6.3、6.5、6.6、6.8、6.9、6.106.1有一个线圈,其匝数N =1000,绕在由铸钢制成的闭合铁心上,铁心的截面积2F 20cm S e =,铁心的平均长度cm l Fe 50=。

如果要在铁心中产生磁通Wb 002.0=Φ,试问线圈中应该通入多大的直流电流?解答:真空的磁导率为H/m 10π470-⨯=μ。

铸钢的μ约为0μ的1000倍,44π10H/m μ-=⨯,磁场强度2440.0027.96104102010BH S μμπ--Φ===⨯=⨯⨯⨯⨯(A/m ) 根据磁路的基本定律可知:B lNi Hl l Sμμ===Φ24450100.0020.441020101000l i SN μπ---⨯=Φ=⨯=⨯⨯⨯⨯(A ) 6.2如果上题铁心中含有一个长度为δ=0.2cm 的空气隙(与铁心柱垂直),由于空气隙较短,磁通的边缘扩散可忽略不计,试问线圈中的电流必须多大才能使铁心中的磁感应强度保持上题中的数值?解答:40.00212010B S -Φ===⨯(T ) 空气隙的磁场强度50717.9610410BH μπ-===⨯⨯(A/m ) 磁路磁场强度27.9610H =⨯(A/m )各段磁压降为:22=7.961050-0.210396.4e F Hl H l δ-=⨯-⨯⨯⨯=()()(A )5207.96100.2101592H δ-=⨯⨯⨯=(A ) 总磁动势为:0396.415921988Ni Hl H δ=+=+=(A ) 电流 19881.9881000Ni i N ===(A ) 6.3为了求出铁心线圈的铁损,先将它接在直流电源上,测得线圈的电阻为1.71Ω;然后再接到交流电源上,测得电压120V =U ,功率W 70=P ,电流A 2=I ,求铁损和线圈的功率因数。

解答:由题可知 1.71R =Ω,221.712 6.84RI =⨯=(W )2Fe cos P UI RI P φ==+∆⇒铁损2Fe 70 6.8463.16P P RI ∆=-=-=(W )功率因素70cos 0.2921202P UI ϕ===⨯ 6.4有一个交流铁心线圈,接在Hz 50=f 的正弦电源上,在铁心中得到磁通的最大值为Wb 1025.22m -⨯=Φ。

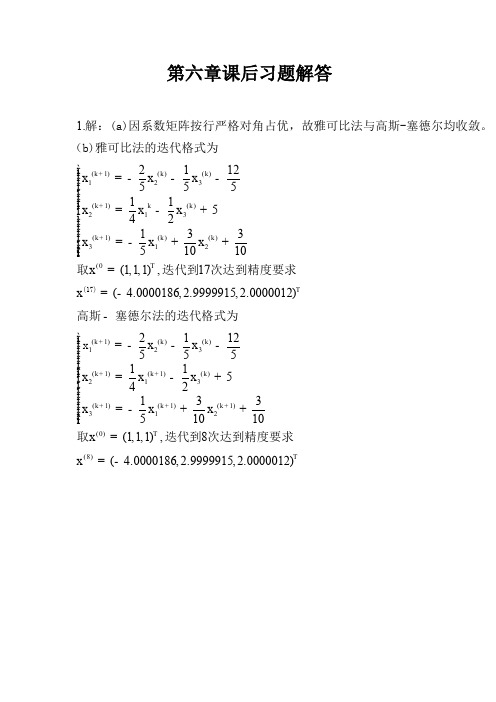

数值分析第六章课后习题答案

第六章课后习题解答(1)()()123(1)()213(1)()()312(01.21125551154213351010(1,1,1),17( 4.0000186,2.99999k k k k k k k k k Tx x x x x x x x x x x+++ìïï=---ïïïïïï=-+íïïïïï=-++ïïïî==-(17)解:(a )因系数矩阵按行严格对角占优,故雅可比法与高斯-塞德尔均收敛。

(b )雅可比法的迭代格式为取迭代到次达到精度要求(1)()()123(1)(1)()213(1)(1)(1)312(0)(8)15,2.0000012)21125551154213351010(1,1,1),8( 4.0000186,2.9999915,2.0000012)Tk k k k k k k k k TTx x x x x x x x x x++++++-ìïï=---ïïïïïï=-+íïïïïï=-++ïïïî==-高斯塞德尔法的迭代格式为x 取迭代到次达到精度要求1212:00.40.4.0.400.80.40.80||(0.8)(0.80.32)()1.09282031,00.40.4()00.160.6400.0320.672DL U I BD L U l l l l--骣--÷ç÷ç÷ç÷ç÷=+=--ç÷ç÷÷ç÷ç÷--÷ç桫-=-+-=>-æ--çççç=-=-ççççèlJJJS解(a )雅可比法的迭代矩阵B()BB故雅可比迭代法不收敛高斯塞德尔法迭代矩阵131()||||0.81022101220||022023002SJBDL U I BD L Ul l¥--ö÷÷÷÷÷÷÷÷÷÷ç÷ø?<骣-÷ç÷ç÷ç÷ç÷=+=--ç÷ç÷÷ç÷ç÷--ç÷桫-=骣-÷ç÷ç÷ç÷ç÷=-=-ç÷ç÷÷ç÷ç÷ç桫llSJJ SB故高斯-塞德尔迭代法收敛。

第六章 习题解答.

(1)[x2]浮=1,0101;1.110 110 000 0 (2)[x2]浮=1,1011;1.001 010 000 0 (3)[x2]浮=0,1011;1.001 010 000 0 (1)[x3]浮=0,0011;0.111 011 000 0 (2)[x3]浮=0,0011;0.111 011 000 0 (3)[x3]浮=1,0011;0.111 011 000 0 (1)[x4]浮=0,0111;1.101 011 010 0 (2)[x4]浮=0,0111;1.010 100 110 0 (3)[x4]浮=1,0111;1.010 100 110 0 注:以上浮点数也可采用如下格式:

原 码 反 码 1.001 1010 1.110 0101 0.001 1101 0.001 1101 0,110 0100 0,110 0100 1,101 0111 1,010 1000

补 码 1.110 0110 0.001 1101 0,110 0100 1,010 1001

5. 已知[x]补,求[x]原和x。 [x1]补=1. 1100; [x2]补=1. 1001; [x3]补=0. 1110; [x4]补=1. 0000; [x5]补=1,0101; [x6]补=1,1100; [x7]补=0,0111; [x8]补=1, 0000; 解:[x]补与[x]原、x的对应关系如下:

第六章 习题解答

4. 设机器数字长为8位(含1位符号位在 内),写出对应下列各真值的原码、补码和 反码。 -13/64,29/128,100,-87 解:真值与不同机器码对应关系如下:

真

十进制

值

二进制

-13/64 29/128 100 -87

-0.00 1101 0.001 1101 110 0100 -101 0111

结构化学习题解答6

[6.23] 根据磁性测定结果知, NiCl42-为顺磁性而 Ni ( CN) 42- 为 反磁性,试推测它们的几何构型。 [解]:Ni2+为(3d)8组态,半径小,其四配位化合物既可呈四面体 构型,也可呈平面正方形构型,决定因素是配体间排斥作用的 大小。若 Ni2+的四配位化合物呈四面体构型,则d电子的排布方 式为:

第六章 配合物的结构和性质

[6.3] 判断下列配位离子是高自旋型还是低自旋型,画出d电 子排布方式,说明配位离子的磁性,计算LFSE(用△0表示)。 (a) Mn(H2O)62+ (b) Fe(CN)64- (c) FeF63[解]:兹将各项结果列于下表: 配位离子 Mn(H2O)62+ Fe(CN)64FeF63-

t2 e

配合物因有未成对的 d电子而显顺磁性。若呈平面正方形, 则d电子的排布方式为:

dx2 -y 2 dxy dz2 dxz,dyz

配合物因无不成对电子而显反磁性。反之,若 Ni2+ 的四配位 化合物显顺磁性,则它呈四面体构型;若显反磁性,则它呈平面 正方形。此推论可推广到其他具有 d8组态过渡金属离子的四面体 配位化合物。 NiCl42-为顺磁性离子,因而呈四面体构型。Ni(CN)42-为反 磁性离子,因而呈平面正方形。 [6.17] 某学生测定了三种配合物的d—d跃迁光谱,但是忘记了贴 标签,请帮助他将光谱波数与配合物对应起来。三种配合物是: CoF63- , Co(NH3)63+ , Co(CN)63- 。三种光谱波数是: 3400cm-1 , 1300cm-1,2300cm-1。 [解]: d—d跃迁光谱的波数与配位场分裂能的大小成正比,而分 裂能大小与配位体的强弱及中心离子的性质有关。因此,光谱波 数与配体强弱及中心离子的性质有关。而在这三种配合物中,中 心离子及其 d 电子构型都相同,因此光谱波数只决定于各自配体 的强弱。配体强者,光谱波数大;反之,光谱波数小。据此,可 将光谱波数与配合物对应起来: CoF63Co(NH3)63+ Co(CN)631300cm-1 2300cm-1 3400cm-1

第6章习题解答

第六章分子结构与晶体结构一、填空题1. 方向性;饱和性2. 小;大;变小3.S-S 轨道重叠;s-p x轨道重叠;p x-p x轨道重叠4. 键长;键角;键能;;几何构型;分子的极性;热稳定性5. 金属晶体;离子晶体;原子晶体;分子晶体二、选择题1. B;2. B;3. D;4. B;5.A;6.D;7. D;8. B;9. A三、是非题(正确的划“V”,错误的划“X”)1.V;2. X;3. X;4. X;5. X;6. V四、问答题1.答:(1)电子配对原理自旋相反的未成对电子的原子相互接近时,可形成稳定的共价键。

若原子中没有未成对电子,一般不能形成共价键。

共价键的数目取决于原子中未成对电子的数目。

例如H原子有1个未成对电子只能形成共价H-H或H-CI单键。

(2)最大重叠原理两原子成键时,若双方原子轨道重叠越多,成键能力越强,所形成的共价键越牢固,这称为轨道最大重叠原理。

(3)饱和性一个原子含有几个未成对电子,就可以和几个自旋量子数不同的电子配对成键,或者说,原子能形成共价键的数目是受原子中未成对电子数目限制的,这就是共价键的饱和性。

(4)方向性原子轨道中,除s轨道是球形对称,没有方向性外,p、d、f轨道都具有一定的空间伸展方向。

原子形成共价键时,在可能的范围内一定要采取沿着原子轨道最大重叠方向成键。

轨道重叠越多,两核间电子的几率密度越大,形成的共价键就越牢固。

2. 答:键的极性大小取决于成键两原子的电负性差。

电负性差越大,键的极性就越强。

如果两个成键原子的电负性差足够大,致使共用电子对完全转移到另一原子上而形成阴、阳离子,这样的极性键就是离子键。

从极性大小的角度,可将非极性共价键和离子键看成是极性共价键的两个极端,或者说极性共价键是非极性共价键和离子键之间的某种过渡状态。

3. 答:(1)离子键的形成当电负性相差较大的两种元素的原子相互接近时,电子从电负性小的原子转移到电负性大的原子,从而形成了阳离子和阴离子。

第6章 习题解答

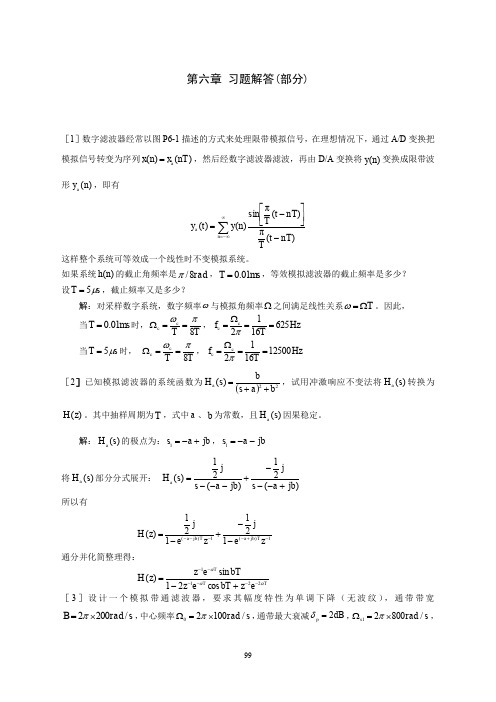

第六章 习题解答(部分)[1]数字滤波器经常以图P6-1描述的方式来处理限带模拟信号,在理想情况下,通过A/D 变换把模拟信号转变为序列)()(nT x n x a =,然后经数字滤波器滤波,再由D/A 变换将)(n y 变换成限带波形)(n y a ,即有∑∞-∞=-⎥⎦⎤⎢⎣⎡-=n a nT t nT t n y t y )(Tπ)(T πsin )()( 这样整个系统可等效成一个线性时不变模拟系统。

如果系统)(n h 的截止角频率是rad 8/π,ms T 01.0=,等效模拟滤波器的截止频率是多少? 设s T μ5=,截止频率又是多少?解:对采样数字系统,数字频率ω与模拟角频率Ω之间满足线性关系T Ω=ω。

因此,当ms T 01.0=时,T T cc 8πω==Ω,Hz T f c c 6251612==Ω=π当s T μ5=时, TT c c 8πω==Ω,Hz T f c c 125001612==Ω=π[2]已知模拟滤波器的系统函数为()22)(b a s bs H a ++=,试用冲激响应不变法将)(s H a 转换为)(z H 。

其中抽样周期为T ,式中a 、b 为常数,且)(s H a 因果稳定。

解:)(s H a 的极点为:jb a s +-=1,jb a s --=1将)(s H a 部分分式展开: )(21)(21)(jb a s j jb a s j s H a +---+---= 所以有1)(1)(121121)(-+------+-=z e j zej z H T jb a Tjb a通分并化简整理得:TT T ez bT e z bTe z z H ααα2211cos 21sin )(------+-= [3]设计一个模拟带通滤波器,要求其幅度特性为单调下降(无波纹),通带带宽s rad B /2002⨯=π,中心频率s rad /10020⨯=Ωπ,通带最大衰减dB p 2=δ,s rad s /80021⨯=Ωπ,s rad s /124022⨯=Ωπ,阻带最小衰减dB s 15=δ。

物理习题解答第6-..

提示:各位同学认真复习,认真准备,以防挂科;如有疑问可到德信楼110。

第六章 真空中的静电场一、选择题:1(D ),2(C ), 3(A ), 4(C ), 5(D ), 6(B ), 7(C ), 8(D ),9( ), 10(D ), 11(D ), 12(B ),13(C ), 14(C ), 15(D ),16(C ),17(C ),18(C ), 19(C ) 填空题: 1、00023,2,23εσεσεσ--; 2、40216RSQ επ∆,由圆心O 指向∆S ; 3、,0,qqεε-; 4、 5、)11(400ab r r qq -πε; 6、Ed ; 7、20092,r R Q Qπεε 0; 8、3028R qdεπ,由圆心O 指向缺口;9、r r R3020εσ; 10、020ελ, 11、43ln 40πελ, 0;12、R R dS Q R QdS 024024)41(,16πεπεπ-; 13、⎰=⋅Ll d E 0,将任意电荷沿任意闭合路径移动一周,静电场力做功代数和恒为零,保守; 14、RQq RQ 004,4πεπε-;15、πAR 4; 16、πR 2E ; 17、三、计算题1.如图所示,一长为10cm 的均匀带正电细杆,其带电量为1.5×10-8C.试求在杆的延长线上距杆的端点5cm 处的P 点的电场强度2280/10941C m N ⋅⨯=πε)解:设P 点在杆的右边,选取杆的左端为坐标原点O ,X 轴沿杆的方向,如图. 并设杆的长度为L . P 点离杆的端点距离为d . 在x 处取一电荷元dq =(q/L )dx ,它在P 点产生场强:2020)(4)(4x d L L qdxx d L dq dE -+=-+=πεπεXdxP 点处的总场强为:)(4)(04020d L L q x d L dx L L qE +=-+=⎰πεπε 代入题目所给数据,得C N E /108.14⨯= E的方向沿X 轴正向.2. 一个细玻璃棒被弯成半径为R 的半圆形,沿其上半部分均匀分布有电量+Q ,沿其下半部分均匀分布有电量-Q ,如图所示.试求圆心O 处的电场强度。

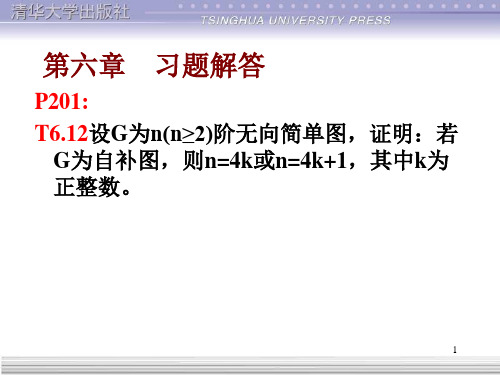

6习题解答

(2)由于G为自补图,所以 G G

m1=m2,记m1=m2=m,有 m1+m2=2m=n(n-1)/2 m=n(n-1)/4

2

第六章 习题解答

P201: T6.12设G为n(n≥2)阶无向简单图,证明:若G为自

补图,则n=4k或n=4k+1,其中k为正整数。

(6) 长度等于4的回路共有多少条?

(7) 长度小于等于4的通路共有多少条?其中回路共有多少条?

(8) 写出D的可达矩阵, 并问D是强连通的吗?

解

1200 0010 A= 1 0 0 1

v1

v4

0010

v2

v3

6

1200 0010 A= 1 0 0 1 0010

1220

3222

1001

1210

A2= 1 2 1 0 A3= 2 2 2 1 A4=

9

第六章 习题解答 甲 乙 丙

T6.31解:

a

b

c

甲 乙丙

a

b

c

甲 乙丙

a

b

c

甲 乙丙

a

b

c

10

证: m=n(n-1)/4

(3)由于n和n-1是连续的自然数,一奇一偶,又因m 是整数,必有以下两种情况:

情况1:n=4k 情况2:n-1=4k n=4k+1

3

第六章 习题解答

P201: T6.19设无向图G如图6.51所示, (1)G中最短的圈长为几?最长的圈长为几? (2)G中最短的简单回路长度为几?最长的简单回路长

1001

1210

(1) v1到v4, 长度为1,2,3,4的通路各有0,0,2,2条

概率论第六章习题解答(全)

1 P{0.3 2 ( X Y ) 2 0.3 2} 1 (0.3 2) (0.3 2) 2 2 (0.3 2) 2 2 (0.42) 2(1 0.6628) 2 0.3372 0.6744

4、 (1) 设 X 1 , X 2 , , X 6 样本是来自总体 N (0,1) , Y ( X1 X 2 X 3 ) ( X 4 X 5 X 6 ) ,

(

1 10 i1 2 2 ) e 2

( xi )2

10

又

X

1 10 1 10 1 10 X i , E( X ) E( X i ) E( X i ) 10 i 1 10 i 1 10 i 1 1 10 1 D( X ) D( X i ) 2 10 i 1 10

i 1 5 i 1 5 5

1 (1 P{

i 1 5

X i 12 10 12 }) 2 2

5

1 (1 (1)) 1 (1)

i 1 i 1

1 (0.8413)5 1 04215 0.5285

3、求总体 N (20,3) 的容量分别为 10,15 的两个独立样本均值差的绝对值不超过 0.3 的概率。 解 则 设容量为 10 的样本均值为 X ,样本容量为 15 的样本均值为 Y ,

且

X1 X 2 2 2 2 , X 3 X 4 X 5 相互独立,于是由 t 分布的定义知 2 X1 X 2 X1 X 2 3 2 t (3) 2 2 2 2 X3 X4 X5 2 ( X X 2 X 2 ) 12 3 4 5 3

因此所求常数为

C

理论力学习题解答(第六章)

6-1在图示四连杆机构中,已知:匀角速度O ω,OA =B O 1=r 。

试求在°=45ϕ且AB ⊥B O 1的图示瞬时,连杆AB 的角速度AB ω及B 点的速度。

解:连杆AB 作平面运动,由基点法得BA A B v v v +=由速度合成的矢量关系,知φcos v A BA =v杆AB 的角速度)(/AB /O BA AB 2122+==ωωv (逆时针)B 点的速度2245/r cos v O A B ω=°=v (方向沿AB )6-2. 在图示四连杆机构中,已知:3.021===L B O OA m ,匀角速度2=ωrad/s 。

在图示瞬时,11==L OB m ,且杆OA 铅直、B O 1水平。

试求该瞬时杆B O 1的角速度和角加速度。

解:一.求1ω60230..OA v A =×=⋅=ω m/s取A 为基点,则有BA A B v v v += 得 23.0/6.0ctg v v A B ===ϕ m/sm09.2)3.01()3.0/6.0(sin /v v 2/122A BA =+×==ϕ杆B O 1的角速度67630211../BO /v B ===ω rad/s 顺时针 二.求1ε取点A 为基点,则有n BA A a a a a a ++=+ττBA nB B将上式向X 轴投影21222857s /m .B O /ctg v )sin AB /v (OA ctg a )sin /a (a a a sin a cos a sin a BBA n B n BA A B nBA A n B B +=⋅+⋅+⋅−=++−=−=+−ϕϕωϕϕϕϕϕττ杆B O 1的角加速度7.1923.0/8.57/11===B O a B τεrad/s 2逆时针6-3.图示机构中,已知:OA =0.1m , DE =0.1m ,m 31.0=EF ,D 距OB 线为h=0.1m ;rad 4=OA ω。

概率论课后习题第6章答案

第六章 数理统计的基本概念1.设样本均值为X ,则由题意,有6,4.1(~2n N X ,或)1,0(~/64.1N nX −,于是由1)3(2/64.34.5/64.3/64.34.1}4.54.1{95.0−Φ=⎭⎬⎫⎩⎨⎧−<−<−=<<≤nn n X nP X P⇒ 975.03(≥Φn ⇒ 96.13≥n⇒5744.34≥n 故样本容量至少应取35. 2.由题意可知)1,0(~/2.0N na X n −,又122/2.01.0/2.0}1.0|{|95.0−⎟⎟⎠⎞⎜⎜⎝⎛Φ=⎭⎫⎩⎨⎧<−=<−≤n n n a X P a X P n n 故有 975.0)2(≥Φn ⇒ 96.12≥n⇒ 3664.15≥n 因此至少应等于16.n 3. 由正态分布的性质及样本的独立性知,212X X −和4343X X −均服从正态分布,由于,0)2(21=−X X E 20)(4)()2(2121=+=−X D X D X X D以及,0)43(43=−X X E 100)(16)(9)43(4343=+=−X D X D X X D所以,有)20,0(~221N X X −⇒)1,0(~20221N X X −)100,0(~4343N X X − ⇒)1,0(~104343N X X −于是由分布的定义知,当2χ,201=a 1001=b 时,有 ()())2(~10432024322243221243221χ⎟⎠⎞⎜⎝⎛−+⎟⎟⎠⎞⎜⎜⎝⎛−=−+−=X X X X X X b X X a X 4. 由正态分布的性质及样本的独立性知, ⇒ )9,0(~2921N X X X +++")1,0(~)(91921N X X X +++" 又)1,0(~3N Y i, 9,,2,1"=i 所以 )9(~)(913332292221292221χY Y Y Y Y Y +++=⎟⎠⎞⎜⎝⎛++⎟⎠⎞⎜⎝⎛+⎟⎠⎞⎜⎝⎛""由于两个总体是X 和Y 相互独立的,所以其相应的样本也是相互独立的,故)9(9121X X X +++"与)(21Y 912922Y Y +++"也相互独立,于是由t 分布的定义知,)9(~9/)(91)(91292191292191t Y Y X X YY X X U +++=++++=""""5.由题意知,)1,0(~2N X i,,故有 15,,2,1"=i )10(~22)(4122102121021χ⎟⎠⎞⎜⎝⎛++⎟⎠⎞⎜⎝⎛=+=X X X X U "" )5(~22)(412215211215211χ⎟⎠⎞⎜⎝⎛++⎟⎠⎞⎜⎝⎛=+=X X X X V ""利用样本的独立性以及F 分布的定义,有)5,10(~5/10/)(221521121021F V U X X X X Y =++++="" 6.解法1 考虑n n n n X X X X X X 22211,,,+++++",将其视为取自正态总体的简单随机样本,则其样本均值为 )2,2(2σμN X X n X X n ni i n i i n i 21)(1211==+∑∑==+样本方差为 Y n 11−由于2211σ=⎟⎠⎞⎜⎝⎛−Y n E ,所以 22)1(2)2)(1()(σσ−=−=n n Y E 解法2 记,11∑==′n i i X n X ,11∑=+=′ni i n X n X 显然有X X X ′′+′=2,因此[]⎭⎬⎫⎩⎨⎧′′−+′−=⎥⎦⎤⎢⎣⎡−+=∑∑=+=+n i i n i n i i n i X X X X E X X X E Y E 1212)()()2()( []⎭⎬⎫⎩⎨⎧′′−+′′−′−+′−=∑=++n i i n i n i i X X X X X X X X E 122)())((2)(222)1(2)1(0)1(σσσ−=−++−=n n n 7.记(未知),易见2)(σ=X D )()(21Y E Y E =, ,6/)(21σ=Y D 3/)(22σ=Y D 由于相互独立,故有21,Y Y ,0)(21=−Y Y E 236)(22221σσσ=+=−Y Y D从而 )1,0(~2/21N Y Y U σ−=,又 )2(~22222χσχS =由于与相互独立,与独立,由定理 6.3.2,与独立,所以1Y 2Y 1Y 2S 2Y 2S 21Y Y −与独立,于是由t 分布的定义,知 2S )2(~2/)(2221t USY Y Z χ=−=8.由)1(~)1(222−−n S n χσ,其中由题意知,25=n , ,于是1002=σ}12)125({)1(50)1(}50{22222>−=⎭⎬⎫⎩⎨⎧−>−=>χσσP n S n P S P975.0}12)24({2≥>=χP 上式中的不等式是查表得到的,所以所求的概率至少为0.9759. 本题要用到这样一个结论,即Γ分布),(βαΓ关于第一个参数具有可加性,即若),(~1βαΓU ,),(~2βαΓV ,且U 与V 相互独立,则),(~21βαα+Γ+V U ,其中),(βαΓ的概率密度为: ⎪⎩⎪⎨⎧=)(x f αβ>其它0,x βΓ−)(1/1e x α−0x α可利用卷积公式证明.回到本题,当λβα11=,=,分布就是参数为Γλ的指数分布,所以样本的独立性及Γ分布的可加性,有 )1,(~21λn X +X X n Γ++"即的概率密度为 ∑=ni i X 1⎪⎩⎪⎨⎧>−=−−其它00,)!1()(1x e x n x g x n nλλ 因此∑==ni i X n X 11的概率密度为 ⎪⎩⎪⎨⎧≤>−==−−0,00,)!1()()()(1y y e y n n ny ng y h ny n n λλ 10. (1) 根据正态分布的性质,与21X X +21X X −服从二维正态分布,所以要证明它们相互独立,只需它们不相关,由于0)()()])([(22212121=−=−+X E X E X X X X E 0)()(2121=−+X X E X X E 所以 0),(2121=−+X X X X Cov 即与相互独立21X X +21X X −(2) 由于0=μ,所以)2,0(~221σN X X +⇒)1,0(~221N X X σ+ ⇒)1(~212221χσ⎟⎠⎞⎜⎝⎛+X X⇒)2,0(~221σN X X −)1,0(~221N X X σ− ⇒)1(~212221χσ⎟⎠⎞⎜⎝⎛−X X由上面证明的独立性,再由F 分布的定义知)1,1(~2/2/)()(21221221221F X X X X X X X X F ⎟⎠⎞⎜⎝⎛−⎟⎠⎞⎜⎝⎛+=−+=σσ 所以 25.0}83.5{}4{4)()(221221=<<<=⎭⎬⎫⎩⎨⎧<−+F P F P X X X X P。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

9. 试针对8 位数据总线和16 位地址总线的计算机系统设计一监视2 台设备状态的接口电 路和监控程序:若发现某一设备状态异常(由低电平变为高电平),则发出报警信号(指示灯亮), 一旦状态恢复正常,则将其报警信号撤除。 解答:电路原理图如下图所示,其中T0,T1分别表示监控设备0和设备1的状态线,led灯D0, D1分别表示监控设备0和设备1的报警状态。假设CS译码地址为0x380.

15 14 13 12 11 10 9 7

74LS138

6. 通过查阅存储芯片AT29C256 的数据手册,说明该存储芯片的容量,地址线、数据线宽度 以及读写操作时序。 解答:

地址线:15位 数据线:8位 容量:32KB 读时序图:

写时序图:

7. 试为一个32 位的微处理器设计一个存储容量为128K*32b 的SRAM 存储器,要求采用 SRAM 62256 存储芯片,并且该存储器需能支持字节、半字以及字类型的数据访问。 解答:128K*32b的SRAM存储器共需32位数据线(D0~D31),19根地址线(A0~A18),由于要 支持字节、半字以及字类型的数据访问,因此提供字节使能信号BE0,BE1,BE2,BE3,从而

15 14 13 12 11 10 9 7

74LS138

74LS138

U3

1 2 3

A B C

6 4 5

E1 E2 E3

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

15 14 13 12 11 10 9 7

74LS138

U4

1 2 3

A B C

6 4 5

E1 E2 E3

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

A0~A1不再提供。SRAM 62256为32K*8位的SRAM芯片,因此共需=4*4=16片芯片,其中4片构 成一组进行字长扩展,4组进行字数扩展。下图画出了采用139译码之后CS0连接的其中一组 的电路连接图,这里采用WE信号实现不同字节访问的控制。另外三组除了CE信号分别连接 CS1,CS2,CS3,其余信号的连接完全相同。

D0 D1 D2 D3 D4 D5 D6 D7

11 D0 12 13 15 16 17 18 19 D7

U?:A

CS0

A17 A18

CS

2 3

A B

1E

Y0 Y1 Y2 Y3

4 5 6 7

CS1 CS2 CS3

20 27 22

CE WE OE

62256

74LS139

MEMR

U5

U5

MEMW

BE0

BE1

OE 1

D4 12 D5 14

D616 D718

Y3 Y2 Y1 Y0

A3 A2 A1 A0

8 6 4 2

74LS244

U8

RD

DSW?

16 OFF ON1Biblioteka 15214

3

13

4

12

5

11

6

10

7

9

8

DIPSW_8

D[0..7]

U7:A

2 3

74S02

OR

D0 D1 D2 D3 D4 D5 D6 D7

1

解答:16位地址总线,表示提供了A0~A15地址信号,端口地址范围为0x2A0H~0x2BF,由此 可知A15~A5固定为:0000 0010 101;A4~A0可以任意变化,因此需要将A15~A5参与译码,形 成138的使能信号,而A4~A0形成各个具体端口地址的选择信号,共32个不同的端口地址, 每片138可以提供8个不同的端口地址,由此可知需要4片138,而这4片138需要4个不同的使 能信号,因此又需要一片138,这片138共6个输入端,2个输入端为地址选择,剩余的4个输 入端可以连接高位地址信号。电路原理图如下图所示。

U5

U5

OR

OR

A2 10 9 8 7 6 5 4 3

25 24 21 23

2 26 A16 1

U4

A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14

20 27 22

CE WE OE

62256

D0 D1 D2 D3 D4 D5 D6 D7

11 D24 12 13 15 16 17 18 19 D31

第六章 习题解答

1. IO 接口的一般结构包括哪些部分?它们各具有什么功能? 解答:接口电路主要由控制命令逻辑电路、状态设置和存储电路、数据存储和缓冲电路3部 分组成

控制命令逻辑电路一般由命令寄存器和控制执行逻辑组成,这一部分是接口电路的“中 央处理器”,用来完成全部接口操作的控制。

状态设置和存储电路主要由一组状态寄存器构成,中央处理器和外设就是根据状态寄存 器的内容进行协调动作的。

数据存储和缓冲电路也是一组寄存器,用于暂存中央处理器和外设之间传送的数据,以 完成速度匹配工作。

2. IO 接口的数据通信方式分为几类?各有什么优缺点?各自主要的应用场景有哪些? 解答: 只有两种:串行传送和并行传送。 并行数据的每一位都对应独立的传输线路,所以数据传送速度快,但线路多,一般只用于较 短距离的数据传送。 串行数据传送主要用于远程终端或经过公共电话网的计算机之间的通信。远距离数据传送采 用串行方式比较经济。但串行数据传送比并行数据传送控制复杂,要求收发双方遵从统一的 通讯协议。

8. 采用某8 位独立开关输入十六进制字符(0~9,a~f)的ASCII 码,并将该ASCII 码表示的 十六进制字符通过一位七段显示器显示出来。试针对8 位数据总线和16 位地址总线的计算 机系统设计接口电路和控制程序。要求输入输出端口地址均为0x380,控制程序Xilinx C 语 言。地址译码可任选一种方式。 解答:译码电路采用逻辑芯片完成译码的接口电路如下图所示

char asciicode,hexdigit; int temp;

while(1){ asciicode=Xil_In8(0x380); if((asciicode>0x2f)&(asciicode<0x3a)) hexdigit=asciicode-0x30;//数字0~9 else if ((asciicode>0x40)&(asciicode<0x47)) hexdigit=asciicode-0x37;//大写A~F else if ((asciicode>0x60)&(asciicode<0x67)) hexdigit=asciicode-0x57;//小写a~f else hexdigit=17;//显示横线 Xil_Out8(0x380,segcode[hexdigit]);//查表并输出 for(temp=0;temp<0x1000;temp++);//延时 }

4. IO 接口寻址方式分为几类?各有什么优缺点? 解答: 有两种不同的I/O接口寻址方式:一种是标准的I/O寻址,另一种是存储器映象I/O寻址 (memory mapped I/O)。 存储器映象 I/O 寻址方式的优点是:

(1)CPU 对外设的操作可使用全部的存储器操作指令,故指令多,使用方便,如可对 外设中的数据(存于外设的寄存器中)进行算术和逻辑运算,进行循环或移位等;

3. IO 接口的通信控制方式有哪些?分别具有什么特点? 解答: 查询、中断和DMA 3种方式控制接口的传送操作。 查询方式是中央处理器在数据传送之前通过接口的状态设置存储电路询问外设,待外设允许 传送数据后才传送数据的操作方式。在查询方式下,中央处理器需要花费较多的时间去不断 地“询问”外设,外设的接口电路处于被动状态。 中断方式是在外设要与中央处理器传送数据时,外设向中央处理器发出请求,中央处理器响 应后再传送数据的操作方式。在中断方式下,中央处理器不必查询外设,而由接口在外设的 输出数据发送完毕或接收数据准备好时通知中央处理器,中央处理器再发送或接收数据。 DMA方式是数据不经过中央处理器在存储器和外设之间直接传送的操作方式。DMA方式是 这3种方式中效率最高的一种传送方式,DMA方式控制接口也最复杂,需要专用的DMA控制 器。

U5:B

T0 T1

11 13 15 17

A0 A1 A2 A3

Y0 Y1 Y2 Y3

9 7 5 3

D0 D1

19 OE

U8

74LS244

RD

CS WR

OR D0

U7:A

2

3

74S02

D7 1

U4

3 4 7 8 13 14 17 18

U4

3 4 7 8 13 14 17 18

D0 D1 D2 D3 D4 D5 D6 D7

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

1 11

OE LE

74LS373

2a

5b

6c

9

d

12 e

15

f

16 g

19

控制程序: 原理:通过输入指令输入的为ASCII码,首先需转换为16进制数字,然后再根据16进制数字 查找7段数码管显示的字符表得到16进制数字对应的段码,再将段码通过输出指令进行输出。 采用Xilinx C语言实现,主要限定输入输出指令分别采用:Xil_In8(PORT),Xil_Out8(PORT, DATA). char segcode[17]= {0x3f,0x6,0x5b,0x4f,0x66,0x6d,0x7d,0x7,0x7f,0x6f,0x77, 0x7c,0x49,0x1e,0x79,0x71,0x40};//“0~9,a~f,-”的段码,共阴极型7段数码管的段码 void main(){

D[24..31] D[16..23]

D[8..15] D[0..7]

A[2..16]

A[2..16]