可控硅的工作原理和设计参考

可控硅温控器的工作原理

可控硅温控器的工作原理1.引言1.1 概述可控硅温控器是一种常用的电子温控设备,它在控制温度方面具有重要的应用。

通过对电流进行调节,可控硅温控器能够实现对电热器等加热装置的温度进行精确控制,从而满足不同实际应用场景中的温度要求。

可控硅温控器采用了可控硅技术,可控硅是一种半导体器件,具有较高的电压和电流承受能力,可以实现电流的可控调节。

其工作原理是通过控制可控硅通导角度,从而控制电路中的电流大小,从而达到对温度的精确调节。

可控硅温控器具有以下特点:一是控制精度高,能够精确控制温度在设定值范围内;二是响应速度快,能够快速调节并稳定温度;三是稳定性好,能够在长时间的运行中保持良好的温度控制效果;四是可靠性高,能够适应恶劣的工作环境并具备较长的使用寿命。

在实际应用中,可控硅温控器广泛应用于各种需要对温度进行精确控制的场景,例如工业生产中的熔炉、烘干设备、空调系统等。

同时,它也可以在家用电器中发挥作用,如家用烤箱、电热水器等。

可控硅温控器的工作原理和优势使得它成为了温控领域不可或缺的重要设备。

在本文中,我们将详细介绍可控硅温控器的工作原理和工作过程,探讨其在不同领域的应用前景。

通过深入了解可控硅温控器,我们可以更好地应用它来满足不同实际需求,并进一步推动其在技术和应用领域的发展。

文章结构主要包括引言、正文和结论三个部分。

引言部分旨在为读者提供对全文的概述,引起读者的兴趣,并明确文章的目的。

正文是全文的核心部分,展开论述主题,阐述可控硅温控器的定义、原理和工作过程。

结论部分对正文进行总结,并展望可控硅温控器的应用前景。

具体来说,文章结构可以按照以下方式进行组织:1. 引言1.1 概述在这一小节中,可以简要介绍可控硅温控器的背景和重要性,引出对其工作原理的探讨。

1.2 文章结构这一小节主要介绍文章的整体结构,包括引言、正文和结论三个部分的内容,并说明每个部分的主要内容。

1.3 目的在这一小节中,应明确本文的目的,即通过对可控硅温控器的工作原理的讲解,使读者了解其工作原理并展望其应用前景。

可控硅工作原理及作用

可控硅工作原理及作用

可控硅,也称为晶闸管,是一种半导体器件。

可控硅的主要作用是控制电流,是电子行业中最广泛应用的器件之一。

可控硅的工作原理可以简单概括为:通过控制晶体管的控制电流,从而控制晶体管的导电状态。

当控制电流为零时,晶体管无法导电。

当控制电流为正值时,晶体管处于导通状态,电流可以顺畅地通过晶体管。

当控制电流为负值时,晶体管处于截止状态,电流无法通过晶体管。

可控硅在电路中主要有以下两种作用:

1. 控制电压

可控硅通常用于控制电压达到特定的阈值。

通过控制可控硅的控制电流,可以使电路中的电压稳定在所需范围内。

2. 控制电流

可控硅还可以用于控制电流,特别是在高功率电子设备中,控制电流非常重要。

通过控制可控硅的导通和截止状态,调整电路中的电流值。

基于可控硅的电路有很多应用,包括变频器,逆变器和直流电源。

例如,

在变频器中,可控硅可以用来控制电机运行的速度,从而达到能耗节约的效果。

总之,可控硅是一种常见的半导体器件,可以用于控制电路中的电压和电流。

它在电子设备中的应用非常广泛,成为电子技术中不可或缺的一部分。

双向可控硅的工作原理及原理图

双向可控硅的工作原理及原理图双向可控硅(Bilateral Switch)是一种常用的电子器件,它具有双向导通的特性,可以在正向和反向的电压条件下控制电流的通断。

在本文中,我们将详细介绍双向可控硅的工作原理及其原理图。

一、工作原理双向可控硅由两个PN结组成,分别称为主PN结和辅助PN结。

主PN结的两个端子分别为主阳极(A1)和主阴极(A2),辅助PN结的两个端子分别为辅助阳极(G1)和辅助阴极(G2)。

当主PN结的A1端施加正向电压,A2端施加负向电压时,主PN结处于导通状态。

此时,主PN结的正向电流从A1流入,经过主PN结和辅助PN结,最终流入G2。

同时,主PN结的负向电流从G2流出,经过辅助PN结和主PN结,最终流出A2。

这样,双向可控硅就完成了正向导通。

当主PN结的A1端施加负向电压,A2端施加正向电压时,主PN结处于反向导通状态。

此时,主PN结的负向电流从A2流入,经过主PN结和辅助PN结,最终流入G1。

同时,主PN结的正向电流从G1流出,经过辅助PN结和主PN结,最终流出A1。

这样,双向可控硅就完成了反向导通。

二、原理图以下是一个双向可控硅的原理图示例:```A1 ───┐│┌┴┐│ │G1 ──┘ ││┌┴┐│ │G2 ──┘ ││A2 ───┘```在原理图中,A1和A2分别表示主阳极和主阴极的连接点,G1和G2分别表示辅助阳极和辅助阴极的连接点。

三、应用领域双向可控硅广泛应用于电力控制领域。

它可以用于交流电的调光、电机的控制、电源的开关等。

由于双向可控硅具有双向导通的特性,可以实现正向和反向电流的控制,因此在电力控制中具有重要的作用。

四、总结双向可控硅是一种常用的电子器件,具有双向导通的特性,可以在正向和反向的电压条件下控制电流的通断。

它由主PN结和辅助PN结组成,通过施加不同的电压,实现正向和反向导通。

双向可控硅在电力控制领域有广泛的应用,如交流电调光、电机控制等。

通过了解双向可控硅的工作原理和原理图,我们可以更好地理解和应用这一电子器件。

可控硅元件的工作原理及基本特性

可控硅元件的工作原理及基本特性可控硅元件(SCR)是一种半导体器件,也称为可控硅二极管。

它是一种四层结构的晶体管,由三个PN结与一个NPN结叠加而成。

SCR的工作原理基于控制极施加的电压,通过改变控制极电流来控制电流流过晶体管的能力。

SCR的工作原理如下:1.当控制极处于高电平时,SCR处于断开状态。

此时,控制极封闭了SCR的PNP结,使其无法导电。

2.当控制极处于低电平时,SCR处于导通状态。

此时,进一步控制极电压下降会使控制晶体二极管达到导通的临界电压。

一旦电压超过了临界电压,晶体管将开始导电并保持这种状态,直到通过SCR的电流下降到一个可接受的水平。

1.可控性:SCR可以通过控制极的电压来控制其导通状态。

调节控制极电压可以使SCR在开启和关闭电路的特定条件下工作。

2.可逆性:SCR可以在两个方向上导通电流。

它既可以由正向电压触发,也可以由反向电压触发。

这使得SCR在控制交流电源的整流和直流电源的变流中非常有用。

3.放大效应:一旦SCR导通电流,它将保持导通状态,直到电流下降到一个可接受的水平。

这是因为SCR具有正反馈特性,其中一部分导通电流将进一步加热晶体管并推动更多电流流过。

SCR在电力控制和电力电子应用中具有广泛的用途。

它可以用作整流器、开关、电压稳定器和电压调节器。

此外,SCR还用于电子点火系统、变频器、电动机控制和照明控制等领域。

总之,SCR是一种可通过控制极电压来控制其导通状态的半导体器件。

它具有可逆性、可控性和放大效应的特点,常用于电力控制和电力电子应用。

通过了解SCR的工作原理和基本特性,我们可以更好地理解和应用这种重要的半导体器件。

可控硅

一、单向可控硅工作原理可控硅导通条件:一是可控硅阳极与阴极间必须加正向电压,二是控制极也要加正向电压。

以上两个条件必须同时具备,可控硅才会处于导通状态。

另外,可控硅一旦导通后,即使降低控制极电压或去掉控制极电压,可控硅仍然导通。

可控硅关断条件:降低或去掉加在可控硅阳极至阴极之间的正向电压,使阳极电流小于最小维持电流以下。

二、单向可控硅的引脚区分对可控硅的引脚区分,有的可从外形封装加以判别,如外壳就为阳极,阴极引线比控制极引线长。

从外形无法判断的可控硅,可用万用表R×100或R×1K挡,测量可控硅任意两管脚间的正反向电阻,当万用表指示低阻值(几百欧至几千欧的范围)时,黑表笔所接的是控制极G,红表笔所接的是阴极C,余下的一只管脚为阳极A。

三、单向可控硅的性能检测可控硅质量好坏的判别可以从四个方面进行。

第一是三个PN结应完好;第二是当阴极与阳极间电压反向连接时能够阻断,不导通;第三是当控制极开路时,阳极与阴极间的电压正向连接时也不导通;第四是给控制极加上正向电流,给阴极与阳极加正向电压时,可控硅应当导通,把控制极电流去掉,仍处于导通状态。

用万用表的欧姆挡测量可控硅的极间电阻,就可对前三个方面的好坏进行判断。

具体方法是:用R×1k或R×10k挡测阴极与阳极之间的正反向电阻(控制极不接电压),此两个阻值均应很大。

电阻值越大,表明正反向漏电电流愈小。

如果测得的阻值很低,或近于无穷大,说明可控硅已经击穿短路或已经开路,此可控硅不能使用了。

用R×1k或R×10k挡测阳极与控制极之间的电阻,正反向测量阻值均应几百千欧以上,若电阻值很小表明可控硅击穿短路。

用R×1k或R×100挡,测控制极和阴极之间的PN结的正反向电阻在几千欧左右,如出现正向阻值接近于零值或为无穷大,表明控制极与阴极之间的PN结已经损坏。

反向阻值应很大,但不能为无穷大。

可控硅的工作原理是啥

可控硅的工作原理是啥

可控硅(SCR)的工作原理是基于半导体材料的电子特性。

SCR是一种四层结构的PNPN型半导体器件,在无触发信号时处于阻断状态,不导通电流。

当施加一个正向的触发脉冲信号时,SCR会进入导通状态,允许电流流过。

SCR的工作原理如下:

1. 阻断状态:当没有施加触发信号时,SCR处于阻断状态。

在这种情况下,P1区和N区之间的结正向偏置,导致P1区和P2区之间的PN结反向偏置,从而阻止电流通过。

2. 触发信号:当施加一个正向的触发脉冲信号时,SCR会进入导通状态。

触发脉冲信号使得SCR中的P1区和P2区中的电子被注入,形成电子云,破坏PN结反向偏置。

这导致P1区和P2区之间的PN结变为正向偏置,开始导通电流。

3. 导通状态:一旦SCR进入导通状态,它将保持导通,直到通过其的电流降低到一个较低的水平(称为保持电流),或者施加一个正向的阻断信号。

4. 阻断状态复位:为了将SCR从导通状态转换为阻断状态,需要施加一个正向的阻断信号。

这个信号使得SCR中的电子被移除,使得P1区和P2区之间的PN结再次反向偏置,导致阻断电流流动。

通过适当的控制触发信号的时机和持续时间,可控硅可以实现

电流的精确控制和开关操作。

这使得它在电力电子和控制领域中得到广泛应用,例如变频器、交流电调速器、电源电路等。

可控硅控制器工作原理

可控硅控制器工作原理可控硅控制器(Silicon Controlled Rectifier,SCR)是一种常用的电子元件,广泛应用于交流电源控制、直流电源变换、电机控制以及电炉等领域。

它的工作原理基于PN结的导电特性和控制电流的触发方式。

可控硅控制器由四层半导体材料构成,其中包括三个PN结。

当给可控硅控制器加上正向电压时,PN结处于正向偏置状态,可控硅控制器处于导通状态。

在这种情况下,可控硅控制器的电流可以沿着一个方向流动,从而实现电流的控制。

在可控硅控制器的工作中,触发电压起着关键的作用。

当外部施加一个触发电压时,可控硅控制器将从关断状态转变为导通状态。

触发电压可以通过不同的方式提供,比如直流电压、脉冲电压或者连续变化的电压。

触发电压的作用是改变PN结的导电状态,从而控制可控硅控制器的导通和关断。

可控硅控制器的导通状态维持时间取决于外部电路的控制。

一旦触发电压施加到可控硅控制器上,它将一直保持导通状态,直到外部电路中的电流降低到一个特定的水平,或者施加一个反向电压,使其进入关断状态。

因此,可控硅控制器的导通状态可以根据需要进行控制。

可控硅控制器的主要特点是能够承受高电压和高电流。

它具有较低的开关损耗和较高的开关速度,适用于高功率和高频率的应用。

此外,可控硅控制器还具有良好的温度稳定性和长寿命的特点。

在实际应用中,可控硅控制器经常与其他元件组合使用,以实现更复杂的控制功能。

例如,通过将多个可控硅控制器串联或并联连接,可以实现更高电压和电流的控制。

同时,可控硅控制器还可以与其他类型的开关元件,如晶体管和继电器,配合使用,以实现更灵活和精确的控制。

可控硅控制器是一种重要的电子元件,通过控制触发电压实现导通和关断状态的切换。

它具有高电压、高电流承载能力,适用于高功率和高频率的应用。

在实际应用中,可控硅控制器常常与其他元件结合使用,以实现更复杂的电路控制功能。

通过深入理解可控硅控制器的工作原理,可以更好地应用和设计电子电路。

可控硅的工作原理带图

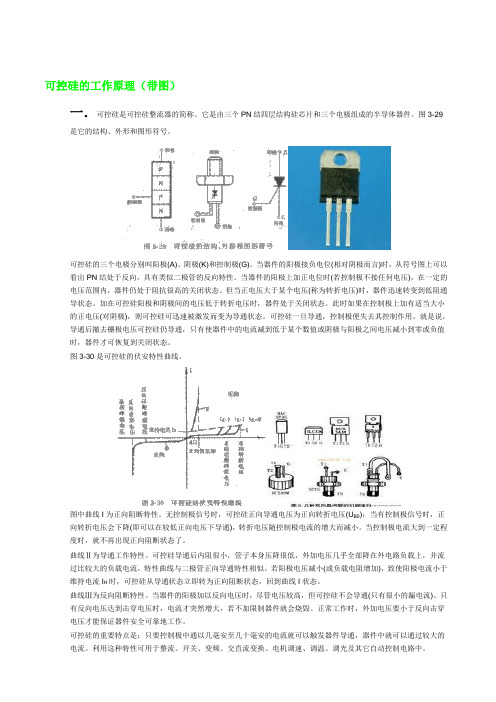

可控硅的工作原理(带图)一.可控硅是可控硅整流器的简称。

它是由三个PN结四层结构硅芯片和三个电极组成的半导体器件。

图3-29是它的结构、外形和图形符号。

可控硅的三个电极分别叫阳极(A)、阴极(K)和控制极(G)。

当器件的阳极接负电位(相对阴极而言)时,从符号图上可以看出PN结处于反向,具有类似二极管的反向特性。

当器件的阳极上加正电位时(若控制极不接任何电压),在一定的电压范围内,器件仍处于阻抗很高的关闭状态。

但当正电压大于某个电压(称为转折电压)时,器件迅速转变到低阻通导状态。

加在可控硅阳极和阴极间的电压低于转折电压时,器件处于关闭状态。

此时如果在控制极上加有适当大小的正电压(对阴极),则可控硅可迅速被激发而变为导通状态。

可控硅一旦导通,控制极便失去其控制作用。

就是说,导通后撤去栅极电压可控硅仍导通,只有使器件中的电流减到低于某个数值或阴极与阳极之间电压减小到零或负值时,器件才可恢复到关闭状态。

图3-30是可控硅的伏安特性曲线。

图中曲线I为正向阻断特性。

无控制极信号时,可控硅正向导通电压为正向转折电压(U B0);当有控制极信号时,正向转折电压会下降(即可以在较低正向电压下导通),转折电压随控制极电流的增大而减小。

当控制极电流大到一定程度时,就不再出现正向阻断状态了。

曲线Ⅱ为导通工作特性。

可控硅导通后内阻很小,管子本身压降很低,外加电压几乎全部降在外电路负载上,并流过比较大的负载电流,特性曲线与二极管正向导通特性相似。

若阳极电压减小(或负载电阻增加),致使阳极电流小于维持电流I H时,可控硅从导通状态立即转为正向阻断状态,回到曲线I状态。

曲线Ⅲ为反向阻断特性。

当器件的阳极加以反向电压时,尽管电压较高,但可控硅不会导通(只有很小的漏电流)。

只有反向电压达到击穿电压时,电流才突然增大,若不加限制器件就会烧毁。

正常工作时,外加电压要小于反向击穿电压才能保证器件安全可靠地工作。

可控硅的重要特点是:只要控制极中通以几毫安至几十毫安的电流就可以触发器件导通,器件中就可以通过较大的电流。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

可控硅的工作原理和设计参考

可控硅物理结构如下图所示,P-N-P-N,就象两只背靠背的三极管。

我们先来分析栅极不作电气联接的情况。

当可控硅阴极电位大于阳极电位,J1和J3结反偏,器件截止。

当可控硅阴极电位小于阳极电位,J1和J3正偏,但J2反偏,器件仍然截止。

如果J2的反偏电压达到引发雪崩击穿时,器件的导通特性就象单个正偏的PN结一样。

P

1 N ANODE

P

N

P

图一图二图三

进而分析图三:可控硅可等效为一个PNP晶体管和一个NPN晶体管集基相联而成,T1的集电极为T2提供基极电流,T1的基极电流由外电路通过栅极加T2的集电极电流提供。

如果T1、T2集基环路的增益超过单位增益(请参考晶体管增益和偏置电流的关系图)则环路电流持续保持增加,T1、T2进入饱和,可控硅被称为锁定,阳极到阴极的电流由外部偏置电路决定。

因此有几种情况能使可控硅进入锁定状态。

1、超过击穿电压使可控硅进入导通

当加在可控硅阳极和阴极之间的电压超过击穿电压V BO时,可控硅导通,V BO大于器件的额定电压。

在击穿电压时可控硅的阳极电流被称作为锁定电流IL。

击穿电压触发在大多数电路设计中是避免使用的。

它的特点是正向电压的下降沿很陡,下降时间是栅极触发的二十分之一;但它允许的di/dt却比栅极触发的低。

2、靠漏电流使可控硅进入导通

可控硅的结温升高,漏电流也增大。

如果结温允许升得足够高,使漏电流大到足以触发可控硅体内的集基耦合正反馈环路进入锁定而导通。

在结温超过Tjmax的某一温度,可控硅将不存在截止电压。

3.利用dv/dt使可控硅导通。

任何PN结都有电容,结面积越大,电容也越大。

当一锯齿电压加到可控硅的阳极和阴极之间,充电电流由下式表示:

ic=Cdv/dt

如果电流足够大,将引起可控硅导通。

4.利用栅极触发可控硅导通

这是一种常用的方法使可控硅导通,提供栅极电流触发可控硅体内的集基耦合正反馈环,使可控硅进入锁定状态。

如图四所示。

FORWARD CURRENT

ARD

当栅流大于零时,使可控硅进入导通的正向偏压小于VBO。

手册上提供要保证某一可控硅可靠触发导通的栅流和偏压条件。

同时,可控硅的触发特性和温度有关,所以要保证栅极触发脉冲的宽度和时间必须足够保证在所有条件下使可控硅进入锁定。

设计时注意几点:

1、电路设计上要保证dIF/dt不能超过规定指标,否则可控硅将被损坏。

2、在栅极触发电流设计上,比较好的方法是提供高速大电流过驱动脉冲(dIG/dt)(不超过

额定功率),使可控硅快速导通,怎样可提高dIF/dt的额定值。

3、一旦可控硅锁定,栅极驱动即可减小或完全取消。

使用脉冲信号触发可控硅可减小栅极

功耗。

4、在栅极触发方式中,触发脉冲必须持续到可控硅的阳、极之间电流超过锁定电流IL才

能取消。

一旦稳定的导通状态建立,IH是维持可控硅导通的最小电流。

要关断可控硅,必须使可控硅的导通电流降至IH之下。

具体做法可减小可控硅两端所施加的电压。

5、下面以本公司常用型号BT151为例作一说明。

在规格书中, IGT=15MA,Vd=12V,It=0.1A

在电阻性负载时的IL=40MA,TGT=2US。

在下面的栅极触发参考图中可查得,有一特性曲线与其对应。

为了缩小开通时间的分散性,都应采用强触发脉冲,当触发脉冲的Igtm/Igt=5—6倍时,元件的开通性能有明显的改善,这样比较恰当的强触发电流波形的前沿如下图所示.其对应的特性曲线如断态通态电压曲线中标示的with high gate current

Igtm/Igt Igtm/Igt=5—6

实际

20us 3--4 20US

断态通态电压曲线。