数字电子技术基础2试题与答案

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

.已知三变量逻辑函数的最大项之积的形式为

B.

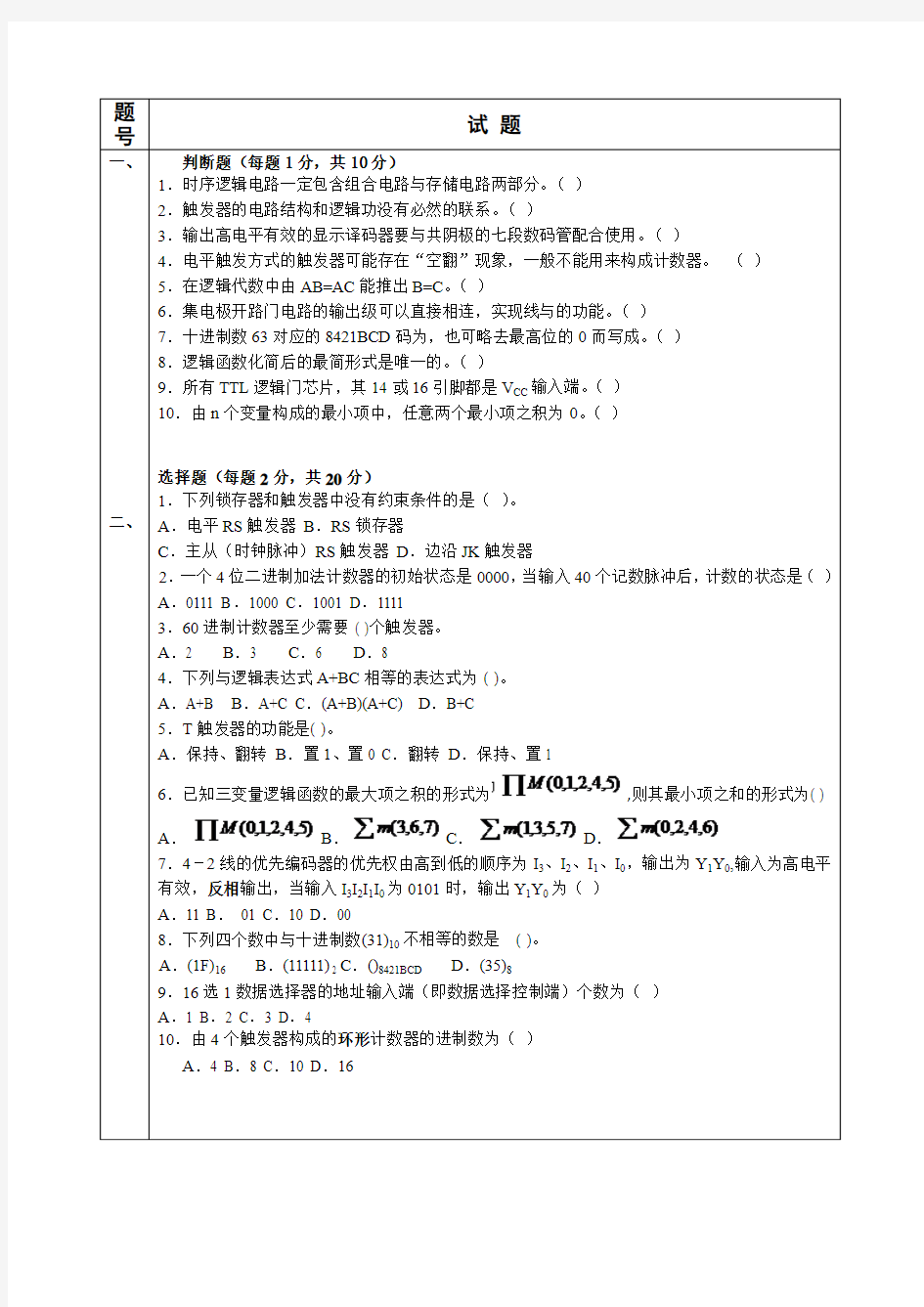

试题

填空题(每题3分,共18分)

1.有一移位寄存器,高位在左,低位在右,欲将存放在该移位寄存器中的二进制数除以十进制数4,则需要将该移位寄存器中

的数()移()位,需要()个移位脉冲。

2.4K*1的RAM有()根地址线,()根数据线,要扩展成8K*8的RAM,需要4K*1的RAM()片。

3.三态门中的“三态”指的是()、()和高阻态;现有8个三态门的输出连接在同一根总线上,则在任何时刻,至少有()个三态门处于高阻态。

4.由3个触发器构成的扭环形计数器,为()进制计数器,若时钟频率为6KHz,则此环形计数器输出信号的频率为()5.根据对偶规则,直接写出的对偶式为()。

6.函数在()时发生冒险现象,属于()冒险(填1或0),而通过添加冗余项()可以消除其中的冒险现象。

题(每题6分,共12分)

1.用逻辑代数公式化简

2.用卡诺图法化简逻辑函数

分析设计题(1题12分,2题14分,3题14分,共40分)

1.74LS161是四位二进制加法计数器,具有异步清零、同步预置数、保持和计数的功能,请分别分析图1(a)、(b)所示电路实现的是几进制计数器,并画出对应的状态转换图。

图1

试题

所示时序逻辑电路的逻辑功能,要求写出驱动方程、状态方程,画出状态表、状态图,并指出其实现的是几进制的计数器,是否具

图2

个三变量的奇数判别电路,即当输入变量中1的个数为奇数个时输出为1,否则输出为0。(1)基于2输入异或门电路实现;(2)基实现;(3)基于8选1数据选择器74LS151实现。图3和表1分别是74LS138的逻辑符号图和功能表,图4和表2是74LS151的逻辑

图3 74LS138逻辑符号图图4 74LS151逻辑符号图

1 74LS138的功能表表

2 74LS151的功能表