CPU大作业报告(详细)

cpu专题报告范文

专题报告范文标题由事由、文种组成,如《关于招商工作有关政策的报告》。

有的报告标题也可标明发文机关。

标题要明显反映报告专题事由,突出其专一性。

正文可采用“三段式”结构法。

以反映情况为主的专题工作报告主要写情况、存在的问题、今后的打算和意见;以总结经验为主的专题工作报告主要写情况、经验,有的还可略写不足之处和改进措施;因工作失误向上级写的检查报告主要写错误的事实、产生错误的主客观原因、造成错误的责任、处理意见及改进措施等。

结尾通常以“请审核”、“请审示”等语作结。

我要写篇报告,请大家帮我简要概括一下cpu的发展历史一、诞生但从20世纪70年代开始,由于集成电路的大规模使用,把本来需要由数个独立单元构成的CPU集成为一块微小但功能空前强大的微处理器时。

CPU才真正在电子计算机产业中得到广泛应用。

1971年, Intel公司推出了世界上第一台真正的微处理器--4004。

起步的角逐1978年,Intel公司生产出16位的微处理器,称之为X86指令集。

二、微机时代的来临三、高速CPU时代的腾飞1990年,Intel公司推出的80386 SL和80386 DL都是低功耗、节能型芯片,主要用于便携机和节能型台式机。

增加了一种新的工作方式:系统管理方式。

当进入系统管理方式后,CPU 就自动降低运行速度、控制显示屏和硬盘等其它部件暂停工作,甚至停止运行,进入“休眠”状态,以达到节能目的。

四、奔腾时代Pentium(奔腾)微处理器于1993年三月推出,它集成了310万个晶体管。

它使用多项技术来提高cpu性能,主要包括采用超标量结构,内置应用超级流水线技术的浮点运算器,增大片上的cache容量,采用内部奇偶效验一边检验内部处理错误等。

对cpu的认识500字论文按研究问题的大小不同可以把论文范文分、为宏观论文范文和微观论文范文。

凡属国家全局性、带有普遍性并对局部工作有一定指导意义的论文范文,称为宏观论文范文。

它研究的面比较宽广,具有较大范围的影响。

CPU大作业实验报告

实验目的1.深入理解基本模型计算机的功能、组成知识;2.深入学习计算机各类典型指令的执行流程;3.学习硬布线控制器的设计过程和相关技术;4.在掌握部件单元电路实验的基础上,进一步将单元电路组成系统,构造一台基本模型计算机;5.定义20条MIPS指令集的典型指令,并编写相应的汇编程序,能在模型机上调试,掌握计算机整机概念;6.通过熟悉较完整的计算机的设计,全面了解并掌握硬布线控制方式计算机的设计方法,真正理解利用软件进行硬件设计的方法和技巧。

实验原理在部件实验过程中,各部件单元的控制信号是人为模拟产生的,而本实验将能在硬布线控制下自动产生各部件单元控制信号,实现特定的功能。

实验选择了MIPS体系结构中比较典型的指令,使用QuartusII软件工具,通过原理图以及VHDL语言设计CPU的逻辑电路来实现这些指令。

另外还用MIPS汇编语言编写了用于CPU测试的简单程序,对所设计的CPU逻辑电路进行功能仿真模拟,以验证CPU逻辑电路的正确性。

实验涉及到的R指令有ADD、SUB、AND、OR、XOR、SLL、SRL、SRA、JR;I 指令有ADDI、ANDI、ORI、XORI、LW、SW、BEQ、BNE、LUI;J指令有J、JAL。

指令格式如下图所示。

单周期CPU的逻辑电路图跳转指令寄存器指定是从32位的寄存器堆中选择出一个32位的寄存器用于读或写数据。

由于JAL指令要把分支延迟槽下一条指令的指令地址保存在寄存器31号中,故需要设置一个控制信号CALL,当CALL=1时,选择31号寄存器,为JAL跳转指令提供寄存器,当CALL=0时,从32位的寄存器堆中根据地址选择出一个32位的寄存器用于读或写数据。

它的真值表如表9-1所示,电路符号如图9-1所示。

表9-1 跳转指令寄存器指定的真值表CALL 1 0输入REGN[4..0] X REGN[4..0]输出WN[4..0] 11111 REGN[4..0]原理图设计跳转指令寄存器指定元件图5-10-2跳转指令寄存器指定电路符号由描述和真值表创建跳转指令寄存器指定的原理图,如图5-10-2所示:图5-10-1跳转指令寄存器指定的原理图VHDL设计跳转指令寄存器指定元件由于VHDL语法的多样性和灵活性。

cpu的实验报告

cpu的实验报告CPU的实验报告引言:计算机是现代社会不可或缺的工具,而CPU(Central Processing Unit)则是计算机的核心部件之一。

CPU负责执行计算机指令,处理数据和控制计算机的各种操作。

本文将对CPU进行实验,并对实验结果进行分析和总结,以便更好地理解和掌握CPU的工作原理。

一、实验目的本次实验的目的是通过对CPU的实验,深入了解CPU的结构和工作原理,掌握CPU的运行过程和性能评估方法。

二、实验过程1. CPU的结构CPU主要由控制单元和算术逻辑单元组成。

控制单元负责解析和执行指令,算术逻辑单元负责进行算术和逻辑运算。

实验中,我们对CPU的各个部件进行了详细的分析和研究。

2. CPU的指令执行过程CPU的指令执行过程包括取指、译码、执行和写回四个阶段。

在实验中,我们通过模拟CPU的指令执行过程,对每个阶段进行了详细的观察和记录,并分析了每个阶段的作用和影响因素。

3. CPU的性能评估为了评估CPU的性能,我们进行了一系列的实验。

通过改变CPU的主频、缓存大小和指令集等因素,观察CPU的运行速度和效率,并进行性能比较和分析。

实验结果表明,这些因素对CPU的性能有着重要的影响。

三、实验结果与分析1. CPU的结构分析通过对CPU的结构进行分析,我们发现控制单元和算术逻辑单元之间的协作非常重要。

控制单元负责解析和执行指令,而算术逻辑单元负责进行计算和逻辑运算。

两者之间的紧密配合使得CPU能够高效地运行。

2. 指令执行过程分析通过对CPU的指令执行过程进行分析,我们发现每个阶段都有其特定的作用。

取指阶段负责从内存中读取指令,译码阶段负责解析指令,执行阶段负责执行指令,写回阶段负责将结果写回内存。

每个阶段的效率和性能都对CPU的整体运行速度有着重要的影响。

3. 性能评估结果通过对CPU的性能评估实验,我们发现主频、缓存大小和指令集等因素对CPU 的性能有着重要的影响。

提高主频可以加快CPU的运行速度,增加缓存大小可以提高数据读取和存储的效率,而优化指令集可以提高CPU的指令执行效率。

cpu报告

计算机设计与实践CPU设计报告班级:1203103学号:1120310312姓名:孙艳铎一.实验目的1、掌握Xilinx ISE集成开发环境和ModelSim仿真工具的使用方法。

2、掌握VHDL语言。

3、掌握FPGA编程方法及硬件调试手段。

4、深刻理解处理器结构和计算机系统的整体工作原理。

二.实验环境1、Xilinx ISE 9.1i集成开发环境2、MOdelSim XE II v5.6a仿真工具3、COP2000系统实验平台三.实验内容及要求根据计算机组成原理课程所学的知识和本课程所讲的设计思想,设计并实现一个给定指令系统的处理器,包括VHDL语言的实现和FPGA芯片的编程实现,为以后应用和设计处理器系统打下基础。

本实验的任务是设计一个简单的RISC处理器,该处理器是在给定的指令集下构建的,支持十条指令。

假定主存可以在一个时钟周期内完成一次存取操作,而且可以和CPU同步工作。

系统使用一个主存单元:指令读取和数据访问都使用同一组存储器。

处理器的指令字长和指令寄存器IR长度自定,CPU包含8个8位通用寄存器R0~R7,和1个16位的程序计数器PC。

取指令时,可以直接从主存中提取16位的指令信息,而进行数据访问时,与主存进行8位的数据交换。

处理器的地址总线宽度是16位,数据总线宽度也是16位,无论是取指还是数据访问,都使用同一组数据总线,只是数据信息的宽度不同。

处理器所支持的指令包括LDA,STA,MOV,MVI,ADD,SUB,JZ,JMP,IN,OUT。

其中仅有LDA和STA是访存指令,所有的存储器访问都通过这两条指令完成;ADD 和SUB是运算指令,MOV和MVI是传数指令,他们都在处理器内部完成;JZ 是跳转指令,根据寄存器的内容进行绝对跳转;JMP是无条件转移指令;IN和OUT是输入输出指令,所有I/O端口与CPU之间的通信都由IN和OUT指令完成。

要求根据给定的指令系统设计处理器,包括指令格式设计、微操作的定义、节拍的划分、VHDL语言的实现及FPGA编程实现。

CPU性能测试实验报告

CPU性能测试实验报告计算机硬件技术基础课程实验报告实验题目:CPU性能测试1、实验目的了解CPU参数的含义,以及各个参数对CPU性能的影响2、实验环境①实验硬件环境(计算机的型号、基本配置)宏基4741G华硕K401E联想Y560处理器型号Intel酷睿i3370M Inter Pentium T4400Intel酷睿i5460M 处理器主频 2.4GHz 2.2GHz 2.53GHz内存容量2G1G4GB硬盘容量320G320G500G显卡芯片NVIDIA Geforce GT320M NVIDIA Geforce310M ATI Mobility Radeon 操作系统Windows7Wiindows XP Windows7②实验软件坏境(操作系统、测试软件等)CPU-Z,是一款检测CPU使用程度最高的一款软件,它可以提供一些关於处理器的资讯,包含了制造厂及处理器名称,核心构造及封装技术,内部、外部频率,最大超频速度侦测,也可以查出处理器相关可使用的指令集。

最新的1.5.5版加入了可侦测处理器的核心电压、L2快取汇流排频宽、Windows NT/2000环境下的双处理器模式侦测,及记忆体时脉(如CAS Latency,RAS to CAS,RAS Precharge)。

Everestultimate(原名AIDA32)一款强大测试软硬件系统信息的工具。

它可以详细的测试PC每一个方面的信息。

支持CPU、FPU基准测试,提供C PU Queen、CPU PhotoWorxx、CPU ZLib、CPU AES、FPU Julia、FPU Mande、FPU SinJulia基准测试模块,最新版支持三核心AMD Phenom、六核心Inte l Dunnington Xeon处理器;SuperPi cpu性能测试软件原理是计算圆周率小数点的位数SuperPi是一个测试CPU性能的计算软件;它的工作原理是计算圆周率小数点的位数.例如:SuperPi100万位就是CPU计算到圆周率小数点后100万的意思,时间越短表示CPU的计算能力越强!Fritz Chess Benchmark是一款国际象棋测试软件,是国际象棋软件Fr itz自带的电脑棋力测试程序,由于支持多线程,而且它做的是大量科学计算,所有经常被用来测试电脑的科学运算能力。

cpu设计实验报告

cpu设计实验报告CPU设计实验报告1. 引言计算机是现代社会不可或缺的工具,而中央处理器(CPU)则是计算机的核心组件之一。

本实验旨在设计和实现一个简单的CPU,以加深对计算机组成原理的理解,并通过实践掌握CPU的基本工作原理。

2. CPU设计概述我们的CPU设计基于冯·诺依曼结构,包括指令寄存器(IR)、程序计数器(PC)、算术逻辑单元(ALU)和寄存器文件等关键组件。

CPU的指令集采用RISC(精简指令集计算机)风格,指令长度为32位。

3. 指令集设计我们设计了一套简单的指令集,包括算术运算指令(加法、减法、乘法、除法)、逻辑运算指令(与、或、非)以及数据传输指令(加载、存储)。

指令的格式包括操作码、源操作数和目标操作数。

4. 寄存器文件设计寄存器文件是CPU中用于存储数据的重要组件。

我们设计了一个包含8个通用寄存器的寄存器文件,每个寄存器的宽度为32位。

通过寄存器文件,CPU能够高效地进行数据的读取和存储。

5. 控制单元设计控制单元是CPU中的重要模块,负责解析指令并控制各个组件的操作。

我们设计了一个简单的控制单元,使用有限状态机(FSM)来实现指令的解析和控制信号的生成。

控制单元根据指令的操作码,决定对应的操作,并将操作所需的控制信号发送给其他组件。

6. 数据通路设计数据通路是CPU中各个组件之间的数据传输路径。

我们设计了一个简单的数据通路,包括指令寄存器、程序计数器、寄存器文件、算术逻辑单元等。

数据通路能够将指令中的操作数从寄存器文件中读取出来,并将运算结果写回到寄存器文件。

7. CPU实现与验证我们使用硬件描述语言(HDL)对CPU进行实现,并通过仿真和测试验证其正确性。

通过编写测试程序,我们能够对CPU的各个指令进行测试,并检查其运行结果是否符合预期。

8. 结果与分析经过测试,我们的CPU能够正确执行设计的指令集,并产生正确的运算结果。

通过性能测试,我们还评估了CPU的运行速度和效率,并与其他现有的CPU进行了比较。

CPU设计实验报告Word版

实验中央处理器的设计与实现一、实验目的1、理解中央处理器的原理图设计方法。

2、能够设计实现典型MIPS的11条指令。

二、实验要求1、使用Logisim完成数据通路、控制器的设计与实现。

2、完成整个处理器的集成与验证。

3、撰写实验报告,并提交电路源文件。

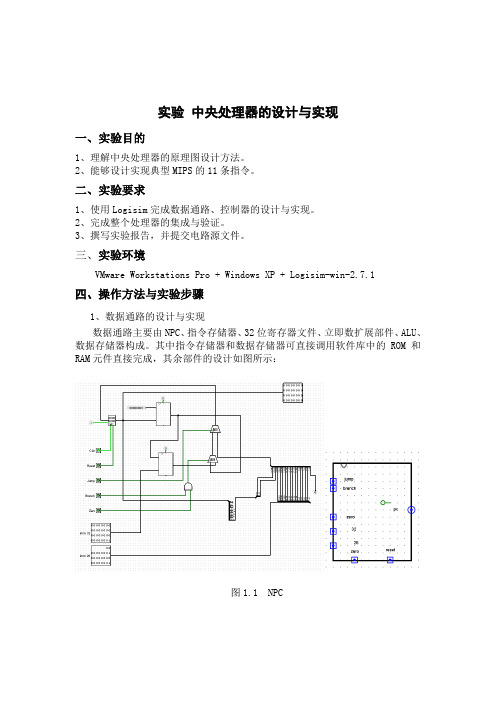

三、实验环境VMware Workstations Pro + Windows XP + Logisim-win-2.7.1四、操作方法与实验步骤1、数据通路的设计与实现数据通路主要由NPC、指令存储器、32位寄存器文件、立即数扩展部件、ALU、数据存储器构成。

其中指令存储器和数据存储器可直接调用软件库中的ROM和RAM元件直接完成,其余部件的设计如图所示:图1.1 NPC图1.2 32位寄存器图1.3 立即数扩展部件图1.4 ALU2、控制器的设计与实现控制器的主要设计思想如图所示图2.1 控制器设计思想输入000000001101100011101011000100000010输出R-type ORI LW SW BEQ JUMP RegDst100x x x ALUSrc01110x MemtoReg001x x x RegWrite111000 MemWrite000100 Branch000010 Jump000001 Extop x0111x ALUop210000x ALUop1x100x x ALUop0x0001xALUop[2:0]Funct[3:0]指令ALUctr[2:0] 1110000add0101110010sub1101110100and0001110101or0011111010slt111010xxxx ori001000xxxx Lw/sw010011xxxx beq110表2.1 控制器设计真值表图2.2 控制器3、处理器的集成与验证集成:将各个部件按要求链接,具体方式如图所示:图3.1 CPU验证:将指令的16进制表示输入指令存储器,运行后记录寄存器中的数据与标准值进行对照:图3.2 寄存器对照值图3.3 寄存器实际运行值由上两图对照可得CPU的功能实现成功。

CPU实验报告范文

CPU实验报告范文一、实验目的本次实验的目的是设计和实现一个简单的中央处理器(CPU),通过实践掌握CPU的基本工作原理和实现方法。

二、实验原理1.CPU的基本概念中央处理器(CPU)是计算机的核心部件,负责执行计算机指令和控制计算机的操作。

它由运算器、控制器和寄存器组成。

运算器负责执行算术和逻辑运算,包括加法、减法、乘法、除法等。

控制器负责指挥CPU的工作,通过控制总线实现对内存和其他外部设备的访问。

寄存器是CPU内部的存储器,用于暂时存放指令、数据和中间结果。

2.CPU的实现方法CPU的实现采用组合逻辑电路和时序逻辑电路相结合的方法。

组合逻辑电路是由逻辑门构成的电路,它的输入只依赖于当前时刻的输入信号,输出也只与当前时刻的输入信号有关。

而时序逻辑电路则包含存储元件,其输出不仅与当前时刻的输入信号有关,还与之前的输入信号有关。

CPU的实现过程主要包括以下步骤:(1)设计指令集:确定CPU支持的指令集,包括指令的格式和操作码。

(2)设计控制器:根据指令集设计控制器,确定各个指令的执行过程和控制信号。

(3)设计运算器:根据指令集设计运算器,确定支持的算术和逻辑运算。

(4)设计寄存器:确定需要的寄存器数量和位数,设计寄存器的输入输出和工作方式。

3.实验环境和工具本次实验使用的环境和工具如下:(1)硬件环境:计算机、开发板、示波器等。

(2)软件环境:Win10操作系统、Vivado开发工具等。

三、实验步骤1.设计指令集根据实验要求,我们设计了一个简单的指令集,包括加法、减法、逻辑与、逻辑或和移位指令。

每个指令有特定的操作码和操作数。

2.设计控制器根据指令集设计了一个控制器。

控制器根据指令的操作码产生相应的控制信号,控制CPU内部寄存器、运算器和总线的操作。

3.设计运算器根据指令集设计了一个运算器。

运算器包括加法器、减法器、与门和或门等。

它通过输入的操作数和控制信号完成相应的运算操作。

4.设计寄存器根据实验需求确定了所需的寄存器数量和位数。

CPU设计报告 网络工程 计算机组成原理大作业 西安科技大学

课程设计:计算机组成原理题目名称:CPU设计姓名:学号:班级:网络工程完成时间:2014年1月6日1设计目的:通过一个完整的16位指令系统结构的设计,加深对计算机组成原理课程内容的理解,建立起整机系统的概念,掌握计算机设计的基本方法,培养学生科学的工作作风和分析、解决实际问题的工作能力。

要求学生综合理解和熟悉计算机系统的组成原理,掌握计算机主要功能部件的工作原理和设计方法,掌握指令系统结构设计的一般方法,掌握并运用微程序设计思想,在设计过程中能够发现、分析和解决各种问题,自行设计自己的指令系统结构。

2 设计任务:CPU 的主要功能是执行指令,控制完成计算机的各项操作,包括运算操作、传送操作、输入/输出操作等。

此次设计CPU就是为了了解CPU运行的原理,从而完成从指令系统到CPU的设计,采取较简单的组成模式,以尽量简洁的设计帮助读者掌握CPU 的基本原理。

3 设计指标:能实现MOV,LAD,ADD,SUB,INC,AND,STO,JMP,STOP,JNZ这些指令,并建立完整的指令系统。

4 设计说明:4.1数据格式此自设计CPU规定数据采用定点整数表示,字长16位,格式如下:CPU设计三大类指令共10条,其中包括算术逻辑指令、访问及转移指令和停机指令。

1.算术逻辑指令设计5条算术逻辑指令并用单字长表示,寻址方式采用寄存器直接寻址,其格式如下:其中,OP-CODE为操作码,RS为源寄存器,RD为目的寄存器。

2.访存指令及转移指令模型机设计2条访问指令,即存数(STA)、取数(LDA)、3条转移指令,即无条件转移(JMP)、结果为零或有进位转移指令(BZC)。

其格式如下:其中,OP-CODE为操作码, RD为目的寄存器地址(LDA、STA指令使用),D为位移量(正负均可)。

3. 停机指令这类指令只有1条,即停机指令STO,用于实现停机操作。

4.2 数据通路通常把许多寄存器之间传送信息的通路,称为“数据通路”。

cpu设计报告

Z0

以下是带符号数乘法器的代码,其中前半部分用与非门实现,后半部分经过逻辑综合后得到结果。

modulemul_signed(a,b,z);

input[15:0]a,b;

output[31:0] z;

reg[15:0]a_bi[15:0];

integeri,j;

always@ * begin

for(i=0;i<15;i=i+1)

+p[i]p[i-1]g[i-2]

+……

+p[i]p[i-1]……p[1]c[0]

+ p[i]p[i-1]……p[1]p[0]c[0]

从理论上来讲,由c[i+1]的表达式可以并行产生所有位的进位输入,但是这样的电路太复杂,难以实现。所以采用了树形结构来分层次产生进位。

首先是一位加法器的代码,除了产生一位加法结果s外,还生成进位产生的函数g和进位传递函数p。一位加法器和GP生成器代码如下:

modulecla_2 (a,b,c_in,g_out,p_out,s);

input[1:0]a,b;

inputc_in;

outputg_out,p_out;

output[1:0] s;

wire[1:0]g,p;

wirec_out;

add add0 (a[0],b[0],c_in, g[0],p[0],s[0]);

endmodule

六、指令系统

本CPU部分指令如下(有一些是我自己用来调试的指令,在此就不列举了):

000000

Rs

rt

rd

00000

100000

寄存器加

000000

Rs

Rt

Rd

CPU武汉大学信息安全实验报告完整版

开放式教学CPU设计与测试系统----信息安全专业实践报告班级:撰写人:时间:X年X月X日一.前言1.1 实验目的1.融会贯通本实验课程所教授的知识,通过知识的综合应用,加深对CPU系统各模块的工作原理及相互联系的认识。

2.学习设计和调试CPU的基本步骤和方法,基本熟悉现代EDA技术设计电子系统的流程和方法。

3.初步掌握CPU设计与组装调试的实践方法。

1.2 实验内容1.按给定的数据格式和指令系统,设计一个包含指令系统、运算器、控制器和寄存器组的完整的CPU。

2.利用VHDL硬件描述语言,对CPU的各个功能模块进行代码编写,并学会将各个功能部分组织连接成一个完整CPU体系结构。

3.掌握实验平台上的调试方法。

1.3 实验环境软件:Quartus-5.1我们使用该软件完成编码工作,并可以进行有效的时序模拟。

最终烧片等都用该软件。

调试软件DC使用该软件监控FPGA-CPU的状态和通过设置断点调试FPGA-CPU正在执行的程序。

硬件:FPGA (Field Programmable Gate Array),即现场可编程门阵列。

FPGA具有掩膜可编程门阵列的通用结构,它由逻辑功能块排成阵列组成,并由可编程互联资源连接这些逻辑功能块来实现不同的设计。

二.设计报告2.1 实验方法1.指令系统设计:设计FPGA-CPU的指令集。

2.逻辑设计:分析并确定CPU主要功能模块,分析每条指令的执行过程,数据的流向和控制信号的产生,画出逻辑结构图3.代码实现:依据各个功能模块分别编写源码并生成器件,将各个器件和模块之间互连,得到顶层设计图,根据逻辑图将器件引脚逐一连接好,并对封装好的CUP个端口配置管脚4.硬件调试:将sof文件下载到FPGA中用调试软件进行调试2.2 总体说明1、指令系统:计算机的指令是用户使用计算机与计算机本身运行的最小功能单位。

一台计算机支持的全部指令就构成该机的指令系统。

从计算机本身的组成看,指令系统直接与计算机系统的性能和硬件结构的复杂程度等密切相关,它是CPU设计的起始点和基本依据。

CPU计算机组成原理实验报告

CPU计算机组成原理实验报告实验名称:CPU计算机组成原理实验一、实验目的:1.了解计算机硬件的基本组成原理,特别是CPU的工作原理;2.掌握计算机的组装和调试技能;3.熟悉计算机操作系统的安装和配置方法;4.学习使用计算机进行基本的应用程序开发。

二、实验设备和材料:1.CPU主机:包括主板、CPU、内存、硬盘等;2.显示设备:显示器、键盘、鼠标等;3.软件:操作系统、开发工具等。

三、实验步骤:1.将主板、CPU、内存、硬盘等硬件组件组装到主机箱中,连接电源、显示器、键盘、鼠标等外设;2.打开电源,按照BIOS界面提示进行主板和硬件设置;3.插入操作系统安装光盘,根据安装界面提示进行操作系统的安装;4.安装完成后,进入操作系统,根据提示进行相应驱动程序的安装和配置;5.打开开发工具,进行编程实践。

四、实验结果与分析:通过以上步骤,成功组装了一台计算机并安装了操作系统。

在操作系统中,能够正常运行各种应用程序,并且能够进行编程开发。

通过实验,可以清楚地了解到计算机硬件的组成原理,特别是CPU的工作原理。

CPU 作为计算机的核心部件,负责指令的执行和数据的处理。

通过对CPU的组装和调试,可以更深入地了解其工作原理和操作方法。

五、实验心得与体会:通过实验,我对计算机硬件的组装和设置有了更深入的理解。

计算机硬件的组成非常复杂,需要我们仔细阅读说明书,按照步骤进行操作。

在实验过程中,我们学会了解决一些常见的硬件问题,如硬件不兼容、连接错误等。

此外,操作系统的安装和配置也是非常重要的一步,只有正确地安装和配置操作系统,才能保证计算机的正常运行。

通过这个实验,我不仅学到了理论知识,还锻炼了实际操作的能力。

计算机的组装和调试需要我们仔细、耐心地进行,一丝不苟地对待每一步操作。

只有掌握了计算机组成原理,才能更好地理解和应用计算机技术。

通过实验,我深刻地认识到计算机是一台高度复杂的机器,它可以帮助我们解决各种问题,提高工作效率。

cpu设计实验报告

cpu设计实验报告CPU设计实验报告摘要:本实验旨在设计一个基本的中央处理器(CPU),并通过实验验证其性能和功能。

在设计过程中,我们使用了Verilog硬件描述语言和ModelSim仿真工具。

通过对CPU的设计和仿真实验,我们验证了CPU的正确性和性能,并对其进行了性能分析和优化。

1. 引言CPU是计算机系统中最核心的部件之一,它负责执行计算机指令和控制数据流动。

因此,设计一个高效、稳定的CPU对于计算机系统的性能至关重要。

本实验旨在通过Verilog硬件描述语言和ModelSim仿真工具,设计一个基本的CPU,并验证其性能和功能。

2. 设计过程我们首先对CPU的功能和性能进行了分析和规划,确定了CPU的基本架构和指令集。

然后,我们使用Verilog语言编写了CPU的硬件描述,并通过ModelSim进行了仿真验证。

在设计过程中,我们重点关注了CPU的时序逻辑、数据通路和控制逻辑,确保CPU能够正确地执行指令并保持稳定的性能。

3. 实验结果通过对CPU的设计和仿真实验,我们验证了CPU的正确性和性能。

我们使用了一系列的测试用例对CPU进行了功能和性能测试,并对其进行了性能分析和优化。

实验结果表明,我们设计的CPU能够正确地执行各种指令,并在性能上达到了预期的目标。

4. 总结和展望本实验通过Verilog硬件描述语言和ModelSim仿真工具,设计并验证了一个基本的CPU。

通过实验,我们对CPU的设计和性能有了更深入的了解,并对其进行了性能分析和优化。

未来,我们将进一步完善CPU的设计,提高其性能和功能,以满足计算机系统的需求。

综上所述,本实验为我们提供了一个宝贵的机会,通过实际设计和验证,深入了解了CPU的工作原理和性能特点,为我们今后的学习和研究打下了坚实的基础。

希望通过不懈的努力,我们能够设计出更加高效、稳定的CPU,为计算机系统的发展做出更大的贡献。

cpu实训报告的总结

cpu实训报告的总结

CPU实训报告的总结应包括以下内容:

1. 实验目的:说明实训的目标和意义,即要实现的功能或解决的问题。

2. 实验原理:介绍CPU的基本结构和工作原理,包括数据通路和控制器的组成,以及指令的执行过程。

3. 实验过程:详细描述实际操作过程和所使用的软件或硬件工具,包括实验环境的搭建、所需的材料和设备的准备等。

4. 实验结果:列出实验中的相关数据、图表和实际运行效果,展示实验的完成情况和达到的目标。

5. 实验分析:对实验结果进行分析和解释,并提供相应的性能评估,比较实验结果与预期目标的差异或实验改进的空间。

6. 实验总结:总结实验的收获和体会,说明实训过程中遇到的困难和解决方法,以及自身对CPU工作原理的理解和提升。

7. 实验展望:展望未来可能的进一步工作和改进方向,指出本实训的不足之处和值得改进的地方,提出对CPU实训的改进建议。

总之,CPU实训报告的总结应该简明扼要地总结实验目的、

原理、过程和结果,并结合分析和总结,展望未来的发展方向,提出改进建议。

《CPU设计实验报告》word版

CPU设计实验报告姓名:学号:邮箱:一、实验目的:1、掌握硬件描述语言VHDL和EDA工具Quartus II;利用VHDL设计16位串行CPU,实现算术和逻辑运算指令、转移指令、访存指令、堆栈指令和控制指令;2、掌握CPU的调试和测试方法。

二、实验内容:1、运用硬件描述语言VHDL实现寄存器堆和算数逻辑单元设计、指令集和指令格式、时序设计和整体结构设计、指令译码器的设计、访存单元的设计、调试单元的设计;2、上机调试。

三、实验步骤:1、寄存器堆的设计寄存器堆由16个16位寄存器组成。

其中reset是异步清0端,reset=0时将所有寄存器清0。

dr_sel和sr_sel是目实用文档标寄存器和源寄存器编号,dr_out和sr_out输出目标寄存器和源寄存器的内容。

reg_sel指定一个寄存器编号,将该寄存器内容送给reg_out,这两个端口用于调试时观察每个寄存器的值。

reg_en是写允许端。

reg_en=“01”时,在clk的上升沿将from_alu写入dr_sel指定的寄存器;reg_en=“10”时,在clk的上升沿将from_mem写入dr_sel指定的寄存器。

reg_en取其他值时不改变寄存器堆的值。

设计方法:subtype WORD is std_logic_vector(15 downto 0);type REGISTERARRAY is array ( 0 to 15 ) of WORD;signal reg_bank: REGISTERARRAY 则reg_bank就是我们所需要的寄存器堆。

写寄存器堆的方法:reg_bank(conv_integer(dr_sel))<=from_alu;实用文档读寄存器堆的方法:dr_out <= reg_bank(conv_integer(dr_sel));其中,conv_integer是STD_LOGIC_ UNSINGED 程序包提供的函数,将标准逻辑矢量转换成整数,作为reg_bank 的下标。

cpu组成与机器指令执行实验实验报告

cpu组成与机器指令执行实验实验报告

CPU组成与机器指令执行实验实验报告

摘要:本实验旨在通过对CPU组成与机器指令执行的实验,深入了解CPU的

结构和工作原理,以及机器指令的执行过程。

实验结果表明,CPU由控制单元、运算单元和寄存器组成,通过时钟信号控制各个部件协调工作,而机器指令的

执行则是通过取指、译码、执行和写回四个阶段完成的。

1. 实验目的

通过实验,深入了解CPU的组成和机器指令的执行过程,加深对计算机硬件的

理解。

2. 实验内容

(1)CPU组成实验:通过拆解一台计算机,了解CPU的组成结构,包括控制

单元、运算单元和寄存器等部件。

(2)机器指令执行实验:通过搭建一个简单的计算机模型,模拟机器指令的执行过程,包括取指、译码、执行和写回四个阶段。

3. 实验步骤

(1)CPU组成实验:拆解计算机,观察CPU的各个部件,了解其结构和功能。

(2)机器指令执行实验:搭建计算机模型,编写简单的机器指令,模拟指令的执行过程。

4. 实验结果

(1)CPU组成实验:观察到CPU由控制单元、运算单元和寄存器组成,通过

时钟信号控制各个部件协调工作。

(2)机器指令执行实验:模拟了机器指令的执行过程,包括取指、译码、执行

和写回四个阶段,加深了对机器指令执行过程的理解。

5. 实验结论

通过本次实验,深入了解了CPU的组成和机器指令的执行过程,加深了对计算机硬件的理解,为进一步学习计算机原理打下了良好的基础。

综上所述,本次实验对于加深对CPU组成和机器指令执行过程的理解起到了积极的作用,为进一步学习计算机原理提供了良好的基础。

多周期cpu 实验报告

多周期cpu 实验报告多周期CPU 实验报告引言计算机的发展已经走过了几十年的历程,从最初的单周期CPU,到后来的多周期CPU,每一次的改进都为计算机的性能和效率带来了显著的提升。

本实验旨在通过设计和实现一个多周期CPU,来深入理解计算机的工作原理和指令执行过程。

一、实验背景随着计算机应用领域的不断扩大,对计算机性能的要求也越来越高。

而单周期CPU在执行指令时,每个指令都需要占用一个完整的时钟周期,这样效率较低。

为了提高计算机的执行效率,多周期CPU应运而生。

多周期CPU将指令的执行过程划分为多个时钟周期,每个周期执行一个特定的操作,从而提高了计算机的并行度和效率。

二、实验设计1. CPU结构本次实验设计的多周期CPU采用经典的冯·诺依曼结构,包括指令存储器、数据存储器、控制器和运算器等模块。

指令存储器用于存储程序指令,数据存储器用于存储数据,控制器用于控制指令的执行过程,运算器用于执行运算操作。

2. 指令执行过程多周期CPU的指令执行过程可以划分为取指、译码、执行、访存和写回等阶段。

在取指阶段,CPU从指令存储器中读取指令,并将其送入译码阶段。

在译码阶段,CPU解析指令的操作码,并根据操作码控制后续的执行操作。

在执行阶段,CPU执行指令的具体操作,如加法、乘法等。

在访存阶段,CPU根据需要访问数据存储器,读取或写入数据。

在写回阶段,CPU将执行结果写回到寄存器中。

三、实验过程1. 指令存储器设计指令存储器是多周期CPU中的一个重要组成部分,它用于存储程序指令。

在本次实验中,我们采用了基于RAM的指令存储器设计。

通过将指令存储器划分为多个存储单元,每个存储单元存储一个指令,可以有效地提高指令的读取速度。

2. 控制器设计控制器是多周期CPU中的核心模块,它负责指令的执行过程控制。

在本次实验中,我们采用了有限状态机的设计方法来实现控制器。

通过定义不同的状态和状态转移条件,可以实现对指令执行过程的精确控制。

多周期cpu实验报告

多周期cpu实验报告多周期CPU实验报告一、引言多周期CPU是计算机体系结构中的一种重要设计,它通过将指令执行过程划分为不同的阶段,从而提高了计算机的性能和效率。

本实验旨在通过设计和实现一个简单的多周期CPU,来加深对计算机体系结构的理解和应用。

二、实验目的1. 理解多周期CPU的基本原理和工作流程。

2. 掌握多周期CPU的设计和实现方法。

3. 进一步熟悉计算机组成原理相关知识。

三、实验环境本实验使用Verilog HDL语言进行设计,并在ModelSim仿真环境下进行验证和测试。

四、实验过程1. CPU的整体设计在多周期CPU中,指令执行过程被划分为取指、译码、执行、访存和写回等多个阶段。

我们首先设计了一个基本的多周期CPU框架,包括指令寄存器、控制单元、ALU等核心组件,并通过总线连接各个组件。

2. 指令寄存器的设计指令寄存器用于存储当前正在执行的指令,它的输入端连接到指令存储器的输出端,输出端连接到译码器。

在每个周期的取指阶段,指令寄存器将从指令存储器中读取指令,并传递给译码器进行解码。

3. 控制单元的设计控制单元负责生成各个阶段的控制信号,以控制各个组件的工作。

在多周期CPU中,控制单元需要根据当前指令的类型和执行阶段的状态,生成相应的控制信号。

例如,在取指阶段,控制单元会生成使指令寄存器读取指令的控制信号。

4. ALU的设计ALU是多周期CPU中的核心组件之一,它负责执行各种算术和逻辑操作。

在多周期CPU中,ALU的输入端连接到寄存器文件和译码器的输出端,输出端连接到数据存储器和写回阶段。

在执行阶段,控制单元会生成相应的操作码,并将其传递给ALU,以执行相应的操作。

5. 数据存储器的设计数据存储器用于存储程序中定义的数据,并在需要时进行读写操作。

在多周期CPU中,数据存储器的输入端连接到ALU的输出端和写回阶段,输出端连接到ALU的输入端和访存阶段。

在访存阶段,控制单元会生成使数据存储器读写数据的控制信号。

cpu实验报告

cpu实验报告CPU实验报告引言计算机是现代社会不可或缺的工具,而中央处理器(CPU)则是计算机的核心。

CPU的性能直接影响着计算机的运行速度和效率。

为了深入了解CPU的工作原理和性能评估方法,我们进行了一系列的CPU实验。

本报告将详细介绍我们的实验过程、结果和分析。

实验一:CPU的组成与工作原理在第一个实验中,我们学习了CPU的基本组成和工作原理。

CPU由控制单元(CU)和算术逻辑单元(ALU)组成。

CU负责指令的解码和执行,而ALU则处理算术和逻辑运算。

我们通过拆解一台计算机,观察和研究了CPU的内部结构和连接方式。

我们还学习了指令集架构(ISA)和微指令的概念。

这个实验使我们对CPU的组成和工作原理有了更深入的理解。

实验二:CPU性能评估在第二个实验中,我们重点关注CPU的性能评估。

我们使用了一款性能评估工具,通过运行一系列的测试程序来测量CPU的性能。

我们评估了CPU的时钟频率、缓存大小和指令级并行性对性能的影响。

实验结果表明,时钟频率越高,CPU的运行速度越快。

增加缓存大小可以提高CPU的数据访问效率。

指令级并行性的优化也可以显著提升CPU的性能。

这个实验让我们了解了如何评估和优化CPU的性能。

实验三:CPU的架构设计在第三个实验中,我们设计了一款简单的CPU架构。

我们选择了精简指令集计算机(RISC)架构,因为RISC架构具有指令集简单、执行效率高的特点。

我们设计了CPU的指令集、寄存器组和数据通路,并使用硬件描述语言进行了模拟和验证。

通过这个实验,我们深入了解了CPU的架构设计原理和方法。

实验四:CPU的能耗优化在第四个实验中,我们研究了CPU的能耗优化方法。

我们使用了一款能耗监测工具,测量了CPU在不同负载下的能耗情况。

我们还尝试了一些能耗优化技术,如动态电压频率调整(DVFS)和低功耗模式。

实验结果显示,通过调整电压和频率,可以显著降低CPU的能耗。

低功耗模式也能有效减少CPU的能耗。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CPU大作业报告(详细)计算机原理课程设计小组信息小组编号XX成员信息姓名学号实验分工分值比例组长PC、控制器CU、硬件成员1 。

成员2 。

成员3 。

2、小组编号以课代表处公布为准;3、分值比例应由小组成员共同协商,总和为1。

设计内容和要求注:1、字体格式,宋体、小4号,居中;2、该项内容简述即可。

通过之前的课程作业实践,进一步学习和理解计算机原理组成原理,在此基础上,设计和实现小组的计算机系统。

该系统能够顺利执行自编的程序(使用自定义指令集),得出正确的运算结果。

实验按照结构组成、指令集、控制器和其它部件、单部件测试、系统组装和系统测试等步骤进行,设计一个较为完整的功能程序。

根据我们组的实际情况我们做的是32位五级流水MIPS指令集CPU,分为取指、译码、执行、访存、写回五个步骤。

设计步骤1.设计计算机的总体框图注:1、数据通路应予以标注;2、可使用其它颜色突出小组特色的功能部件或结构;3、复杂处理器可以给出多张或多层次结构图予以描述;4、文档所有插图格式为“嵌入型”,并居中。

PC PC_Out+PC_Out+44IF_RegPC_Out3funcshamtOPRegMuxPC_Out+ImmEx_IEx_IMUXreset PC_inPC_EnPC_out1IMIIF_EnclkresetPC_out2rsrtrdRegArrayAoutBoutBIoutID_ExRegID_wRegEnID_MemRID_MemwID_MemToRegALUMux1ALUMux2ABALUID_OPIDoutAIDoutBm_wRegEnm_MemRm_Memwm_MemToRegEx_MemRegALU_outclkresetrtrdID_Enclkresete_rtMem_Regm_ALUoutMemm_ALUoutouterDBouterDBm_rtm_RBdataclkresetMemaddrEx_en Mem_enwriteW_MenR W_MenWW_MenRW_MenWMem_MUX结构图双击可放大编辑2.设计各个功能部件的功能(1)算术逻辑运算单元ALU:其功能及与外部的连接端口如下:下图为示例ALUID_op ABFlagALU_outFlag功能简述:根据ID_op 的值选择相应的操作:'b000000:ALU_out=A+B;//add(op[3:2]==00 means R instruction)'b000001:ALU_out=A-B;//sub'b000110:ALU_out=A+B;//addI(op[3:2]==01 means I instruction) 'b000111:ALU_out=A-B;//subI 'b000100:ALU_out=A+B;//store 'b000101:ALU_out=A+B;//load 'b001110:Flag=1;(2)程序计数器PC : 插图PCPC_inresetPC_EnPC_outClock功能简述:1、当pc_En 为1时,pc_out<=pc_in;否则pc_out<=pc_out; 2、当reset 为0时,pc_out<='b0; (2) 通用寄存器GR :插图RegArrayrs rtw_wRegEnw_rtw_DataBoutAoutClock reset功能简述:1、当w_wRegEn 置1时,register[w_rt]<=w_data;将w_data 读到地址为w_rt 的通用寄存器中; 2、传递信号:Aout=register[rs];Bout=register[rt]; (4)IMem 插图IMempc_outI功能简述: I = data[pc_out];将地址为pc_out 的数据读到I 并输出。

(5)ALU-MUX1w_datam_ALUoutALU_MUX1AIDoutAforward A功能简述:当forwardA为00时,选择A=IDoutA;为01时,选择A=m_ALUout;为10时,选择A=w_data;(6)MemRegMemRegw_ALUoutw_MEMoutw_MemToRegw_rtw_wRgEn w_MemR w_MemWm_wRegEn m_MemR m_MemW m_MemToRegm_ALUoutOuterDBvm_rtMem_EnClock reset功能简述:当Mem_En 为1时,传递信号:w_wRegEn<=m_wRegEn;w_MemR<=m_MemR; w_MemW<=m_MemW;w_MemToReg<=m_MemToReg; w_rt<=m_rt;w_MEMout<=OuterDB; w_ALUout<=m_ALUout;(7)ALU-MUX2w_datam_ALUoutALU_MUX2BIDoutBforward B功能简述:当forwardB为00时,选择B=IDoutB;为01时,选择B=m_ALUout;为10时,选择B=w_data;(8)RegMUXOPEx_IRegMUX BIoutBout功能简述:当op[2]为0时,选择BIout=Bout;否则选择BIout=Ex_I;(9)Mem_MUXMem_MUXB w_MEMoutw_ALUoutw_MemToRegw_data功能简述:当w_MemToRega 为1时,选择w_data=w_ALUout;否则w_data=w_MEMout;(10)EX_MemRegEX_MemRegm_ALUoutm_wRegEn m_MemR m_MemW m_MemToRegALUoutClockve_rtEx_Enresetm_RBdataID_wRegEn ID_MemR ID_MemW ID_MemToRegB m_rt功能简述:当Ex_En 时传递信号:m_wRegEn<=ID_wRegEn;m_MemR<=ID_MemR; m_MemW<=ID_MemW;m_MemToReg<=ID_MemToReg; m_ALUout<=ALU_out; m_RBdata<=B; m_rt<=e_rt;(11)PC_MUXPC_MUXFlagPC_inPC_out2PC_out1功能简述:PC 控制信号选择,当flag 为1时选择PC_out2信号,否则选择PC_out1信号。

(12)IF_RegIF_RegClockvIF_EnresetPC_out1IIrtrsrdEx_IPC_out1Func op shamt功能简述:1、IF_En 置1时取指; 2、取指后将PC_out1和I 输出; 3、pc_out3<=pc_out1; Imm<=I[15:0];op<=I[31:26];rs<=I[25:21];rt<=I[20:16];rd<=I[15:11]; shamt<=I[10:6]; func<=I[5:0];(13)PC_AddImm+PC_out1Ex_IPC_out3功能简述:(14)ID_ExRegID_ExRegve_rtFunc op shamtPC_out3BIoutrt rdAoutID_En Clock resetID_wRegEn ID_MemR ID_MemW ID_MemToRegID_shamt ID_op ID_funcIDoutAIDoutB功能简述:1、ID_En 置1时ID_ExReg 工作; 2、BIout 和Aout 是两个操作数的输入; 3、PC_out3信号决定指令类型;(15)MEMOut_DBMEMm_RBdataw_MemW功能简述:1、通过OouterDB信号将MEM内的内容通过MemReg读到RegArray;2、通过m_RBdata信号将RegArray内的内容写到MEM里;3、通过mem_addr信号将执行后的结果写MEM里;4、通过w_MemR和w_MemW使能信号控制MEM的读写。

(16)PC_Add1PC_out1+PC_out功能简述:每次执行指令之前,PC_Add将PC的值加1以PC_out1传到IF_Reg。

3.指令系统注:1、字体格式,宋体、小4号;2、可用颜色标注特色指令。

指令操作码代码指令指令含义000000 ADD A加B结果存到000001 SUB A减B结果存000110 AddI A加立即数结果存000111 SUBI A减立即数结果存000100 Store 将RegArray中的000101 LOAD 将MEM里的值载001110 JUMP111111 NOP 空操作4.控制器描述控制器的设计与实现,给出信号编码表。

指令每一拍中使能信号的值:指令op 第一拍第二拍第三拍第四拍第五拍ADD 00000 PC_En=1 ID_En=1 ForwardA=00 m_MEM_R=0 w_MemToReg=1 IF_Ex=1 w_addr=1 ForwardB=00 m_MEM_W=0 w_wRegEn=1SUB 000001 PC_En=1 ID_En=1 ForwardA=00 m_MEM_R=0 w_MemToReg=1 IF_Ex=1 w_addr=1 ForwardB=00 m_MEM_W=0 w_wRegEn=1ADDI 000110 PC_En=1 ID_En=1 ForwardA=00 m_MEM_R=0 w_MemToReg=1 IF_Ex=1 w_addr=0 ForwardB=00 m_MEM_W=0 w_wRegEn=1SUBI 000111 PC_En=1 ID_En=1 ForwardA=00 m_MEM_R=0 w_MemToReg=1 IF_Ex=1 w_addr=0 ForwardB=00 m_MEM_W=0 w_wRegEn=1Store 000100 PC_En=1 ID_En=1 ForwardA=00 m_MEM_R=0 w_MemToReg=1 IF_Ex=1 w_addr=0 ForwardB=00 m_MEM_W=1 w_wRegEn=0Load 000101 PC_En=1 ID_En=1 ForwardA=00 m_MEM_R=1 w_MemToReg=0 IF_Ex=1 w_addr=0 ForwardB=00 m_MEM_W=0 w_wRegEn=1J 001110NOP 111111系统测试描述部件以及整机的测试方案和测试结果,并分析和总结测试结果。