FPGA器件XCS40XL及其在多画面处理器中的应用

FPGA可编程逻辑器件芯片xc4028xl-3hq208c中文规格书

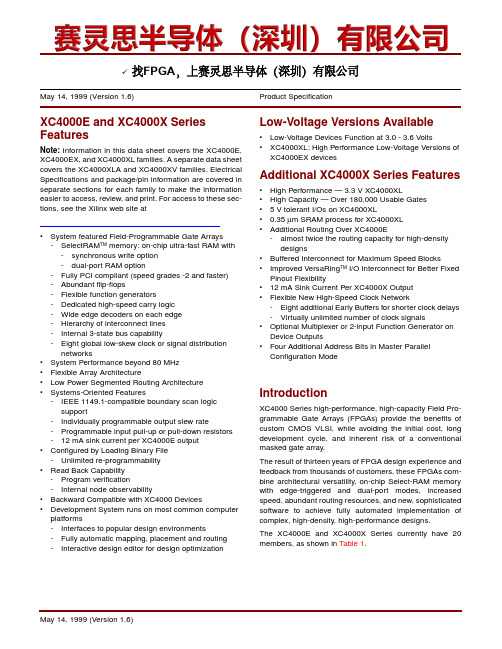

XC4000E and XC4000X Series FeaturesNote: Information in this data sheet covers the XC4000E, XC4000EX, and XC4000XL families. A separate data sheet covers the XC4000XLA and XC4000XV families. Electrical Specifications and package/pin information are covered in separate sections for each family to make the information easier to access, review, and print. For access to these sec-tions, see the Xilinx web site at•System featured Field-Programmable Gate Arrays -SelectRAM TM memory: on-chip ultra-fast RAM with -synchronous write option -dual-port RAM option-Fully PCI compliant (speed grades -2 and faster)-Abundant flip-flops-Flexible function generators-Dedicated high-speed carry logic -Wide edge decoders on each edge -Hierarchy of interconnect lines -Internal 3-state bus capability-Eight global low-skew clock or signal distribution networks•System Performance beyond 80 MHz •Flexible Array Architecture•Low Power Segmented Routing Architecture •Systems-Oriented Features-IEEE 1149.1-compatible boundary scan logic support-Individually programmable output slew rate-Programmable input pull-up or pull-down resistors -12 mA sink current per XC4000E output •Configured by Loading Binary File -Unlimited re-programmability •Read Back Capability -Program verification-Internal node observability•Backward Compatible with XC4000 Devices•Development System runs on most common computer platforms-Interfaces to popular design environments-Fully automatic mapping, placement and routing -Interactive design editor for design optimizationLow-Voltage Versions Available•Low-Voltage Devices Function at 3.0 - 3.6 Volts•XC4000XL:High Performance Low-Voltage Versions of XC4000EX devicesAdditional XC4000X Series Features•High Performance — 3.3 V XC4000XL•High Capacity — Over 180,000 Usable Gates • 5 V tolerant I/Os on XC4000XL•0.35µm SRAM process for XC4000XL •Additional Routing Over XC4000E-almost twice the routing capacity for high-density designs•Buffered Interconnect for Maximum Speed Blocks•Improved VersaRing TM I/O Interconnect for Better Fixed Pinout Flexibility•12 mA Sink Current Per XC4000X Output •Flexible New High-Speed Clock Network-Eight additional Early Buffers for shorter clock delays -Virtually unlimited number of clock signals•Optional Multiplexer or 2-input Function Generator on Device Outputs•Four Additional Address Bits in Master Parallel Configuration Mode IntroductionXC4000Series high-performance,high-capacity Field Pro-grammable Gate Arrays (FPGAs)provide the benefits of custom CMOS VLSI,while avoiding the initial cost,long development cycle,and inherent risk of a conventional masked gate array.The result of thirteen years of FPGA design experience and feedback from thousands of customers,these FPGAs com-bine architectural versatility,on-chip Select-RAM memory with edge-triggered and dual-port modes,increased speed,abundant routing resources,and new,sophisticated software to achieve fully automated implementation of complex, high-density, high-performance designs.The XC4000E and XC4000X Series currently have 20members, as shown in T able 1.May 14, 1999 (Version 1.6)00*Product Specification找FPGA ,上赛灵思半导体(深圳)有限公司Table 1: XC4000E and XC4000X Series Field Programmable Gate ArraysDeviceLogic Cells Max Logic Gates (No RAM)Max.RAM Bits (No Logic)TypicalGate Range (Logic and RAM)*CLB Matrix Total CLBs Number of Flip-Flops er I/OXC4002XL 1521,6002,0481,000 - 3,0008 x 86425664XC4003E 2383,0003,2002,000 - 5,00010 x 1010036080XC4005E/XL 4665,0006,2723,000 - 9,00014 x 14196616112XC4006E 6086,0008,1924,000 - 12,00016 x 16256768128XC4008E 7708,00010,3686,000 - 15,00018 x 183********XC4010E/XL 95010,00012,8007,000 - 20,00020 x 204001,120160XC4013E/XL 136813,00018,43210,000 - 30,00024 x 245761,536192XC4020E/XL 186220,00025,08813,000 - 40,00028 x 287842,016224XC4025E243225,00032,76815,000 - 45,00032 x 321,0242,560256XC4028EX/XL 243228,00032,76818,000 - 50,00032 x 321,0242,560256XC4036EX/XL 307836,00041,47222,000 - 65,00036 x 361,2963,168288XC4044XL 380044,00051,20027,000 - 80,00040 x 401,6003,840320XC4052XL 459852,00061,95233,000 - 100,00044 x 441,9364,576352XC4062XL 547262,00073,72840,000 - 130,00048 x 482,3045,376384XC4085XL744885,000100,35255,000 - 180,00056 x 563,1367,168448XC4000XL 5-Volt Tolerant I/OsThe I/Os on the XC4000XL are fully5-volt tolerant even though the V CC is3.3volts.This allows5V signals to directly connect to the XC4000XL inputs without damage, as shown in Table8.In addition,the3.3volt V CC can be applied before or after5volt signals are applied to the I/Os. This makes the XC4000XL immune to power supply sequencing problems.Registered InputsThe I1and I2signals that exit the block can each carry either the direct or registered input signal.The input and output storage elements in each IOB have a common clock enable input,which,through configuration, can be activated individually for the input or outputflip-flop, or both.This clock enable operates exactly like the EC pin on the XC4000Series CLB.It cannot be inverted within the IOB.The storage element behavior is shown in Table9.Table 9: Input Register Functionality(active rising edge is shown)Optional Delay Guarantees Zero Hold TimeThe data input to the register can optionally be delayed by several nanoseconds.With the delay enabled,the setup time of the inputflip-flop is increased so that normal clock routing does not result in a positive hold-time requirement.A positive hold time requirement can lead to unreliable, temperature- or processing-dependent operation.The inputflip-flop setup time is defined between the data measured at the device I/O pin and the clock input at the IOB(not at the clock pin).Any routing delay from the device clock pin to the clock input of the IOB must,therefore,be subtracted from this setup time to arrive at the real setup time requirement relative to the device pins.A short speci-fied setup time might,therefore,result in a negative setup time at the device pins,i.e.,a positive hold-time require-ment.When a delay is inserted on the data line,more clock delay can be tolerated without causing a positive hold-time requirement.Sufficient delay eliminates the possibility of a data hold-time requirement at the external pin.The maxi-mum delay is therefore inserted as the default.The XC4000E IOB has a one-tap delay element:either the delay is inserted(default),or it is not.The delay guarantees a zero hold time with respect to clocks routed through any of the XC4000E global clock buffers.(See“Global Nets and Buffers(XC4000E only)”on page35for a description of the global clock buffers in the XC4000E.)For a shorter input register setup time,with non-zero hold,attach a NODELAY attribute or property to the flip-flop.The XC4000X IOB has a two-tap delay element,with choices of a full delay,a partial delay,or no delay.The attributes or properties used to select the desired delay are shown in T able10.The choices are no added attribute, MEDDELAY,and NODELAY.The default setting,with no added attribute,ensures no hold time with respect to any of the XC4000X clock buffers,including the Global Low-Skew buffers.MEDDELAY ensures no hold time with respect to the Global Early buffers.Inputs with NODELAY may have a positive hold time with respect to all clock buffers.For a description of each of these buffers,see“Global Nets and Buffers (XC4000X only)” on page37.Table 10: XC4000X IOB Input Delay ElementTable 8: Supported Sources for XC4000 Series Device InputsSource XC4000E/EXSeries InputsXC4000XLSeries Inputs 5 V,TTL5 V,CMOS3.3 VCMOSAny device, Vcc = 3.3 V, CMOS outputs √Unreli-ableData√XC4000Series,Vcc=5V,TTL outputs√√Any device, Vcc = 5 V,TTL outputs (Voh≤ 3.7 V)√√Any device, Vcc = 5 V,CMOS outputs√√√Mode ClockClockEnableD QPower-Up orGSRX X X SR Flip-Flop__/1*D D0X X Q Latch 11*X Q01*D D Both X0X Q Legend:X __/ SR 0* 1*Don’t careRising edgeSet or Reset value. Reset is default.Input is Low or unconnected (default value)Input is High or unconnected (default value)Value When to Usefull delay(default, noattribute added)Zero Hold with respect to GlobalLow-Skew Buffer,Global Early BufferMEDDELAY Zero Hold with respect to Global EarlyBufferNODELAY Short Setup, positive Hold timeXC4000E and XC4000X Series Field Programmable Gate Arrays。

《逻辑器件FPGA》课件

块RAM

块RAM用于存储大规模的数据,提供高密度的 存储容量。

FPGA的输入输出

FPGA的输入输出包括通用I/O接口、高速串行接口和专有外设接口等,用于与外部设备进行数据交互。

FPGA的时序设计

时序设计是指在FPGA设计中对数据和信号的传输时序进行控制和优化,以满足设计要求和时钟约束。

FPGA的时序分析

FPGA的性能指标

1 逻辑门数目

FPGA的逻辑门数目决定了其逻辑资源的容量和处理能力。

2 时钟速度

FPGA的时钟速度越高,它可以处理的操作越快。

3 资源利用率

资源利用率是指FPGA中逻辑资源、内存单元和硬IP的使用效率。

FPGA的逻辑单元

FPGA的逻辑单元(Logic Element)包括查找表、触发器和多路选择器等, 用于实现逻辑功能和存储数据。

时序分析用于评估FPGA设计在实际运行中的时序性能,避免出现时序冲突和 时序失效。

FPGA编程语言

1 硬件描述语言

硬件描述语言(HDL)如VHDL和Verilog,用于描述FPGA的逻辑和功能。

2 高级语言

高级编程语言如C、C++和Python,用于开发FPGA的控制和数据处理部分。

3 编程环境

FPGA编程环境如Quartus和Vivado,提供了开发、仿真和调试FPGA设计所需的工具。

FPGA路由的实现

1

全局路由

全局路由用于将不同区块之间的信号连接起来,实现跨区块的通信。

2

局部路由

局部路由用于连接同一区块内部的信号,实现区块内部的信号传输。

3

时序约束

时序约束用于指定FPGA设计中不同信号的时序关系,以确保设计的正确运行。

基于FPGA的视频图像处理器[发明专利]

![基于FPGA的视频图像处理器[发明专利]](https://img.taocdn.com/s3/m/ce2908ce647d27284a73518f.png)

专利名称:基于FPGA的视频图像处理器专利类型:发明专利

发明人:崔宝英,谢长虹,刘晓军

申请号:CN200610129493.4

申请日:20061122

公开号:CN1964465A

公开日:

20070516

专利内容由知识产权出版社提供

摘要:本发明提供一种基于FPGA的视频图像处理器,该装置包括有均衡器模块、解串器模块、驱动器模块、串码器模块、时钟模块以及FPGA控制处理器;所述均衡器模块接收HD/SD格式视频信号,并对接收的视频信号进行补偿,补偿后的视频信号送入解串器模块实现串行数据到并行数据的转换,转换后的10bit/20bit并行数据经FPGA控制处理器处理后,输入到串码器模块,进行并行数据到串行数据的转换,并经驱动器模块传输到外部设备,时钟模块为解串器模块和串码器模块提供

1.485GHz的时钟信号。

有益效果是该系统能在实时采集处理的HD/SD格式视频信号,功能强大且操作简单,并且容易处理,可根据不同需求订制不同IP核,硬件易于升级,以满足未来对各种新增功能的需求,集成度高,性能稳定,成本低廉,性价比极高。

申请人:天津亚威达电子有限公司

地址:300384 天津市华苑产业区鑫茂科技园E座C2单元3层

国籍:CN

代理机构:天津才智专利商标代理有限公司

代理人:吕志英

更多信息请下载全文后查看。

赛灵思芯片应用场景

赛灵思芯片应用场景

赛灵思(Xilinx)芯片是一种可编程逻辑设备(FPGA),广

泛应用于各种领域。

以下是赛灵思芯片的几个常见应用场景:

1. 通信与网络:赛灵思芯片可以被用来实现高速数据传输、协议转换、网络交换和路由等功能,适用于通信设备、网络设备以及数据中心。

2. 图像与视频处理:赛灵思芯片的高性能计算能力和并行处理架构,使其成为处理高分辨率图像和视频的理想选择,例如视频编解码、图像处理、计算机视觉等。

3. 人工智能与深度学习:赛灵思芯片的高计算密度和灵活配置能力,适用于大规模并行计算,因此被广泛用于人工智能和深度学习领域,例如神经网络加速、模式识别和自动驾驶等。

4. 工业自动化与控制:赛灵思芯片可以实现基于模型的设计和控制方法,用于工业自动化和控制系统中,例如工厂自动化、机器人控制、智能传感器等。

5. 高性能计算与科学研究:由于赛灵思芯片的可编程性和高计算性能,它被用于高性能计算领域,例如数值模拟、科学计算、天气预报、基因组学研究等。

6. 航空航天与国防:赛灵思芯片的可编程性和高可靠性使其适用于航空航天和国防领域,例如雷达信号处理、导航系统、无人机控制等。

总之,赛灵思芯片的灵活性和可编程性使其在各种应用场景下都具备强大的计算和处理能力,满足不同行业的需求。

fpga在通信领域的作用

fpga在通信领域的作用FPGA在通信领域的作用随着信息技术的快速发展,通信领域对于高性能和高速度的需求越来越迫切。

而在满足这些需求的技术中,Field-Programmable Gate Array(FPGA)在通信领域起到了重要的作用。

FPGA是一种可编程逻辑器件,它可以根据需要进行自定义配置,以实现特定的功能和任务。

在通信领域中,FPGA具有以下几个方面的作用。

FPGA在通信领域中的一大作用是实现高速数据传输。

通信系统中需要处理大量的数据,而FPGA的并行处理能力使得它成为高速数据传输的理想选择。

通过在FPGA中实现并行的数据处理算法,可以大大提高数据的传输速度。

此外,FPGA还可以通过硬件加速技术,进一步提升数据的处理速度。

FPGA在通信领域中还可以实现协议转换和接口适配。

在通信系统中,不同设备和网络往往使用不同的通信协议和接口标准。

而FPGA具有灵活的可编程性,可以根据需要对不同的协议和接口进行转换和适配。

通过在FPGA中实现协议转换和接口适配的功能,可以实现不同设备和网络之间的互联互通,提高通信系统的兼容性和可扩展性。

FPGA还可以在通信领域中实现信号处理和算法加速。

在通信系统中,信号处理是非常重要的一环。

FPGA具有强大的计算和信号处理能力,可以通过在FPGA中实现各种信号处理算法,对通信信号进行实时处理和优化。

同时,FPGA还可以通过硬件加速技术,提高算法的执行速度,进一步提升系统的性能和效率。

FPGA还可以在通信领域中实现安全加密和解密功能。

在现代通信系统中,安全性是至关重要的。

FPGA具有可编程性和灵活性,可以在其内部实现各种加密和解密算法,对通信数据进行保护和安全传输。

通过在FPGA中实现安全加密和解密功能,可以有效防止通信数据的泄露和篡改,保障通信系统的安全性和可靠性。

FPGA还可以在通信领域中实现自适应性和动态重构。

通信系统中的环境和需求往往是多变的,而FPGA具有可编程性和可重构性,可以根据需要进行动态配置和重构。

fpga应用案例

fpga应用案例

1. 数字信号处理(DSP):FPGA是实现数字信号处理算法的

理想平台。

例如,FPGA可以用于音频处理、图像处理和视频

处理等领域。

2. 高性能计算(HPC):FPGA可以在并行计算环境中使用,

用于加速科学计算和数值模拟等计算密集型任务。

3. 网络加速:FPGA可以用于网络加速,例如协议转换、加密

解密、负载均衡等。

4. 通信系统:FPGA可以用于实现各种通信标准和协议,例如LTE、Wifi、4G等。

5. 数字信号实时处理:FPGA可以用于实时处理音视频信号,

例如音视频编解码、拼接、切换等。

6. 控制器/接口芯片:FPGA可以用于实现各种接口芯片,例

如USB、以太网、PCI、SATA等。

7. 硬件加速器:FPGA可以作为硬件加速器使用,例如加速机

器学习算法、加速数据库查询等。

8. 自动驾驶:FPGA可以用于自动驾驶系统中,例如用于图像

处理、传感器数据处理、车辆控制等。

9. 无人机:FPGA可以用于无人机系统中,例如用于图像处理、

传感器数据处理、控制系统等。

10. 医疗设备:FPGA可以用于医疗设备中,例如用于医学成像、医学数据处理、生命支持系统等。

FPGA可编程逻辑器件芯片XCS40XL-4BG256C中文规格书

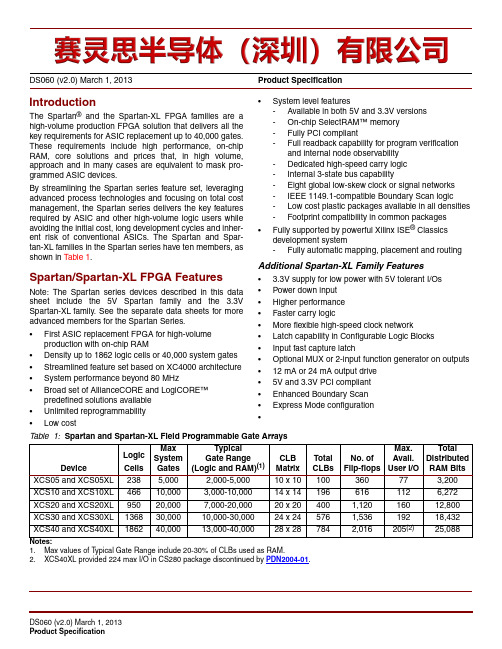

IntroductionThe Spartan® and the Spartan-XL FPGA families are a high-volume production FPGA solution that delivers all the key requirements for ASIC replacement up to 40,000 gates. These requirements include high performance, on-chip RAM, core solutions and prices that, in high volume, approach and in many cases are equivalent to mask pro-grammed ASIC devices.By streamlining the Spartan series feature set, leveraging advanced process technologies and focusing on total cost management, the Spartan series delivers the key features required by ASIC and other high-volume logic users while avoiding the initial cost, long development cycles and inher-ent risk of conventional ASICs. The Spartan and Spar-tan-XL families in the Spartan series have ten members, as shown in Table1.Spartan/Spartan-XL FPGA Features Note: The Spartan series devices described in this data sheet include the 5V Spartan family and the 3.3V Spartan-XL family. See the separate data sheets for more advanced members for the Spartan Series.•First ASIC replacement FPGA for high-volume production with on-chip RAM•Density up to 1862 logic cells or 40,000 system gates •Streamlined feature set based on XC4000 architecture •System performance beyond 80MHz•Broad set of AllianceCORE and LogiCORE™predefined solutions available•Unlimited reprogrammability•Low cost •System level features-Available in both 5V and 3.3V versions-On-chip SelectRAM™ memory-Fully PCI compliant-Full readback capability for program verification and internal node observability-Dedicated high-speed carry logic-Internal 3-state bus capability-Eight global low-skew clock or signal networks-IEEE 1149.1-compatible Boundary Scan logic-Low cost plastic packages available in all densities -Footprint compatibility in common packages •Fully supported by powerful Xilinx ISE® Classics development system-Fully automatic mapping, placement and routing Additional Spartan-XL Family Features• 3.3V supply for low power with 5V tolerant I/Os •Power down input•Higher performance•Faster carry logic•More flexible high-speed clock network•Latch capability in Configurable Logic Blocks•Input fast capture latch•Optional MUX or 2-input function generator on outputs •12 mA or 24 mA output drive•5V and 3.3V PCI compliant•Enhanced Boundary Scan•Express Mode configuration•DS060 (v2.0) March 1, 2013Product Specification Table 1: Spartan and Spartan-XL Field Programmable Gate ArraysDevice LogicCellsMaxSystemGatesTypicalGate Range(Logic and RAM)(1)CLBMatrixTotalCLBsNo. ofFlip-flopsMax.Avail.User I/OTotalDistributedRAM BitsXCS05 and XCS05XL2385,0002,000-5,00010 x 10100360773,200 XCS10 and XCS10XL46610,0003,000-10,00014 x 141966161126,272 XCS20 and XCS20XL95020,0007,000-20,00020 x 204001,12016012,800 XCS30 and XCS30XL136830,00010,000-30,00024 x 245761,53619218,432 XCS40 and XCS40XL186240,00013,000-40,00028 x 287842,016205(2)25,088 Notes:1.Max values of T ypical Gate Range include 20-30% of CLBs used as RAM.2.XCS40XL provided 224 max I/O in CS280 package discontinued by PDN2004-01.Spartan and Spartan-XL FPGA Families Data SheetThe register choice is made by placing the appropriate library symbol. For example, IFD is the basic input flip-flop (rising edge triggered), and ILD is the basic input latch (transparent-High). Variations with inverted clocks are also available. The clock signal inverter is also shown in Figure5 on the CK line.The Spartan family IOB data input path has a one-tap delay element: either the delay is inserted (default), or it is not. The Spartan-XL family IOB data input path has a two-tap delay element, with choices of a full delay, a partial delay, or no delay. The added delay guarantees a zero hold time with respect to clocks routed through the global clock buffers. (See Global Nets and Buffers, page12 for a description of the global clock buffers in the Spartan/XL families.) For a shorter input register setup time, with positive hold-time, attach a NODELAY attribute or property to the flip-flop.The output of the input register goes to the routing channels (via I1 and I2 in Figure6). The I1 and I2 signals that exit the IOB can each carry either the direct or registered input signal. The 5V Spartan family input buffers can be globally config-ured for either TTL (1.2V) or CMOS (VCC/2) thresholds,using an option in the bitstream generation software. The Spartan family output levels are also configurable; the two global adjustments of input threshold and output level are independent. The inputs of Spartan devices can be driven by the outputs of any 3.3V device, if the Spartan family inputs are in TTL mode. Input and output thresholds are TTL on all configuration pins until the configuration has been loaded into the device and specifies how they are to be used. Spartan-XL family inputs are TTL compatible and 3.3V CMOS compatible.Supported sources for Spartan/XL device inputs are shown in Table4.Spartan-XL family I/Os are fully 5V tolerant even though the V CC is 3.3V. This allows 5V signals to directly connect to the Spartan-XL family inputs without damage, as shown in Table4. In addition, the 3.3V V CC can be applied before or after 5V signals are applied to the I/Os. This makes the Spartan-XL devices immune to power supply sequencing problems.Figure 6: Simplified Spartan/XL IOB Block Diagram质量等级领域:宇航级IC、特军级IC、超军级IC、普军级IC、禁运IC、工业级IC,军级二三极管,功率管等;应用领域:航空航天、船舶、汽车电子、军用计算机、铁路、医疗电子、通信网络、电力工业以及大型工业设备祝您:工作顺利,生活愉快!以赛灵思半导体(深圳)有限公司提供的参数为例,以下为XCS40XL-4BG256C的详细参数,仅供参考。

FPGA的几种热门应用

FPGA的几种热门应用

没有一种器件可以满意全人类的众多需求,因此不用担忧FPGA没有用武之地。

必定是一系列产品的组合。

下面主要介绍一下FPGA可以作为现今热门场景的几种应用。

(1)网络存储产品,特殊是现在的NAS,或者SAN设备上,其存储的时间、接口、平安性等都要求较高,而FPGA无论处理性能还是扩展接口的力量都使其在这一领域大有作为。

现在高端FPGA单片就可以扩展32个或者更多4G或者8G的FC接口。

并且其协议处理相对的固定,也使FPGA在这一领域有大量的可能应用。

(2)高速网络设备,现在高速网络设备10G、40/100G以太网设备领域,同样FPGA也是关键的处理部件。

特殊是IPv6的商用化及大数据对于基础设施的高要求,都使这一领域的处理应用会渐渐广泛,这一领域通常是高速网络处理器(NP)+FPGA的典型架构。

(3)4G等通信设备,对于新一代通信基站的信号处理,FPGA+DSP 阵列的架构就是绝配。

特殊是在专用处理芯片面世之前,这样的架构可以保证新一代通信基础设施的快速研发和部署。

没有完善的架构,只有合适的组合,各种芯片和架构都是为应用服务,相互的渗透是趋势,也是必定。

FPGA相对处理器的可编程领域,仍旧属于小众(虽然人数也不少)。

但是正像一则笑话所说:大腿虽然比根命根子粗,但决没有命子重要。

这算开个玩笑。

FPGA的实现为以后的芯片化留下了很多可能和想象空间,从而在应用大量爆

发时通过芯片化来大幅降低成本,这这也正是其他可编程器件所不能比拟的。

fpga技术的作用与意义

fpga技术的作用与意义

FPGA技术(可编程逻辑门阵列)已经成为数字电路设计领域中不可或缺的一部分。

它是一种基于可编程门阵列的可编程器件,允许用户在设计过程中自定义逻辑电路,并在电路运行时进行修改。

由于FPGA具有高度灵活性和可重构性,它已成为许多应用程序的首选。

FPGA技术的作用和意义在于,它可以提供一种高效的可编程逻辑解决方案,使硬件设计师可以更快地开发出更复杂的数字电路。

FPGA技术还可以用来加速计算任务,例如在图像处理、信号处理、加密和解密等方面。

FPGA技术还具有低功耗的优点,这使得它成为移动设备和嵌入式系统的理想选项。

与传统的ASIC(应用特定集成电路)相比,FPGA 具有更快的开发周期和更小的开发成本,因为它们不需要进行复杂的掩膜制造过程。

随着技术的不断进步,FPGA技术的应用领域也在不断扩展。

例如,在人工智能和机器学习领域,FPGA技术已成为加速器的选择,可以加快神经网络和深度学习的训练速度。

总之,FPGA技术在数字电路设计和嵌入式系统中发挥着重要的作用,具有高度灵活性、可重构性、低功耗和快速开发的优点,有望在更多应用场景中得到广泛应用。

- 1 -。

FPGA可编程逻辑器件芯片XC4036XLA-09HQ240I中文规格书

PDN2004-21 (v1.1) November 15, 2004 Product Discontinuation NoticeOverviewXilinx is discontinuing certain low-volume device package-pin combinations of the XC4000E TM, XC4000XL TM, and XC4000XLA TM product families. This applies to commercial and industrial (C-grade and I-grade) products only. Military products are not affected.DescriptionThese device package combinations have declined in customer usage to the point where continued manufacturing is becoming no longer economical. Please note that a Pb-free version will not be provided for discontinued part numbers.Direct replacement devices are listed in the tables below. Although some discontinued part numbers do not have direct replacements, there are indirect device/package-pin combinations available as alternatives. Please contact your Xilinx Sales Representative for help with replacement devices.Products AffectedRefer to the tables below for the discontinued part numbers.Key DatesFinal orders are accepted until August 23, 2005Final deliveries must occur on or before February 23, 2006.XC4000XL Discontinuation SummaryFour packages and three devices in the XC4000XL family are being removed entirely.•Packages: HQ304, HQ160, HT176, and PC84•Devices: XC4036XL, XC4052XL, and XC4085XLIn addition to the above packages and devices, the following device-package combinations are being discontinued:•XC4005XL-PQ100•XC4010XL-PQ160•XC4020XL-PQ240•XC4028XL-BG256Not all recommended replacements identified in the far right column are drop-in replacements for the discontinued part numbers. In these cases, a redesign of the customer’s board may be required. Customers may need to have the original design tools in order to support the re-design. Please note, the XC4000XLA family is a drop-in replacement where available for the XC4000XL family. Product with drop-in capability is identified with an *asterisk in the recommended replacement column. Because of the maturity of the product,recommended replacements provide only a short term solution and there is no commitment for end of life expectancy. For long term solutions, please consider re-designing into the Spartan product family.XC4000XLA Discontinuation SummaryOne package and two devices in the XC4000XLA family are being removed entirely.•Package: PQ160•Devices: XC4044XLA and XC4062XLAIn addition to the above devices and package, the following device-package combinations are being discontinued:•XC4028XLA-HQ208•XC4028XLA-HQ160•XC4036XLA-HQ160•XC4085XLA-HQ304Not all recommended replacements identified in the far right column are drop-in replacements for the discontinued part numbers. In these cases, a redesign of the customer’s board may be required. Customers may need to have the original design tools in order to support the re-design. Because of the maturity of the product, recommended replacements provide only a short term solution and there is no commitment for end of life expectancy. For long term solutions, please consider re-designing into the Spartan product family.XC4000XLA Family Member Discontinued Part Number Recommended ReplacementXC4013XLA-PQ160XC4013XLA-07PQ160CXC4013XLA-08PQ160CXC4013XLA-09PQ160CXC4013XLA-08PQ160IXC4013XLA-09PQ160IXC4020XLA-PQ160XC4020XLA-07PQ160CXC4020XLA-08PQ160CXC4020XLA-09PQ160CXC4020XLA-08PQ160IXC4020XLA-09PQ160IXC4028XLA-HQ160XC4028XLA-07HQ160C XC4052XLA-07HQ160CXC4052XLA-08HQ160CXC4028XLA-08HQ160CXC4028XLA-09HQ160CXC4052XLA-09HQ160CXC4028XLA-08HQ160I XC4052XLA-08HQ160IXC4052XLA-09HQ160IXC4028XLA-09HQ160I XC4028XLA-HQ208XC4028XLA-07HQ208C XC4036XLA-07HQ208CXC4036XLA-08HQ208CXC4028XLA-08HQ208CXC4028XLA-09HQ208CXC4036XLA-09HQ208CXC4036XLA-08HQ208IXC4028XLA-08HQ208IXC4036XLA-09HQ208IXC4028XLA-09HQ208I XC4036XLA-HQ160XC4036XLA-07HQ160C XC4052XLA-07HQ160CXC4052XLA-08HQ160CXC4036XLA-08HQ160CXC4052XLA-09HQ160CXC4036XLA-09HQ160CXC4052XLA-08HQ160IXC4036XLA-08HQ160IXC4052XLA-09HQ160IXC4036XLA-09HQ160I XC4044XLA-BG352XC4044XLA-07BG352C XC4052XLA-07BG352CXC4052XLA-08BG352CXC4044XLA-08BG352CXC4000XLA Family Member Discontinued Part Number Recommended ReplacementXC4085XLA-09HQ160CXC4062XLA-09HQ160CXC4085XLA-08HQ160IXC4062XLA-08HQ160IXC4085XLA-09HQ160IXC4062XLA-09HQ160IXC4062XLA-HQ208XC4062XLA-07HQ208C XC4085XLA-07HQ208CXC4085XLA-08HQ208CXC4062XLA-08HQ208CXC4085XLA-09HQ208CXC4062XLA-09HQ208CXC4085XLA-08HQ208IXC4062XLA-08HQ208IXC4085XLA-09HQ208IXC4062XLA-09HQ208IXC4062XLA-HQ240XC4062XLA-07HQ240C XC4085XLA-07HQ240CXC4085XLA-08HQ240CXC4062XLA-08HQ240CXC4085XLA-09HQ240CXC4062XLA-09HQ240CXC4062XLA-08HQ240IXC4085XLA-08HQ240IXC4085XLA-09HQ240IXC4062XLA-09HQ240IXC4062XLA-HQ304XC4062XLA-07HQ304CXC4062XLA-08HQ304CXC4062XLA-09HQ304CXC4062XLA-08HQ304IXC4062XLA-09HQ304IXC4085XLA-HQ304XC4085XLA-07HQ304C。

fpga原理及案例分享

fpga原理及案例分享FPGA是可编程逻辑器件,全称为Field-Programmable Gate Array,它是一种集成电路芯片,可以通过编程来实现特定的功能。

FPGA的原理是基于可编程的逻辑单元和可编程的连接资源,通过编程来配置这些逻辑单元和连接资源,从而实现特定的逻辑功能。

FPGA的原理可以简单理解为它包含了大量的可编程逻辑单元和可编程连接资源,用户可以根据自己的需求编写代码,将特定的逻辑功能映射到FPGA芯片上,实现定制化的硬件功能。

与传统的固定功能集成电路相比,FPGA具有灵活性高、可重构性强的特点。

在实际应用中,FPGA被广泛用于数字信号处理、通信、图像处理、嵌入式系统等领域。

例如,FPGA可以用于实现数字滤波器、通信协议处理、图像处理算法加速等功能。

另外,FPGA还常用于快速原型设计和验证,因为它可以在短时间内重新编程实现不同的功能,从而加快产品开发的速度。

一个经典的FPGA案例是Xilinx的Zynq系列芯片,它集成了ARM处理器和FPGA芯片,可以实现高性能的嵌入式系统设计。

Zynq芯片可以用于无人机控制、工业自动化、医疗设备等领域,通过FPGA部分实现实时信号处理、高速数据传输等功能,而通过ARM处理器部分实现运行实时操作系统、控制外围设备等任务。

另一个案例是Altera(现在被Intel收购)的Cyclone系列FPGA,它在通信领域有着广泛的应用,可以用于实现各种通信协议的处理、信号处理算法的加速等功能。

Cyclone系列FPGA还常用于工业控制、汽车电子、网络设备等领域,因为它具有低功耗、高集成度、灵活性强的特点。

总的来说,FPGA作为一种可编程逻辑器件,具有灵活性高、可重构性强的特点,在数字信号处理、通信、图像处理、嵌入式系统等领域有着广泛的应用。

通过编程实现特定的硬件功能,FPGA可以加速算法运行、提高系统性能,并且在产品开发过程中起到快速原型设计和验证的作用。

FPGA在OSD中的应用

图1为OSD系 统 框 图 , Camera Link 相 机 获 取 的 数字视频信号, DS90C288A将串行数 字信号解成 并 行 视 频 信 号 以 后 , 通 过 同 步FIFO缓 存 , 经 过DM642

2006 年3 月14 日 收 到

的EMIF口CE1空间进入DM642做相应的 预处理, 处 理 后 数 据 通 过 DM642 的 视 频 口 输 出 进 入 OSD FPGA, 经 过 叠 加 后 的 视 频 数 据 在 视 频 编 码 器 SAA7105 中 编 码 以 后 输 出 到 监 视 器 显 示 结 果 。 DM642可 以 通 过 对 外 部 同 步 或 者 异 步 存 储 器 的 访 问 实 现 对FPGA内 部 寄 存 器 读 写 控 制 。FPGA的 中 断 通 过DSP的 外 部 中 断EXINT6和EXINT7向DSP发 出 中断请求。FPGA由专用的控制芯片来配置, 调试通 过JTAG口调试。

逻辑控制模块控制OSD拆包 模块、DMA事件发 生 器 和OSD混 和 器 之 间 的 状 态 。 它 通 过 监 控 视 频 控 制 信 号 VSYNG和 AVID来 控 制 不 同 的 模 块 。 如 果 OSD FIFO非 空, 同时扫描 也进入了指 定窗口, 控 制 逻辑模块使能对FIFO的读取, 拆包OSD数据, 和OSD 数据和视频数据的混合。

( College of Resource and Environmental Science1 School of Computer & Information Engineering2, Hunan Agricultural University, Changsha 410128)

[ Abstr act] Based on a detailed study of background, theory and methodology of early - warning, the introduction of research history, current situation and method is set out. This essay makes an illustration in the full range of the importance and process of regional development quality monitoring and early- warning, designs evaluating indexes. It aims at setting a frame of Monitoring and Early- warning system of sustainable development quality and provides a new study thinking. [ Key words] region development quality monitoring and early- warning

FPGA可编程逻辑器件芯片XC4VFX140-11FF1517I中文规格书

XC5VTX150T: GTX_DUAL_X1Y3

AF4 AF3

AH1 AG1

AE1 AF1

AJ2 AH2

AD2 AE2

MGTREFCLKP_118 MGTREFCLKN_118

MGTRXP1_118 MGTRXN1_118

MGTRXP0_118 MGTRXN0_118

MGTTXP1_118 MGTTXN1_118

PMA_TX_CFG_0

PMA_RX_CFG_1

PMA_RX_CFG_0

PMA_COM_CFG

PMA_CDR_SCAN_1

PLL_TXDIVSEL_OUT_0 PLL_TXDIVSEL_OUT_1

PLL_LKDET_CFG PMA_CDR_SCAN_0

PLL_TDCC_CFG[2:0]

Table D-2: DRP Address by Attribute (Cont’d)

CHAN_BOND_SEQ_LEN_0 CHAN_BOND_SEQ_LEN_1

Integer

Defines the length in bytes of the channel bonding sequence that the transceiver matches to detect opportunities for channel bonding.

21

45<9> 0a<6> 5<8> 49<7> 6<8>

20

45<8> 0a<7> 4a<7> 49<6> 6<9>

19

45<7> 0a<8> 3a<6> 49<5> 6<10>

基于FPGA的多路数据采集模块硬件设计

基于FPGA的多路数据采集模块硬件设计

李鹏;马游春;李锦明

【期刊名称】《仪表技术与传感器》

【年(卷),期】2010(000)003

【摘要】为了实现对58路模拟信号进行不同频率的采集,设计了一种以现场可编程门阵列(FPGA)为核心的多路模拟信号采集模块.该模块采用FPGA芯片XC2S30作为系统的核心控制器件来实现对A/D转换器的控制、多路模拟开关的选通控制以及数据的编帧和并串转换等功能.该设计方案结构灵活、控制简单、可靠性高,并且通过试验已验证了其功能的正确性.

【总页数】3页(P80-82)

【作者】李鹏;马游春;李锦明

【作者单位】中北大学电子测试技术国家重点实验室,山西太原,030051;中北大学仪器科学与动态测试教育部重点实验室,山西太原,030051;中北大学电子测试技术国家重点实验室,山西太原,030051;中北大学仪器科学与动态测试教育部重点实验室,山西太原,030051;北京航空航天大学光电技术研究所,北京,100083;中北大学电子测试技术国家重点实验室,山西太原,030051;中北大学仪器科学与动态测试教育部重点实验室,山西太原,030051

【正文语种】中文

【中图分类】TN47

【相关文献】

1.基于单片机的多路温度控制器硬件设计 [J], 张迎雪;

2.基于FPGA的多功能数据采集模块设计 [J], 金刚;徐志跃;周强

3.基于MSP430AFE231系统数据采集模块的硬件设计 [J], 赵驭阳

4.基于DSP+FPGA结构的高速数据采集模块 [J], 王志刚;师奕兵

5.基于FPGA的实时图像数据采集模块设计 [J], 伍乾永;陈彬

因版权原因,仅展示原文概要,查看原文内容请购买。

FPGAs--支持DSP技术在实时视频处理中的应用

FPGAs--支持DSP技术在实时视频处理中的应用

David Nicklin

【期刊名称】《世界电子元器件》

【年(卷),期】2002(000)005

【摘要】@@ 实时视频处理对系统级性能提出了极高的要求,几乎最简单的功能也超出了单个通用DSP器件的处理能力.采用可编程逻辑器件进行设计使工程师可利用并行处理技术实现视频信号处理算法.

【总页数】2页(P41-42)

【作者】David Nicklin

【作者单位】Xilinx战略解决方案营销高级经理

【正文语种】中文

【中图分类】TN91

【相关文献】

1.实时操作系统DSP/BIOS在DSP开发中的应用 [J], 李进

2.集成DSP的视频处理卡在机器视觉中的应用 [J], 畅琮

3.DSPs实时视频处理中的Cache优化算法研究 [J], 唐文佳;朱光喜;王曜;刘瑜

4.基于DSP的实时视频处理系统及应用 [J], 杨东华;李久贤;谢树林

5.Blackfin DSP并行外围接口在红外视频处理通用模块中的应用研究 [J], 张智杰;郭晓东

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

-41-●新特器件应用FPG A器件XCS40X L及其在多画面处理器中的应用解放军广州通信学院黄再银FPGA Device XCS40X L and It’s A pp lication I n Picture Multi p lexerHuan g Z ai Y in摘要:FPG A器件XCS40X L是X ilinx公司推出的低价格、高性能现场可编程门阵列,文中详细讨论了XCS40X L中三大模块(C LB、IO B、布线通道)的结构和功能,同时给出了XCS40X L器件在多画面处理器中的应用情况。

关键词:现场可编程门阵列;逻辑模块;FPG A;XCS40X L分类号:T N79+.1文献标识码:B文章编号:1006-6977(2003)02-0041-04FPG A器件XCS40X L及其在多画面处理器中的应用1XCS40X L的主要特点现场可编程门阵列(F ield Pro g ramm able G ate Ar2 ra y简称FPG A)是80年代中期发展起来的可编程器件,与传统逻辑电路和门阵列(如PAL、G AL及CP LD 器件)相比,FPG A不受“与-或”阵列在结构上的限制以及触发器和I/O端在数量上的限制。

它可以通过器件内部的逻辑单元以及它们之间的连接来构成任何复杂的逻辑电路,因而更适合于实现多级逻辑功能之间,同时,该器件还具有更高的密度和更大的灵活性,因而是目前数字电路或系统的首选器件之一。

FPG A器件采用CM OS-SRAM工艺制作,电路结构为逻辑单元阵列形式,每个逻辑单元均可编程。

FPG A的逻辑功能是通过向内部静态存储器单元加载编程数据来实现的。

由于编程数据一般存储在器件内部的静态随机存储器中,因而在停电后,这些编程数据便会丢失,这就要求每次开始工作时都需要重新装载编程数据。

FPG A的这种结构允许无限次的编程。

XCS40X L是X ilinx公司推出的低价格、高性能的FPG A,其主要特点如下:●系统门数高达40000门,其逻辑单元数目达1862个,C LB矩阵数为784;●触发器个数为2016,可用的最大I/O口数目为224个,因此,系统资源极其丰富;●带有片上可编程分布式RAM,最多可编程的RAM Bit可达25088位;●具有分布式算术逻辑单元,可以支持分布式DSP运算;●支持Alliance C ord及系统集成;●工作电压为3.3V。

2XCS40X L的结构XCS40X L的结构如图1所示,由图可见,该器件主要由可编程逻辑模块(C onfi g urable Lo g ic Block) C LB、输入输出模块(In p ut/Out p ut Block)IO B、布线通道(R outin g Channel)等3个部分组成。

C LB是实现各种逻辑功能的基本单元,包括组合逻辑、时序逻辑、RAM及各种运算功能,XCS40X L一共包含有784个C LB,它们以28×28的阵列形式分布在其中。

IO B是芯片外部数据与内部数据进行交换的接口,通过编程可将I/O引脚设置成输入、输出或双向等不同的功能,通常IO B分布在芯片的四周。

C LB之间的空隙部分为布线通道,其作用是给C LB和IO B的输入输出提供互连路径。

每个模块的功能均可通过对内部SRAM的编程来确定,存储在SRAM中的编程数据可用于决定XCS40X L的功能。

下面具体介绍XCS40X L的C LB、IO B和布线通道三部分的结构和原理。

2.1C LB的结构XCS40X L的绝大多数逻辑功能均来通过C LB 可实现。

图2所示是XCS40X L器件的简化C LB方框图。

由图2可知,C LB主要由三个用来产生逻辑函数的查找表(Look-U p T able,简称LUT)、两个D触发器及两组数据选择器A和B组成,其中两个由16×1存储单元构成的查找表(F-LUT和G-LUT)可实现4变量的逻辑函数发生器,其输入分别为F1~F4和G1~G4,输出分别为F、G,其输出为4输-42-《国外电子元器件》2003年第2期2003年2月图1XCS40X L 的方框图入变量的任意组合逻辑函数。

而3输入变量的逻辑函数发生器(H -LUT )可产生3输入变量的任意组合逻辑函数,它的两个输入变量G 、F 受可编程数据选择器控制,并可由G-LUT 和F -LUT 输出或者直接由C LB 的外部输入。

H -LUT 的第三个输入始终来自C LB 的外部输入H1,由此可见,经过3个LUT 的两级组合,在H 端即可实现多达9个变量的任意组合逻辑函数。

每个C LB 包含两个存储逻辑函数发生器输出的D 触发器。

通过4选1数据选择器,触发器的输入既可选择F -LUT 或G-LUT 的输出,也可选择H -LUT 的输出,还可直接选择C LB 的外部输入DIN 。

这两个D 触发器可共用一个时钟信号CK 及使能信号EC ,它们的异步置位/复位信号也可以共用一个C LB 内部控制信号。

C LB 除了可以实现一般的组合逻辑功能和时序逻辑功能外,其F -LUT 和G-LUT 还可作为分布式RAM 使用,当它们作为RAM 使用时,可以有两种RAM 编程模式:单口RAM 或双口RAM 。

其中在单口模式下,一个C LB 可编程设定为16×1、(16×1)×2或32×2位RAM 阵列;而在双口模式下,一个C LB 只能设定为16×1的RAM 阵列,有关分布式RAM 的具体操作请参考有关文献1]。

2.2IO B 的结构原理IO B 是XCS40X L 外部封装引脚和内部逻辑间的接口电路,每个IO B 对应一个封装引脚,通过向IO B 有关的编程数据存储单元中写入不同的数据,即可将它们的引脚定义成输入、输出和双向功能。

IO B 的输入信号可编程设定为直接送往内部的布线通道(图中经过I1、I5)或者送往输入寄存器。

输入寄存器可编程设定为边沿触发器或锁存器;XCS40X L 可选择是否插入二个或一个延迟单位、或者不插入图2XCS40X L C LB 的简化逻辑图-43-FPG A 器件XCS40X L 及其在多画面处理器中的应用图4XCS40X L C LB 的布线通道和接口方框图图3XCS40X L I OB 的简化方框图延迟单位。

输入寄存器的输出可直接送往布线通道(图中通过I1和I2)。

当I/O 引脚用作输出时,内部逻辑信号由O 端输入IO B 模块,同时可编程设定为是否反相,然后再选择是直接送往三态缓冲器还是经过D 触发器寄存后再送往三态缓冲器,该三态输出缓冲器的使能控制信号T 也可以编程定义为高电平有效或低电平有效。

当T 有效时,输出信号经缓冲器输出到I/O 引脚。

其输入通路和输出通路中的两个D 触发器虽然共用一个时钟使能控制信号EC ,但它们有各自的时钟脉冲OK (输出时钟)和IK (输入时钟)。

可编程的上拉、下拉电阻可用来将没有用到的引脚接电源或接地以减少功耗和系统噪声,可编程的上拉电阻为P 沟道晶体管,它与VCC 相连;可编程的下拉电阻为N 沟道晶体管,它与地相连,阻值的范围为20kΩ~100k Ω。

XCS40X L 的IO B 的简化原理框图如图3所示。

2.3布线通道(R outin g channel )XCS40X L 中的所有内部布线通道均由金属线段组成,这些金属线段带有可编程的开关点及开关矩阵,并同时分布在C LB 的行列间隙上。

图4为XCS40X L 的C LB 的布线通道及接口方框图,图中的PSM (Pro g ramm able Sw itchin g M atrix )为可编程开关矩阵,小圆点为可编程开关点,可编程连线有单长线、双长线和长线之分。

单长线通过PSM 与其它单长线相连,每根双长线都从一个开关矩阵出发,绕过相邻的开关矩阵后进入下一个开关矩阵,双长线在电路中成对出现;长线不经过开关矩阵,其长度可穿越整个芯片。

由图4可看出,C LB 的输入、输出均匀地分布在四周,通过对可编程开关点的编程可以将它们连接到单长线、双长线或长线上。

单长线与C LB 输入、输出间有许多直接连接点,因此有很高的布线成功率,单长线提供了最好的互连灵活性和相邻模块的快速布线。

由于信号每经过一个开关矩阵都要产生一定的延时,所以单长线不适合长距离传输信号。

与单长线相比,双长线减少了经过矩阵开关的数量,它能有效地提供中等距离的信号通路,从而可提高系统的工作速度;而长线则通常用于高扇出和时间要求苛刻的信号网。

除此以外,XCS40X L 还有专用的全局网络及缓冲器,可用来分配全局时钟信号和长线驱动。

3XCS40X L 的编程实现原理所谓编程,就是将事先设计好的数据通过某种方式装入一片或多片XCS40X L 中,以确定XCS40X L 内部的C LB 和IO B 的功能以及布线通道的连接方式,数据的写入只在编程过程中完成。

在正常工作期间,存储单元只提供固定的控制信号,编程存储单元以阵列形式分布在XCS40X L 中。

每个C LB 有几百个编程数据位,每个编程数据位定义了一个静态存储单元的状态,而该存储单元可以控制一个逻辑函数查找表位、一个数据选择器输入或一个互连开关晶体管。

X ilinx 开发系统可以将逻辑设计转换成网络表文件,同时可以自动对逻辑电路进行分区、设置和布线,并以EPROM 格式产生编程数据,随后将数据存入EPROM 中。

-44-《国外电子元器件》2003年第2期2003年2月图6四画面处理器方框图图5主/从串模式编程电路图3.1XCS40X L 的编程模式3V 的XCS40X L 器件有如下三种编程模式:M1/M0=11:为从串模式;M1/M0=10:为主串模式;M1/M0=0X:为快速模式。

通常在编程开始前,芯片会自动检测M ODE 脚以确定编程模式。

而在编程结束后,这些引脚就没有用了。

当M ODE 脚为高电平时,为从串模式,这也是目前最常用的一种编程模式,实际上,此时M ODE 脚可悬空。

如果要选择主串模式,则M ODE/M0脚必须与地相连或通过1kΩ的下拉电阻接地。

3.2编辑数据的装入由于SRAM 内部的数据在掉电后会丢失,所以,基于SRAM 的XCS40X L 必须配置一个EPROM 芯片,以存放XCS40X L 的编程数据。

主串模式是利用XCS40X L 内部振荡器产生的编程时钟(CC L K)信号来驱动从(S lave )XCS40X L 器件和具有串行功能的PROM (SPROM ),CC L K 可选择1MH z (缺省状态)或8MH z 。

在CC L K 的上升沿,SPROM 内部地址计数器自动加1,直到将所有数据全部装载完毕。