高速串行总线技术发展与应用分析

串行通信及串行扩展技术

传感器数据采集

01

串行通信接口可以连接各种模拟或数字传感器,实现数据的实

时采集和传输。

数据处理与存储

02

通过串行通信将采集到的数据传输到上位机或数据中心,进行

进一步的处理、分析和存储。

系统监控与控制

03

串行通信可用于实现远程监控和控制,提高数据采集系统的灵

活性和可维护性。

在远程监控系统中的应用

01

特点

传输线少,成本低,适用于远距 离通信,但传送速度较慢。

串行通信协议

异步通信协议

以字符为单位进行传输,字符间通过 特定的起始位和停止位进行同步。

同步通信协议

以数据块为单位进行传输,通过同步 字符或同步信号实现收发双方的时钟 同步。

串行通信接口标准

RS-232C接口标准

定义了数据终端设备(DTE)和数据通信设备(DCE)之间的接口标准,采用 负逻辑电平,最大传输距离约15米。

串行扩展工作原理

01

数据传输

在串行通信中,数据以位为单位进行传输。发送端将数据按位依次发送

到传输线上,接收端按位接收并组合成完整的数据。数据传输过程中需

要遵循特定的通信协议和数据格式。

02

同步与异步通信

串行通信可分为同步通信和异步通信两种方式。同步通信需要发送端和

接收端保持严格的时钟同步,而异步通信则通过特定的起始位和停止位

无线化发展趋势

无线通信技术的普

及

随着无线通信技术的不断发展, 串行通信逐渐实现无线化,使得 设备间的通信更加灵活方便。

低功耗无线通信技

术

针对低功耗设备的需求,发展出 低功耗无线通信技术,延长设备 的续航时间。

无线通信安全性增

总线与总线标准

率的通信。SerDes技术将广泛应用于各种高速总线和接口协议中,推

动总线技术的发展。

03 总线的应用领域

工业控制领域

实时性要求高

安全可靠性

工业控制领域中,总线需要满足高实 时性要求,确保设备之间的快速通信 和精确控制。

工业控制领域对安全可靠性要求极高, 总线需要具备高度的稳定性和可靠性, 以避免因通信故障导致的生产事故。

灵活性高

总线结构允许节点在总线上任意接入 或断开,提高了系统的灵活性。

总线的缺点

带宽有限

总线的带宽有限,限制了数据 的传输速率。

竞争激烈

多个节点共享总线资源,导致 资源竞争激烈,影响系统性能 。

故障排除困难

一旦总线发生故障,故障排除 比较困难。

对线缆要求高

总线结构的线缆要求较高,需 要高质量的线缆以保证信号传

灵活性

通信领域中,总线需要具 备较好的灵活性,能够适 应不同传输介质和传输距 离的需求。

计算机硬件领域

高速数据传输

计算机硬件领域中,总线需要满 足高速数据传输的要求,确保

CPU、内存、硬盘等硬件设备之 间的快速信息交换。

兼容性

计算机硬件领域中,总线需要遵 循国际通用的标准协议,以确保

不同硬件设备之间的兼容性。

扩展性

计算机硬件技术不断发展,总线 需要具备良好的扩展性,以适应 新的硬件设备和更高的性能要求。

04 总线的优缺点分析

总线的优点

可靠性高

总线结构简单,减少了故障发生的可 能性,提高了系统的可靠性。

可扩展性强

总线采用分支结构,方便增加和减少 节点,具有良好的可扩展性。

成本低

总线结构减少了线缆的使用量,降低 了布线和维护成本。

单片机中的USB接口技术分析

单片机中的USB接口技术分析USB(Universal Serial Bus,通用串行总线)是一种常见的数据传输接口,广泛应用于各种设备和系统中,包括在单片机中。

本文将对单片机中的USB接口技术进行分析,探讨其原理、应用和发展趋势。

一、USB接口的原理USB接口是一种点对点数据传输接口,通过主机和从机之间的通信来实现数据传输。

在单片机中,主机通常是PC或其他嵌入式系统,而从机则是嵌入了USB控制器的单片机芯片。

USB接口使用了四根导线,包括一个用于数据传输的差分对、一个用于电源和一个用于地线。

USB接口采用了主从结构,主机发送控制命令给从机,并收集从机返回的数据。

主机和从机之间的通信是通过“令牌”、“数据”和“握手”包来实现的。

主机发送令牌包指定操作和从机地址,从机返回响应,并根据主机的要求发送数据包或握手包。

二、USB接口的应用单片机中的USB接口被广泛应用于各种领域,包括消费电子、通信、工业控制和医疗设备等。

以下是一些常见的应用场景:1. 外部存储器:通过USB接口连接外部存储设备(如闪存驱动器或硬盘驱动器)可以方便地进行数据存储和传输。

这在很多嵌入式系统中是一个常见的功能。

2. 通信设备:许多嵌入式系统需要与PC、手机或其他设备进行通信。

通过使用USB接口,可以实现快速、稳定的数据传输,用于例如串口通信和网络连接。

3. 人机界面:通过USB接口连接键盘、鼠标、摄像头或触摸屏等外部设备,可以实现人机交互。

这在智能手机、平板电脑和其他嵌入式系统中非常常见。

4. 工业控制:许多工业领域需要远程监控和控制设备。

通过使用USB接口,可以实现与嵌入式系统的连接,对设备进行监控和控制。

三、USB接口的发展趋势随着嵌入式系统的不断发展和进步,USB接口技术也在不断演进和改进。

以下是一些USB接口的发展趋势:1. USB 3.0和USB 3.1:USB 3.0和USB 3.1标准提供了更高的传输速度和更大的带宽,比之前的版本快得多。

SRIO与PCI Express的比较

图1 SRIO协议层级PCI Express协议有物理层、数据链路层、处理层等共三层。

如图2所示。

嵇康(1981-),男,江苏涟水人,本科,工程师。

研究方向:机载座舱显示技术。

林茂宽(1988-),男,湖北大冶人,本科,助理工程师。

研究方向:机载座舱显示技术。

李兵强(1981-),男,河北邢台人,硕士,工程师。

研究方向:机载座舱显示技术。

张杰(1984-),男,江苏淮安人,本科,高级工程师。

研究方向:机载座舱显示技术。

夏建平(1988-),男,江苏常州人,本科,助理工程师。

研究方向:机载座舱显示技术。

图2 PCI Express网络分层两者的第一层都为物理层,但其实质内容略有不同,SRIO串行物理层电器接口使用差分电流量控制基于802.3XAUI规范的驱动器,而PCI Express协议的电器接口采用高速的低压差分信号(LVDS)的驱动器和接收器。

两者的第二层名称不同,实质内容更是不一样,SRIO的传输层支持8bit或16bit器件ID,一个网络最多可容纳256或65 536个终端器件。

PCI Express的数据链路层,其功能设置图3 SRIO网络结构图从以上对比来看,注重网络结构多样性时,尽量选择,考虑到设备升级换代影响时,尽量选择PCI Express。

SRIO和PCI Express这两种最常用的总线形式的工作机制、特点、分层模型、拓扑结构等。

协议具有传输效率更高、允许更灵活的拓扑结构和多样的处理部件的特点,当考虑到高实时性、高可靠性时应优先选择。

PCI Express协议具有前后兼容性的特点,当考虑到大块数据传输、低成本设计、实时性较低以及系统网络简单时应优先选择。

参考文献[1]孟会,刘雪峰.PCI Express工程,2006(23):253-255.[2]Sam Fuller.SRIO嵌入式系统互联电子工业出版社,2004.图4 PCI Express网络结构图,B A r e z o o,A A b d u l l a h. Positional,Geometrical,and Thermal Errors Compensation by Tool Path Modification Using Three Methods of Regression,N euralNetworks,andFuzzy Logic[J].The International Journal of Advanced ManufacturingTechnology,2013:1635-1649.童恒超,等.数控机床热误差实时上海交通大学学报,2005,39(9):1389-1392.范嘉桢,等.基于FANUC oi系统外部坐标原点偏移功能的数控机床误差补偿研究造,2009,47(7):73-76.[12]W Wang,Y Zhang,JG Yang.Modeling of Compound Errors for CNC Machine Tools[J].Advanced Materials Research,2012:1796-1799.[13]G Cui,Y Lu,D Gao,etal.ANovel Error Compensation Implementing Strategy and Realizing on Siemens 840D CNC Systems[J].The International Journal of AdvancedManufacturing Technology,2012:595-608.。

pcie的detect信号电平标准

PCIE(Peripheral Component Interconnect Express)是一种用于连接外设的高速串行总线技术,它在计算机领域中扮演着至关重要的角色。

其中,PCIE的detect信号电平标准作为PCIE总线规范中的重要组成部分,其作用是确保正确的设备检测和初始化。

在本文中,我将围绕这一主题展开深入探讨。

1. PCIE总线简介PCIE总线是一种并行总线与串行总线相结合的高速总线标准,其优势在于高带宽、低延迟和热插拔功能。

它被广泛应用于图形卡、显卡、网卡等外设设备的连接和数据传输中。

PCIE总线规范中包含了一系列严格的信号电平标准,以确保各种设备在不同环境下能够正常工作。

2. PCIE的detect信号电平标准PCIE的detect信号电平标准是指在PCIE总线中用于设备检测和初始化的电平要求。

这些电平标准通常由PCIE规范中的工作组或标准化组织制定,以确保设备在不同环境下都能够正常工作。

在PCIE规范中,对detect信号的电平标准有着严格的要求,以确保设备能够在不同环境下稳定可靠地被检测和初始化。

3. detect信号的作用在PCIE总线中,detect信号通常用于设备的检测和初始化。

它在设备接入总线时起着至关重要的作用,通过检测detect信号的电平状态,总线控制器可以确保设备已正确连接并初始化。

detect信号的电平标准对设备的可靠性和稳定性有着直接影响。

4. 个人观点和理解作为一名经验丰富的文章写手,对PCIE的detect信号电平标准我有着深刻的理解和认识。

我认为,严格的电平标准可以确保设备在各种环境下能够正常工作,这对于PCIE总线的稳定性和可靠性至关重要。

在实际的PCIE设备设计和应用中,合理设计并符合电平标准的detect信号,可以有效降低设备出现问题的可能性,提高设备的稳定性和可靠性。

总结:通过本文的阐述,我们可以清晰地了解到PCIE的detect信号电平标准在PCIE总线中的重要性,以及其对设备的检测和初始化起到的关键作用。

(完整)现场总线技术的发展与应用

现场总线技术的发展与应用摘要:现场总线作为一种开放的、全数字化、双向、多站的通信系统,近年来得到了迅猛的发展和应用。

为此本文阐述了现场总线的发展和多现场总线技术的应用。

关键字:现场总线自动化控制系统1 概述在计算机自动控制系统急速发展的今天,特别是考虑到现场总线已经普遍地渗透到自动控制的各个领域的现实,现场总线必将成为电工自动控制领域主要的发展方向之一。

现场总线技术一直是国际上各大公司激烈竞争的领域;并且国外大公司已经在大力拓展中国市场,发展我国的现场总线产品已经刻不容缓。

现场总线对自动化技术的影响意义深远。

当今可以认为现场总线是提高自动化系统整体水平的基础技术,对国民经济影响重大。

因此,要在自动化领域中推广应用和发展现场总线。

现场总线是近年来自动化领域中发展很快的互连通信网络,具有协议简单开放、容错能力强、实时性高、安全性好、成本低、适于频繁交换等特点。

目前,国际上各种各样的现场总线有几百种之多,统一的国际标准尚未建立。

较著名的有基金会现场总线(FF)、HART现场总线、CAN现场总线、LONWORKS现场总线、PROFIBUS 现场总线、MODBUS、PHEONIX公司的INTERBUS、AS-INTERFACE总线等.自动化控制系统就是通信网络把众多的带有通信接口的控制设备、检测元件、执行器件与主计算机连接起来,由计算机进行智能化管理,实现集中数据处理、集中监控、集中分析和集中调度的新型生产过程控制系统。

从目前国内外自动化控制系统所应用的现场总线来看,主要有PROFIBUS、MODBUS、LONWORKS、FF、HART、CAN等现场总线。

以上系统基本上都是采用单一的现场总线技术,即整个自动化控制系统中只采用一种现场总线,整个系统构造比较单一。

现场总线已不仅仅是一个新技术领域或新技术问题,在研究它的同时,我们发现它已经改变了我们的观念;如何去看待现场总线,要比研究它的技术细节更为重要.1.1现场总线是一个巨大的商业机会一项权威报告声称现场总线的应用将使控制系统的成本下降67%;巨大的商业利益直接导致产生一个巨大的市场,并且促使传统市场萎缩,从而引发技术进步。

通用串行总线

通用串行总线通用串行总线(USB)是一种用于连接计算机及外部设备的标准接口。

USB接口的发展根植于个人电脑的普及,其已经成为一种被广泛应用的接口标准,用来连接各类设备,如打印机、键盘、鼠标、摄像头、外部硬盘等。

USB的发展历程USB接口的发展经历了几个重要的版本和演进。

在USB 1.0时代,数据传输速率较慢且设备插拔不方便,局限性明显。

随着USB 2.0的推出,数据传输速率得到了显著提升,达到了480Mbps,同时接口设计也更加便捷。

USB 3.0和USB 3.1进一步提高了传输速率,提供更好的性能和效率。

最新的USB 3.2为用户提供了更高的速度和带宽。

USB的特点USB接口的主要特点包括:•通用性:USB接口被广泛用于连接各类设备,具有极高的通用性。

•热插拔:用户可以在在不关闭计算机的情况下插拔USB设备,方便实用。

•供电:USB接口不仅能传输数据,还可为外部设备提供电源。

•速率:USB传输速率高,适合数据传输要求较高的设备。

USB的应用领域USB接口在各个领域都有着广泛应用。

以下是一些常见的应用领域:1.通信领域:手机、平板等设备通过USB接口实现数据传输和充电。

2.办公领域:打印机、扫描仪、键盘、鼠标等设备通过USB接口连接至计算机。

3.娱乐领域:摄像机、音箱、游戏手柄等设备通过USB接口连接到计算机或主机。

4.存储领域:外部硬盘、U盘等存储设备通过USB接口实现数据传输和备份。

USB的未来发展随着科技的不断进步,USB接口也在不断演进。

未来USB接口将会更加智能化和高效化,提供更快的数据传输速率、更高的电源输出能力,并且支持更多种类的设备连接。

未来USB接口的发展将为人们的日常生活带来更多的便利和效率。

总结:USB作为一种通用串行总线接口,在现代计算机和设备中扮演着重要角色。

它的发展至今已经历经多个版本的演进,成为连接各类设备的标准接口。

USB 接口的普及和进步为用户带来了更便捷的设备连接和数据传输方案,是现代科技不可或缺的一部分。

《2024年基于FPGA的PCIE总线接口和光纤通信模块设计》范文

《基于FPGA的PCIE总线接口和光纤通信模块设计》篇一一、引言随着信息技术的飞速发展,数据传输的速度和效率成为了系统性能的关键因素。

FPGA(现场可编程门阵列)以其高度的可定制性和并行处理能力,在高速数据传输和处理领域得到了广泛应用。

本文将详细介绍基于FPGA的PCIE总线接口和光纤通信模块设计,探讨其设计原理、实现方法和应用前景。

二、PCIE总线接口设计1. 设计原理PCIE(Peripheral Component Interconnect Express)总线是一种高速串行计算机扩展总线标准,具有高带宽、低延迟、支持即插即用等特点。

FPGA作为PCIE设备的核心控制器,需要设计相应的接口电路以实现与主机的通信。

2. 实现方法在FPGA中,PCIE总线接口的设计主要包括物理层设计、数据链路层设计和事务层设计。

物理层设计负责信号的收发和电气特性的匹配;数据链路层设计负责数据的封装、解封和流控制;事务层设计则负责处理数据传输过程中的各种事务请求。

3. 优势与挑战PCIE总线接口的设计具有高带宽、低延迟、可扩展性强等优势,能够满足高速数据传输的需求。

然而,设计过程中也面临着诸如信号完整性、电磁兼容性、时序约束等挑战。

需要通过合理的电路设计和严格的时序分析来确保系统的稳定性和性能。

三、光纤通信模块设计1. 设计原理光纤通信模块利用光信号在光纤中传输信息,具有传输距离远、传输速度快、抗干扰能力强等优点。

在FPGA系统中,光纤通信模块负责与外部设备进行高速数据传输。

2. 实现方法光纤通信模块的设计包括光模块和电模块两部分。

光模块负责将电信号转换为光信号,并通过光纤进行传输;电模块则负责将光信号转换为电信号,并与FPGA进行通信。

在FPGA中,需要设计相应的接口电路和协议栈来实现与光纤通信模块的通信。

3. 关键技术光纤通信模块设计的关键技术包括光模块的选择与配置、电模块的电路设计、光纤传输协议的制定等。

一种基于1394B的CCDL设计与实现

信息通信INFORMATION & COMMUNICATIONS2019年第5期(总第197期)2019(Sum. No 197)一种基于1394B 的CCDL 设计与实现周勇,王博,白M(中国航空工业集团公司西安航空计算技术研究所,陕西西安710065)摘要:1394B 是一种高速串行总线,以其离带宽、低延迟、高可靠特性在机栽系统中被广泛应用。

文章提出了一种在容错 计算机中使用1394B 总线作为通道间CCDL 对数据进彳亍可靠性传输,满足目前高性能容错计算机对高速数据通信及可 靠性的要求。

关键词:高性能容错计算机;1394B ; CCDL 中图分类号:TP333 文献标识码:A 文章编号:1673-1131(2019)05-0291-020引言IEEE 1394 是 1995 年 12 月由 IEEE(Institute of E lectiwiic and Electrical Engineers 〉制定的一种高性能串行总线标准,又名火线(FireWire)。

它的数据传输速率为100Mbps 、200Mbps 和400Mbps. IEEE 1394B 是对IEEE 1394增强或者扩展,主 要是对总线效率的改进,输速率达到800 Mbps 、1600 Mbps 和 3200 Mbps,支持即插即用热插拔功能。

航空电子系统的综合化带来总线网络传输的高带宽、高可 靠性和实时性需求。

原来广泛使用的1553B 总线1Mbps 的传 输速率已经无法满足系统总线带宽要求,而1394B 、AFDX 、FC 等新型总线在带宽上可满足系统需求叫并行总线比如PCI 、 VME 等虽然在带宽上能与上述总线相媲美,但是其冗余的数 据通路增加了错误发生的概率,使得系统高可靠性面临考验, 而串行总线的使用,使得故障比较容易隔离.相对于FC 和 AFDX, 1394B 在协议复杂度、开发的成本、总线线缆等方面具 有成本上的优势。

FPGA在机载雷达信号处理系统中的应用探析

科技创新23FPGA 在机载雷达信号处理系统中的应用探析胡建伟(江苏金陵机械制造总厂,江苏 南京 210000)摘要:本文首先对FPGA 和机载雷达信号处理系统的概念简要概述,然后对机载雷达信号处理系统的结构、特点和FPGA 在机载雷达信号处理系统中的应用问题简要分析,最后从HDL 语言设计、自顶向下模块化设计、同步设计、流水设计、增量设计等方面阐述FPGA 在机载雷达信号处理系统中的应用设计。

关键词:FPGA;机载雷达信号处理系统;应用设计随着FPGA 技术越来越成熟,基于FPGA 研发的系统功能也越来越强,而且这种系统设计方式理念更为先进,在成本、灵活性等方面均有较大优势。

因此雷达行业设计人员也逐渐认识到了FPGA 在信号处理系统中的重要性,目前FPGA 在机载雷达信号处理系统中的应用越来越普遍。

1 FPGA 和机载雷达信号处理系统概念 1.1 FPGA FPGA 是专业集成电路中的一种半定制电路,该集成电路应用了PAL 和GAL 等可编程器件,实现了定制电路和可编程器件的整合,让其同时具备二者的优点。

FPGA 设计模式在通信行业中比较常见,FPGA 芯片能够以特定的模型为基础并在后续的研究中对其进行进一步优化,从而使基于FPGA 研发的系统具备更强的功能和优点,同时FPGA 芯片从构造方面进行了优化,使整个系统的结构更加简单、性能更加优越。

FPGA 利用可编程逻辑列阵解决了器件门电路不足的问题,通过结构设计在设计成本、编程、集成等方面取得了一定优势,而算法和仿真设计等方面的运行效果也比较出色[1]。

FPGA 发展过程中逐渐将处理器和高速串行口融入其中,使其性能具有极大提高,某公司基于FPGA 研发的芯片在主频、硬核及波特率、数据处理、处理控制等方面的能力均获得了一定提升,而片上系统的出现更是让FPGA 设计产生质的飞跃,目前基于FPGA 已经已经可以设计可编程系统。

FPGA 数字时钟管理器的瞬时抖动、相位偏移等参数都比较小,在Select 1O-U1tra 技术下更是支持多个输出标准。

CAN总线在铁路设备通信中的应用

CAN总线在铁路设备通信中的应用【摘要】CAN总线在铁路设备通信中的应用,是铁路领域中的一项重要技术。

本文从CAN总线的基本原理入手,介绍了其在铁路信号系统、铁路车辆控制系统、列车诊断系统等方面的应用。

通过CAN总线,不仅可以实现设备之间的高效通信,还可以提高系统的可靠性和安全性。

本文也分析了CAN总线在铁路设备通信中的优势,包括高速传输、实时性强、抗干扰能力强等。

结论部分探讨了CAN总线在铁路设备通信中的发展前景和重要性,指出其将成为铁路领域通信技术的主流,对提升铁路设备通信效率和质量起到至关重要的作用。

CAN总线技术的不断发展将为铁路行业带来更多创新和进步,推动铁路设备通信的现代化发展。

【关键词】CAN总线, 铁路设备通信, 应用, 基本原理, 信号系统, 车辆控制系统, 列车诊断系统, 优势, 前景, 发展趋势,重要性1. 引言1.1 CAN总线在铁路设备通信中的应用CAN总线是一种基于事件驱动的通信协议,它采用串行通信方式,能够实现高速的数据传输。

在铁路信号系统中,CAN总线被用来传输控制指令和监测数据,实现信号设备之间的互联互通。

在铁路车辆控制系统中,CAN总线可以集成车辆各个部件的控制和监测功能,提高列车的运行安全性和效率。

在列车诊断系统中,CAN总线可以实时传输列车各个部件的健康状态数据,帮助维护人员及时发现并排除故障。

CAN总线在铁路设备通信中的应用具有显著的优势,包括高效的数据传输、可靠的通信质量和灵活的拓扑结构等。

未来CAN总线在铁路设备通信中的应用前景广阔,将继续发挥重要作用。

为了更好地适应铁路行业的发展需求,CAN总线在铁路设备通信中的发展趋势将是快速的、智能化的发展。

加强对CAN总线在铁路设备通信中的重要性认识,并持续推动其发展和应用是至关重要的。

2. 正文2.1 CAN总线的基本原理CAN总线的基本原理是一种车载网络通信技术,用于在铁路设备中实现实时数据传输和控制。

CAN总线采用了分布式通讯的方式,通过多个节点之间的信息交换来实现通信。

usb通信简介

USB接口还可以实现手机与其他设备之间的无线连接 ,如连接蓝牙耳机、车载导航等。

USB通信在嵌入式系统中的应用场景

工业控制

USB接口在工业控制领域应用广 泛,如连接传感器、执行器等设 备,实现快速稳定的数据传输。

智能家居

USB接口可以用于连接智能家居 设备,如智能灯泡、智能插座等 ,实现智能化控制和远程管理。

随着智能手机、平板等移动设备的普及,USB Type-C接口在移动设备中的应用将进一步扩大,同时也会带来更 多的便利性和创新功能。

USB通信在物联网中的应用

物联网设备的数量和种类不断增加,USB通信在物联网中的应用也将得到更广泛的拓展,如USB传感器、USB通 信模块等。

USB通信的产业发展和市场前景

包括USB Type-A、USB Type-B和 USB Type-C等连接器。

USB端点的定义

每个USB设备都有一个或多个端点, 用于与主机进行通信。

03

USB通信协议层

USB通信的协议栈

USB设备驱动程序负责管理USB设备的各种功 能和特性,例如设备的电源管理、数据传输等

。

USB核心驱动程序是USB协议栈的核心部分,它负责 管理USB设备的连接和通信,以及处理USB设备的各

设备响应配置请求

设备根据主机的要求进行响应,进入指定的配置状态,并向主机返 回配置结果。

配置信息的获取和设置

主机通过配置过程获取设备的配置信息,如接口、端点等,并设置 设备的配置状态,以便设备能够正常工作。

USB设备的接口和类别的定义和识别

接口的定义和识别

USB设备的接口是用于实现特定功能的软件资源,主机通过枚举过程获取设备 的接口信息并进行识别。

无线USB技术的研发

《高速串行总线信号完整性分析》范文

《高速串行总线信号完整性分析》篇一摘要:本文主要探讨高速串行总线中信号完整性的重要性、影响信号完整性的主要因素及其对系统性能的影响。

通过对信号完整性的深入分析,我们提出了有效的设计策略和改进措施,以提高信号完整性和系统的整体性能。

一、引言随着现代电子技术的发展,高速串行总线已成为数据传输的主要手段。

然而,在高速传输过程中,信号完整性成为一个关键问题。

信号完整性的好坏直接影响到系统的性能和可靠性。

因此,对高速串行总线信号完整性的分析具有重要的实际意义。

二、信号完整性的定义及重要性信号完整性是指信号在传输过程中保持其形状、幅度、时间和相位关系的能力。

在高速串行总线中,由于传输线效应、反射、电磁干扰等的影响,信号完整性可能受到损害,导致系统性能下降,甚至出现错误。

因此,保证信号完整性是提高系统性能和可靠性的关键。

三、影响信号完整性的主要因素1. 传输线效应:传输线效应是高速串行总线中影响信号完整性的主要因素之一。

由于传输线的特性阻抗与驱动器和接收器的阻抗不匹配,会导致反射、振荡等现象,从而影响信号的完整性。

2. 电磁干扰:电磁干扰是另一个影响信号完整性的重要因素。

外部电磁场和电流可能会对传输的信号产生干扰,导致信号失真或衰减。

3. 串扰:串扰是指不同传输线之间的耦合效应,它会导致信号的误读或畸变,从而影响信号的完整性。

四、信号完整性对系统性能的影响信号完整性的好坏直接影响到系统的性能和可靠性。

信号失真或衰减可能导致数据的误读或丢失,从而影响系统的正常工作。

此外,由于反射和振荡等现象,可能会增加系统的噪声和功耗,降低系统的稳定性和可靠性。

五、提高信号完整性的设计策略和改进措施1. 优化传输线设计:通过合理设计传输线的长度、阻抗等参数,以减小传输线效应对信号完整性的影响。

2. 电磁屏蔽:通过合理的电磁屏蔽设计,减小外部电磁场对传输的信号的干扰。

3. 串扰控制:通过优化布线、增加地线层等方式,减小不同传输线之间的耦合效应,从而控制串扰对信号完整性的影响。

高速SERDES接口芯片的应用浅析

高速SERDES接口芯片的应用浅析摘要:本文主要分析高速SERDES接口芯片仿真验证和实际应用,其次阐述了TLK2711工作原理和工作属性,通过相关分析希望进一步提高高速SERDES接口芯片的应用效果,满足星上数传系统更高的速率要求,解决之前存在的技术难题,仅供参考。

关键词:高速SERDES接口;芯片;应用1、TLK2711工作原理TLK2711属于一种千兆高速收发器件,物理层接口器件的典型代表,可对高速串行数据完成接受工作,后将其转换使其成为需要的低速并行数据。

最后将低速并行数据发送出去,使其成为高速串行数据,无论是发送端还是接受端,都可对单工通信单独使用,也可对双工通信同时应用,在超高速双向传输系统(点对点)中可以有效应用。

对于工作原理,如图一所示。

TKLSB属于一种发送控制信号,为K码发生器提供服务,TKMSB也是如此。

TKLSB在发送数据中表示低8bit,数据或者K码,TKMSB表示的是高8bit,他们的使用一般都会结合起来,TXCLK为参考输入时钟,为发送端外部提供服务,发送过程中,TXCLK当中的上升沿,会将想用的TXD[15:0]提供出来,后借助差分高速通道完成编码的效果,编码为8B/10B,进行串行,便可根据顺序有效输出[1]。

这一过程中,时钟综合器会对时钟(TXCLK)10具有的倍频进行参考,当有Bit时钟产生后,可在串行器中使用,起作用于并行转串行移位寄存器,应用该时钟,Bit会沿着上升/下降沿,对数据进行发送,因此速率(串行数据)是时钟的二十倍。

相同的原理,RKLSB和RKMSB也属于指示信号,可为K码提供服务,低8bit和高8bit(数据或者K码)通过两者接收后,RXTLK变成时钟信号,负责接收以及恢复,串行数据只要经过编码后,便可被接收,内插器和时钟恢复电路会对数据流进行锁定,进而把比特率时钟提取出来。

重新计时数据流便可应用恢复的时钟,之后对齐好需要使用的串行数据,安排在2个10位码字边界的地方,实施8B/10B编码。

浅谈1394总线技术

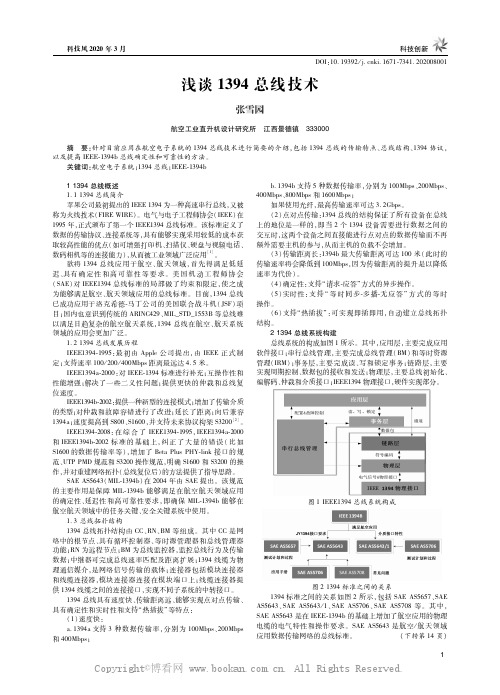

11394总线概述 1.11394总线简介 苹果公司最初提出的 IEEE1394为一种高速串行总线,又被 称为火线技术(FIREWIRE)。电气与电子工程师协会(IEEE)在 1995年,正式颁布了第一个 IEEE1394总线标准。该标准定义了 数据的传输协议、连接系统等,具有能够实现采用较低的成本获 取较高性能的优点(如可增强打印机、扫描仪、硬盘与视频电话、 数码相机等的连接能力),从而被工业领域广泛应用[1]。 欲将 1394总线应用于航空、航天领域,首先得满足低延 迟、具有 确 定 性 和 高 可 靠 性 等 要 求。美 国 机 动 工 程 师 协 会 (SAE)对 IEEE1394总线标准的局部做了约束和限定,使之成 为能够满足航空、航天领域应用的总线标准。目前,1394总线 已成功应用于洛克希德马丁公司的美国联合战斗机(JSF)项 目;国内也意识到传统的 ARINC429、MIL_STD_1553B等总线难 以满足日趋复杂的航空航天系统,1394总线在航空、航天系统 领域的应用会更加广泛。 1.21394总线发展历程 IEEE13941995:最初由 Apple公司提出,由 IEEE正式 制 定;支持速率 100/200/400Mbps距离最远达 4.5米。 IEEE1394a2000:对 IEEE1394标准进行补充;互操作性和 性能增强;解决了一些二义性问题;提供更快的仲裁和总线复 位速度。 IEEE1394b2002:提供一种新型的连接模式;增加了传输介质 的类型;对仲裁和故障容错进行了改进;延长了距离;向后兼容 1394a;速度提高到 S800、S1600,并支持未来协议构架 S3200[2]。 IEEE13942008:在 综 合 了 IEEE13941995,IEEE1394a2000 和 IEEE1394b2002标 准 的 基 础 上,纠 正 了 大 量 的 错 误 (比 如 S1600的数据传输率等),增加了 BetaPlusPHYlink接口的规 范、UTPPMD规范和 S3200操作规范,明确 S1600和 S3200的操 作,并对重建网络拓扑(总线复位后)的方法提供了指导思路。 SAEAS5643(MIL1394b)在 2004年由 SAE提出。该规范 的主要作用是保障 MIL1394b能够满足在航空航天领域应用 的确定性、延迟性和高可靠性要求,即确保 MIL1394b能够在 航空航天领域中的任务关键、安全关键系统中使用。 1.3总线拓扑结构 1394总线拓扑结构由 CC、RN、BM等组成。其中 CC是网 络中的根节点、具有循环控制器、等时源管理器和总线管理器 功能;RN为远程节点;BM为总线监控器,监控总线行为及传输 数据;中继器可完成总线速率匹配及距离扩展;1394线缆为物 理通信媒介,是网络信号传输的载体;连接器包括模块连接器 和线缆连接器,模块连接器连接在模块端口上;线缆连接器提 供 1394线缆之间的连接接口,实现不同子系统的中转接口。 1394总线具有速度快、传输距离远、能够实现点对点传输、 具有确定性和实时性和支持“热插拔”等特点: (1)速度快: a.1394a支持 3种数据传输率,分别为 100Mbps、200Mbps 和 400Mbps;

总线和数据通信技术整

汽车总线需要具备高可靠性、耐久性和安全性等特点,以适应汽车恶劣的工作环境。常见的汽车总线有CAN、LIN、FlexRay等。

汽车总线

航空总线主要用于连接航空电子系统中的各种设备和模块,实现实时数据传输和协同工作。

航空总线需要满足高可靠性、高安全性和高效率等要求,以确保飞行的安全和稳定。常见的航空总线有ARINC 429、ARINC 629等。

总线标准与协议

数据通信技术基础

02

数据一位一位地顺序传送,占用通信线路少,适合于远距离通信。

串行传输

数据以字节或字为单位,同时传送多个二进制位,速度快,适合于近距离通信。

并行传输

数据传输方式

比特率

表示每秒传输的二进制位数,单位是bps(bits per second)。

波特率

表示每秒传输的符号数,单位是baud。

工业物联网

工业物联网通过数据通信技术将工业生产过程中的设备、传感器和控制系统连接起来,实现智能化监控、远程控制和数据分析等功能,提高生产效率和降低运营成本。

数据通信在物联网中的应用

总线和数据通信技术的发展趋势和挑战

05

随着数据量的增长,总线及数据通信技术正向着更高的传输速率发展,以满足大数据时代的需求。

城域网

03

城域网是一种介于局域网和广域网之间的数据通信网络,覆盖城市或地区范围内的网络,用于连接不同地点的据通信应用

无线数据通信应用

移动通信

移动通信是指移动用户之间或移动用户与固定用户之间的通信方式,包括2G、3G、4G和5G等技术。

无线局域网

无线局域网是一种基于无线传输介质的局域网,通过无线信号传输数据,常见的标准包括WiFi和蓝牙等。

《总线技术》课件

定制化解决方案

针对不同行业和领域的需求,未来总线技术 将提供定制化的解决方案。

跨界融合与协同创新

总线技术将与其他领域的技术进行跨界融合 和协同创新,推动相关产业的发展。

THANKS

感谢观看

仲裁技术

总线通信协议的仲裁技术用于解决多个节点同时访问总线时可能出现的数据冲突问题。常见的仲裁技术包括令牌 传递、轮询和竞争等。

流量控制

总线通信协议的流量控制用于防止接收方来不及接收数据而造成的数据丢失问题。常见的流量控制方法包括停止 -等待、滑动窗口和缓冲区交换等。

03

总线标准与规范

IEEE标准

总线的分类与特点

总线分类

根据传输方式,总线可分为并行总线 和串行总线;根据连接的部件类型, 总线可分为内部总线和外部总线。

总线特点

总线具有规范性、共享性、互操作性 等特点,它规定了数据传输的规范和 标准,允许多个部件共享总线资源, 实现了各部件之间的互操作。

总线技术的发展历程

01

早期总线技术

在计算机发展的早期阶段,总线技术尚未形成规范和标准,各部件之间

传输方式

总线通信协议的传输方式包括单工、半双工和全双工三种。单工只能实现单向 通信,半双工可以同时实现双向通信,而全双工则可以实现同时双向通信。

数据格式

总线通信协议的数据格式包括二进制数据和ASCII码数据两种。二进制数据以高 低电平表示0和1,而ASCII码数据则使用可打印字符表示数据。

总线通信协议的仲裁技术与流量控制

的连接和通信较为混乱。

02 03

标准总线技术的出现

随着计算机技术的不断发展,出现了多种标准总线技术,如ISA、EISA 、PCI等,这些技术规范了数据传输的标准和规范,推动了计算机技术 的发展。

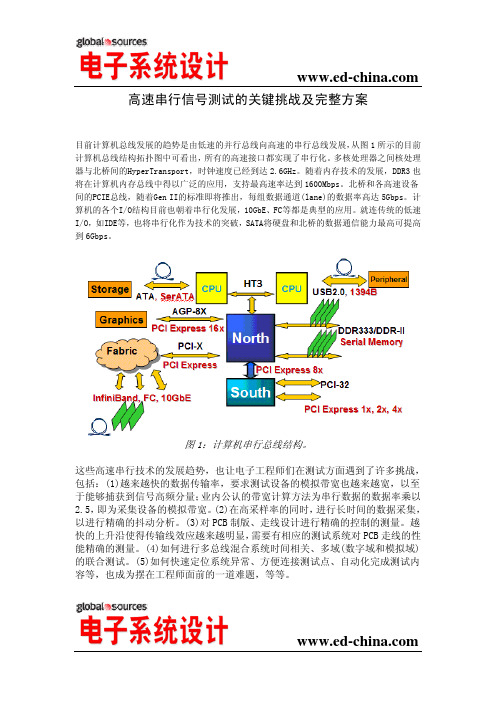

高速串行信号测试的关键挑战及完整方案

Bandwidth: 带宽 (Typical 典型) <calculated from Tr/Tf> <计算自 Tr/TF>

Standard: normal (0.75GHz), direct out (3.5GHz): High Bandwidth option (7.5GHz) 标准:正常(0.75GHz),直接输出(3.5GHz):高带宽选 择(7.5GHz)

Rise/fall (20-80) (Typical) 升/降 (典型)

Standard: normal (350ps), direct out (75ps): High Bandwidth option (35ps) 标准:正常(350ps),直接输出(75ps):高带宽选择 (35ps)

下文将分别阐述在高速串行信号测试中的关键技术和挑战,以及解决这些关键问 题的方法。 信号互联层测试 TDR(时域反射测定法)是 PCB 走线的特征阻抗是否符合或达到预计要求的最主要 的测试方法(图 2),HT 和 DDR3 的标准都严格定义了信号传输线阻抗值的范围。 TDR 是一个闭环的测试系统,系统发出快沿脉冲,激励被测走线,同时采集由于 走线阻抗变化而对快沿的反射信号。快沿的上升时间时间决定了 TDR 的分辨率。 对差分走线的阻抗测量,需要测试系统输出差分的快沿信号来进行 TDR 测试,以 如实反应差分走线在差分信号的激励下出现的阻抗突变、串扰等一系列问题。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。