第5章 组合逻辑、时序逻辑的Verilog语言描述(已排)

verilog 组合逻辑 时序逻辑

verilog 组合逻辑时序逻辑下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!Verilog是一种硬件描述语言,主要用于对数字电路进行建模、仿真和综合。

Verilog 语言教程(逻辑及语法部分)

a b #2 c d #3

a

b #2 c

#3

d

#4

e

总延迟=Max{2,3}+4=7

时钟周期必须 > 7ns

总延迟= {Max{2,3}+4+1}=8

时钟周期必须 > 4ns

总处理数据的吞吐量增加

e

#1

#4

#1

22

为什么要设计有限状态机?

如果能严格以时钟跳变沿为前提,按排好时时序, 来操作逻辑系统中每一个开关Si,则系统中数据 的流动和处理会按同一时钟节拍有序地进行,可 以控制冒险和竞争现象对逻辑运算的破坏,时延 问题就能有效地加以解决。

寄存器间数据流动的控制开关

开关S1

组合逻辑

开关S2

dddd qqqq

dddd qqqq

组合逻辑

dddd qqqq

clock

2021/7/13

寄存器1

寄存器2

寄存器3

17

开关逻辑应用举例

寄存器间数据流动的控制开关

开关S1

dq clock

寄存器A

开关S2

2021/7/13

开关S3

dq

寄存器B

开关S4

开关S5

- 时序逻辑: 由多个触发器和多个组合逻辑块组成的网

络。常用的有:计数器、复杂的数据流动控制逻辑、运算 控制逻辑、指令分析和操作控制逻辑。同步时序逻辑的设 计是设计复杂的数字逻辑系统的核心。

- 存储器和寄存器:用于暂时存储数据信息。

2021/7/13

4

组合逻辑举例之一

一个八位数据通路控制器

`define ON 1 ‘b 1 `define OFF 1 ‘b 0 wire ControlSwitch; wire [7:0] out, in; assign out = (ControlSwith== `ON) ? in : 8 ‘h00

verilog时序逻辑和组合逻辑

verilog时序逻辑和组合逻辑(原创实用版)目录1.Verilog 语言概述2.组合逻辑概念与描述3.时序逻辑概念与描述4.组合逻辑与时序逻辑的区别5.Verilog 中组合逻辑和时序逻辑的实现正文一、Verilog 语言概述Verilog 是一种硬件描述语言,主要用于设计数字电路和系统。

它可以描述电路的结构、功能和时序,并可以进行仿真和综合。

在 Verilog 中,我们可以使用不同的逻辑描述方法来实现组合逻辑和时序逻辑电路。

二、组合逻辑概念与描述组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。

组合逻辑不涉及对信号跳变沿的处理,无存储电路,也没有反馈电路。

通常可以通过真值表的形式表达出来。

在 Verilog 中,我们可以使用 wire 和 reg 类型来描述组合逻辑电路。

wire 类型相当于实际的连接线,变量的值随时发生变化,用 assign 连接。

reg 类型则是寄存器类型,在下一个触发机制到来之前保留原值,用 always 描述。

三、时序逻辑概念与描述时序逻辑电路的特点是输出不仅取决于当前输入,还与电路原来的状态有关。

时序逻辑涉及对信号跳变沿的处理,通常包含存储电路和反馈电路。

时序逻辑电路的行为可以用状态转移方程或状态机描述。

在 Verilog 中,我们可以使用 always 块和时序变量来描述时序逻辑电路。

always 块用于描述时序逻辑中的行为,可以对时序变量进行赋值和检测。

时序变量在时间上具有连续性,其值在不同的时间点可能发生变化。

四、组合逻辑与时序逻辑的区别组合逻辑和时序逻辑的主要区别在于输出是否依赖于过去的状态。

组合逻辑的输出仅依赖于当前输入,不涉及过去的状态;时序逻辑的输出则依赖于过去的状态,通常需要存储电路来实现。

此外,组合逻辑通常不涉及时钟信号,而时序逻辑则需要时钟信号来驱动状态转移。

五、Verilog 中组合逻辑和时序逻辑的实现在 Verilog 中,我们可以使用不同的语法结构来实现组合逻辑和时序逻辑电路。

4.6 用VerilogHDL描述组合逻辑电路.ppt

//Gate-level description of a 2-

4、设计举例

to-4-line decoder

试用Verilog语言的门级

module _2to4decoder

(A1,A0,E,Y);

元件描述2线-4线译码器.

input A,B,E;

说明

output [3:0]Y;

部分

E1

& Y0

FA1 (S[1],C1,A[1],B[1],C0), FA2 (S[2],C2,A[2],B[2],C1), FA3 (S[3],C3,A[3],B[3],C2);

endmodule

4.6.2 组合逻辑电路的数据流建模

数据流建模能在较高的抽象级别描述电路的 逻辑功能。通过逻辑综合软件,能够自动地 将数据流描述转换成为门级电路。

&&

逻辑与

||

逻辑或

移位运算符 (双目运算

符)

符号

> < >= <= == !=

& ~&

| ~| ^ ^~ 或 ~^

>> <<

功能说明

大于 小于 大于或等于 小于或等于 等于 不等于

缩位与 缩位与非 缩位或 缩位或非 缩位异或 缩位同或

右移 左移

位运算符与缩位运算的比较

A:4’b1010 、 B:4’b1111,

0 1x

0 xx 0 xx

调用名

and A1(out,in1,in2,in3);

nand真值表

z

nand

输入1

01xz

0

0 1111

x

输1 1 0 x x

杭电第5章时序电路的Verilog设计

Verilog的描述风格

5.9.1 RTL描述 :一切用各种独立的组合电路模块和独立的寄存器模块,但不涉 及底层具体逻辑门结构或触发器电路细节,来构建描述数字电路的形式。

5.9.2 行为描述:比如例3-21。Verilog HDL的模块只描述电路的功能或行为,而 没有直接指明或涉及实现这些行为的硬件结构。

5.1 基本时序元件的Verilog表述

5.1.1 基本D触发器及其Verilog表述

关键词posedge:posedge CLK时钟上升沿敏感。

相对应的,还有negedge CLK时钟下降沿敏感。

5.1 基本时序元件的Verilog表述

5.1.2 用UDP表述D触发器

含异步复位控制的边沿触发型D触发器

Q: 现态;Q+:次态;-:保持原状态;?任意数据

5.1 基本时序元件的Verilog表述

5.1.3 含异步复位和时钟使能的D触发器及其Verilog表述

含异步复位/时钟使能型触发器及其Verilog表述

关键词posedge:posedge CLK时钟上升沿敏感。

相对应的,还有negedge CLK时钟下降沿敏感。

使用移位操作符设计移位寄存器

有符号数左右移的操作符:

对于右移操作时,一律将符号位,即最高位填补 移除的位。 左移操作同普通左移一样,移出腾空的位用0填补。

5.4 可预置型计数器设计

5.4.1 同步加载计数器

4.6 keep属性应用

有时设计者希望在不增加与设计无关的信号连线的条件下,在仿真中也能详细了解 定义在模块内部的某数据通道上的信号变化情况。但往往由于此信号是模块内部临 时性信号或数据通道,在经逻辑综合和优化后被精简掉并除名了,于是在仿真信号 中便无法找到此信号,也就无法再仿真波形中观察到此信号。为解决这个问题,可 以使用keep属性,通过对关心的信号定义keep属性,告诉综合器把此信号保护起来, 不要删除或优化掉,从而使此信号能够完整地出现在仿真信号中。

用VerilogHDL描述组合逻辑电路

endmodule

4位全加器的描述 --调用1位全加器

case (S)

2’d0: Y = D[0]; Nhomakorabea2’d1: Y = D[1];

2’d2: Y = D[2];

2’d3: Y = D[3];

endcase

end

endmodule

例:对基本的4线-2线优先编码器的行为进行Verilog描述。

module priority(W, Y) input [3:0] W; output reg [1:0] Y; always @(W) casex (W) 4’b1xxx: Y = 3; 4’b01xx: Y = 2; 4’b001x: Y = 1; 4’b0001: Y =0;; default: begin z = 0; Y=2’bx;end //W无效时,z=0,Y为高阻 endcase

E

Y0

例:用数据流建模方法对2

线-4线译码器的行为进行

Y1

描述。

A0 Y2

A1 Y3

module decoder_df (A1,A0,E,Y); input A1,A0,E; output [3:0] Y; assign Y[0] = ~(~A1 & ~A0 & ~E); assign Y[1] = ~(~A1 & A0 & ~E); assign Y[2] = ~(A1 & ~A0 & ~E); assign Y[3] = ~(A1 & A0 & ~E);

第5章-Verilog语言要素

5.3.2 Variable型

variable型变量必须放在过程语句(如initial、always)中,通 过过程赋值语句赋值;在always、initial等过程块内被赋值的 信号也必须定义成variable型。 variable型(以前叫register型)是数据存储单元的抽象,但不 能表示真正的硬件,相当于计算机高级语言中的变量。 常用variable型变量:

整数(integer)

Examples:

8'b11000101 //位宽为八位的二进制数11000101

8'hd5

//位宽为八位的十六进制数d5;

5'O27

//5位八进制数

4'D2

//4位十进制数2

4'B1x_01

//4位二进制数1x01

5'Hx

//5位x(扩展的x),即xxxxx

4'hZ

//4位z,即zzzz

assign larger=(a>b);

assign equal=(a==b);

assign less=(a<b);

endmodule

【例5.4】 采用参数定义的二进制计数器

module count_w(en,clk,reset,out);

input clk,reset,en; parameter WIDTH=8;

◆ 整数

◆ 实数

◆ 字符串

整数(integer)

整数按如下方式书写:

+/-<size> '<base><value> 即 +/-<位宽>'<进制><数字> size 为对应二进制数的宽度;base为进制;value是 基于进制的数字序列。 进制有如下4种表示形式: ◆ 二进制(b或B) ◆ 十进制(d或D或缺省) ◆ 十六进制(h或H) ◆ 八进制(o或O)

第五章组合逻辑电路的VerilogHDL实现

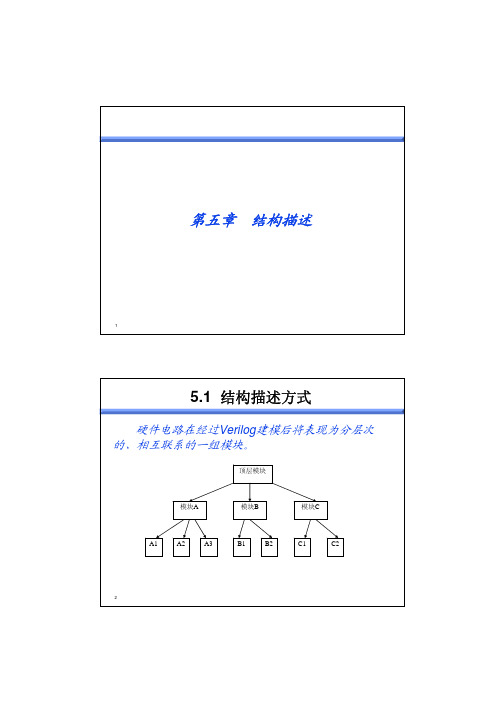

第五章组合逻辑电路的VerilogHDL实现第5章组合逻辑电路的Verilog HDL实现5.10.1 逻辑电路的Verilog HDL描述方式Verilog HDL描述逻辑电路时常用3种描述方式,分别为:行为型描述、数据流型描述和结构型描述。

行为型描述只描述行为特征,不涉及逻辑电路的实现,是一种高级语言描述方式,使用例如always语句或initial 语句块中的过程赋值语句;数据流型描述指通过assign连续赋值实现组合逻辑功能的描述方式;结构型描述指描述实体连接的结构方式,所谓实体一般指Verilog 语言已定义的基元,包括门原语、用户自定义原语(UDP)和其他模块(module)。

行为型描述语句更简练,不能被综合;结构型描述语句通常容易被综合,但语句显得复杂。

在实际开发中往往多种描述方法混合使用。

5.10.2 2选1数据选择器的Verilog HDL实现2选1数据选择器可以有多种描述方式,通过4个实例和3种描述方式对例子中出现的语法现象进行解释。

5.10.12选1数据选择器的数据流型描述方式;5.10.22选1数据选择器的数据流型描述方式;5.10.32选1数据选择器的行为型描述方式;5.10.42选1数据选择器的结构型描述方式;5.10.2.1 2选1数据选择器实例1//例5.10.1module Mux21(a,b,s,y);//----------------1input a,b;input s;output y;assign y=(s==0)?a:b;//----------------2endmodule//----------------310.2.1 2选1数据选择器实例11. Verilog语言描述//例5.10.1module Mux21(a,b,s,y);//----------------1input a,b;input s;output y;assign y=(s==0)?a:b;//----------------2endmodule//----------------32. 程序说明(1)注释行(2)模块定义语句module和endmodule所有的程序都置于模块(module)框架结构内。

verilog语言05

31

5.3

当两个 driven strength不同的 net 相连时,会以 strength level 较高的 net 输出为结果。

Pull 1 Strong 0 Supply 1 Supply 1 Large 1 Strong 0

32

5.3

[例1]四选一多路选择器

33

5.3

module mux4_to_1(out, i0,i1, i2, i3, s1, s0); output out; input i0,i1, i2, i3, s1, s0; //门级实例引用 not (s1n, s1); not (s0n, s0); and (y0, i0, s1n, s0n); and (y1, i1, s1n, s0); and (y2, i2, s1, s0n); and (y3, i3, s1, s0); or (out, y0, y1, y2, y3); endmodule

demo_para #(4,5,6) g1(out, in1, in2);

18

…… endmodule

5.2

注意: 参数值列表中各个参数值的排列次序必须与被调用模块中 各个参数的说明次序保持一致;同时参数的个数也必须相 同; 在只希望对调用模块内的个别参数进行更改的情况下,所 有无需更改的参数值也必须按对应参数的顺序在参数值列 表中全部列出(照抄原值);

15

5.2

实例

module bottom(in); input in; always @(posedge in) begin: keep reg hold; hold=in; end endmodule module middle(stim1,stim2); input stim1,stim2; bottom amod(stim1), bmod(stim2); endmodule 16 module top; reg stim1,stim2; middle a(stim1,stim2); endmodule 模块名:top top.a top.a.bmod

Verilog入门

第五章 Verilog 语言

Verilog 语法与实例

• 数字表示:整数,实数 整数:+/- <位宽> ‘<基数符号> <数值>

<位宽>:指定整数的大小,以bit为单位。

<基数符号>:指定整数的基数,可以是b(binary)二进

制;o(octal)八进制;d(decimal)十进制;h(hex-

adecimal)十六进制。

第五章 Verilog 语言

Verilog 语法与实例

• Verilog的四种逻辑状态: 0:逻辑零、逻辑非、低电平 1:逻辑1、逻辑真、高电平 x或X:不定态 z或Z:高阻态

第五章 Verilog 语言

verilog时序逻辑和组合逻辑

verilog时序逻辑和组合逻辑摘要:I.引言- 简述Verilog时序逻辑和组合逻辑的概念II.Verilog时序逻辑- 定义时序逻辑并介绍其特点- 说明时序逻辑在Verilog中的表示方法- 举例介绍时序逻辑的应用III.Verilog组合逻辑- 定义组合逻辑并介绍其特点- 说明组合逻辑在Verilog中的表示方法- 举例介绍组合逻辑的应用IV.时序逻辑与组合逻辑的比较- 比较两者的异同点- 分析各自的优势和劣势V.结论- 总结Verilog时序逻辑和组合逻辑的重要性正文:I.引言Verilog是一种硬件描述语言,常用于设计数字电路和系统。

在Verilog 中,时序逻辑和组合逻辑是两种基本的逻辑类型。

本文将介绍Verilog时序逻辑和组合逻辑的概念、特点、表示方法和应用,并比较两者的优劣。

II.Verilog时序逻辑时序逻辑是一种在特定时刻输出信号的逻辑类型,其输出不仅取决于当时的输入信号,还与电路原来的状态有关。

时序逻辑的特点是涉及对信号跳变沿的处理,有存储电路和反馈电路。

在Verilog中,时序逻辑可以通过always块和寄存器来表示。

例如,一个计数器模块可以用来显示当前时间,其功能取决于时序逻辑的实现。

III.Verilog组合逻辑组合逻辑是一种任意时刻输出仅取决于该时刻输入信号的逻辑类型,不涉及对信号跳变沿的处理,无存储电路和反馈电路。

组合逻辑的特点是可以通过真值表来表达。

在Verilog中,组合逻辑可以通过或门、与门、非门等逻辑门来表示。

例如,一个加法器模块可以用来计算两个数字的和,其功能取决于组合逻辑的实现。

IV.时序逻辑与组合逻辑的比较时序逻辑和组合逻辑在Verilog中有各自的应用场景。

时序逻辑更适用于需要对信号跳变沿进行处理的场景,如计数器、寄存器等;而组合逻辑更适用于简单的逻辑运算,如加法器、乘法器等。

此外,时序逻辑通常具有较高的计算复杂度,而组合逻辑则相对简单。

在实际应用中,需要根据具体需求选择适当的逻辑类型。

verilog时序逻辑和组合逻辑

verilog时序逻辑和组合逻辑

摘要:

1.组合逻辑简介

2.时序逻辑简介

3.组合逻辑与时序逻辑的区别

4.实例分析

5.总结

正文:

【1】组合逻辑简介

组合逻辑是数字电路设计中的基础部分,它主要研究如何使用布尔代数和逻辑门来实现数字逻辑电路。

组合逻辑电路的特点是,其输出仅依赖于当前时刻的输入,而与之前的输入状态无关。

简而言之,组合逻辑电路不需要考虑时间因素,只需关注输入与输出之间的关系。

【2】时序逻辑简介

时序逻辑是数字电路设计的另一个重要分支,它主要研究如何在电路中处理带有时间约束的逻辑问题。

时序逻辑电路的输出不仅依赖于当前时刻的输入,还与之前时刻的输入状态有关。

这使得时序逻辑电路的设计相比组合逻辑电路更为复杂。

【3】组合逻辑与时序逻辑的区别

组合逻辑和时序逻辑的主要区别在于对时间因素的处理。

组合逻辑不考虑输入信号的历史状态,而时序逻辑关注输入信号的历史状态对电路输出的影

响。

此外,组合逻辑电路的设计相对简单,而时序逻辑电路的设计则更为复杂。

【4】实例分析

以一个简单的触发器为例,触发器的输入信号为A、B,输出信号为Q。

在没有考虑时序约束的情况下,可以使用组合逻辑实现触发器。

但当需要满足一定的时间约束(如设置潜伏期和建立时间)时,组合逻辑无法满足要求,必须采用时序逻辑设计。

【5】总结

总之,组合逻辑和时序逻辑在数字电路设计中具有不同的应用场景。

组合逻辑适用于简单数字电路设计,关注输入与输出之间的关系;而时序逻辑适用于复杂数字电路设计,需要考虑时间约束。

Verilog HDL数字设计教程(贺敬凯)第5章

第5章 同步有限状态机设计

其仿真结果如图5-11所示。 【例5-5】 对应于步骤四的Verilog HDL建模。 ///产生JK激励信号:D触发器的激励d---->JK触发器的激励J 和K

module D_JK(d,q,j,k);

input d,q; output reg j,k;

always @(d,q)

利用多余状态,卡诺图化简后的激励方程和输出方程为:

n n D1 Q0 A,D0 A, Y Q1 A

第六步:画出逻辑图并检查自启动能力。逻辑图如图57所示。

第5章 同步有限状态机设计

图5-7 例5-1的逻辑图

第5章 同步有限状态机设计

经检查,该电路具有自启动能力。 至此解题完毕。 以上六步,我们均可以采用Verilog HDL进行电路建模, 下面从后向前对各个步骤进行建模,见例5-2至例5-9。

第5章 同步有限状态机设计

程序说明:

(1) 例5-4的实现要求得出输出方程和激励方程,然后才

能对时序逻辑电路建模。这种建模方法同例5-2一样,需要 手工做大量复杂的工作,而不是由计算机来完成复杂的计算 工作。 (2) 该模块的综合结果如图5-12所示。

第5章 同步有限状态机设计

图5-12 例5-4的综合结果

第5章 同步有限状态机设计

【例5-3】 对例5-2的改进——消除毛刺。 module input clk,A; output reg Y; wire q0,q1; mydff_2 dff0(.D(A),.Q(q0),.clk(clk)), dff1(.D(A&q0), .Q(q1), .clk(clk)); always @(posedge clk) Y= q1 & (~A); endmodule 该模块的综合结果如图5-10所示。 fsm_1(clk,A,Y);

时序逻辑和组合逻辑的详解

时序逻辑和组合逻辑的详解时序逻辑和组合逻辑是数字电路设计的两种基本逻辑设计方法,它们在数字系统中起着至关重要的作用。

时序逻辑是一种依赖于时钟信号的逻辑设计方法,通过定义在时钟信号上升沿或下降沿发生的动作,来确保逻辑电路的正确性和稳定性。

而组合逻辑则是一种不依赖时钟信号的逻辑设计方法,其输出只取决于当前的输入状态,不受到时钟信号的控制。

本文将分别对时序逻辑和组合逻辑进行详细的阐释,并比较它们在数字电路设计中的应用和特点。

时序逻辑首先来看时序逻辑,它是一种将输入、输出和状态信息随时间推移而改变的逻辑系统。

时序逻辑的设计需要考虑到时钟信号的作用,时钟信号的传输速率影响了时序逻辑电路的稳定性和响应速度。

时钟信号的频率越高,电路的工作速度越快,但同时也会增加功耗和故障率。

因此,在设计时序逻辑电路时,需要充分考虑时钟频率的选择,以及如何合理地控制时钟信号的传输和同步。

时序逻辑电路通常由触发器、寄存器、计数器等组件构成,这些组件在特定的时钟信号下按照预定的顺序工作,将输入信号转换成输出信号。

时序逻辑电路的设计需要满足一定的时序约束,确保信号在特定时间内的传输和处理。

时序约束包括激发时序、保持时序和时序延迟等,这些约束在设计时序逻辑电路时至关重要,一旦违反可能导致电路不能正常工作或产生故障。

时序逻辑的一个重要应用是时序控制电路,它在数字系统中起着至关重要的作用。

时序控制电路通过时序逻辑实现对数据传输、状态转换和时序控制的精确控制,保证系统的正确性和稳定性。

时序控制电路常用于时序逻辑电路的设计中,例如状态机、序列检测器、数据通路等,它们在计算机、通信、工控等领域都有广泛的应用。

时序逻辑还常用于时序信号的生成和同步,如时钟信号、复位信号、使能信号等。

时序信号的生成需要考虑电路的稳定性和同步性,确保各个部件在时钟信号的控制下协调工作。

时序信号的同步则是保证各个时序逻辑电路之间的数据传输和处理是同步的,避免数据冲突和错误。

第5章verilogHDL语法规范3基本结构和结构说明

(2)通常采用异步清零!只有在时钟周期很小或清零信号为 电平信号时(容易捕捉到清零信号)采用同步清零。

18

5.7结构说明语句

二、initial语句

格式

initial begin 语句1; 语句2; …… 语句n; end

ISE部分支持!

[例3.9.4] 利用initial语句生成激励波形。

initial begin inputs = ’b000000; #10 inputs = ’b011001; #10 inputs = ’b011011; #10 inputs = ’b011000; #10 inputs = ’b001000; end

在仿真的初始状态对各变量进行初始化; 在测试文件中生成激励波形作为电路的仿真信号。

19

结构说明语句

[例] 对各变量进行初始化。

…… parameter size=16; reg[3:0] addr; reg reg1; reg[7:0] memory[0:15]; initial begin reg1 = 0; for(addr=0;addr<size;addr=addr+1); memory[addr]=0; end ……

21

5.7结构说明语句

1.任务(task)

ISE支持!

当希望能够对一些信号进行一些运算并输出多个结果(即有多 个输出变量)时,宜采用任务结构。

11

5.7结构说明语句

注2:always语句必须与一定的时序控制结合在一起才有用! 如果没有时序控制,则易形成仿真死锁!

[例]生成一个0延迟的无限循环跳变过程——形成仿真死锁! always areg = ~areg; [例]在测试文件中,用于生成一个无限延续的信号波形 ——时钟信 号 ‘define half_period 50 module half_clk_top; reg reset, clk; // 输入信号 wire clk_out; // 输出信号 always #half_period clk = ~clk; …… endmodule

Verilog HDL语言的描述语句

第4节Verilog HDL语言的描述语句Verilog HDL 描述语句2.4.1 结构描述形式通过实例进行描述的方法,将Verilog HDL预先定义的基本单元实例嵌入到代码中,监控实例的输入。

Verilog HDL中定义了26个有关门级的关键字,比较常用的有8个。

在实际工程中,简单的逻辑电路由逻辑门和开关组成,通过门元语可以直观地描述其结构。

基本的门类型关键字如下所述:•and•nand•nor•or•xor•xnor•buf•notVerilog HDL支持的基本逻辑部件是由该基本逻辑器件的原语提供的。

其调用格式为:门类型<实例名> (输出,输入1,输入2,……,输入N)例如,nand na01(na_out, a, b, c );表示一个名字为na01的与非门,输出为na_out,输入为a, b, c。

例2-5 一个简单的全加器例子:module ADD(A, B, Cin, Sum, Cout);input A, B, Cin;output Sum, Cout;// 声明变量wire S1, T1, T2, T3;xor X1 (S1, A, B),X2 (Sum, S1, Cin);and A1 (T3, A, B),A2 (T2, B, Cin),A3 (T1, A, Cin);or O1 (Cout, T1, T2, T3);endmodule在这一实例中,模块包含门的实例语句,也就是包含内置门xor、and和or的实例语句。

门实例由线网型变量S1、T1、T2和T3互连。

由于未指定顺序,门实例语句可以以任何顺序出现。

门级描述本质上也是一种结构网表。

在实际中的使用方式为:先使用门逻辑构成常用的触发器、选择器、加法器等模块,再利用已经设计的模块构成更高一层的模块,依次重复几次,便可以构成一些结构复杂的电路。

其缺点是:不易管理,难度较大且需要一定的资源积累。

2.4.2 数据流描述形式数据流型描述一般都采用assign连续赋值语句来实现,主要用于实现组合功能。

第5讲-用verilog语言建模组合逻辑

三十二位加器

结构化描述方法结构图

ain[0] bin[0] ain[1] bin[1] ain[30] bin[30] ain[31] bin[31]

ca

FA

ca1

FA

ca2

ca30

FA

ca31

FA

cin

sum[0]

sum[1]

sum[30]

sum[31]

2013-11-15

2013-11-15

23

1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 12.

`timescale 1ns/100ps module sample_of_bus(databus,link_bus,clk); inout [11:0] databus; input clk; input link_bus; reg [11:0] outsigs; assign databus=(link_bus) ? outsigs:12'bz; always@(posedge clk ) begin outsigs <=databus >> 5; end endmodule

2013-11-15

7

三十二位加器

结构化描述方法

`timescale 1ns/100ps module adder_32bits(ain,bin,cin,sum,ca); input [0:31] ain; input [0:31] bin; input cin; output [0:31] sum; output ca; wire ca31,ca30,ca29,...,ca1; one_full_adder UUT_31(.a(ain[31]),b(bin[31]),cin(cin), .ca(ca31),.sum(sum[31]));

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

15

对应的CMOS工艺下D触发器的电路结构

5

always过程块与连续赋值语句描述的组合逻辑电路效果相同 两种方法描述的2路选择器电路均相同, 综合工具根据Verilog代码综合自动生成的电路均为下图所示:

.

6

5.1.3 时序逻辑电路的always过程块实现

module DFF(clk, rst, d ,q); input clk, rst ,d; output q; reg q; always @( posedge clk) if (rst) q <= 1'b0; else q <= d; endmodule 注意:1. 过程块描述的时序逻辑电路,其敏感量采用边沿触发; 2. 为了避免竞争,描述时序电路只能用非阻塞赋值,不能用阻 塞赋值。 问题: 为什么描述时序逻辑要采用边沿触发的方式?

3

5.1.1 组合逻辑电路的连续赋值实现

以2路选择器为例: module mux2to1( a, b, sel, out); input a, b; input sel; output out; assign out = (sel) ? b:a; endmodule

注意:

连续赋值语句的被赋值变量只能是线网wire型。

. . . .

clk T2 clk clk clk T4 clk

q

D触发器符号

D触发器电路图

问题:1.为什么说d触发器是边沿触发? 2.为什么当时钟信号clk变为高电平后,无论输入端d信号如 何变化,都不能反映到输出端q上去?

17

5.2.6 D触发器-工作过程分析

d T1 . clk = 0 T1 . T2 . T2 . q T3 . T4 q T3 . T4 . q . q

13

对应的CMOS工艺下D触发器的电路结构

rst clk d

T1 clk

. . . .

clk q T3 clk T2 clk clk clk T4 clk

.

q

D触发器符号

D触发器电路图 说明:复位信号不受时钟信号clk的影响。 只要复位信号rst为高电平时,电路就复位,输出q为0。

14

D触发器的Verilog描述(同步复位)

注意:锁存器是在敏感量为电平触发方式的组合逻辑电路中产生的。

10

5.2.3 CMOS工艺下锁存器的电路结构

问题:为什么锁存器要在电平触发方式下生成?

d

clk T1 clk

.

.

q q

clk T2 clk

11

5.2.4 锁存器-工作过程分析

d T1 q q d T1

.

.

.

T2 2,当clk = 0时

18

5.2.7 总结-锁存器与D触发器

问题:锁存器与D触发器的区别?

答案要点:从触发方式和电路结构两方面说明。

19

Verilog语法下的锁存器与D触发器 module LATCHorDFF (q, data, enable); input clk,data, enable; output q; reg q;

rst clk d

T1 clk

. . . .

clk q T3 clk T2 clk clk clk T4 clk

q

D触发器符号

D触发器电路图 说明:复位信号受时钟信号clk的影响,只有在时钟上升沿来临后, 复位信号rst为高电平时,电路就复位,输出q为0。

16

不考虑复位信号后的D触发器的电路结构

clk d clk T1 clk q T3

硬件描述语言和数字系统设计

第5章 组合逻辑、时序逻辑的 Verilog 语言描述

主讲教师:刘政林 童乔凌

主要内容:

5.1 组合逻辑、时序逻辑的Verilog语言描述

5.2 锁存器 LATCH 与 D触发器的Verilog语言 描述与电路特点

2

5.1 组合逻辑、时序逻辑的Verilog 语言描述

知识点: 5.1.1 组合逻辑电路的连续赋值实现 5.1.2 组合逻辑电路的always过程块实现 5.1.3 时序逻辑电路的always过程块实现

20

第二次作业:

1. 说明latch(锁存器)与register(触发器)的区别,行为级描

述中latch如何产生的 .画出DFF的结构图,并用verilog 实现之。 2.用verilog实现4进制的计数,并画出用D触发器搭建的 schematic图。

3.用verilog实现10分频电路,占空比为50%,并画出D触发 器搭建的 schematic图,7分频呢?

always @( enable or data) if (enable) q <= data; // enable为低电平的情况没有定义 endmodule

9

5.2.2 锁存器-综合情况

综合工具Leonardo所报的Warning信息: Warning, q is not always assigned. Storage may be needed..

(请贴上仿真波形,并对波形进行分析 )

21

always @( posedge clk) if (enable) q <= data; //else // q<=0; always @(enable or data) if (enable) q <= data; // else // q<=0;

endmodule

问题 1.上面左边描述的电路,如果不加else q<=0,会生成锁存器吗? 2.上面右边描述的电路,如果不加else q<=0,会生成锁存器吗?

d

clk = 1 clk d q

分析:1.因为当 clk 为低电平0时, 传输门T1导通,输入端d的信号被送到q_点; 而当 clk在由低电平0跳变到高电平1时刻(即clk上升沿时), T3导通, q_ 点的值得以被传到输出端q去,对外即好像在时钟上升沿触发,完成数据采集。 2.在clk保持高电平1时,由于传输门T1处于关断状态,无论输入端d的信号如 何变化,均不能被送到输出端口。

12

5.2.5 D触发器的Verilog描述(异步复位)

module asynrst_DFF(clk, rst, d ,q ); input clk, rst ,d; output q; reg q; always @(posedge clk or posedge rst) if (rst) q <= 1'b0; else q <= d; endmodule

.

q q

T2 1,当clk = 1时 波形: clk d q

分析:因为当 clk 为高电平1时, 传输门T1导通,输入端d到输出端q形成通路,所 以输出q能够反映输入端d的信号; 而当 clk变为低电平0时,导致传输门T1关断,输出q就不能反映输入端口d的 信号,此时由于传输门T2的导通,输出级有反馈环路,输出端q能够保持原值。

4

5.1.2 组合逻辑电路的always过程块实现

仍然以2路选择器为例: module mux2to1( a, b, sel, out); input a, b; input sel; output out; reg out; always @(sel or a or b) out = (sel) ? b:a; endmodule 注意: 过程块描述的组合逻辑电路: 1. 被赋值变量只能是reg型; 2. 触发方式采用电平触发; 3. always@( )引导的敏感量要完整。

8

5.2.1 Verilog语言中锁存器(latch)的产生

在 always 过程块所描述的组合逻辑电路中,所使用的条

件语句如果没有说明全部条件,将产生 latch锁存器,例: module latch (data, enable, q); input data, enable; output q; reg q;

7

5.2 锁存器 LATCH 与 D触发器的Verilog语言 描述与电路特点

知识点: 5.2.1 Verilog语言中锁存器(latch)的产生 5.2.2 锁存器-综合情况 5.2.3 CMOS工艺下锁存器的电路结构 5.2.4 锁存器工作过程分析 5.2.5 D触发器的Verilog描述 5.2.6 D触发器-工作过程分析 5.2.7 总结