逻辑门实验指南Verilog hdl

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

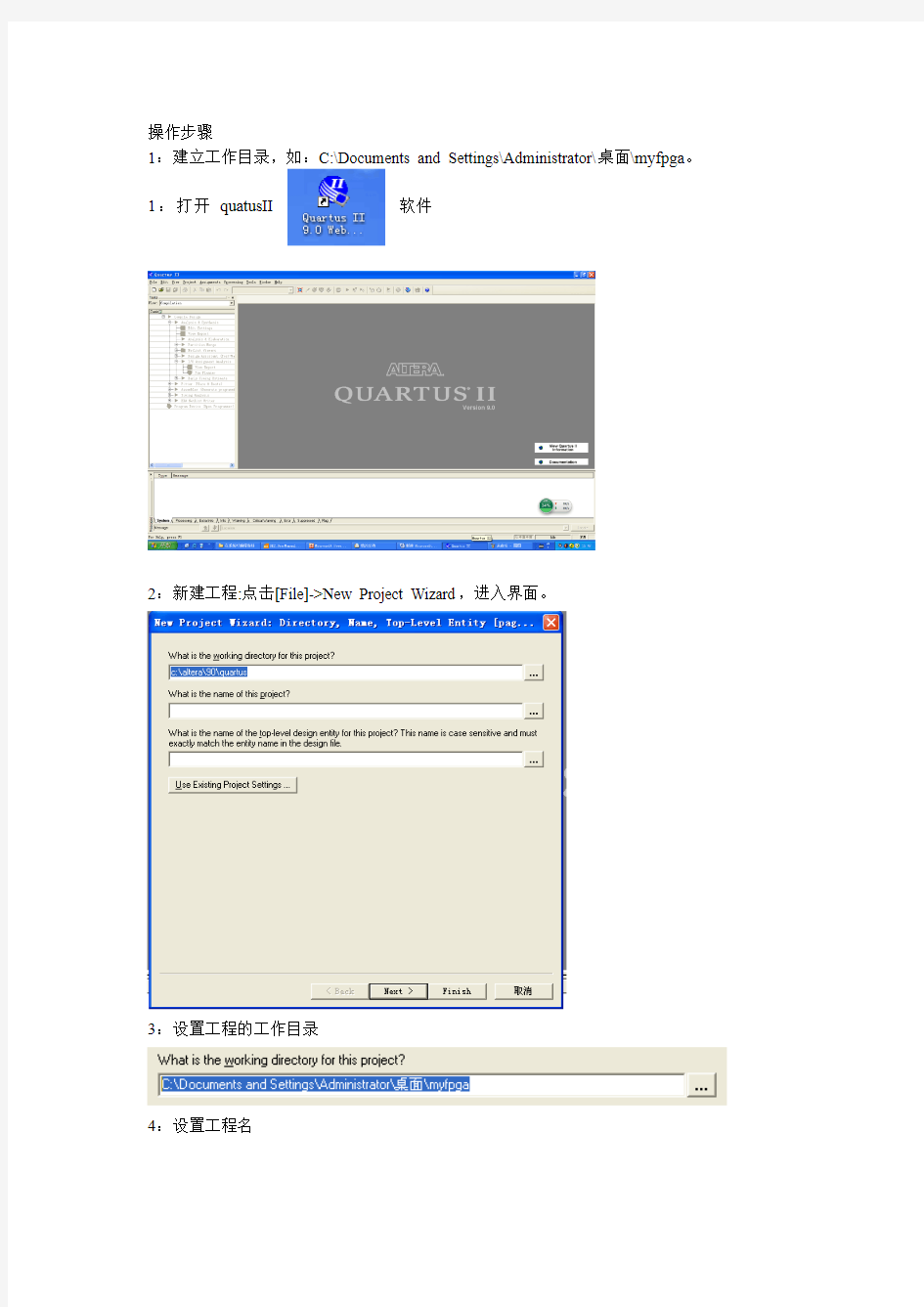

操作步骤

1:建立工作目录,如:C:\Documents and Settings\Administrator\桌面\myfpga。

1:打开quatusII软件

2:新建工程:点击[File]->New Project Wizard,进入界面。

3:设置工程的工作目录

4:设置工程名

5:点击[Next]进入下一个界面

6:如果没有需要导入到工程中的文件,直接点击Next进入下一个界面。

7:按上图所示设置“Family”、“Package”、“Pin count”、“Speed grade”,选择对应芯片。8:点击Next,进入如下界面,设置仿真工具。

9:点击Next,进入下一界面,确认工程信息是否正确。

10:如果确认信息无误,点击Finish按钮完成工程创建。

11:新建文件,点击[File]->New,如图所示

12:选择Design Files 中的Verilog HDL File。

13:输入代码,例如

module gates2(input wire a, input wire b, output wire [5:0]z);

assign z[5]=a&b;

assign z[4]=~(a&b);

assign z[3]=a|b;

assign z[2]=~(a|b);

assign z[1]=a^b;

assign z[0]=~(a^b);

endmodule

温馨提示:模块名(gates2)需要与工程名一致。

14:设置管脚:点击[Assignments]->Pins

15:在location中输入对应的管脚号。

16:点击按钮进行工程编译。

17:点击按钮进入下载程序界面。

18:点击Close,在Mode中选择JTAG

19:点击按钮选择USB-Blaster。

20:点击按钮开始烧录。

进度条达到100%时表示烧录完成

21:改变输入引脚的电平,观察输出的变化。