基于Verilog的AES加密算法的实现毕业设计论文

基于FPGA的高级加密标准AES设计与实现

基于FPGA的高级加密标准AES设计与实现【摘要】确保网络与通信安全的最重要的工具就是加密,对称加密中又以AES加密算法最为重要,目前已成为标准,研究AES加密算法对于防范信息安全泄密具有重要意义。

本文对AES加密算法做简单的介绍,并利用硬件描述语言进行设计,设计采用流水线的思想,AES-128算法共有10轮,在每一轮之间都插入流水线寄存器,提高系统工作频率,最终下载到FPGA芯片CycloneIII系列的EP3C120F484I7器件中,经验证功能正确。

【关键词】AES;流水线;状态矩阵;FPGAAbstract:The most important tool to encrypt the security of networks and communications,is the symmetric encryption algorithm,AES is the Advanced Encryption Standard,which is now the most famous Symmetric encryption algorithm,it is meaningful to research this algorithm.This paper introduces the principle of AES encryption algorithm and the detailed description of the FPGA implementation,to make the optimization to achieve the best speed,the design of the state are designed by pipeline technology.we used the hardware description language to design each modules,fianly examed in the FPGA chip of CycloneIII EP3C120F484I7.Keywords:AES;pipelines;state;FPGA1.前言现如今,信息安全一直都是热门话题,而密码学又是信息安全的重要组成部分,研究密码学具有重要意义。

毕业设计论文AES加密算法

毕业设计论文AES加密算法摘要随着信息技术的快速发展,人们对数据安全问题的关注日益增加。

AES(Advanced Encryption Standard)是目前应用最广泛的对称加密算法之一,被广泛应用于保护数据的机密性。

本文主要探讨了AES加密算法的原理、过程及其在信息安全中的应用,以期提高数据的安全性。

1.引言随着网络的迅猛发展,信息的传输已经成为我们日常生活中不可或缺的一部分。

然而,信息的传输安全问题也愈发凸显,特别是在敏感信息的保护方面。

因此,保护信息安全和隐私已成为重要的议题。

2.AES加密算法的选择和设计AES加密算法是由美国国家标准与技术研究院(NIST)制定的一种对称加密算法。

与其他对称加密算法相比,AES算法在安全性和效率方面表现更优秀。

在选择AES算法时,需要考虑加密算法的安全性、性能和算法的复杂度等因素。

3.AES加密算法的原理AES加密算法采用分组密码的方式,将明文按照一定的分组长度进行分组,再对每个分组进行轮函数的处理。

在AES算法中,明文分组长度为128位,密钥长度为128、192或256位。

AES算法由四个基本的运算模块构成,包括字节代换(SubBytes)、行移位(ShiftRows)、列混淆(MixColumns)和轮密钥加(AddRoundKey)。

4.AES加密算法的过程在AES加密算法的过程中,首先需要进行密钥的扩展,根据密钥的长度生成多轮的轮密钥。

然后,对明文进行分组、轮函数的处理和轮密钥加操作。

最后得到密文。

5.AES加密算法的应用AES加密算法广泛应用于各个领域,特别是在信息安全领域。

在网络通信中,AES算法被用于保护数据的机密性,防止数据被非法获取。

在存储介质中,AES算法可以被用于加密存储的数据,确保数据的安全性。

此外,AES算法还广泛应用于数字版权保护、无线通信和智能卡等领域。

6.AES加密算法的优化和改进尽管AES加密算法在安全性和效率方面表现出色,但仍有一些改进和优化的空间。

基于FPGA的AES加密算法在网络认证中的应用

分类号U D C密级学号、砂矫争了,去军硕士学位论文基于F P G A的A E S加密算法在网络认证中的应用路伟学科名称:学科门类:指导教师:申请日期:微电子学与固体电子学工学余宁梅教授2010年3月第二章AE S 算法的原理及系统的整体实现方式是用128位的状态按位与256位的密钥进行异或运算)四个函数组成,最后一次轮变换不包含列混合变换。

解密算法(右图),则是加密部分的逆运算〔5,〔6〕。

2.3 AE S 算法的原理2.3.1加密的基本轮变换A E S 加密算法的基本轮变换有4个变换组成,分别是:S 盒变换(su b B y t e s ())、行移位运算(sh i f t R o w s ())、列混合变换(M i xC ol u mn s())、轮密钥加变换(A ddR ou n d K ey())I刀2.3.1 .15盒变换—S ubBvt e s ()SubBytes ()变换时AES 算法中唯一的基于s 盒的非线性置换。

SubBytes ()变换用于将输入或中间态的每一个字节都通过一个简单的查表,将其映射为另一个字节,映射方法是:把输入字节的高4位作为S 盒的行值,低4位作为列值,然后取出S 盒中对应行和列的元素作为输出〔8〕。

我心)盆之3、4567分,口l,,二j r f 肠神巧乃料“禅此称扎为璐肠,)e 滋伟祀3比2f 朋侧。

扮01曰肋8川驾汕心润洲刀刁4’3l .“知头仍杨M d 斤价补比妈如加拍秘击引仍如肠s j 姗气︸男代I 4)2h 川f l 心协对万刀州1462朋“功内川价记乃阳而价倪如九储酬f 4材盯幼汉川润必垃熟山份涌价什书肠翻”卜哟劝闪34()7犯肠乃肠两拓论饭礴们叭41乃川八畅弘舒巧价朋,初诵枷如聪配7f7仍肠川孙绍哪叹4’t 以角肠426l j 叨对抓彻斤材如97骊必涌仍四涌e 肠抓比I l ,加书刃到”︸心翻卜姗的t]7I l 7’I 加必臼司几盯代山肠间寿肠1训”碑的刀万训翻叨玲4f 为37乃协钾补舰川刀幻泪“码。

基于FPGA的AES算法芯片设计实现

基于FPGA的AES算法芯片设计实现引言密码模块作为安全保密系统的重要组成部分,其核心任务就是加密数据。

分组密码算法AES 以其高效率、低开销、实现简单等特点目前被广泛应用于密码模块的研制中。

密码模块一般被设计成外接在主机串口或并口的一个硬件设备或是一块插卡,具有速度快,低时延的特点。

而从整体发展趋势来看,嵌入式密码模块由于灵活,适用于多种用户终端、通信设备和武器平台,将会得到更加广泛的应用。

基于FPGA 实现的嵌入式密码模块与以往的主流硬件实现方式(如DSP 芯片、单片机)相比,具有低成本、高速度、微功耗、微小封装以及保密性强等优点,与ASIC 相比具有设计灵活、成本低、周期短等优点。

另一个明显的优点在于:在对时间代价和空间代价的取舍上,基于FPGA 实现的加密技术提供了多种实现方案,分别对时间代价和空间代价有不同的偏重,有利于在各种应用环境中进行优化。

硬件实现无论是ASIC 方案还是FPGA 方案,数据处理速度的提高都离不开优化技术,包括算法轮函数和设计结构的优化。

AES 算法的快速实现方案包括:优化S 盒的结构(如使用复合域、查表等方法),列混合与密钥加的结合,以及采用流水线技术等。

表1 为几种典型的AES 算法实现性能对比情况。

AES 算法结构AES 是一个迭代型的分组密码,包含了轮变换对状态的重复作用。

用State表示待加密状态,CipherKey 表示初始加密密钥,ExpandedKey 表示扩展密钥,其加密过程描述如下:Round(State,ExpandedKey) --轮变换{SubByte(State);--字节代替表1 几种典型的AES 算法实现性能对比。

基于FPGA的AES加密算法的高速实现

基于FPGA的AES加密算法的高速实现马肃王击摘要:介绍AES算法的原理以及基于FPGA的高速实现。

结合算法和FPGA的特点,采用查表法优化处理了字节代换运算、列混合运算。

同时,为了提高系统工作速度,在设计中应用了内外结合的流水线技术,并应用Altera公司的开发工具及芯片进行实际开发。

关键词: AES; FPGA; 查表法; 流水线技术;中图分类号: B, 文献标识码: TP271+.5High speed implementation of AES algorithm based onFPGAMaSu WangJiAbstract: This paper describes the design of AES and fast implementations of AES on hardware based on FPGA.Based on the characteristic of AES and FPGA,the implementation of subbytes, mixcolumns is optimized by using the method of look-up tables.For making it work faster,the pipelining method is taken in the design.The develop tools and IC are from the Altera company.Keywords: AES; FPGA; method of look-up tables; Pipeline Technology1 引言随着信息技术的迅速发展,信息已成为当今社会的一种重要资源。

但当人们享受信息资源带来的巨大便利的同时,也承受着信息被篡改、泄漏、伪造的威胁,安全问题日益严重。

安全风险制约着信息的有效使用,信息安全对现代社会健康有序的发展,保障国家安全和社会稳定有着重要作用。

使用FPGA实现AES算法的优化设计

使用FPGA实现AES算法的优化设计信息安全是计算机科学技术的热点研究领域,数据加密则是信息安全的重要手段。

随着可编程技术的飞速发展及高速集成电路的不断出现,采用FPGA实现加密算法已受到越来越广泛的关注和重视。

与传统的软件加密方法相比,硬件加密的优点是:(1)安全性好,不易被攻击;(2)计算速度快,效率高;(3)成本低,性能可靠。

加密系统中体现数据传输速度的一个重要性能指标是数据吞吐量,计算公式为:(数据长度M/时钟个数N)×时钟频率F。

提高数据吞吐量是改善加密系统性能的关键,也是加密算法硬件实现技术的重要内容。

AES算法作为DES算法的替代者应用非常广泛,其硬件实现方法已有不少讨论,主要是通过提高算法频率来提高吞吐量。

但是在实际运行中,为了保证整个加密系统的稳定性,通常全局时钟频率较低,不可能达到算法的仿真频率,如PCI接口电路时钟频率只有33MHz,因此实际数据吞吐量仍然较低。

本文根据AES算法的结构特点及硬件系统的特点,提出一种快速的AES算法IP核设计方法。

该方法采用优化设计轮函数和流水线技术,在较低的系统时钟频率下,通过减少分组运算时钟数目来获得更高的吞吐量和更快的传输速度。

1 AES算法AES是美国国家标准与技术研究所(NIST)提出的高级加密标准。

2000年10月,NIST 宣布将比利时人Joan Daemen和Vicent Rijinen提交的Rijndael算法作为高级加密标准(AES)。

该算法设计简单,与公钥密码算法不同,没有复杂的乘法运算,易于实现,灵活性强,轮函数良好的并行特性有利于硬件设计与实现。

AES算法是一种迭代型分组密码,其分组长度和密钥长度均可变,各自可以独立指定为128bit、192bit、256bit。

本文主要讨论分组长度和密钥长度为128bit的情况。

AES算法是将输入的明文(或密文)分成16个字节,在第一个Add Round Keys变换后进。

基于fpga的aes密码算法设计

基于FPGA的AES密码算法设计一、引言随着信息技术的快速发展,信息安全问题也日益突出,密码算法成为保障信息安全的重要手段之一。

AES(Advanced Encryption Standard)是一种对称密码算法,已经成为当前最流行、最安全的数据加密标准之一。

而FPGA(Field-Programmable Gate Array)作为一种可编程逻辑器件,具有高度的灵活性和可编程性,逐渐成为密码算法设计中的重要工具。

二、AES密码算法概述1. AES密码算法简介AES密码算法是一种对称密码算法,旨在提供快速、高效和安全的数据加密解密功能。

它可以使用128位、192位或256位的密钥,并对固定大小的数据块进行加密处理。

AES算法采用了替代、置换、线性变换等多种复杂运算方法,以实现高度的安全性。

2. AES密码算法的结构AES密码算法主要由四个连续执行的操作组成:字节替代、行移位、列混淆和轮密钥加。

在这些操作的基础上,AES算法通过多轮迭代的方式来实现对数据块的加密处理。

三、FPGA在密码算法设计中的应用1. FPGA的优势FPGA作为一种可编程逻辑器件,具有高度的灵活性和可编程性,能够实现复杂的数字逻辑电路设计。

与传统的固定功能集成电路相比,FPGA可以根据具体需求进行重新配置,同时具有较高的运算速度和并行处理能力。

2. FPGA在密码算法设计中的应用利用FPGA的可编程特性,可以实现对称密码算法的硬件加速和优化设计。

FPGA可以并行处理大量数据,并且能够高效地实现复杂的运算逻辑,从而提高密码算法的加密解密速度和安全性。

四、基于FPGA的AES密码算法设计1. FPGA加速AES算法的优势基于FPGA的AES算法设计可以充分发挥FPGA并行处理和高速运算的优势,实现对数据加密解密过程的加速和优化。

与传统的软件实现相比,FPGA加速的AES算法能够显著提高算法的执行效率和性能表现。

2. FPGA加速AES算法设计的实现步骤(1)针对AES算法的具体特点,对其加密解密过程进行硬件逻辑设计;(2)通过VHDL或Verilog等硬件描述语言对AES算法进行逻辑电路设计和仿真验证;(3)利用FPGA开发板进行算法的实际实现,并进行性能测试和调优。

AES算法设计与实现毕业设计

AES算法的实现

编程语言的选择

C语言:高效、简洁,适合底层开发 Python:易学易用,适合快速原型开发 Java:面向对象,适合大型项目开发 JavaScript:前端开发,适合Web应用开发

加密过程的实现

密钥生成:使用密钥生成器生成密 钥

解密过程:将密文与密钥进行异或 运算,得到明文

添加标题

AES算法设计与实现毕 业设计

汇报人:

目录

添加目录标题

01

AES算法的实现

04

AES算法概述

毕业设计过程与成果

02

05

AES算法的设计

总结与展望

03

06

添加章节标题

AES算法概述

加密算法简介

AES算法:一种高级加密标准,用于保护数据安全 特点:高效、安全、易于实现 应用领域:广泛应用于网络通信、数据存储等领域 加密过程:包括密钥生成、数据加密、数据解密等步骤

对AES算法的改进建议

提高加密速度:优化算法实现,减少计算量 增强安全性:引入新的加密技术,提高抗攻击能力 提高灵活性:支持多种加密模式,满足不同应用场景需求 优化内存管理:减少收获与不足

收获:掌握了AES算法的原理和实 现方法

不足:在实现过程中遇到了一些技 术难题,需要进一步学习和研究

密钥更新:定期更新密钥, 提高安全性

安全性分析

加密算法:采用对称加密算法,安 全性高

加密模式:支持多种加密模式,如 CBC、CFB、OFB等,提高安全性

添加标题

添加标题

添加标题

添加标题

密钥长度:支持128、192、256 位密钥长度,满足不同安全需求

抗攻击能力:具有较强的抗攻击能 力,如抗差分攻击、抗线性攻击等

AES算法设计与实现-毕业设计

AES加密算法的研究与实现摘要:在信息安全领域,对信息数据进行加密是一种常用而且行之有效的安全措施。

但近年来,随着分布式计算和并行处理技术的发展,56位密钥的DES(Data Encryption Standard)已难以胜任公用数据加密标准算法。

为此,1997年,美国国家标准和技术研究所(NISI)开始征集先进加密标准(AES)算法,以此作为DES 的替代品.新的加密算法的密钥长度可以为128、192和256位,它可以实现对128位的数据分组进行加密和解密。

1998年,NISI对15中候选算法进行评定,最终,Rijndael 算法以其设计灵活、实现简单、加解密速度快、安全性高、支持并行处理等特点而胜出。

随着AES算法的普及应用,AES算法在日常生活、国民生产和国家安全等方面越来越起着重要的作用。

因此,对AES加密算法实现的研究便成为一个重要的课题。

本文首先对AES算法进行分析和研究,并在此基础上实现了AES核心代码,然后,以此核心代码为基础设计实现了一个加密软件。

通过该软件既可以对128位的数据分组进行加密和解密,也可以完成对文件的加密和解密。

AES 算法是一个复杂的算法,对其进行研究和实现它在一定程度上促进我国信息安全的发展。

关键词:私钥加密;分组加密;文件加密;AES算法Research and Implementation of AESalgorithmAbstract:In the field of information security, the encryption of information is a common and effective security measures。

But in recent years, with the development of the distributed computing and parallel processing technology,the 56 bits of key of the DES (Data Encryption Standard)has been difficult to be competent with the standard of the common data algorithm。

学术论文:【毕业论文】加密和密码学的(AES加密算法)

【毕业论文】加密和密码学的(AES加密算法)本科毕业论文〔设计〕题目::加密和密码学 (AES加密算法)姓名:邓小明第一章绪论1.1 AES高级加密标准随着Internet的迅猛开展,基于Internet的各种应用也日新月异,日益增长。

但是,由于Internet是一个极度开放的环境,任何人都可以在任何时间、任何地点接入Internet获取所需的信息,这也使得在Internet上信息传输及存储的平安问题成为影响Internet应用开展的重要因素。

正因为如此,信息平安技术也就成为了人们研究Internet应用的新热点。

信息平安的研究包括密码理论与技术、平安协议与技术、平安体系结构理论、信息对抗理论与技术、网络平安与平安产品等诸多领域。

在其中,密码算法的理论与实现研究是信息平安研究的根底。

而确保数据加密算法实现的可靠性和平安性对于算法理论应用到各种平安产品中起到了至关重要的作用。

对各类电子信息进行加密,以保证在其存储,处理,传送以及交换过程中不会泄露,是对其实施保护,保证信息平安的有效措施。

1977年1月数据加密标准DES(Data Encryption Standard)正式向社会公布,它是世界上第一个公认的实用分组密码算法标准。

但DES在经过20年的实践应用后,现在已被认为是不可靠的。

1997年1月2日NIST发布了高级加密标准(AES-FIPS)的研发方案,并于同年9月12日正式发布了征集候选算法公告,NIST希望确定一种保护敏感信息的公开、免费并且全球通用的算法作为AES,以代替DES,用以取代DES的商业应用。

在征集公告中,NIST对算法的根本要求是:算法必须是私钥体制的分组密码,支持128bits分组长度和128,192,256bits密钥长度。

经过三轮遴选,Rijndael最终胜出。

2000年10月2日,NIST宣布采用Rijndael算法作为新一代高级加密标准。

Rijndael的作者是比利时的密码专家Joan Daemon博士和Vincent Rijmen博士。

基于Verilog的AES加密算法的实现毕业设计论文

基于VERILOG的AES加密算法的实现摘要:随着信息产业在我国国民经济中扮演越来越重要的角色,信息技术的发展和数据传输的安全性受到了有关部门的重视,加强网络信息安全的加密产品具有广泛的应用前景。

此课题主要研究了基于VERILOG硬件描述语言的AES加密算法原理及优化,以及设计硬件实现。

本文先介绍了先进加密算法(AES)的原理,同时讲述了其与Rijndael设计的异同。

安全,高效,易拓展优化,硬件实现简单是其的特点,同时,本文还研究了算法实现的关键技术。

在设计过程中,完成了整体结构的规划和各部分的端口的定义,用VERILOG语言完成了电路的RTL级的描述,同时使用了Model公司的Modelsim仿真工具进行了软件平台上的仿真,实现了128位比特密钥的加密解密的逻辑功能,硬件上使用了基于Xilinx公司的VIRTEX系列芯片,并用Synplify 软件进行了FPGA综合,仿真基本达到了要求,这也证明了设计的正确性。

在设计中尤其要提到的是本文采用了ECB(电子密码本)加密算法模式,采用流水线结构,提高了电路的工作频率和速度,本设计的创新点在于用语言实现S盒变换时,并没有采用传统的查表方式,而是直接采用了算法描述,相较之下,节省了电路的存储面积,实现了优化。

关键字:Verilog,AES,先进加密标准,Rijndael设计,FPGA,加密,高速,流水线结构The implement of AES encrypt arithmetic base on Verilog HDL06204518 YuhuanSupervised by Zheng LixiaAbstract:With the information industry plays more important role in the country economy, the development of communication technique and security of data transfer is taken serious by some government department. The encrypt product which is used to strengthen net information security has extensive foreground. This subject mainly investigate AES encrypt arithmetic principium and its upgrade, then offer the design of hardware implement.This subject introduce the principium of AES arithmetic first, at the same time, it gives the similarities and differences. The AES arithmetic contains following characteristic: security, high efficiency, easy optimized, easy progress of hardware implement. The subject introduces the pivotal technique of the implement and attentions at the same time. Within the process of designing, I complete the programming of whole configuration and the defining of port of each part, complete the RTL description of circuit with Verilog HDL. And I complete the emulation which is based on software with Modelsim which is the product of Model Co. It achieves the logic function of 128 bit key. I use the CMOS chip of Virtex series which comes from Xilinx Co., and carry through synthesis using the software of Synplify. The result of the synthesis is reach the request of design, it prove the correctness of the design. I should mention especially that I use the ECB encrypt arithmetic mode and pipelining configuration which advances work frequency and work speed. The innovative point lies to the mode of the implement of s-box transform. I don’t use the mode of looking through the table. It save the area of ROM and implement the upgrade.Key words: Verilog, AES, advanced encrypt standard, Rijndael design, FPGA, encrypt, high speed, pipelining configuration.目录摘要 (I)关键字 (I)Abstract. (II)Key words (II)第一章绪论 (1)1.1密码学简介和我国信息安全现状 (1)1.2 数据加密标准的发展过程 (2)1.2.1数据加密标准DES (2)1.2.2 高级加密标准AES (2)1.3 AES的研究现状 (3)1.3.1 算法的研究现状 (3)1.3.2 硬件实现的研究现状 (3)1.4 本论文的意义 (5)1.5 内容和创新 (5)1.6 本章小结 (5)第二章 AES加密算法原理介绍和安全性能分析 (6)2.1 Rijndael和AES的区别 (6)2.2 预备知识 (6)2.2.1 Rijdael的数学基础和设计思想 (7)2.2.2 字节运算(位运算) (9)2.2.3 四字节运算 (10)2.3 加密算法的四种主要工作模式 (11)2.4 加密算法原理描述 (13)2.5 AES加/解密算法的实现 (14)2.5.1 S盒变换 SubBytes() (15)2.5.2 行变换ShiftRows() (16)2.5.3 列变换Mixcolumns() (16)2.5.4 与扩展密钥的异或运算AddRoundKey() (17)2.5.5 密钥扩展程序 Key Expansion( ) (17)2.6 AES安全性能分析 (17)2.6.1安全性原则 (17)2.6.2 AES算法的安全性 (18)2.6.3AES算法的性能分析 (19)2.7 本章小结 (19)第三章开发环境介绍 (20)3.1 硬件描述语言 (20)3.2 Modelsim+Synplify+(Virtex-5)开发环境 (20)3.2.1 Modelsim (20)3.2.2 逻辑综合和综合工具Synplify (21)3.2.3 Xilinx Virtex-5系列FPGA (22)3.3 设计方法 (23)3.4 本章小节 (24)第四章 AES算法的FPGA设计 (25)4.1 FPGA实现系统分析 (25)4.1.1 软硬件实现方法比较 (25)4.1.2 性能参数 (26)4.1.3 关键技术 (26)4.2 整体结构设计 (28)4.2.1 总体设计方案 (28)4.2.2 总体系统结构框图 (30)4.3 各系统分支设计 (31)4.3.1 加解密模块的设计 (31)4.3.2 控制模块设计 (33)4.3.3 密钥扩展模块设计 (34)4.3.4 接口模块设计 (35)4.4 编码实现 (36)4.5 本章小节 (37)第五章系统的仿真和测试 (38)5.1 仿真测试简介 (38)5.2 Modelsim功能仿真 (38)5.3 Synplify 综合和时序分析 (43)第六章结论和展望 (44)致谢 (45)参考文献 (46)基于VERILOG的AES加密算法的实现第一章绪论计算机技术和网络技术的发展极大丰富了人们的眼界和接受外界信息的方式,大量敏感重要信息通过公用通信设施和计算机网络进行交换。

基于AES算法的数据加密与解密硬件设计

考虑到AES的并行运算需要大量的硬件资源及FPGA的价格等因素,选用 Altera公司的Cyclone EPlC20F400C8来实现算法,为便于向其他FPGA平台和 ASIC移植,采用VHDL语言实现该算法。.

1.2.1 AES在网络层安全中的应用

由于在IP设计之初没有考虑安全性,在早期的英特网上时常发生诸如企业 或机构网络遭受到攻击、机密数据被窃取等不幸的事情。为了加强英特网的安全 性,从1995年开始,IEFT着手研究制定安全套用于保护IP通信的安全协议一

AES在提出时就考虑到并行处理问题,但仅局限于通用处理器的处理方法, 从并行加速的角度来看目前任何通用处理器都无法做到同时计算一个分组(无论 是128bits或者是256bits)。从处理器的微观处理过程来看,在任何时刻,处理

第一章绪论

器仅在某一步骤对一部分数据进行运算处理,在整个处理过程中,大量的资源处 于闲置状态,影响了加密解密的速度。

will be used widely.The realization of AES algorithm has many advantages,such as fast,flexible,has no need for the structure of processor and SO on.All of this

基于Verilog的FPGA的电子密码锁的设计

基于 FPGA 设计的电子密码锁是一个小型的数字系统,与普通机械锁相比,具有许多独特的优点:保密性好,防盗性强,可以不用钥匙,记住密码即可开锁等。

目前使用的电子密码锁大部份是基于单片机技术,以单片机为主要器件。

在实际应用中,程序容易跑飞,系统的可靠性较差。

本文介绍的一种基于现场可编辑门阵列 FPGA 器件的电子密码锁的设计方法,采用 VHDL 语言对系统进行描述,并在EP3C10E144C8 上实现。

通过仿真调试,利用可编程逻辑器件 FPGA 的电子密码锁的设计基本达到了预期目的。

固然,该系统在一些细节的设计上还需要不断地完善和改进,特殊是对系统的扩展有很好的使用系统和设计的价值。

现场可编程门阵列; VHDL 语言;电子密码锁FPGA—based design of the electronic code lock is a small digitalsystem. It has many unique advantages:good privacy and security , it do not need the key but remember password to unlock, and so on while it compare to ordinary mechanical locks. At present, the electronic code lock is most used of SCM technology 。

In practice, however, the process easy run to fly。

So the reliability of this system is poor。

The paper introduced a field programmable gate arrays FPGA devices to design electronic password lock 。

基于FPGA的信息加密系统的设计与实现

基于FPGA的信息加密系统的设计与实现信息加密系统已经成为现代社会不可或缺的一部分,它可以保护数据的安全性,并且只有授权的人才可以访问敏感数据。

在过去,人们使用软件来实现加密,但随着科技的发展,硬件加密系统也变得越来越普及。

其中,基于FPGA的信息加密系统在其高速性、可编程性和低功耗等方面得到了广泛的应用。

本文将介绍一个基于FPGA的信息加密系统的设计与实现,包括加密算法的选择、系统架构的设计和关键技术的分析等内容。

一、加密算法的选择在设计一个基于FPGA的信息加密系统时,首先需要选择一个成熟的加密算法。

这里选择了AES算法作为核心加密算法。

AES算法是一种对称密钥加密算法,具有高速性和强大的安全性。

它的加密过程采用了分组密码的设计,将明文按照一定的规则分组加密,而密文则通过不断的子密钥加密得到。

为了进一步提高AES的安全性,可以加入其他算法作为补充,例如SM4算法、RSA算法等等。

二、系统架构的设计在确定了加密算法之后,接下来需要设计基于FPGA的信息加密系统的架构。

在本文中,我们采用了一种包含FPGA、RAM、Flash和外设等核心组件的架构。

具体来说,我们可以通过选择一款性能优良的FPGA芯片(例如Xilinx Kintex-7系列),并将其与高带宽的DDR3 RAM、大容量的Flash存储器以及各种外设(例如网卡、USB接口等等)相结合,形成一个完整的信息加密系统。

在设计系统架构时,需要考虑到以下因素:1. 性能:系统需要具有高速性,能够保证数据的快速加密和解密。

2. 可编程性:FPGA的可编程性使得系统可以满足不同的加密需求,并且方便进行升级和维护。

3. 安全性:系统需要具有强大的安全性,能够保护用户的数据免受攻击和窃取。

三、关键技术的分析在实现基于FPGA的信息加密系统时,还需要掌握一些关键技术。

以下是几个主要的技术点:1. 高速数据传输:为了保证系统的高速性,需要采用高速数据传输协议,如PCIe、Ethernet等等。

基于FPGA的AES加密算法设计与实现

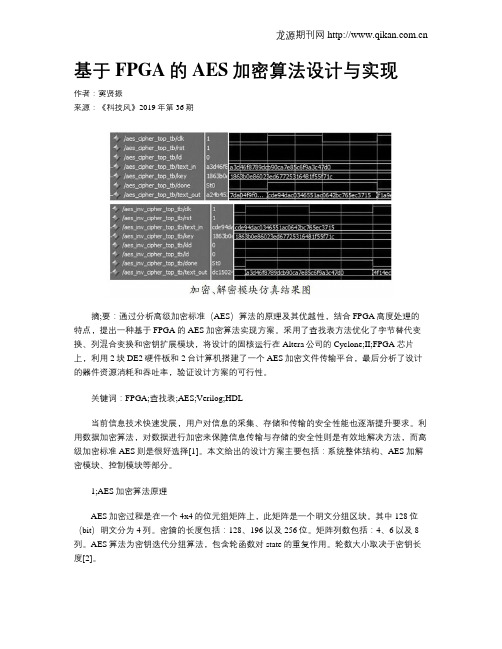

基于FPGA的AES加密算法设计与实现作者:窦贤振来源:《科技风》2019年第36期摘;要:通过分析高级加密标准(AES)算法的原理及其优越性,结合FPGA高度处理的特点,提出一种基于FPGA的AES加密算法实现方案。

采用了查找表方法优化了字节替代变换、列混合变换和密钥扩展模块,将设计的固核运行在Altera公司的Cyclone;II;FPGA芯片上,利用2块DE2硬件板和2台计算机搭建了一个AES加密文件传输平台,最后分析了设计的器件资源消耗和吞吐率,验证设计方案的可行性。

关键词:FPGA;查找表;AES;Verilog;HDL当前信息技术快速发展,用户对信息的采集、存储和传输的安全性能也逐渐提升要求。

利用数据加密算法,对数据进行加密来保障信息传输与存储的安全性则是有效地解决方法,而高级加密标准AES则是很好选择[1]。

本文给出的设计方案主要包括:系统整体结构、AES加解密模块、控制模块等部分。

1;AES加密算法原理AES加密过程是在一个4x4的位元组矩阵上,此矩阵是一个明文分组区块。

其中128位(bit)明文分为4列。

密鑰的长度包括:128、196以及256位。

矩阵列数包括:4、6以及8列。

AES算法为密钥迭代分组算法,包含轮函数对state的重复作用。

轮数大小取决于密钥长度[2]。

AES解密过程和加密过程互为逆运算,解密过程主要包含四个方面:逆行移位、逆字节替换、轮密钥加以及逆列混合。

AES加密需要Nb个字节的初始密钥及Nr轮迭代过程所需轮密钥,所以密钥生成算法需将初始密钥扩展为Nb(Nr+1)个字。

2;AES加密算法建模与设计系统整体结构主要包括:接口模块、AES加解密模块、串并转换和并串转换模块以及LCD显示模块。

通过硬件平台DE2的开关来选择工作模式,LCD显示屏显示系统“Mode:Encryption或Decryption”。

计算机通过串口将数据发送到DE2,接口模块收到数据后送到串并转换模块,处理后将数据发送到AES加解密模块,根据模式选择将数据送到相应模块,完成加密或者加密后将数据发送到并串转换模块,然后将数据发送到接口模块完成数据加密或解密。

基于Verilog硬件描述语言的AES密码算法实现

基于Verilog硬件描述语言的AES密码算法实现密码模块是平安保密系统的重要组成部分,其核心任务就是加/解密数据。

目前,分组密码算法AES以其高效率、低开销、实现容易等特点被广泛应用于密码模块的研制。

随着计算机信息技术和超大规模技术的成熟与进展,通过硬件来实现密钥模块的内部运作,可保证在外界无密钥的明文流淌,能够实现真正意义上的保密。

此外,硬件实现还具有高速、高牢靠性等特点。

目前许多AES算法的硬件实现采纳基于RAM查找表方式来实现算法中最关键的SubBytes部分。

本文采纳复合域来实现SubBytes部分的求逆运算,以便于采纳组合规律减小面积。

同时采纳加/解密运算中列变换的部分举行复用,从而进一步节约实现面积。

这样可以使AES密码应用于系统,IC卡等面积要求较小的场合。

1 AES算法简介AES算法是一种迭代型分组密码,其分组长度和密钥长度均可变,各自可以自立指定为128 b,192 b,256 b。

本文主要研究分组长度和密钥长度为128 b的状况。

AES算法是将输入的明文(或密文)分成16个字节,在第一个Add Round Keys变换后进入10轮迭代。

迭代过程的前9轮彻低相同,依次经过字节代替(substitute bytes)、行移位(shift rows)、列混合(mixcolumns)、轮密钥加(add round keys),最后一轮则跳过了列混合(mix columns)。

解密过程与加密过程类似,但执行挨次与描述内容有所不同,因此AES算法的加解密运算需要分离实现。

2 AES算法的硬件设计按照AES算法的原理和基本结构,将囫囵AES算法模块分成4个相对自立的子模块:接口模块、控制单元模块、加解密运算模块、密钥扩展模块。

本文所设计的密码算法不包括密钥发生器,所用的密钥通过接口模块由外部输入,加解密运算后的数据经输出接口输出。

AES算法模块的总体结构1所示。

2.1 接口模块的设计输入接口模块的主要任务是:将数据传送到加解密运算模块,将外部输入的密钥传送到密钥扩展模块。

AES加密算法的一种优化的FPGA实现方法

随着密码分析水平,芯片处理能力和计算技术的不断进步,DES的安全强度已经难以适应新的安全需要,其实现速度、代码大小和跨平台性均难以继续满足应用需求。

因此,NIST(美国国家标准与技术研究所)筹划AES(高级数据加密标准)算法,旨在取代DES,以保护21世纪敏感政府信息的新型加密标准。

Rijndael算法以其简洁、高效、安全和原则性的设计被接纳为AES,并于2001年11月26日正式公布在FIPS(Federal Information Processing Standards)出版的FIPS-PUB 197中。

作为DES的继承者,AES自从被接纳为标准之日起就已经被工业界、银行业和行政部门作为事实上的密码标准。

随着网络传输速度提升为gigabits数量级,业界对算法的执行速度的要求也越来越高,基于软件的密码算法便显得性能不足,需要采用硬件加密的方式,他采用一些特殊的优化技术(如流水线和查找表等),可极大地提高数据的流量并减少密钥的生成时间。

另外,用硬件实现加密算法及与之相关的密钥生成过程,并且封装到芯片中,因为他们不易被外部攻击者读取或更改,会有较高的物理安全性。

因此,基于硬件的密码算法就受到业界的普遍关注。

以FPGA为代表的可重构硬件以其自身所固有的特点——既具有硬件的安全性和高速性又有软件的灵活性和易维护性,已经成为分组密码算法硬件实现的热点研究方向。

本文介绍AES加密算法的一种FPGA实现的方法以及对其加密速度的优化处理技巧。

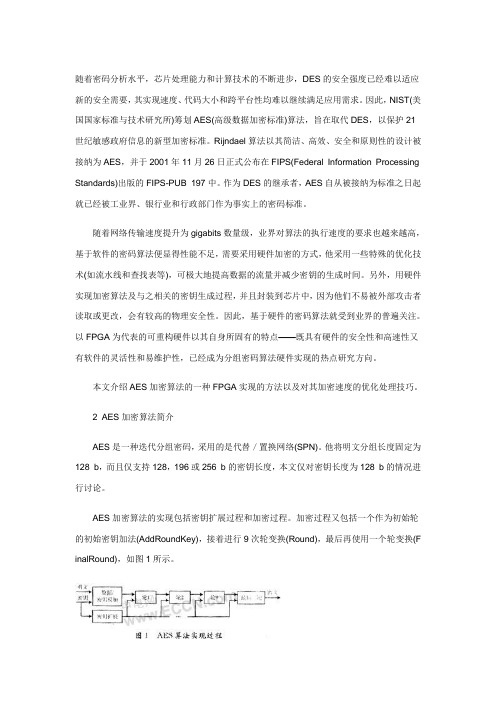

2 AES加密算法简介AES是一种迭代分组密码,采用的是代替/置换网络(SPN)。

他将明文分组长度固定为128 b,而且仅支持128,196或256 b的密钥长度,本文仅对密钥长度为128 b的情况进行讨论。

AES加密算法的实现包括密钥扩展过程和加密过程。

加密过程又包括一个作为初始轮的初始密钥加法(AddRoundKey),接着进行9次轮变换(Round),最后再使用一个轮变换(F inalRound),如图1所示。

基于FPGA的高性能数据加密与解密系统设计与实现

基于FPGA的高性能数据加密与解密系统设计与实现随着信息技术的迅猛发展,数据的安全性问题日益突出。

为了保护敏感信息的机密性,数据加密与解密技术成为了当今社会中不可或缺的一部分。

在这篇文章中,我们将探讨基于FPGA(现场可编程门阵列)的高性能数据加密与解密系统的设计与实现。

一、引言数据加密与解密是保护数据安全和隐私的关键技术。

传统的软件实现数据加密与解密在处理大规模数据时会遇到性能瓶颈的问题。

相较于软件实现,FPGA在加密与解密的计算密集型任务上具有显著的优势。

FPGA具备并行计算能力,可以加速加密与解密算法的执行速度。

本文将阐述基于FPGA的高性能数据加密与解密系统设计与实现的方法与步骤。

二、数据加密与解密算法选择在设计数据加密与解密系统之前,我们首先需要选择合适的加密与解密算法。

常见的对称加密算法包括DES(数据加密标准),3DES(Triple DES)和AES(高级加密标准)。

而非对称加密算法包括RSA(Rivest-Shamir-Adleman)和椭圆曲线密码算法等。

对于高性能的加密与解密系统,我们选择了AES算法作为基础。

AES算法使用分组密码,适合在FPGA上进行硬件加速。

其具备较高的安全性和执行速度,因此是许多数据通信和存储系统中使用的主要加密算法。

三、FPGA高性能数据加密与解密系统设计1. 系统架构设计基于FPGA的高性能数据加密与解密系统的设计需要考虑多个模块的协同工作。

该系统的主要模块包括数据缓存模块、加密/解密算法模块、协议控制模块和数据传输接口模块等。

- 数据缓存模块:负责临时存储输入和输出的数据,减少对外部存储器的访问延迟。

- 加密/解密算法模块:实现AES加密/解密算法,包括轮密钥生成、字节代换、行移位、列混淆等操作。

- 协议控制模块:负责控制系统的工作流程,包括输入数据的传输、加密/解密操作的控制和输出数据的传输等。

- 数据传输接口模块:与外部系统进行数据的输入和输出。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于VERILOG的AES加密算法的实现摘要:随着信息产业在我国国民经济中扮演越来越重要的角色,信息技术的发展和数据传输的安全性受到了有关部门的重视,加强网络信息安全的加密产品具有广泛的应用前景。

此课题主要研究了基于VERILOG硬件描述语言的AES加密算法原理及优化,以及设计硬件实现。

本文先介绍了先进加密算法(AES)的原理,同时讲述了其与Rijndael设计的异同。

安全,高效,易拓展优化,硬件实现简单是其的特点,同时,本文还研究了算法实现的关键技术。

在设计过程中,完成了整体结构的规划和各部分的端口的定义,用VERILOG语言完成了电路的RTL级的描述,同时使用了Model公司的Modelsim仿真工具进行了软件平台上的仿真,实现了128位比特密钥的加密解密的逻辑功能,硬件上使用了基于Xilinx公司的VIRTEX系列芯片,并用Synplify 软件进行了FPGA综合,仿真基本达到了要求,这也证明了设计的正确性。

在设计中尤其要提到的是本文采用了ECB(电子密码本)加密算法模式,采用流水线结构,提高了电路的工作频率和速度,本设计的创新点在于用语言实现S盒变换时,并没有采用传统的查表方式,而是直接采用了算法描述,相较之下,节省了电路的存储面积,实现了优化。

关键字:Verilog,AES,先进加密标准,Rijndael设计,FPGA,加密,高速,流水线结构The implement of AES encrypt arithmetic base on Verilog HDL06204518 YuhuanSupervised by Zheng LixiaAbstract:With the information industry plays more important role in the country economy, the development of communication technique and security of data transfer is taken serious by some government department. The encrypt product which is used to strengthen net information security has extensive foreground. This subject mainly investigate AES encrypt arithmetic principium and its upgrade, then offer the design of hardware implement.This subject introduce the principium of AES arithmetic first, at the same time, it gives the similarities and differences. The AES arithmetic contains following characteristic: security, high efficiency, easy optimized, easy progress of hardware implement. The subject introduces the pivotal technique of the implement and attentions at the same time. Within the process of designing, I complete the programming of whole configuration and the defining of port of each part, complete the RTL description of circuit with Verilog HDL. And I complete the emulation which is based on software with Modelsim which is the product of Model Co. It achieves the logic function of 128 bit key. I use the CMOS chip of Virtex series which comes from Xilinx Co., and carry through synthesis using the software of Synplify. The result of the synthesis is reach the request of design, it prove the correctness of the design. I should mention especially that I use the ECB encrypt arithmetic mode and pipelining configuration which advances work frequency and work speed. The innovative point lies to the mode of the implement of s-box transform. I don’t use the mode of looking through the table. It save the area of ROM and implement the upgrade.Key words: Verilog, AES, advanced encrypt standard, Rijndael design, FPGA, encrypt, high speed, pipelining configuration.目录摘要 (I)关键字 (I)Abstract. (II)Key words (II)第一章绪论 (1)1.1密码学简介和我国信息安全现状 (1)1.2 数据加密标准的发展过程 (2)1.2.1数据加密标准DES (2)1.2.2 高级加密标准AES (2)1.3 AES的研究现状 (3)1.3.1 算法的研究现状 (3)1.3.2 硬件实现的研究现状 (3)1.4 本论文的意义 (5)1.5 内容和创新 (5)1.6 本章小结 (5)第二章 AES加密算法原理介绍和安全性能分析 (6)2.1 Rijndael和AES的区别 (6)2.2 预备知识 (6)2.2.1 Rijdael的数学基础和设计思想 (7)2.2.2 字节运算(位运算) (9)2.2.3 四字节运算 (10)2.3 加密算法的四种主要工作模式 (11)2.4 加密算法原理描述 (13)2.5 AES加/解密算法的实现 (14)2.5.1 S盒变换 SubBytes() (15)2.5.2 行变换ShiftRows() (16)2.5.3 列变换Mixcolumns() (16)2.5.4 与扩展密钥的异或运算AddRoundKey() (17)2.5.5 密钥扩展程序 Key Expansion( ) (17)2.6 AES安全性能分析 (17)2.6.1安全性原则 (17)2.6.2 AES算法的安全性 (18)2.6.3AES算法的性能分析 (19)2.7 本章小结 (19)第三章开发环境介绍 (20)3.1 硬件描述语言 (20)3.2 Modelsim+Synplify+(Virtex-5)开发环境 (20)3.2.1 Modelsim (20)3.2.2 逻辑综合和综合工具Synplify (21)3.2.3 Xilinx Virtex-5系列FPGA (22)3.3 设计方法 (23)3.4 本章小节 (24)第四章 AES算法的FPGA设计 (25)4.1 FPGA实现系统分析 (25)4.1.1 软硬件实现方法比较 (25)4.1.2 性能参数 (26)4.1.3 关键技术 (26)4.2 整体结构设计 (28)4.2.1 总体设计方案 (28)4.2.2 总体系统结构框图 (30)4.3 各系统分支设计 (31)4.3.1 加解密模块的设计 (31)4.3.2 控制模块设计 (33)4.3.3 密钥扩展模块设计 (34)4.3.4 接口模块设计 (35)4.4 编码实现 (36)4.5 本章小节 (37)第五章系统的仿真和测试 (38)5.1 仿真测试简介 (38)5.2 Modelsim功能仿真 (38)5.3 Synplify 综合和时序分析 (43)第六章结论和展望 (44)致谢 (45)参考文献 (46)基于VERILOG的AES加密算法的实现第一章绪论计算机技术和网络技术的发展极大丰富了人们的眼界和接受外界信息的方式,大量敏感重要信息通过公用通信设施和计算机网络进行交换。

因此,处理高效的加密和解密数据信息的密码学重新进入人们的视线,它很好的解决了数据机密性保护和身份认证等方面的难题。

绪论部分我将介绍密码学的一些概况和数据加密标准的发展过程,接着讨论一下高级加密标准的研究现状,最后给出本文研究的内容和意义以及创新等。

1.1密码学简介和我国信息安全现状密码学的基本思想是对机密信息进行交换,以保护信息在传送过程中不被非法窃取、解读和利用。

密码体制的分类方法有很多,一般是通过加密算法与解密算法所使用的密钥是否相同的原则分为:对称密钥密码体制和公开密钥密码体制。

后者一般基于一个数学上的实现,适用于开放的使用环境,可以安全方便的实现数字签名和认证,通常用于密钥的分配与传输上,但对数据加、解密的速度较慢。

而前者的安全性基于复杂的非线性变换,由于其加密速度比公钥密码相对较快,因此是目前商业领域比较重要而流行的一种加密体制。

对称密钥密码体制从加密模式上又可分为:序列密码和分组密码。

序列密码使用密钥短的位串生成长的位串,然后再与明文按位模2相加产生密文,它的安全基于密钥的随机性。

如果密钥是真正的随机数,则这种密码体制在理论上就是不可攻破的,这也可以称为一次一密乱码本体制。

严格的该体制所需的密钥量不存在上限,且很难得到真正意义上的随机数序列。

实际中更多的是采用伪随机数序列。

为了提高安全强度,伪随机序列的周期要足够长,并且序列要有很好的随机性,但这也很难做到,因此除了一些高度保密的环境以外,很少使用。

应用在网络通信环境中的数据加密方法更多的是采用分组加密体制。

分组密码算法通常由加、解密算法和密钥扩展算法两部分组成,密钥扩展算法用于生成m个子密钥。