中电智能卡 COB工艺流程简介

COB封装工艺流程

COB封装工艺流程COB(Chip on Board)封装工艺是将芯片直接封装到印制电路板(PCB)上,通过将芯片粘贴焊接到金属基板上,然后进行封装和封装材料填充,最后进行测试和包装。

下面将详细介绍COB封装工艺流程。

1.设计和制造金属基板:首先,根据芯片的需求,设计和制造金属基板。

金属基板通常由铜制成,其上有一层特殊的涂层,以提供与芯片的电气连接。

2.准备芯片:接下来,准备芯片,包括设计和制造芯片的晶圆。

晶圆是从单晶硅材料中切割出来的圆片,上面有许多芯片。

根据芯片的尺寸和功能要求,将芯片切割成可用的单个芯片。

3.粘贴芯片:将芯片粘贴到金属基板上。

这可以通过使用导热胶粘剂来实现。

首先,将导热胶粘剂均匀涂抹在金属基板上,然后将芯片粘贴到胶上。

确保芯片与基板的对其和位置准确。

4.焊接芯片:一旦芯片粘贴到金属基板上,就需要将芯片与基板进行焊接。

这可以通过热压焊接或激光焊接来实现。

焊接将芯片与基板的电气连接,确保信号和功率的传输。

5.封装和封装材料填充:在芯片粘贴和焊接后,将进行封装和封装材料填充。

封装是将芯片包围、保护和固定在一个外壳(封装)中的过程。

填充材料(如环氧树脂)将用于填充封装空间,并提供保护和固化。

6.测试:完成封装和封装材料填充后,需要进行测试以确保芯片的功能和性能。

这包括功能测试、电性能测试、温度测试等。

只有通过测试的芯片才能进入下一步。

7.包装:最后,经过测试的芯片将进行包装。

包装通常采用暗盒、接触型(FC)或无接触型(FO)等形式。

芯片将放置在包装中,并进行外部连接和引脚处理。

这样芯片就可以连接到其他设备或系统中使用了。

通过以上步骤,COB封装工艺能够实现将芯片直接封装到印制电路板上的目标。

这种封装方式具有空间效率高、散热好、电性能优秀等优点,因此在许多电子设备中得到广泛应用。

COB简介

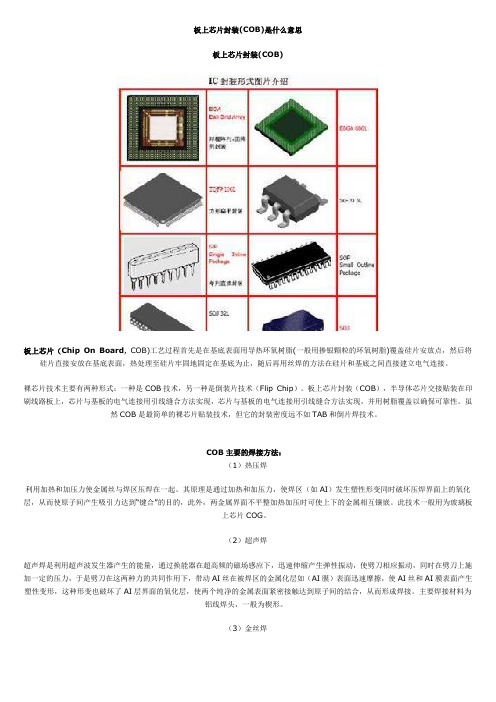

板上芯片封装(COB)是什么意思板上芯片封装(COB)板上芯片(Chip On Board, COB)工艺过程首先是在基底表面用导热环氧树脂(一般用掺银颗粒的环氧树脂)覆盖硅片安放点,然后将硅片直接安放在基底表面,热处理至硅片牢固地固定在基底为止,随后再用丝焊的方法在硅片和基底之间直接建立电气连接。

裸芯片技术主要有两种形式:一种是COB技术,另一种是倒装片技术(Flip Chip)。

板上芯片封装(COB),半导体芯片交接贴装在印刷线路板上,芯片与基板的电气连接用引线缝合方法实现,芯片与基板的电气连接用引线缝合方法实现,并用树脂覆盖以确保可靠性。

虽然COB是最简单的裸芯片贴装技术,但它的封装密度远不如TAB和倒片焊技术。

COB主要的焊接方法:(1)热压焊利用加热和加压力使金属丝与焊区压焊在一起。

其原理是通过加热和加压力,使焊区(如AI)发生塑性形变同时破坏压焊界面上的氧化层,从而使原子间产生吸引力达到“键合”的目的,此外,两金属界面不平整加热加压时可使上下的金属相互镶嵌。

此技术一般用为玻璃板上芯片COG。

(2)超声焊超声焊是利用超声波发生器产生的能量,通过换能器在超高频的磁场感应下,迅速伸缩产生弹性振动,使劈刀相应振动,同时在劈刀上施加一定的压力,于是劈刀在这两种力的共同作用下,带动AI丝在被焊区的金属化层如(AI膜)表面迅速摩擦,使AI丝和AI膜表面产生塑性变形,这种形变也破坏了AI层界面的氧化层,使两个纯净的金属表面紧密接触达到原子间的结合,从而形成焊接。

主要焊接材料为铝线焊头,一般为楔形。

(3)金丝焊球焊在引线键合中是最具代表性的焊接技术,因为现在的半导体封装二、三极管封装都采用AU线球焊。

而且它操作方便、灵活、焊点牢固(直径为25UM的AU丝的焊接强度一般为0.07~0.09N/点),又无方向性,焊接速度可高达15点/秒以上。

金丝焊也叫热(压)(超)声焊主要键合材料为金(AU)线焊头为球形故为球焊。

COB工艺制程简介

COB工艺制程简介1.芯片的焊线连接:1.1芯片直接封装简介:现代消费性电子产品逐渐走向轻、薄、短、小的潮流下,COB(Chip On Board)已成为一种普遍的封装技术。

COB的关键技术在于Wire Bonding(俗称打线)及Molding (封胶成型),是指对裸露的集成电路芯片(IC Chip),进行封装,形成电子组件的制程,其中IC藉由焊线(Wire Bonding)、覆晶接合(Flip Chip)、或卷带接合(Tape Automatic Bonding;简称TAB)等技术,将其I/O经封装体的线路延伸出来。

集成电路芯片必须依照设计和外界的电路连接,方能成为具有一定功能的电子组件就如我们所看到的"IC"就是这种已封装好、有外引脚的封装的集成电路。

1.2芯片的焊线连接方式简介:IC芯片必须与封装基板完成电路连接才能发挥既有的功能,现时市面上流行的焊线连接方式有三类 :打线接合(Wire Bonding)、卷带自动接合(Tape Automated Bonding,TAB)与覆晶接合(Flip Chip,FC),分述如下:1.2.1打线接合(Wire Bonding)打线接合是最早亦为目前应用最广的技术,此技术首先将芯片固定于导线架上,再以细金属线将芯片上的电路和导线架上的引脚相连接。

而随着近年来其它技术的兴起,打线接合技术正受到挑战,其市场占有比例亦正逐渐减少当中。

但由于打线接合技术之简易性及便捷性,加上长久以来与之相配合之机具、设备及相关技术皆以十分成熟,因此短期内打线接合技术似乎仍不大容易为其它技术所淘汰。

图1.2a打线接合的示意图1.2.2卷带式自动接合(Tape Automated Bonding,TAB)卷带式自动接合技术首先于1960年代由通用电子(GE)提出。

卷带式自动接合制程,即是将芯片与在高分子卷带上的金属电路相连接。

而高分子卷带之材料则以polyamide为主,卷带上之金属层则以铜箔使用最多。

COB技术详解

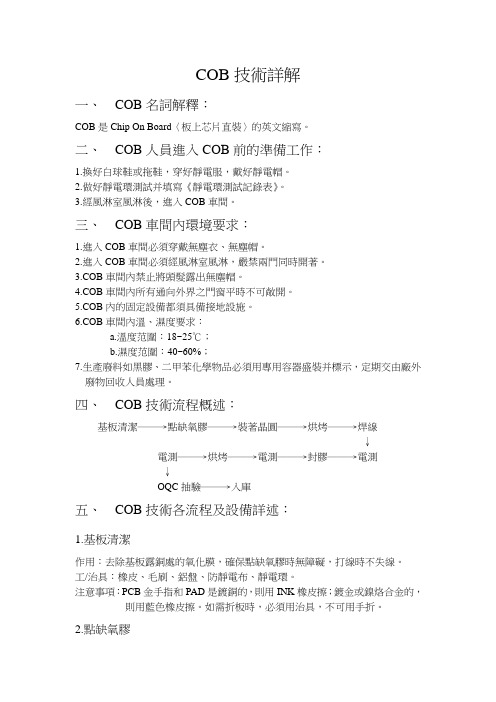

COB技術詳解一、COB名詞解釋:COB是Chip On Board〈板上芯片直裝〉的英文縮寫。

二、COB人員進入COB前的準備工作:1.換好白球鞋或拖鞋,穿好靜電服,戴好靜電帽。

2.做好靜電環測試并填寫《靜電環測試記錄表》。

3.經風淋室風淋後,進入COB車間。

三、COB車間內環境要求:1.進入COB車間必須穿戴無塵衣、無塵帽。

2.進入COB車間必須經風淋室風淋,嚴禁兩門同時開著。

3.COB車間內禁止將頭髮露出無塵帽。

4.COB車間內所有通向外界之門窗平時不可敞開。

5.COB內的固定設備都須具備接地設施。

6.COB車間內溫、濕度要求:a.溫度范圍:18~25℃;b.濕度范圍:40~60%;7.生產廢料如黑膠、二甲苯化學物品必須用專用容器盛裝并標示,定期交由廠外廢物回收人員處理。

四、COB技術流程概述:基板清潔──→點缺氧膠──→裝著晶圓──→烘烤──→焊線↓電測──→烘烤──→電測──→封膠──→電測↓OQC抽驗──→入庫五、COB技術各流程及設備詳述:1.基板清潔作用:去除基板露銅處的氧化膜,確保點缺氧膠時無障礙,打線時不失線。

工/治具:橡皮、毛刷、鋁盤、防靜電布、靜電環。

注意事項:PCB金手指和PAD是鍍銅的,則用INK橡皮擦;鍍金或鎳烙合金的,則用藍色橡皮擦。

如需折板時,必須用治具,不可用手折。

2.點缺氧膠作用:點粘著劑,使晶圓能夠裝著在PCB的PAD上。

工/治具:針頭、針筒、防靜電布、靜電環。

材料:常用粘著劑有缺氧膠〈紅膠〉、黑膠〈混合膠、冷膠〉、銀漿。

操作步驟:操作人員在配戴好靜電環的情況下,手持灌好缺氧膠的針筒,將缺氧膠點在裝著晶圓的PAD上。

材料具體作用及適用產品:‧缺氧膠:粘性一般,價格便宜。

一般用於P1058、P1205、P1128等英新達系列產品。

‧銀漿:導電性和粘性很好,價格較貴,目前只用於正運達的XO產品。

‧黑膠:粘性好,價格比銀漿便宜,目前用於HP系列產品。

〈HP系列有HP103,HP103C,HPCPU,HPCPUC〉注意事項:‧膠量適中均勻,如果膠量過多易溢到金手指上;膠量過少,晶圓裝著不上。

cob与csp的制造流程

cob与csp的制造流程英文回答:Cob and CSP are two different manufacturing processes used in various industries.Cob, short for Chip-On-Board, is a technology used in electronic packaging where the bare integrated circuit (IC) chip is directly mounted onto a printed circuit board (PCB). The process involves wire bonding the IC chip to the PCB, followed by encapsulation to protect the chip from external elements.The manufacturing process of Cob typically involves the following steps:1. PCB fabrication: The first step is to fabricate the PCB, which involves designing the circuit layout, etching the copper tracks, and drilling holes for component placement.2. Wire bonding: The IC chip is then wire bonded to the PCB using fine wires made of gold or aluminum. This process involves making electrical connections between the chip and the PCB by bonding the wires to the appropriate contact points.3. Encapsulation: After wire bonding, the IC chip is encapsulated with a protective material, such as epoxy resin or silicone gel. This encapsulation provides mechanical support and protects the chip from moisture, dust, and other contaminants.4. Testing and inspection: Once the encapsulation is complete, the assembled Cob module undergoes rigorous testing and inspection to ensure its functionality and quality. This includes electrical testing, visual inspection, and functional testing.CSP, short for Chip Scale Package, is another packaging technology used in the semiconductor industry. In CSP, the IC chip is packaged in a compact form factor that is asclose to the size of the chip itself. This allows for higher packaging density and smaller form factors in electronic devices.The manufacturing process of CSP generally includes the following steps:1. Die preparation: The first step is to prepare the IC chip for packaging. This involves singulating the chips from the wafer and testing them for functionality.2. Substrate fabrication: A substrate is prepared, which acts as the base for mounting the IC chip. The substrate is typically made of materials like ceramic or organic laminate.3. Die attach: The IC chip is then attached to the substrate using conductive adhesive or solder. This process ensures a secure and reliable connection between the chip and the substrate.4. Wire bonding or flip chip bonding: Depending on thespecific CSP design, wire bonding or flip chip bonding may be used to make electrical connections between the IC chip and the substrate. Wire bonding involves using fine wires to connect the chip to the substrate, while flip chip bonding involves directly bonding the chip to the substrate using solder bumps.5. Encapsulation: Similar to Cob, the CSP module is encapsulated with a protective material to provide mechanical support and protect the chip from external elements.6. Testing and inspection: Finally, the assembled CSP module undergoes testing and inspection to ensure its functionality and quality.中文回答:Cob和CSP是用于各个行业的两种不同的制造工艺。

COB制作工艺流程及设备应用情况

COB制作工艺流程及设备应用情况COB (Chip on Board)制作工艺流程及设备应用情况COB制作工艺是将电子芯片(IC)直接粘贴在线路板(PCB)的表面上,然后通过线缆进行电路连接的一种封装技术。

相比于传统的封装技术,如QFP、BGA等,COB制作工艺具有尺寸小、重量轻、成本低等优势。

在COB制作过程中,需要使用到一系列设备:1.IC贴装机:IC贴装机是COB制作过程中最关键的设备之一、它用于将IC芯片精确地贴在PCB上,贴装机通过引导针、真空吸附等机械手段将IC精准地定位在PCB的特定位置上,并确保IC与PCB的电路相连。

2.热压机:在IC贴装完成后,需要使用热压机将IC芯片与PCB进行牢固的黏合。

热压机通过加热和压力的双重作用,将IC芯片与PCB上的导电胶水进行固化,从而确保芯片在使用过程中不会脱落。

3.焊接设备:在COB制作工艺中,还需要进行电路的连线焊接。

这个过程通常使用焊锡丝和焊锡炉来完成。

焊锡丝在炉子中熔化,然后通过机械移动或人工操作,将焊锡丝与芯片引脚和PCB上的焊盘连接。

4.清洗设备:在COB制作完成后,需要对PCB进行清洗,以去除焊锡残留物、胶水残留物等杂质。

清洗设备通常使用喷淋式清洗机,使用喷淋喷头将清洗液均匀地喷洒在PCB上,然后通过高压水流将杂质冲走。

以上是COB制作工艺中常用的设备,下面将介绍COB制作的工艺流程:1.PCB准备:首先,需要准备好空的PCB板,并进行表面处理,以提高黏附性和贴装质量。

2.粘贴IC芯片:使用IC贴装机将IC芯片粘贴到PCB上的特定位置。

贴装机通过引导针和真空吸附等方式,确保IC芯片的正确定位和黏附。

3.热压黏合:将贴好的IC芯片和PCB放入热压机中,通过加热和压力,将芯片与PCB的导电胶水进行牢固黏合。

4.连线焊接:使用焊锡丝和焊锡炉,将IC芯片的引脚与PCB上的焊盘进行焊接,以建立电路连接。

5.清洗:使用清洗设备对PCB进行清洗,以去除焊锡残留物、胶水残留物等杂质。

芯片减划工艺 中电智能卡

中电智能卡有限责任公司COB封装厂减薄划片工艺介绍减薄划片工艺介绍—生产流程减薄划片工艺介绍背面减薄 贴磨片膜 抛光 贴划片膜 揭磨片膜 划片团队协作,共创辉煌!减薄划片工艺介绍—贴磨片膜Chuck table CCD Alignme ntRobotDouble load portWork flow:Wafer load Wafer alignmentBG tape laminatingW f unload Wafer l d团队协作,共创辉煌!减薄划片工艺介绍—贴磨片膜Machine specification: 1.Wafer size 8 inch O.F., 8 inch V-notch, 12 inch wafer thickness ≧300μm;V-notchO.F.团队协作,共创辉煌!减薄划片工艺介绍—贴磨片膜2.Load port 8 inch wafer: wafer cassette, FOSB 12 inch wafer: FOUP, FOSBWafer cassetteFOUP团队协作,共创辉煌!减薄划片工艺介绍—贴磨片膜3. 磨片膜型号 Tape Type: UV tape, blue tape, bump tape; Tape Width:230~340mm; Tape Thickness:100~300 μm;团队协作,共创辉煌!减薄划片工艺介绍—背面减薄和贴划片膜Machine model: DGP8761+DFM2800 DFM2800 DGP8761 3 主轴,4磨片平台团队协作,共创辉煌!减薄划片工艺介绍—背面减薄和贴划片膜生产流程:1) ) Cassette 2) Transfer with robot pick 3) Alignment at the position table 4) To C/T with transfer arm 1 5) Rough grinding with Z1‐axis 6) Fine grinding with Z2‐axis 7) Dry ry polish with Z3 3‐axis 8) Wafer cleaning at C/T 9) To Spinner with transfer arm 2 10) Wafer cleaning / dry at spinner section 11) To DFM2800 UV irradiation 12)Transfer to the mounting table 13) Dicing tape mounting using ring 14) Transfer to the peeling table 15) Back grinding tape peeling 16) Load wafer to the frame cassette团队协作,共创辉煌!减薄划片工艺介绍—背面减薄和贴划片膜1. Z1/Z2 Spindle: Diamond wheel, Φ300mm; Z3 Spindle: Dry polishing wheel,为海绵,Φ450mm; 同时选配 G tti DP Getting DP, 可以有效防止memory wafer f 的电迁移效应; 的电迁移效应2. Damage of back side#2000 Dry yp polishTEM (x 106)团队协作,共创辉煌!减薄划片工艺介绍—背面减薄和贴划片膜Wafer厚度控制1. Z1 axis配置1套Inline process gauge Z1 axis i 配置2个Inline li process gauge, 厚度检测范围为0~1800um;Z1轴磨片速度分为 3段, 速度范围:0.1um/s~80um/s。

板上芯片封装的焊接方法及工艺流程简述

板上芯片封装的焊接方法及工艺流程简述板上芯片封装的焊接方法及工艺流程简述发布时间: 2013-6-13 22:13 发布者: qq8426030板上芯片封装(COB),半导体芯片交接贴装在印刷线路板上,芯片与基板的电气连接用引线缝合方法实现,芯片与基板的电气连接用引线缝合方法实现,并用树脂覆盖以确保可靠性。

虽然COB是最简单的裸芯片贴装技术,但它的封装密度远不如TAB和倒片焊技术。

板上芯片(Chip On Board, COB)工艺过程首先是在基底表面用导热环氧树脂(一般用掺银颗粒的环氧树脂)覆盖硅片安放点,然后将硅片直接安放在基底表面,热处理至硅片牢固地固定在基底为止,随后再用丝焊的方法在硅片和基底之间直接建立电气连接。

与其它封装技术相比,COB技术价格低廉(仅为同芯片的1/3左右)、节约空间、工艺成熟。

但任*技术在刚出现时都不可能十全十美,COB技术也存在着需要另配焊接机及封装机、有时速度跟不上以及PCB贴片对环境要求更为严格和无法维修等缺点。

某些板上芯片(CoB)的布局可以改善IC信号性能,因为它们去掉了大部分或全部封装,也就是去掉了大部分或全部寄生器件。

然而,伴随着这些技术,可能存在一些性能问题。

在所有这些设计中,由于有引线框架片或BGA标志,衬底可能不会很好地连接到VCC或地。

可能存在的问题包括热膨胀系数(CTE)问题以及不良的衬底连接。

COB主要的焊接方法:(1)热压焊利用加热和加压力使金属丝与焊区压焊在一起。

其原理是通过加热和加压力,使焊区(如AI)发生塑性形变同时破坏压焊界面上的氧化层,从而使原子间产生吸引力达到“键合”的目的,此外,两金属界面不平整加热加压时可使上下的金属相互镶嵌。

此技术一般用为玻璃板上芯片COG。

(2)超声焊超声焊是利用超声波发生器产生的能量,通过换能器在超高频的磁场感应下,迅速伸缩产生弹性振动,使劈刀相应振动,同时在劈刀上施加一定的压力,于是劈刀在这两种力的共同作用下,带动AI丝在被焊区的金属化层如(AI膜)表面迅速摩擦,使AI丝和AI 膜表面产生塑性变形,这种形变也破坏了AI层界面的氧化层,使两个纯净的金属表面紧密接触达到原子间的结合,从而形成焊接。

COB封装工艺流程参考文档

2、配粉硅胶

硅胶:

与荧光粉有较好的兼容 性,需要较长时间的搅 拌,易沉淀,粘度大, 胶量变异大,白光颜色 不均匀,往往有黄圈。

优点: 1、耐蓝光辐射,光衰小。 2、弹性体,防止产生裂 胶。 3、抗紫外线能力强。 4、散热性好。

测试分光

测试分BIN项目 1.光通量 2.显色指数 3.相关色温 5.电压 6.电流 7.电性不良

老化测试

喷码、包装入库

可根据客户需求进行喷码、包装。

COB介绍

COB封装工艺流程

F 发光原理

前景

什么是LED发光二极管

LED发光原理

1 基本原理

➢ 周期表 ➢ LED晶片的元素为III-V族化合半单体

注意:

1.点粉时注意空气洁净度, 人员需带口罩和无尘手套。 2.严禁点粉时接触橡胶制品 3.严禁附近有化学品和易挥 发液体。如:丙酮、酒精等 。

5抽真空

抽出点粉时产生的气泡

注意事项。

真空箱必须洁净

抽真空的时间和温度。

6.烘烤

检测成品与样品颜色和 光斑是否一致。

使用加热板对点粉的材 料进行初步烘烤。

IB IIB III IV V VI VII

B硼 C N氮 O F Al 鋁 Si P 磷 S CL Cu Zn Ga鎵 Ge As 砷 Se Br Ag Cd In 銦 Sn Sb 銻 Te I

➢ 材料的排列模式: Si (硅) • 原子內各层的稳定电子数: 2, 8, 8, …..个

• 矽的外层电子 数为4个电子

➢ N-type的排列模式: Si (硅)+ As(砷)

• 在Si(硅)的排列中 放入As(砷),则将 多出一个电子, 在结 构上称为带负电 (Negative),故定义为 N-type.

COB工艺流程及应用优缺点精讲

注意:对于防静电要求严格的产品要用离子吹尘机.

COB工艺流程-点胶

目的:固定晶片,防止在传递和邦线过程中晶片脱落. 方法: a. 针式转移法:用针从容器里取一小滴粘剂点涂在PCB上, 这是一种非常迅速的点胶方法. b. 压力注射法:将胶装入注射器内,施加一定的气压将胶挤 出来,胶点的大小由注射器针头口 径及加压时间和压力大 小决定. 胶点尺寸:按晶片(DIE)的类型, 尺寸,重量而定. 胶的种类:红胶,银胶. 注意:保证足够的粘度,同时胶不能污染邦线焊盘.

COB工艺流程-邦定

邦定:依邦定图所定位置把各邦线的两个焊点连接起来,使其达到电气与机械连接。 原理:在常温下利用超声机械振动带动丝线与镀膜进行摩擦,使氧化膜破碎,纯净的金属表 面相互接触,通过摩擦产生的热量使金属之间发生扩散,实现连接. a. 铝线邦定: b. 金线邦定:

COB工艺流程-邦定

邦定机主要参数 压力:向铝线施予的压力 功率:超声震动的幅度 弧度:由整段线路的最高点与晶片 最高点间的距离,晶片厚度越高, 弧度越大. 熔合时间:铝线与介面亙相熔合所 需的时间.

COB封装的优缺点

与COB类似的电路组装技术还有柔性电路板上芯片(chip on film,COF) 和玻璃板上芯片(chip on glass,COG)。前者用于柔性印制电路板电路 中,后者用于液晶显示面板等产品制造中。其互连方式也是如图5.4.5 所示的方式。 由于传统封装成本较高,一般占集成电路总成本的40%甚至更高, 采用COB技术,省去了封装成本,可显著降低产品制造成本,在大批 量生产中尤为突出。此外,COB连接方式是封装技术中成熟的技术, 相应工艺、设备都可使用,不存在技术难题。 芯片直接安装到印制电路板上,从理论上说是最简洁的封装方式, 但由于缺少了中间引线的缓冲作用和封装外壳的保护作用,无法充分 保证可靠性,同时也无法维修,因而目前只运用在可靠性要求不高的 产品中,例如数字钟表、玩具、计算器、低成本数码产品等方面。但 随着技术进步,COB的可靠性也逐步提高,现在已扩展到电话卡、存 储卡、各种智能卡、打印机模块、存储器以及经济型数码相机等产品 中,因而在某些应用领域,COB有部分取代SMT之势。 由于COB技术兼有封装与组装技术要素,介于1级封装和2级封裴之间, 因此又称为1.5级封装。

中电智能卡 COB工艺流程简介

中电智能卡有限责任公司CSP及COB产品封装工艺简介1 / 22中电智能卡有限责任公司简介◆国内专业智能卡及模块制造企业。

下设COB封装厂、模块厂和卡厂,专业生产各种接触、非接触、双界面模块,双界面卡片,TF卡,大容量SIM及U-KEY等;◆公司年生产能力为:IC卡4亿张,接触和非接触模块5.1亿块,大容量SIM和TF卡2000万张。

◆完整的生产管理和质量控制体系,已获得ISO9000国际质量管理体系认证、中国移动SIM卡生产许可、国家质量监督局IC卡生产许可等多种资质。

公司良好的信誉和先进的生产技术,获得工信部和公安部认可,被指定为第二代身份证专用模块生产厂。

◆坚持“严格管理、规范操作、用户至上、创新技术、快速行动”的经营理念,用先进的制造技术,为国内外用户累计制造各种IC卡模块约30亿块,IC卡约15亿张。

2 / 22中电智能卡有限责任公司COB封装厂一、CSP封装工艺流程简介二、CSP技术应用于智能卡模块的生产优势三、COB封装工艺流程简介四、SIMpass/SDpass案例介绍五、COB封装厂产品介绍六、合作伙伴3 / 22➢工艺介绍➢CSP(Chip Scale Package),即芯片级封装,具有封装尺寸小,导电性能和散热性能好,制造工艺成熟等一系列的优点。

➢实用新型专利:ZL2.7;ZL2.2;ZL2.2。

发明专利:ZL20110039517.8倒贴装4 / 22➢流程介绍Wafer减薄RDL+SOLDER+划片印刷粘结剂芯片倒贴装Flip Chip 加热固化 curing 点胶固化测试Test5 / 226 / 22一、CSP 封装工艺流程介绍---RDL(重新布线技术)已钝化圆片 涂覆BCB(或PI) 光刻新/老焊区 溅射UBM(如Ti-Ni-Cu) 光刻UBM,使新/老焊区布线相连二次涂覆BCB(或PI) 光刻新焊区窗口 电镀(或印刷)焊料(膏) 再流,形成焊料球WLP 完成 WLP 测试/贴装/打印等一、CSP封装工艺流程介绍---Flip Chip➢ 工艺目的Flip Chip(倒封装工艺)通过倒封装技术将植球后的晶圆级芯片倒贴到载板焊点上,实现芯片与载板的电性导通.➢ 工艺步骤1.印刷粘结剂.2.芯片倒贴装.3.加热固化.4.点胶固化.7 / 22上手臂完成贴片下手臂拾取芯片上手臂接取芯片8 / 22➢传统载带模块工艺 ➢CSP 模块工艺●CSP 模块工艺中RDL+Solder 是 对整个WAFER 的布线植球,加工 效率极高;采用成熟的半导体倒贴 装工艺和点胶固化,成本降低。

【VIP专享】芯片减划工艺 中电智能卡

中电智能卡有限责任公司COB封装厂 减薄划片工艺介绍减薄划片工艺介绍—生产流程减薄划片工艺介绍贴磨片膜背面减薄 抛光贴划片膜揭磨片膜划片团队协作,共创辉煌!减薄划片工艺介绍—贴磨片膜CCD AlignmentChuck tableRobotWork flow:Wafer loadWafer alignment团队协作,共创辉煌!Double load portBG tape laminatingWafer unload减薄划片工艺介绍—贴磨片膜Machine specification: 1.Wafer size8 inch O.F., 8 inch V-notch, 12 inch wafer thickness ≧300μm;V-notch团队协作,共创辉煌!O.F.减薄划片工艺介绍—贴磨片膜2.Load port 8 inch wafer: wafer cassette, FOSB 12 inch wafer: FOUP, FOSBWafer cassette团队协作,共创辉煌!FOUP减薄划片工艺介绍—贴磨片膜3. 磨片膜型号 Tape Type: UV tape, blue tape, bump tape; Tape Width:230~340mm; Tape Thickness:100~300 μm;团队协作,共创辉煌!减薄划片工艺介绍—背面减薄和贴划片膜Machine model: DGP8761+DFM28003 主轴,4磨片平台DFM2800 DGP8761团队协作,共创辉煌!减薄划片工艺介绍—背面减薄和贴划片膜团队协作,共创辉煌!生产流程:1) Cassette 2) Transfer with robot pick 3) Alignment at the position table 4) To C/T with transfer arm 1 5) Rough grinding with Z1‐axis 6) Fine grinding with Z2‐axis 7) Dry polish with Z3‐axis 8) Wafer cleaning at C/T 9) To Spinner with transfer arm 2 10) Wafer cleaning / dry at spinnersection 11) To DFM2800 UV irradiation 12)Transfer to the mounting table 13) Dicing tape mounting using ring 14) Transfer to the peeling table 15) Back grinding tape peeling 16) Load wafer to the frame cassette减薄划片工艺介绍—背面减薄和贴划片膜1. Z1/Z2 Spindle: Diamond wheel, Φ300mm; Z3 Spindle: Dry polishing wheel,为海绵,Φ450mm; 同时选配Getting DP, 可以有效防止memory wafer的电迁移效应;2. Damage of back side#2000TEM (x 106)Dry polish团队协作,共创辉煌!减薄划片工艺介绍—背面减薄和贴划片膜Wafer厚度控制1. Z1 axis配置1套Inline process gauge Z1 axis配置2个Inline process gauge, 厚度检测范围为0~1800um;Z1轴磨片速度分为 3段, 速度范围:0.1um/s~80um/s。

COB流程及技术分析解读

冷胶

固化

将封好胶的COB放入烘箱,根据不同的胶体,调节 烘箱的温度和烘烤的时间,将胶体烘干固化。

封胶注意事项

1、胶体一般都要冷藏,故取用时一定要回至室温 后方可使用。每次取用量要按需用量而定。因胶在 常温下会有化学变化。 2、封胶时注意碰线问题,封胶范围及厚度,不可 露线。 3、封胶硬化条件要注意避免发生针孔、气泡、变 色情形,急速硬化会产生气泡孔及造成拉力过大, 严重时还会将线拉断。

测试

对于不同的产品,进行加电测试,检测产品的 功能是否正常,这是对邦定和IC的电性能测试。

注意事项

1、已邦好的线不能碰触任何物体。 2、检测前检验工装是否处于正常状态。 3、加电检测前检验电压等参数是否正常。

封胶

为保护邦定线和IC不在以后的搬运和生产过程中 损坏,在IC的表面滴一层黑胶,称之为封胶。 胶分为冷胶和热胶两种。对于不同的胶,封胶的 过程是不一样的。他们的主要区别在于: 对于冷胶,一般配胶时需添加稀释剂来调节胶体 流动性,调节封胶的高度。滴胶时PCB不用加热。 对于热胶,一般不要加稀释剂,而是用加热的方 法来调节胶体流动性。最好是将PCB预热到110℃ 。

胶体的典型参数

热胶 固化条件 150℃/20-30min 100~115℃/90~60min 热变形温度 120~125 ℃ 220℃ 3.4×1014 7×1014 表面电阻25℃ohm 11~13 抗拉强度 kg/mm2 17~19 5×1015 体积电阻:ohm-cm 3.2×1015 <0.15 0.25 膨胀系数:%

晶粒檢驗

1、檢驗的目的 2、檢驗的方法

•发现來料IC中外觀上的不良。 •有利於和IC的供應商責任劃分。 •通過50倍放大鏡對來料IC進行抽檢,對IC 的型號和外觀。

芯片减划工艺 中电智能卡

中电智能卡有限责任公司COB封装厂减薄划片工艺介绍减薄划片工艺介绍—生产流程减薄划片工艺介绍背面减薄 贴磨片膜 抛光 贴划片膜 揭磨片膜 划片团队协作,共创辉煌!减薄划片工艺介绍—贴磨片膜Chuck table CCD Alignme ntRobotDouble load portWork flow:Wafer load Wafer alignmentBG tape laminatingW f unload Wafer l d团队协作,共创辉煌!减薄划片工艺介绍—贴磨片膜Machine specification: 1.Wafer size 8 inch O.F., 8 inch V-notch, 12 inch wafer thickness ≧300μm;V-notchO.F.团队协作,共创辉煌!减薄划片工艺介绍—贴磨片膜2.Load port 8 inch wafer: wafer cassette, FOSB 12 inch wafer: FOUP, FOSBWafer cassetteFOUP团队协作,共创辉煌!减薄划片工艺介绍—贴磨片膜3. 磨片膜型号 Tape Type: UV tape, blue tape, bump tape; Tape Width:230~340mm; Tape Thickness:100~300 μm;团队协作,共创辉煌!减薄划片工艺介绍—背面减薄和贴划片膜Machine model: DGP8761+DFM2800 DFM2800 DGP8761 3 主轴,4磨片平台团队协作,共创辉煌!减薄划片工艺介绍—背面减薄和贴划片膜生产流程:1) ) Cassette 2) Transfer with robot pick 3) Alignment at the position table 4) To C/T with transfer arm 1 5) Rough grinding with Z1‐axis 6) Fine grinding with Z2‐axis 7) Dry ry polish with Z3 3‐axis 8) Wafer cleaning at C/T 9) To Spinner with transfer arm 2 10) Wafer cleaning / dry at spinner section 11) To DFM2800 UV irradiation 12)Transfer to the mounting table 13) Dicing tape mounting using ring 14) Transfer to the peeling table 15) Back grinding tape peeling 16) Load wafer to the frame cassette团队协作,共创辉煌!减薄划片工艺介绍—背面减薄和贴划片膜1. Z1/Z2 Spindle: Diamond wheel, Φ300mm; Z3 Spindle: Dry polishing wheel,为海绵,Φ450mm; 同时选配 G tti DP Getting DP, 可以有效防止memory wafer f 的电迁移效应; 的电迁移效应2. Damage of back side#2000 Dry yp polishTEM (x 106)团队协作,共创辉煌!减薄划片工艺介绍—背面减薄和贴划片膜Wafer厚度控制1. Z1 axis配置1套Inline process gauge Z1 axis i 配置2个Inline li process gauge, 厚度检测范围为0~1800um;Z1轴磨片速度分为 3段, 速度范围:0.1um/s~80um/s。

《COB制程技术研究》PPT课件

精选ppt

20

9 严格的物料存储如金线( 放在干燥的N2环境中,减小湿 度的影响 )

10 一般,球焊的第一个焊点要比第二个位置要高 11 压焊工艺返修简单,但受制于操作空间

Ball Bonding(球焊)和 Wedge Bonding (平焊/楔焊)

1 Ball Bonding ( 球焊)

金线通过空心夹具的毛细管穿出,然后经过电弧放电使 伸出部分熔化,并在表面张力作用下成球形,然后通过夹具 将球压焊到芯片的电极上,压下后作为第一个焊点,为球焊 点,然后从第一个焊点抽出弯曲的金线再压焊到相应的位置 上,形成第二个焊点,为平焊(楔形)焊点,然后又形成另 一个新球用作于下一个的第一个球焊点。

精选ppt

21

2.7 压焊工艺的评估

通常,对压焊效果的评估有两种方法:外观检查及机械 测试。 1 外观检查

外观检查主要通过光学显微镜,电子显微扫描(SEM), X 射线探测等手段来实现。

SEM 探测图(良好的球焊效果及月牙形的尾部)

精选ppt

22

2 机械测试

最常用的机械测试方法有两种:拉力测试和焊球剪切测 试。

COB制程技 術研究

精选ppt

1

目錄

一 前言 二 綁定技术介绍 三 COB制作工艺流程 四 COB技朮的電子技術快速發展帶動下,小型化的攜帶式電子產品, 不再是遙不可及,已成為風行全球的發展趨勢。最具代表性 的例子,如薄型筆記型電腦、個人數位助理(PDA)、移動電 話、數碼相機,均是時下最熱門的電子產品。這些小型化攜 帶式電子產品中,由於IC晶片的廣泛使用,也使得半導體的 技術發展一日千里。在未來電子產品不斷朝向輕薄、短小、 高速、高腳數等特性發展的潮流下,其中除電子元件是主要 關鍵外,COB (Chip On Board)已成為一種普遍的封裝技 術,各種型式的先進封裝方式中,晶片直接封裝技術扮演著 重要角色。

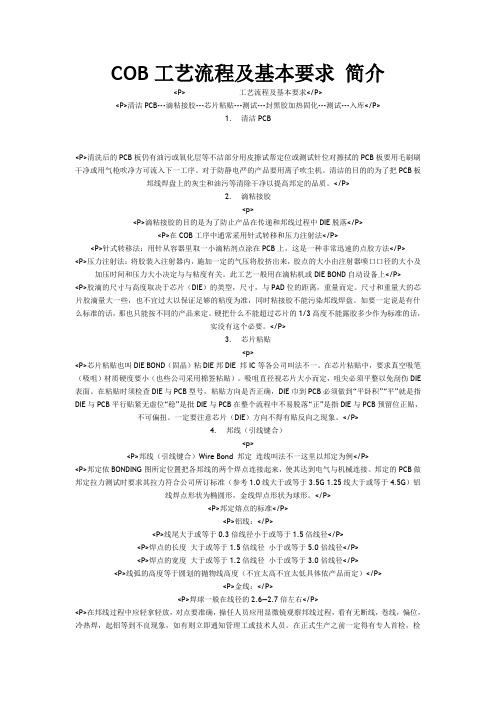

COB工艺流程及基本要求简介

COB工艺流程及基本要求简介<P> 工艺流程及基本要求</P><P>清洁PCB---滴粘接胶---芯片粘贴---测试---封黑胶加热固化---测试---入库</P>1.清洁PCB<P>清洗后的PCB板仍有油污或氧化层等不洁部分用皮擦试帮定位或测试针位对擦拭的PCB板要用毛刷刷干净或用气枪吹净方可流入下一工序。

对于防静电严的产品要用离子吹尘机。

清洁的目的的为了把PCB板邦线焊盘上的灰尘和油污等清除干净以提高邦定的品质。

</P>2.滴粘接胶<p><P>滴粘接胶的目的是为了防止产品在传递和邦线过程中DIE脱落</P><P>在COB工序中通常采用针式转移和压力注射法</P><P>针式转移法:用针从容器里取一小滴粘剂点涂在PCB上,这是一种非常迅速的点胶方法</P><P>压力注射法:将胶装入注射器内,施加一定的气压将胶挤出来,胶点的大小由注射器喷口口径的大小及加压时间和压力大小决定与与粘度有关。

此工艺一般用在滴粘机或DIE BOND自动设备上</P><P>胶滴的尺寸与高度取决于芯片(DIE)的类型,尺寸,与PAD位的距离,重量而定。

尺寸和重量大的芯片胶滴量大一些,也不宜过大以保证足够的粘度为准,同时粘接胶不能污染邦线焊盘。

如要一定说是有什么标准的话,那也只能按不同的产品来定。

硬把什么不能超过芯片的1/3高度不能露胶多少作为标准的话,实没有这个必要。

</P>3.芯片粘贴<p><P>芯片粘贴也叫DIE BOND(固晶)粘DIE邦DIE 邦IC等各公司叫法不一。

在芯片粘贴中,要求真空吸笔(吸咀)材质硬度要小(也些公司采用棉签粘贴)。

吸咀直径视芯片大小而定,咀尖必须平整以免刮伤DIE 表面。

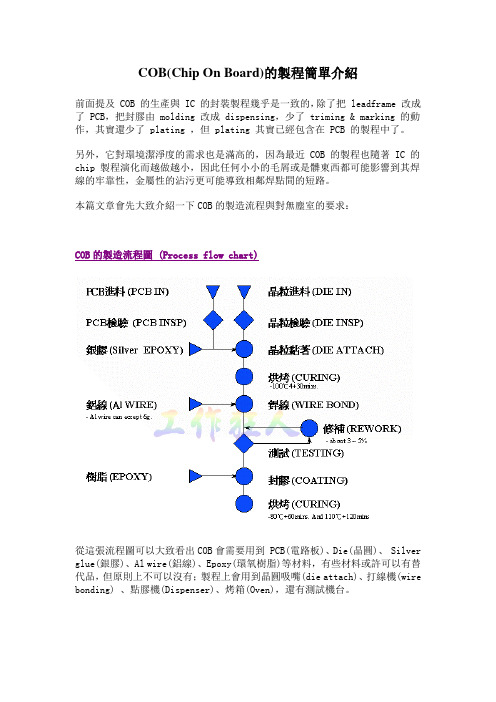

COB(Chip On Board)的制程简单介绍

COB(Chip On Board)的製程簡單介紹前面提及 COB 的生產與 IC 的封裝製程幾乎是一致的,除了把 leadframe 改成了 PCB,把封膠由 molding 改成 dispensing,少了 triming & marking 的動作,其實還少了 plating ,但 plating 其實已經包含在 PCB 的製程中了。

另外,它對環境潔淨度的需求也是滿高的,因為最近 COB 的製程也隨著 IC 的chip 製程演化而越做越小,因此任何小小的毛屑或是髒東西都可能影響到其焊線的牢靠性,金屬性的沾污更可能導致相鄰焊點間的短路。

本篇文章會先大致介紹一下COB的製造流程與對無塵室的要求:COB的製造流程圖 (Process flow chart)從這張流程圖可以大致看出COB會需要用到 PCB(電路板)、Die(晶圓)、 Silver glue(銀膠)、Al wire(鋁線)、Epoxy(環氧樹脂)等材料,有些材料或許可以有替代品,但原則上不可以沒有;製程上會用到晶圓吸嘴(die attach)、打線機(wire bonding) 、點膠機(Dispenser)、烤箱(Oven),還有測試機台。

看起來很簡單,其實也真的很簡單,只要把建一個無塵室的房間,買進必要的機台就可以生產了,但要達到99%以上的良率,紀律及製程管控是一定需要的。

後來我們再一一的詳細介紹吧!COB的環境要求—無塵室建議一定要有潔淨室/無塵室 (Clean Room)且等級(Class)最好在100K以下,IC 封裝測試業的無塵室一般都要求在10k或甚至1k,晶圓廠就更高等級了。

因為COB的製程屬於晶圓封裝等級,所以任何小小的微粒沾污於焊接點都會造成焊線結品質構的嚴重不良,就把房子蓋在有垃圾的地基上,房子怎麼穩固呢。

相關閱讀:無塵室(Clean Room)的級數標準規格基本的無塵衣帽防護也有其必要,不一定需要套頭包成肉粽式的無塵衣,但基本的帽子、衣服、及靜電鞋都是必須的,最主要是避免 wire bond 時微塵到處飛沾污到焊線位置。

cob芯片工艺

cob芯片工艺1. 概述cob芯片工艺指的是Chip on Board的制程技术,是一种新型的半导体封装技术。

传统的半导体封装技术中,芯片通常是先进行封装封装,再焊接至电路板。

而cob芯片工艺,是将裸露的芯片直接贴合在PCB上,利用导电胶水或焊线进行连接,在简化封装过程的同时提高了电路的可靠性和性能。

2. cob芯片工艺的优势cob芯片工艺相较于传统封装技术具有以下几个优势:2.1 尺寸小由于cob芯片工艺省去了芯片封装,因此芯片和PCB之间的距离很小,可以实现非常紧凑的设计。

这对于一些有尺寸限制的应用场景非常重要,如便携设备、空间受限的电子产品等。

2.2 散热性能优秀由于芯片直接贴合在PCB上,通过PCB整体散热,相比于传统封装技术有更好的散热性能。

这对于功耗较高的芯片来说尤为重要,可以避免过热对芯片性能和寿命的影响。

2.3 电信号传输短延迟cob芯片工艺中,芯片直接贴合在PCB上,电信号传输距离短,减少了信号延迟。

这对于一些对实时性要求较高的应用场景非常有利,如光通信、高频电路等。

2.4 可靠性高由于芯片直接贴合在PCB上,与传统封装技术相比,cob芯片工艺的连接更为牢固,减少了外部环境因素对连接的影响,提高了电路的稳定性和可靠性。

3. cob芯片工艺的应用领域cob芯片工艺由于其优势,被广泛应用于以下领域:3.1 LED照明LED照明中,cob芯片工艺可以实现尺寸小、散热好的设计,满足高亮度、高可靠性的要求。

3.2 汽车电子在汽车电子中,cob芯片工艺可以应用于电子控制单元(ECU)、车载电子、车灯等模块,具有尺寸小、散热好、可靠性高的优势。

3.3 通讯设备在通讯设备中,cob芯片工艺可以应用于天线、射频模块等,具有尺寸小、传输短延迟、可靠性高的特点。

3.4 传感器在传感器领域,cob芯片工艺可以实现尺寸小、散热好的设计,满足高性能、高可靠性的要求。

4. cob芯片工艺的制程步骤cob芯片工艺的制程步骤如下:4.1 芯片切割将芯片从硅晶圆切割成单个芯片。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

工程设计是一个项目的起点,主要分为两类情况 1.客户提供电路设计,我司完成拼版设计 2.客户提供原理图后由我司设计电路图和拼版图

Wafer减薄划片:

芯片减划厚度主要由以下三个方面决定 1. 产品厚度; 2.叠层需求; 3.芯片自身制程能力。

专业封装协作,共创商业价值

四、SIMpass/SDpass案例介绍---SMT贴件

专业封装协作,共创商业价值

中电智能卡有限责任公司COB封装厂

一、CSP封装工艺流程简介 二、CSP技术应用于智能卡模块的生产优势 三、COB封装工艺流程简介 四、SIMpass/SDpass案例介绍 五、COB封装厂产品介绍 六、合作伙伴

专业封装协作,共创商业价值

一、CSP封装工艺流程介绍

工艺介绍

表面贴装设备

回流炉

专业封装协作,共创商业价值

三、SIMpass/SDpass案例介绍---装片

工艺能力

1.基板和框架尺寸: 长度:120—260mm; 宽度:9-75mm; 厚度: 0.1-0.4mm 2.Wafer尺寸:8inch 或 12inch 3.Die尺寸:Max:25.4* 25.4mm; Min:0.25 * 0.25mm 4.Die厚度:>70um 5.粘接方式:Epoxy 或 DAF

装片

专业封装协作,共创商业价值

案例

四、SIMpass/SDpass案例介绍---压焊

工艺能力:

1.基板和框架尺寸: 长度:100-270mm; 宽度:15-84mm; 厚度:0.10.8mm 2.焊盘规格:Pad size : Min 50um*50um ; Pad pitch: Min 50um 3.线弧长度:Max 9mm(Wire diameter:20um) 4.焊接方式:超声波压焊 5.焊线材料:金线

1.印刷粘结剂. 2.芯片倒贴装. 3.加热固化. 4.点胶固化.

下手臂拾取芯片

专业封装协作,共创商业价值

上手臂接取芯片

上手臂完成贴片

二、CSP技术应用于智能卡模块的生产优势

传统载带模块工艺

晶圆减薄磨片 Wafer划片

芯片正面贴装

CSP模块工艺

晶圆减薄磨片

RDL+SOLDER Wafer划片

芯片倒贴装

完整的生产管理和质量控制体系,已获得ISO9000国际质量管理 体系认证、中国移动SIM卡生产许可、国家质量监督局IC卡生产许可 等多种资质。公司良好的信誉和先进的生产技术,获得工信部和公 安部认可,被指定为第二代身份证专用模块生产厂。

坚持“严格管理、规范操作、用户至上、创新技术、快速行动” 的经营理念,用先进的制造技术,为国内外用户累计制造各种IC卡 模块约30亿块,IC卡约15亿张。

中电智能卡有限责任公司

CSP及COB产品封装工艺简介

专业封装协作,共创商业价值

中电智能卡有限责任公司简介

国内专业智能卡及模块制造企业。下设COB封装厂、模块厂和卡 厂,专业生产各种接触、非接触、双界面模块,双界面卡片,TF卡, 大容量SIM及U-KEY等; 公司年生产能力为:IC卡4亿张,接触和非接触模块5.1亿块,大容 量SIM和TF卡2000万张。

倒贴装

专业封装协作,共创商业价值

一、CSP封装工艺流程介绍

流程介绍

Wafer减薄

RDL+SOLDER+划片

印刷粘结剂

芯片倒贴装 Flip Chip

加热固化 curing

点胶固化

测试Test

专业封装协作,共创商业价值

一、CSP封装工艺流程介绍---RDL(重新布线技术)

已钝化圆片

涂覆BCB(或PI)

固化后产品

固化后产品

专业封装协作,共创商业价值

二、CSP技术应用于智能卡模块的生产优势

1、可靠性高 1.1芯片的粘结牢固程度高,避免了传统工艺贴片+包封的缺点。 1.2导通性能好,避免出现传统工艺的金线键合拉力问题。 1.3散热性能好。 1.4允许芯片厚度大,降低减划裂片风险,提高产品可靠性。 1.5耐高温性能好。 2、生产效率高 现有CSP生产线均采用成熟半导体封装技术,设备稳定可靠,生产流程短, 成品模块的出货周期较短。 3、成本降低 传统载带为FCI法国进口,其来料成本较高。而CSP使用国产基板,交货及 时,产品性价比高。

CSP模块工艺中RDL+Solder是 对整个WAFER的布线植球,加工 效率极高;采用成熟的半导体倒贴 装工艺和点胶固化,成本降低。

传统载带模块工艺需要进行WB 和UV包封,均为单颗模块生产, 整体生产工艺较为繁琐且效率低、 金丝、包封材料成本高。

热固化 WB引线键合

UV包封/塑封

加热固化

点胶固化

专业封装协作,共创商业价值

四、SIMpass/SDpass案例介绍---塑封

工艺目的:

使用热硬化性材料将产品包封起来成形的过程。

工艺步骤:

1.表面清洁PLASMA. 2.注塑成型MOLDING. 3.固化烘烤OVEN CURING.

专业封装协作,共创商业价值

四、SIMpass/SDpass案例介绍---切割(LC、PS)

工艺能力:

1.基板尺寸: 长度:180~280mm;宽度:45~75mm; Thickness: 0.1 - 1.5 mm 2.注塑方式: 真空注塑 3.注塑压力:Max. transfer pressure: 10Mpa 4.料饼规格:Pellet diameter: 11, 14 or 14.3 mm;Max. pellet length: 45 mm

专业封装协作,共创商业价值

三、COB封装工贴件

Die-bonding

压焊

Wire-bonding

电路图和基板设计制作(PCB)

塑封

激光切割

直线切割

测试

Molding

Laser cutting

Package sawing

Testi

专业封装协作,共创商业价值

四、SIMpass/SDpass案例介绍---工程设计及wafer减划 工程设计:

压焊设备

案例

专业封装协作,共创商业价值

四、SIMpass/SDpass案例介绍---压焊

工艺目的:

将芯片的可焊接区和基板的可焊区连接起来, 使之形成电气通路。

工艺步骤:

1.表面清洁。2.金丝压焊。3. 外观检测。

专业封装协作,共创商业价值

四、SIMpass/SDpass案例介绍---塑封

光刻新/老焊区

溅射UBM(如Ti-Ni-Cu) 光刻UBM,使新/老焊区布线相连

二次涂覆BCB(或PI)

光刻新焊区窗口 电镀(或印刷)焊料(膏)

再流,形成焊料球

WLP完成 WLP测试/贴装/打印等

专业封装协作,共创商业价值

一、CSP封装工艺流程介绍---Flip Chip

工艺目的 Flip Chip(倒封装工艺)通过倒封装技术将植球后的晶圆级 芯片倒贴到载板焊点上,实现芯片与载板的电性导通. 工艺步骤

五、COB封装厂主要产品---CSP封装工艺

M2模块封装

M3模块封装

FPC封装

专业封装协作,共创商业价值

六、合作伙伴

专业封装协作,共创商业价值

中电智能卡有限责任公司COB封装厂

专业封装协作,共创商业价值

CSP(Chip Scale Package),即芯片级封装,具有封装尺寸小,导 电性能和散热性能好,制造工艺成熟等一系列的优点。 实用新型专利:ZL201120052387.7; ZL201120039928.2 ; ZL201120193894.2 。发明专利: ZL20110039517.8

工艺能力:

1.激光切割范围是64X64mm2 ,可依客户产品布局单独编制各种程序进 行任意形状的产品切割; 2.直线切割宽度可以依据刀具宽度而定。目前的切割宽度为0.4mm。 3.直线切割可依客户产品布局,量身定制模具和程序。 4.切割精度为±0.1mm

工艺目的:

工艺步骤:

1.图形编程。 2.参数设定。 3.测量确认。

工艺能力

1.可贴装元器件尺寸--- Min 01005封装,常规0201、 0402、0603(英制) 2.Micro Chip贴件精度(Accuracy): ± 50um; 3.可使用PCB基板尺寸:L50mm X W30mm--L610mm XW430mm; 4.包装形式:编带、 托盘

表面印刷

通过(LC)激光切出产品的曲线部分,然后使用(PS)直线设备切 产品的直线部分, 最终形成产品的外形轮廓.

LC切割 专业封装协作,共创商业价值

直线切割

五、COB封装厂主要产品---COB封装工艺

Micro SD卡

3FF卡

4FF卡

2FF卡

USB-Key

CPU模块

SD无线wifi卡

专业封装协作,共创商业价值